Built-in self-test system based on on-chip system or system-in-package

A system-in-package, built-in self-test technology, applied in the field of built-in self-test systems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

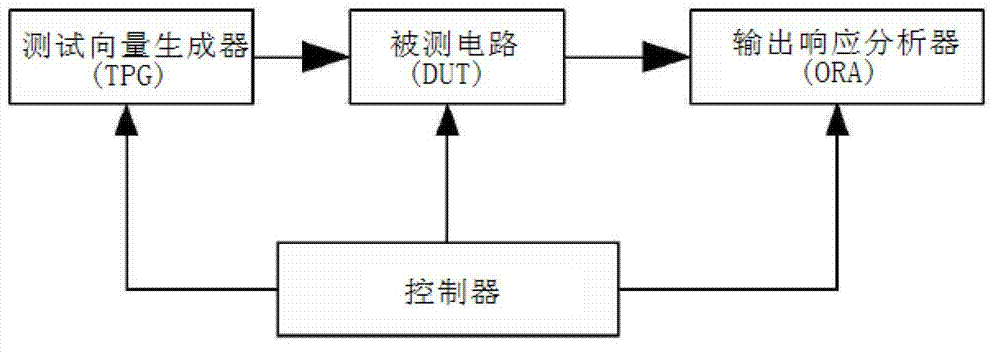

[0027] In order to solve the problem that the built-in self-test occupies a large area of the system-on-chip or system-in-package due to the large number of analog components, the system-on-chip or system-in-package is more complex, and the reliability of the system-on-chip or system-in-package is low. The problem is to provide a built-in self-test system based on a system-on-chip or system-in-package.

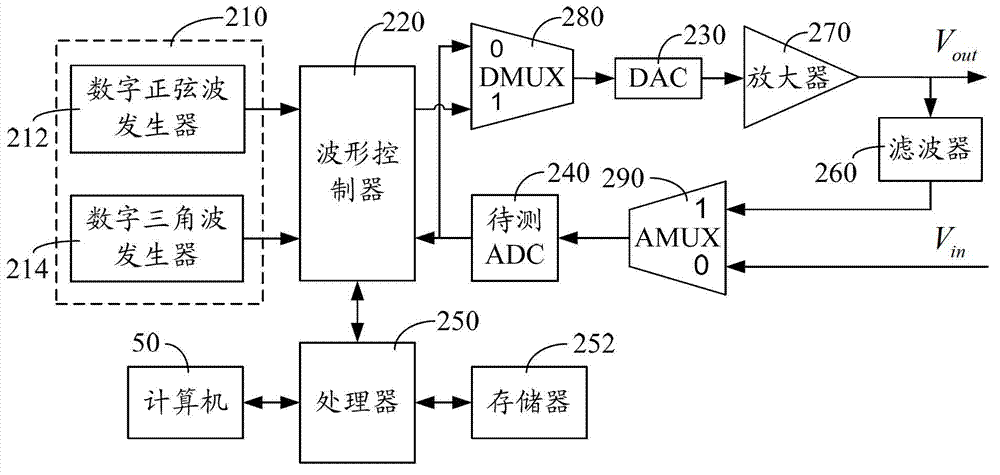

[0028] Such as figure 2 As shown, an embodiment of a system-on-chip or system-in-package based built-in self-test system includes a waveform generator 210 , a waveform controller 220 , a digital-to-analog converter 230 , an analog-to-digital converter under test 240 and a processor 250 .

[0029] The waveform generator 210 is used to generate a test voltage excitation signal. The system-on-chip or system-in-package-based built-in self-test system of this embodiment has a test mode and a normal mode. The waveform generator 210 is integrated in the system-on-chip or system-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com