Dynamic reconfigurable subnetting method and system based on network on chip

An on-chip network and network division technology, applied in the direction of instruments, electrical digital data processing, computers, etc., can solve problems such as inability to meet the requirements of dynamic characteristics, and achieve the effect of improving utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

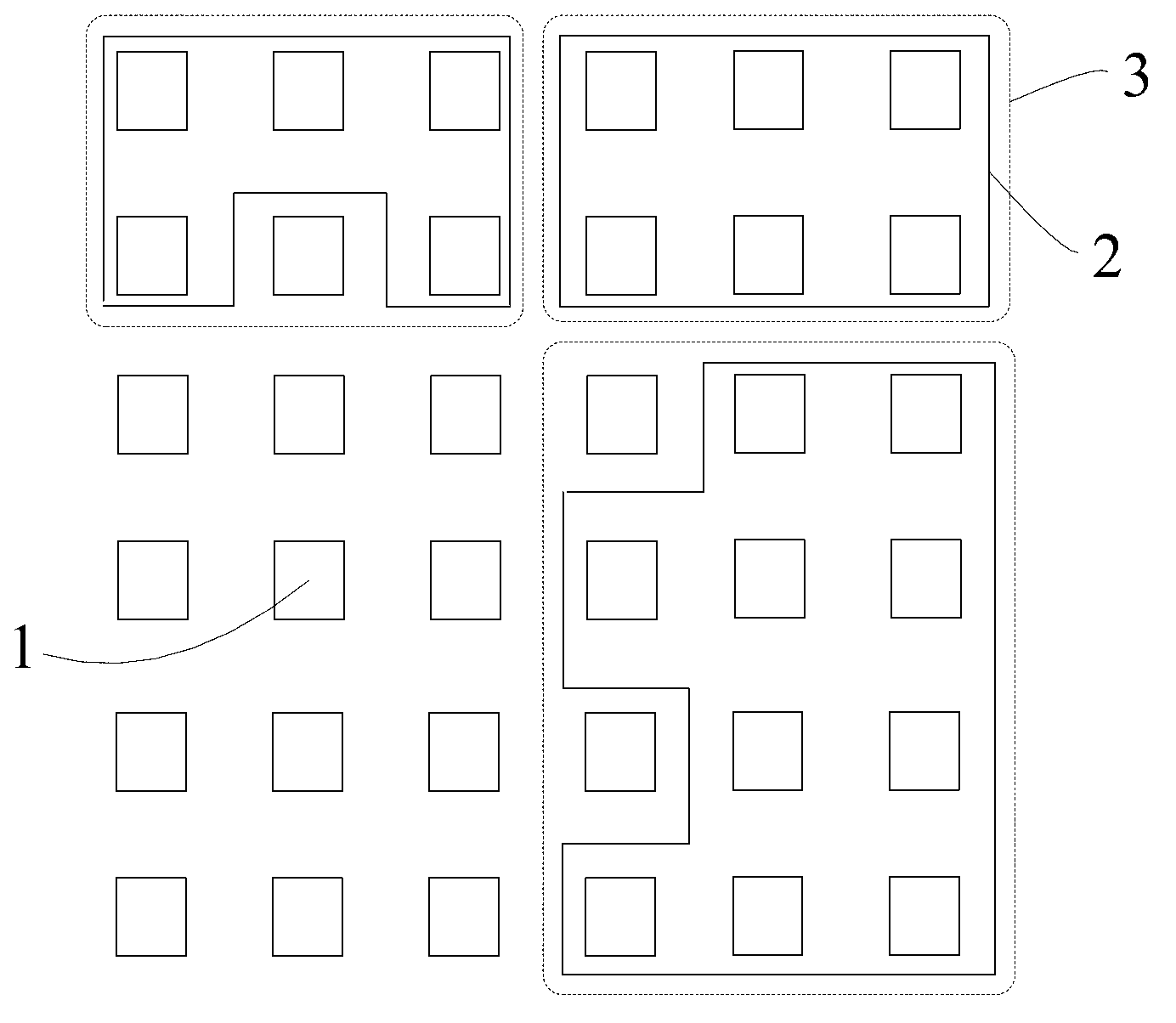

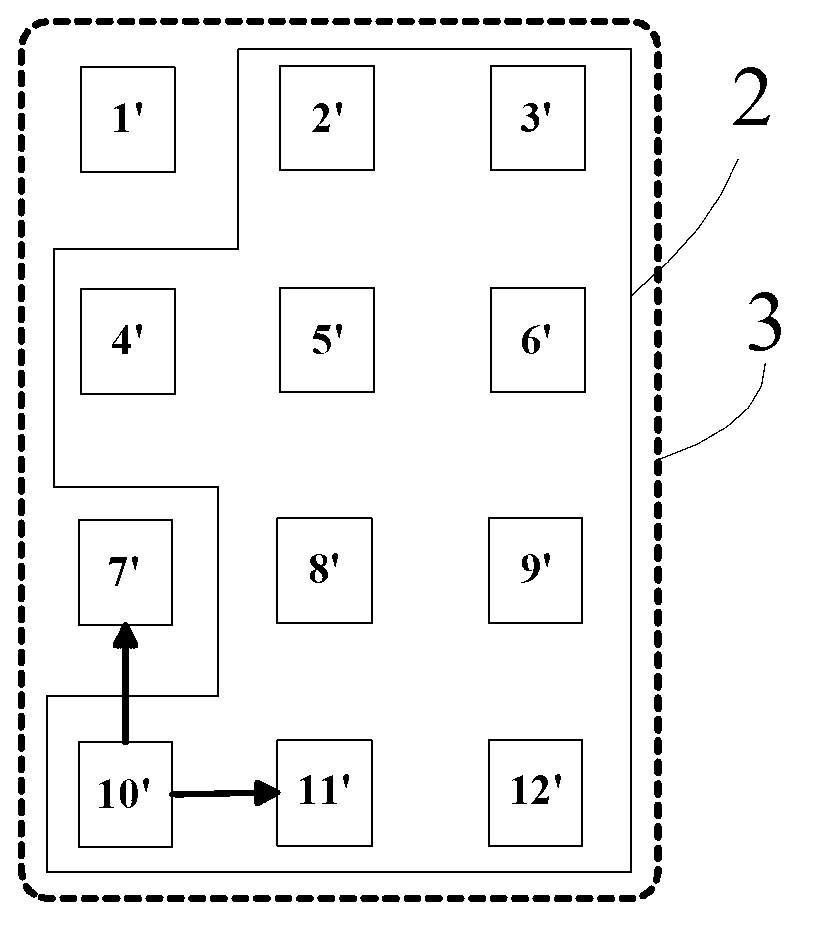

[0034] The present invention proposes a dynamic reconfigurable subnet division method and system based on an on-chip network, which is mainly used in a simple many-core processor environment. By dividing logical subnets and physical subnets at the on-chip interconnection network level, the The purpose of the impact of the subnetwork division scheme on the inter-core communication is to play a huge supporting role in the resource allocation strategy of the upper layer of the system, and finally effectively improve the utilization rate of computing resources in the many-core processor system.

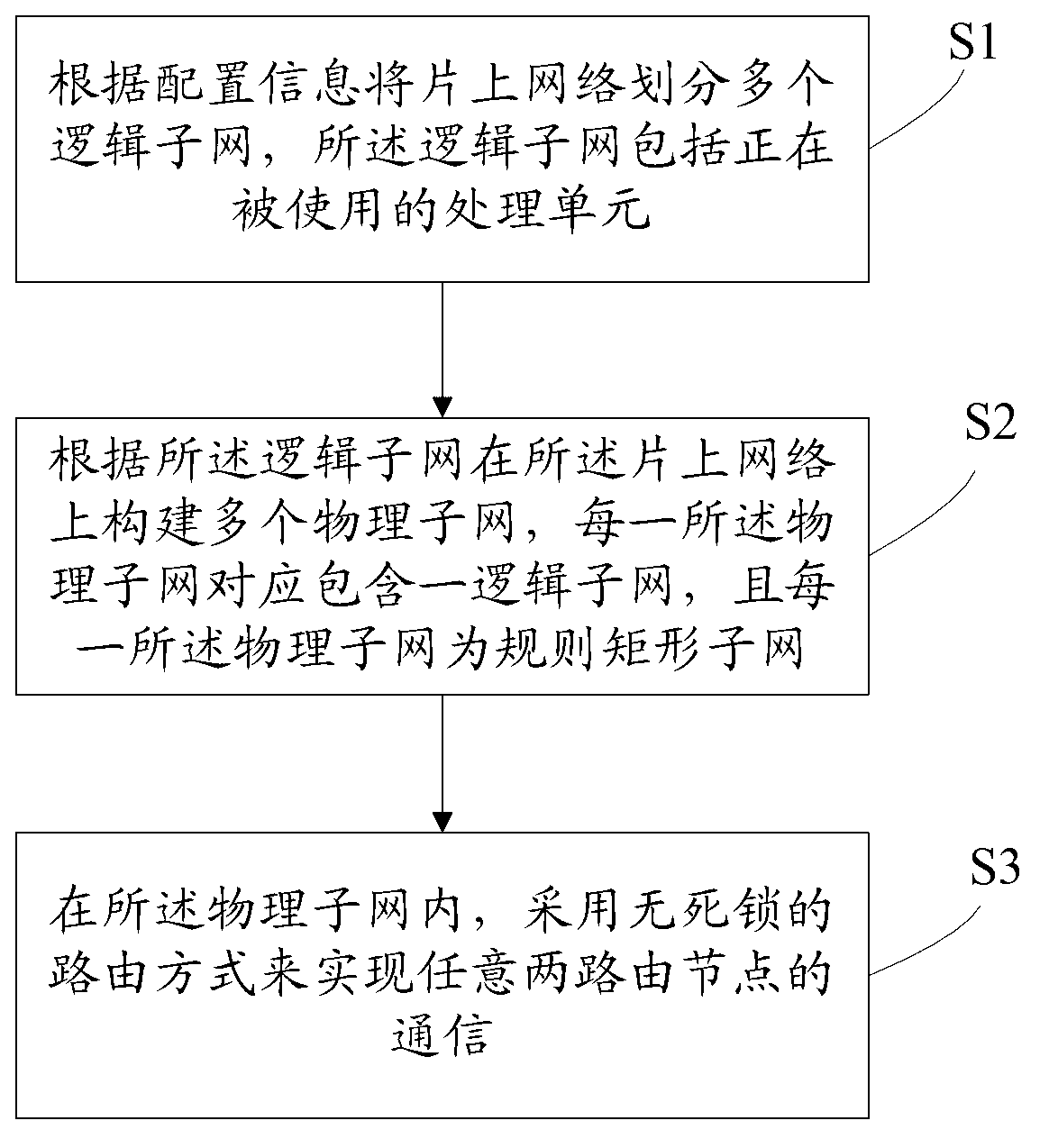

[0035] see figure 1 A method for dividing a dynamically reconfigurable subnet based on a network-on-chip in the present invention comprises the following steps:

[0036] Step S1: divide the network-on-chip into multiple logical subnets according to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More