Patents

Literature

85 results about "Deadlock free" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

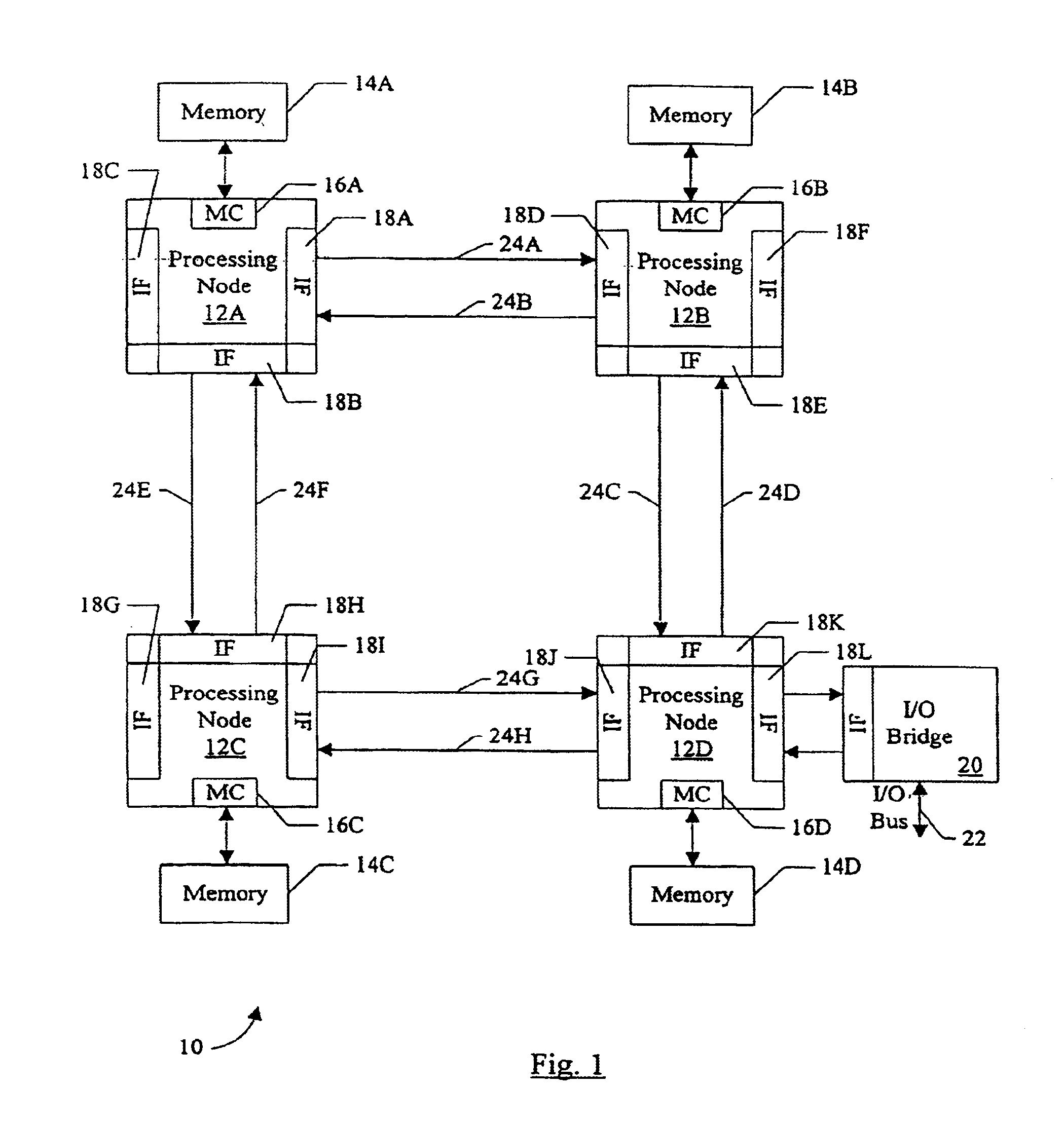

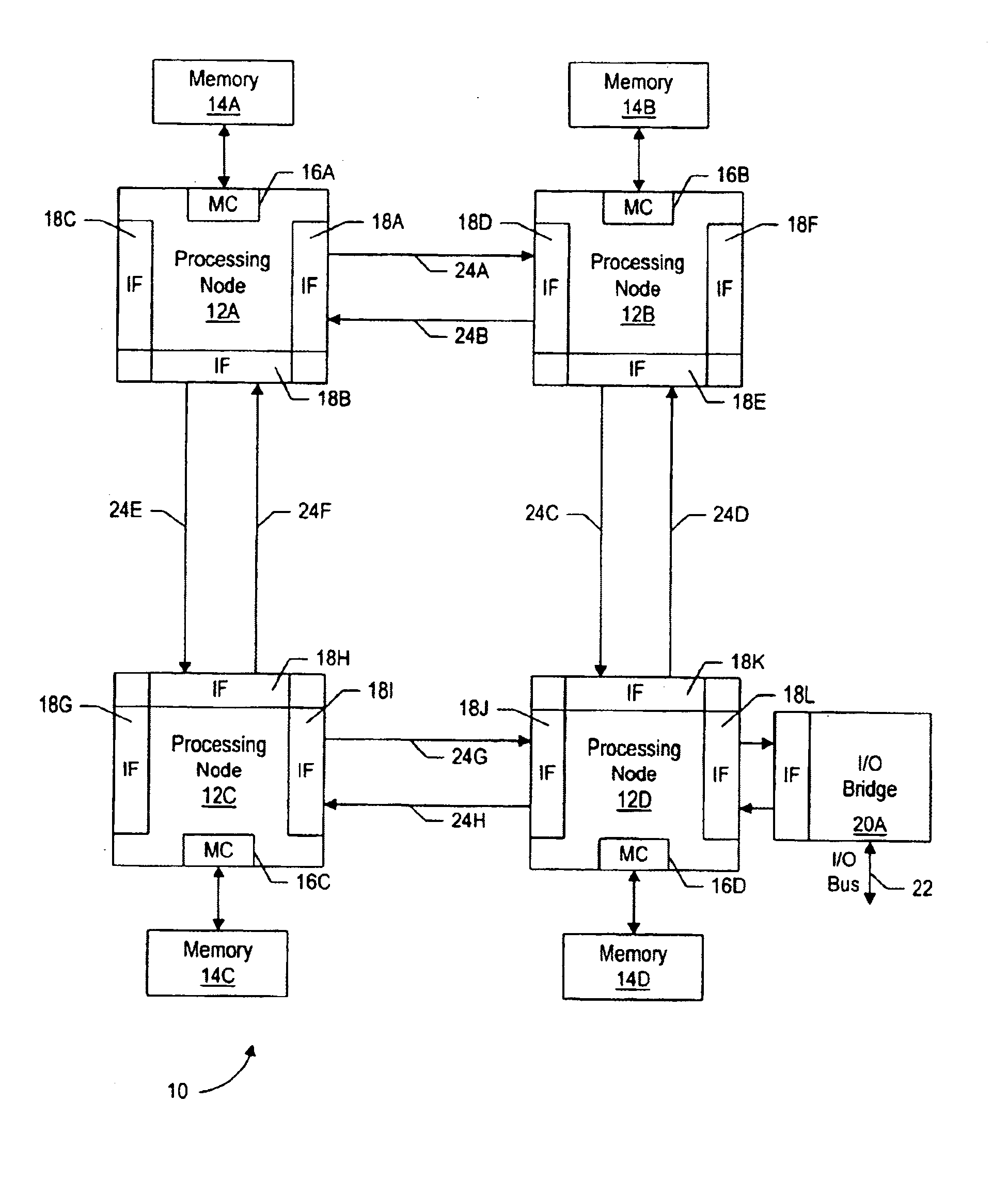

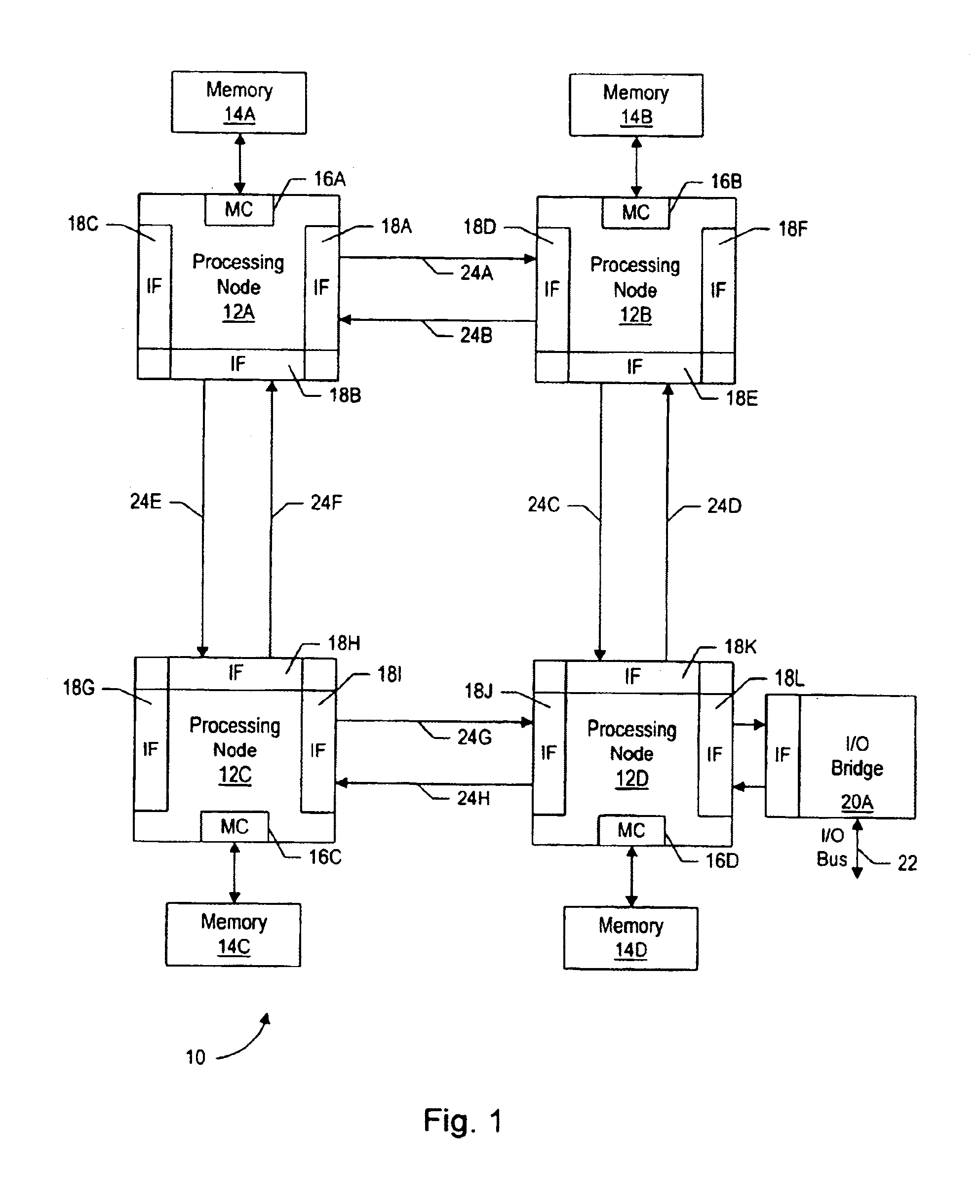

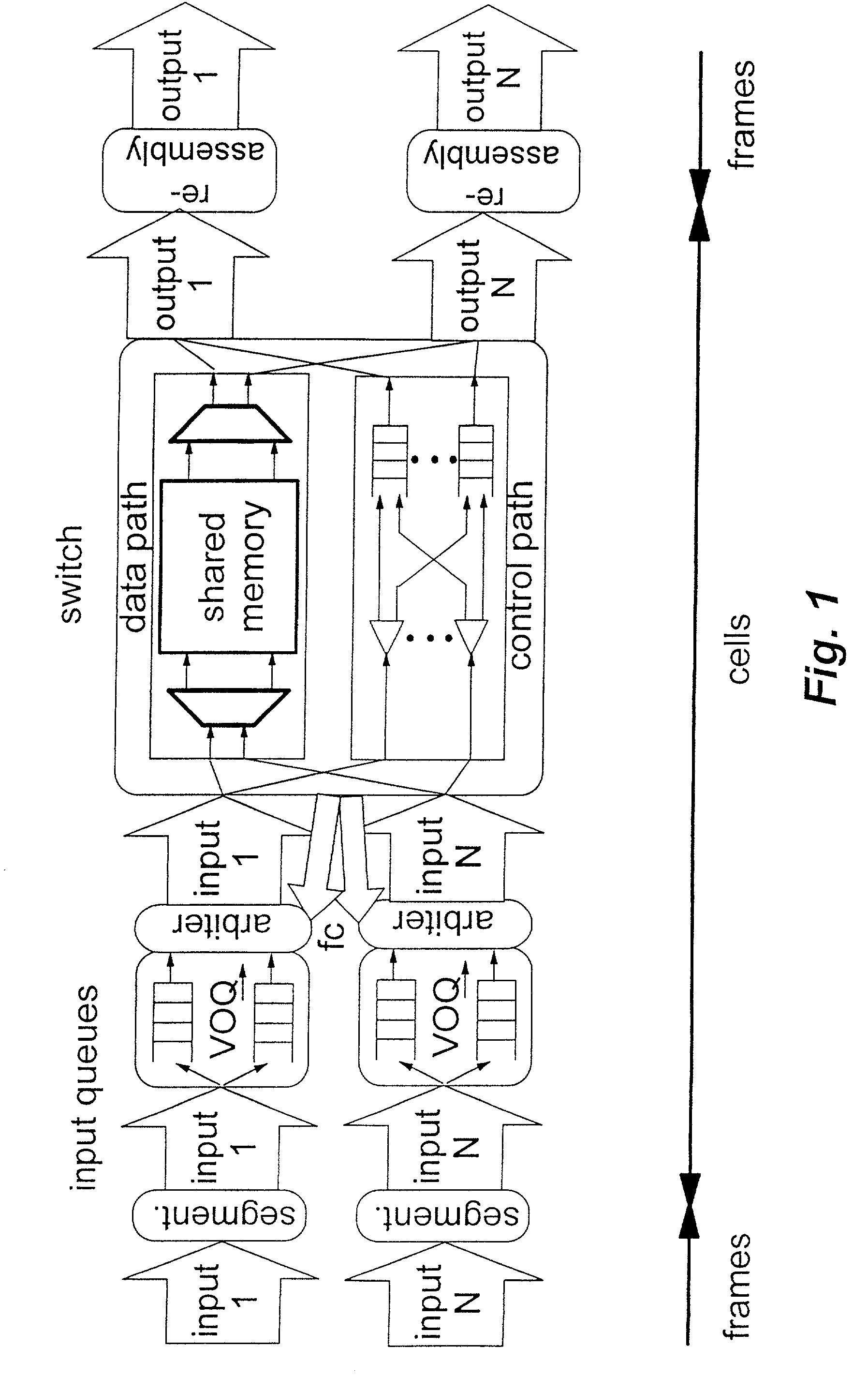

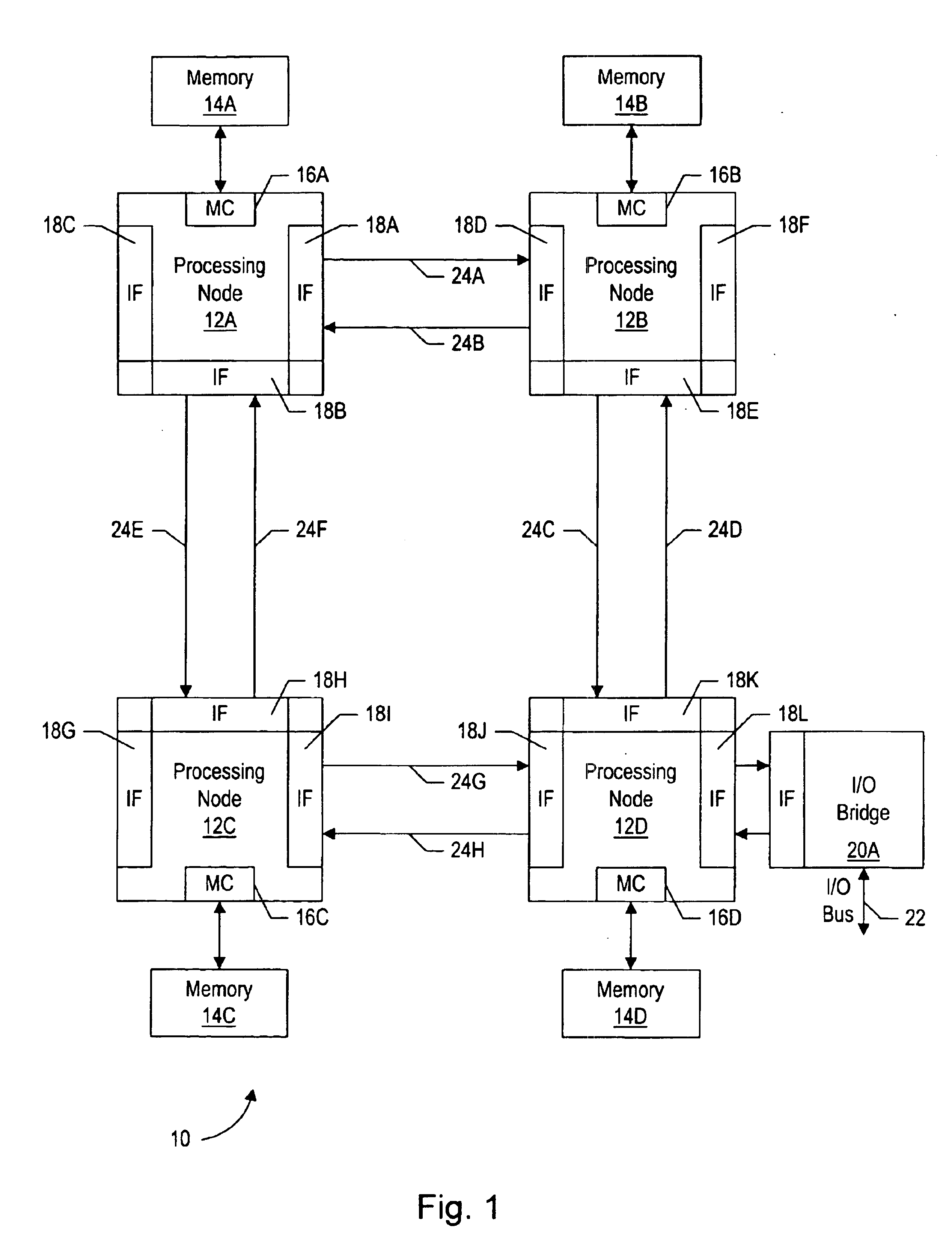

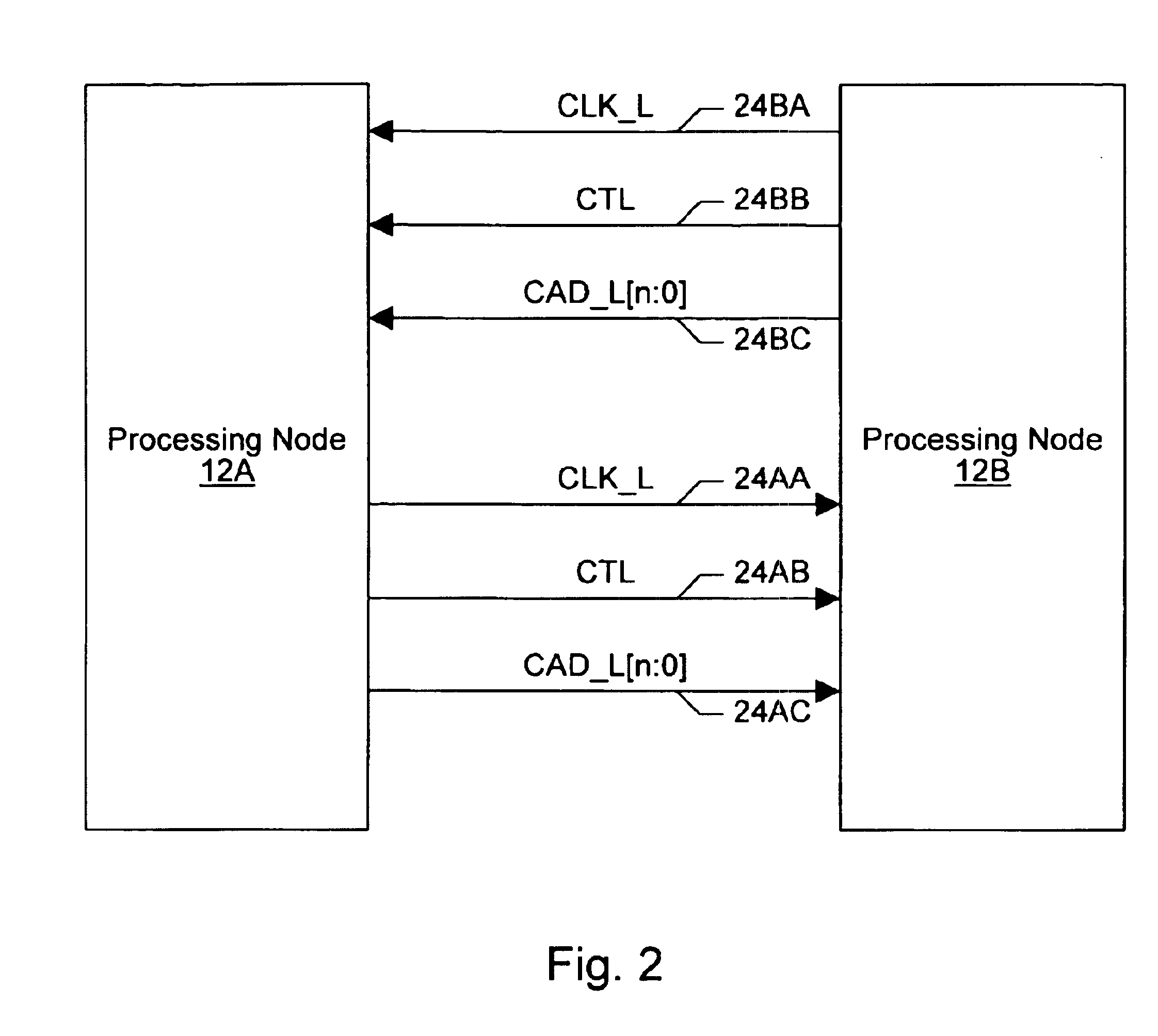

System and method for implementing a separate virtual channel for posted requests in a multiprocessor computer system

InactiveUS6950438B1Avoiding certain deadlockDeadlock-free operationTime-division multiplexData switching by path configurationMulti processorComputer compatibility

A computer system employs virtual channels and allocates different resources to the virtual channels. More particularly, the computer system provides a posted commands virtual channel separate from the non-posted commands virtual channel for routing posted and non-posted commands or requests through coherent and noncoherent fabrics within the computer system. Because separate resources are allocated to the virtual channels in the computer system, posted requests may be allowed to become unordered with other requests from the same source. Implementation of a separate posted commands virtual channel may allow the computer system to maintain compatibility with I / O systems in which posted write requests may become unordered with previous posted requests (e.g., the Peripheral Component Interconnect Bus, or PCI). Implementation of the separate posted commands virtual channel thus may assist in providing deadlock-free operation.

Owner:ALPHA PROCESSOR +2

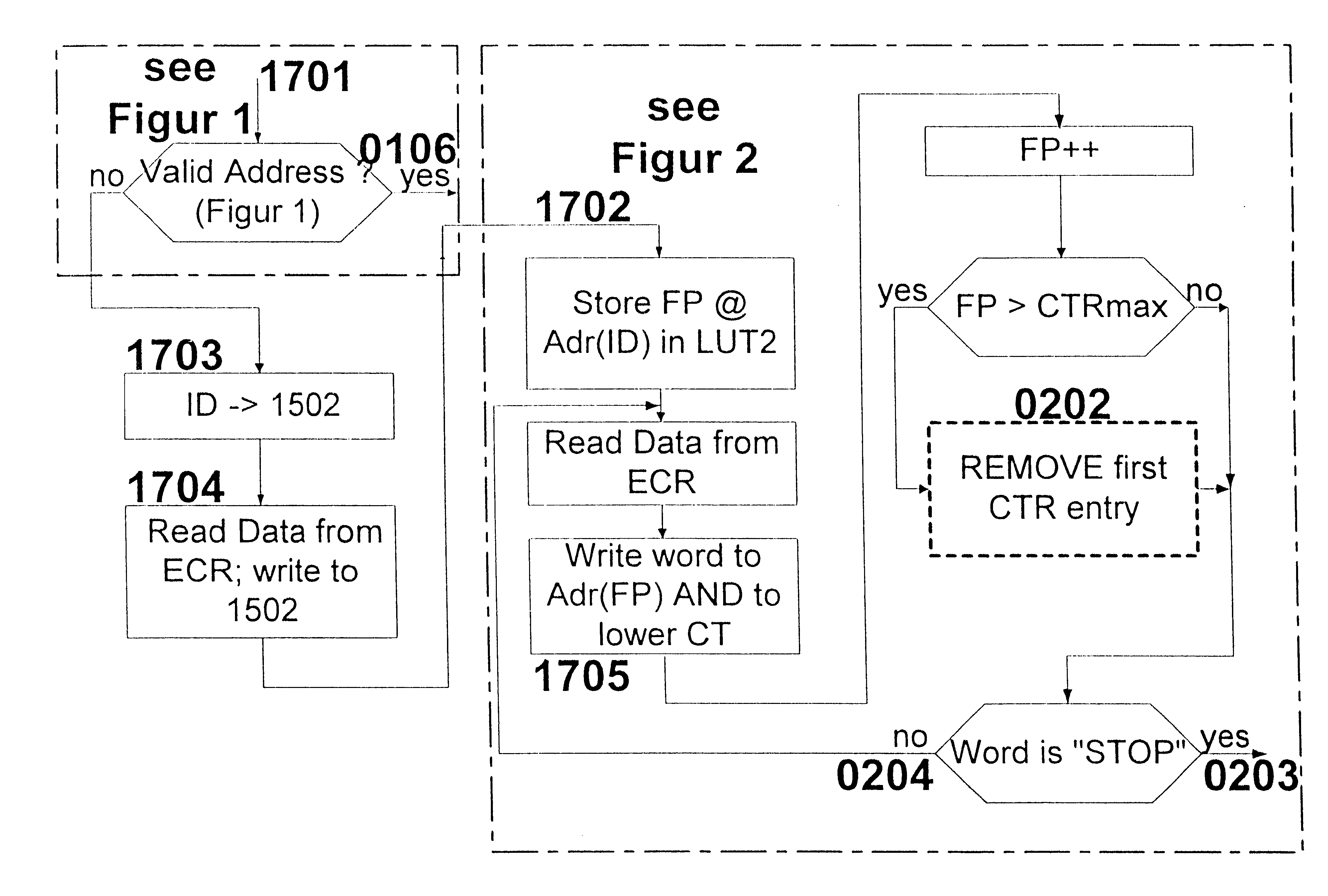

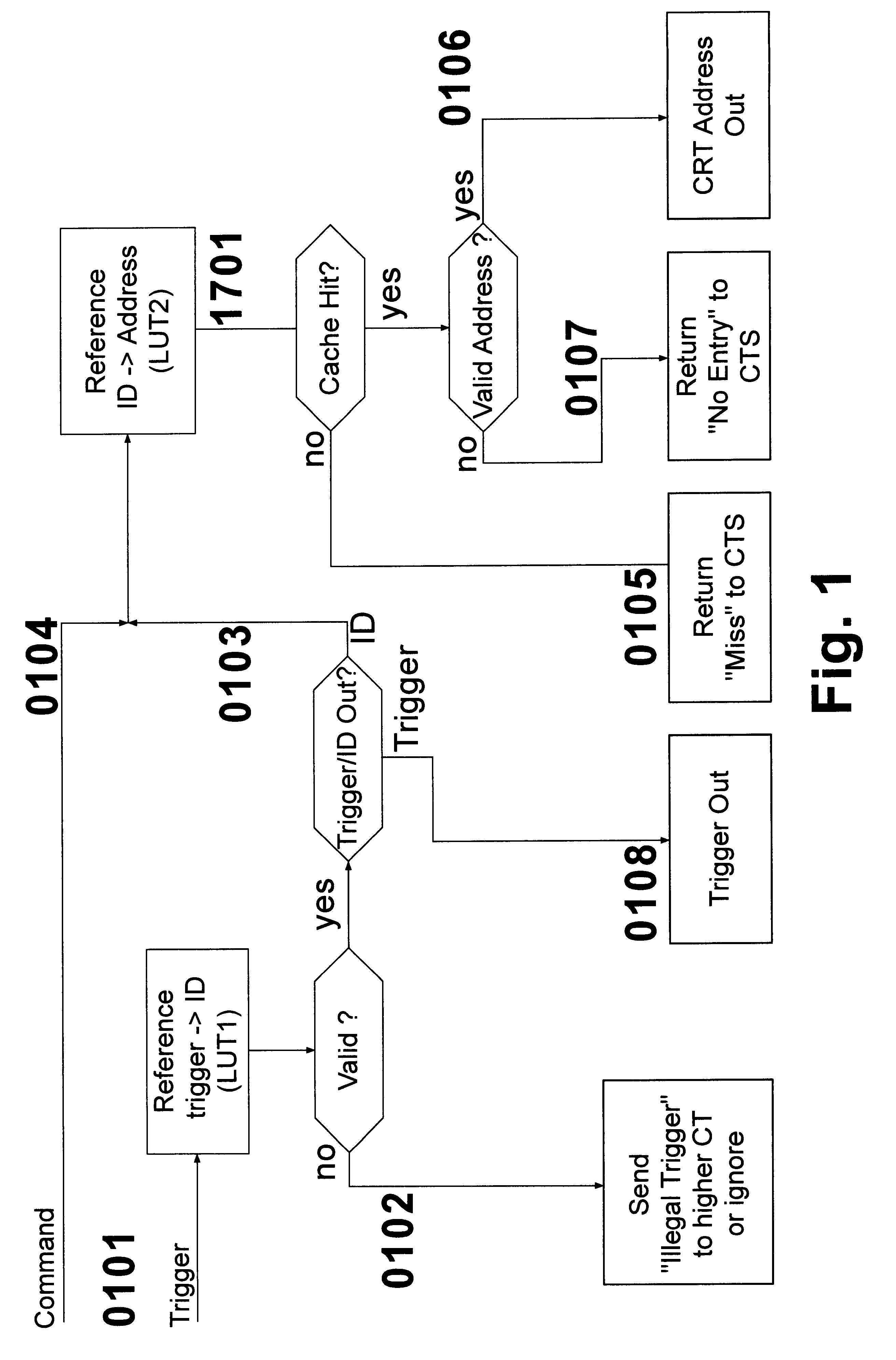

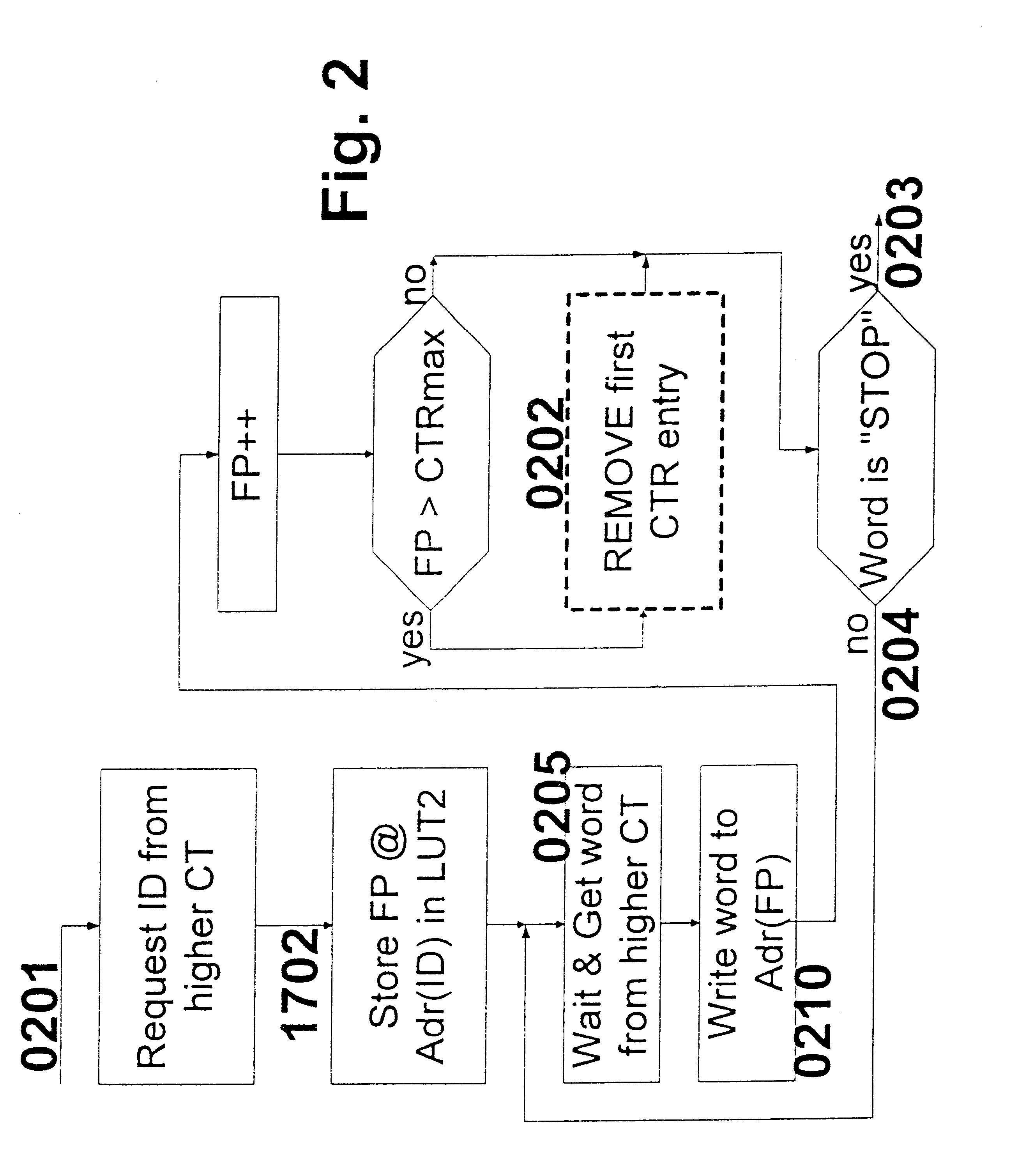

Method for deadlock-free configuration of dataflow processors and modules with a two- or multidimensional programmable cell structure (FPGAs, DPGAs, etc.)

InactiveUS6571381B1Memory adressing/allocation/relocationData resettingAuto-configurationData stream processing

A method of deadlock-free, automatic configuration and reconfiguration of modules having a two- or multidimensional cell arrangement, in which a unit for controlling the configuration and reconfiguration manages a set of associated configurable elements, the set being a subset or the total set of all configurable elements, and the management takes place as follows: reconfiguration requests from the associated configurable elements are sent to the unit; the unit processes the requests; the unit processes the configuration data of the command sequence; and after the configuration data has been fully processed, new requests are accepted again, the configuration data still to be loaded of the existing previous requests being loaded from a buffer memory (FILMO) into the configurable elements until a new request occurs.

Owner:SCIENTIA SOL MENTIS AG

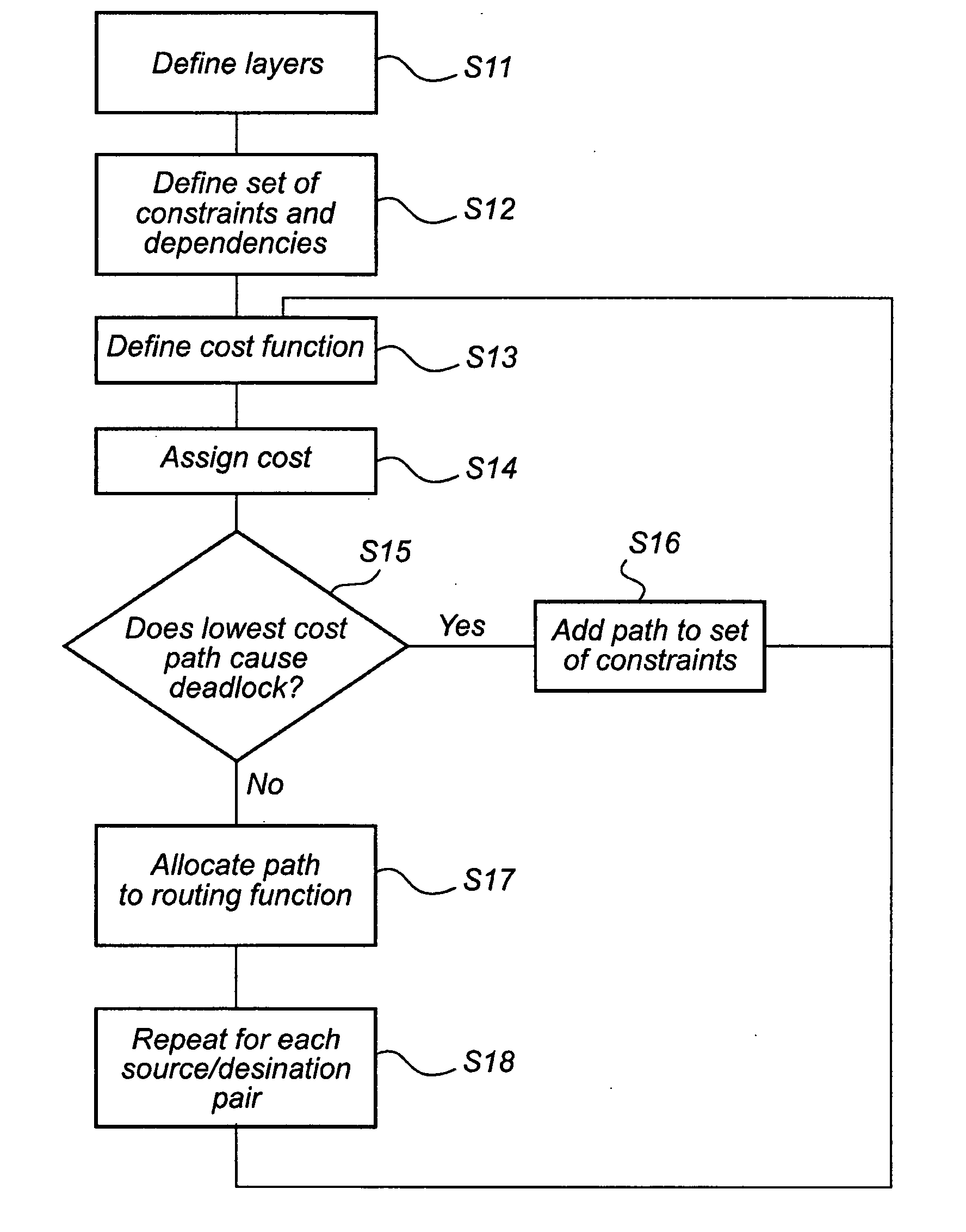

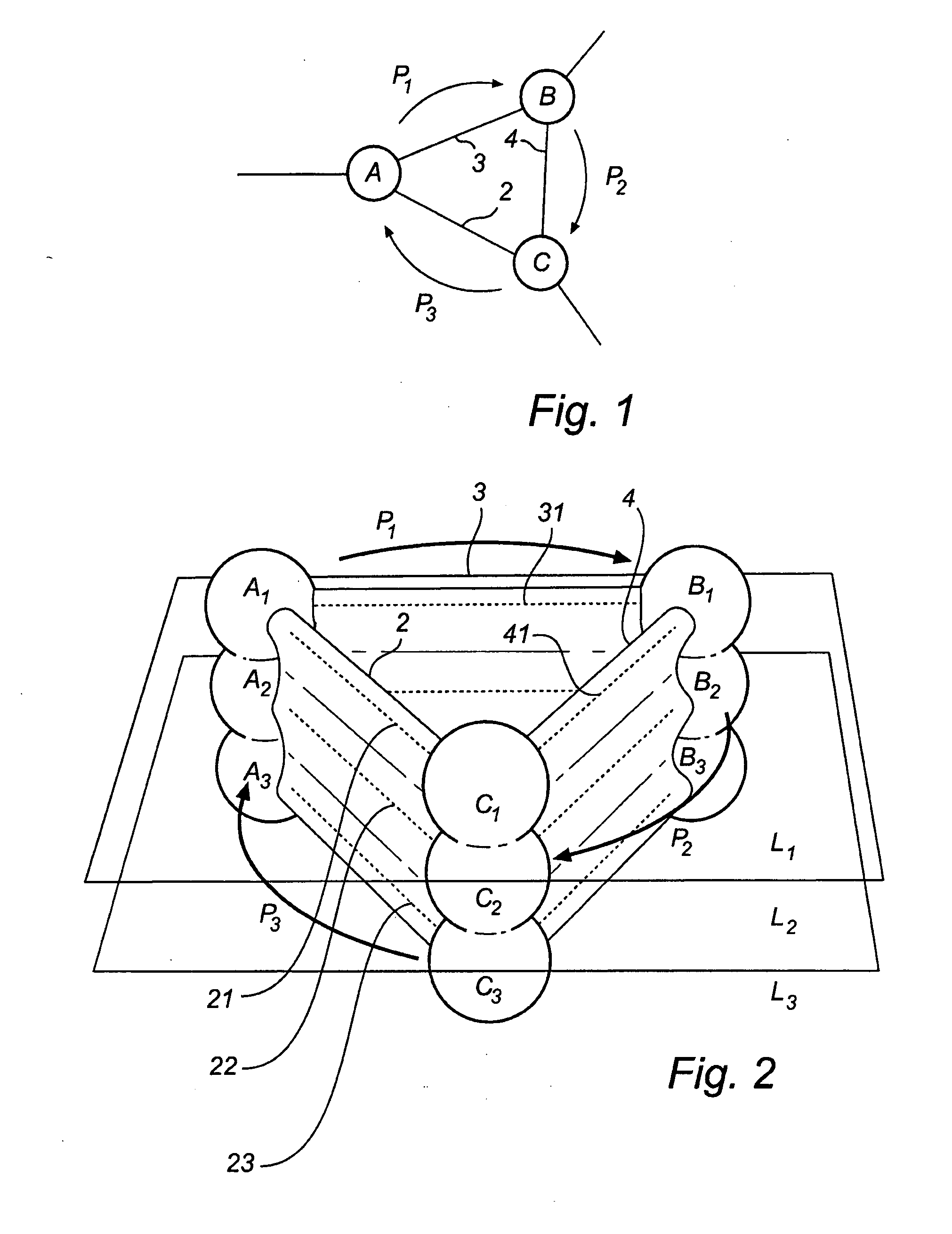

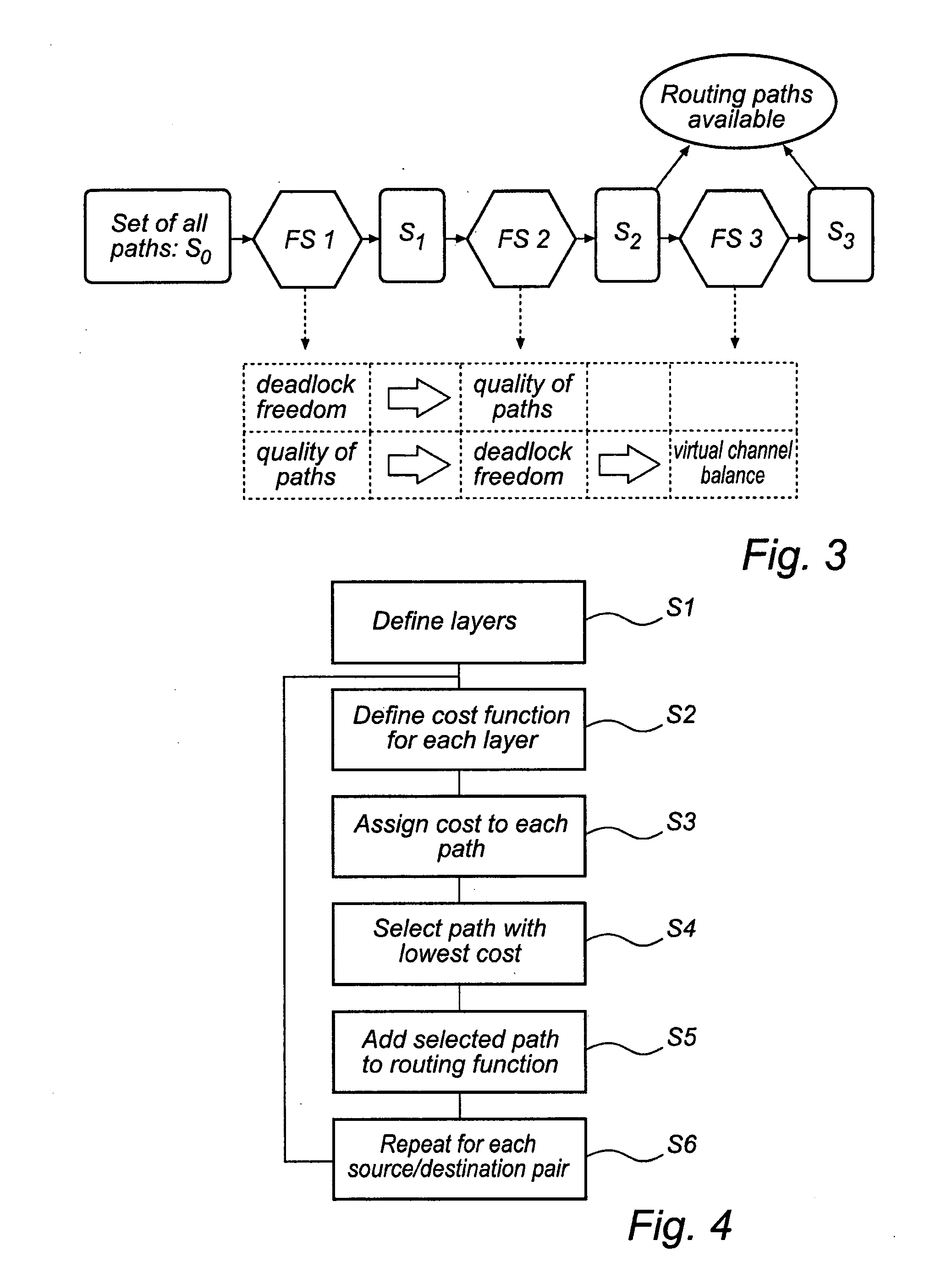

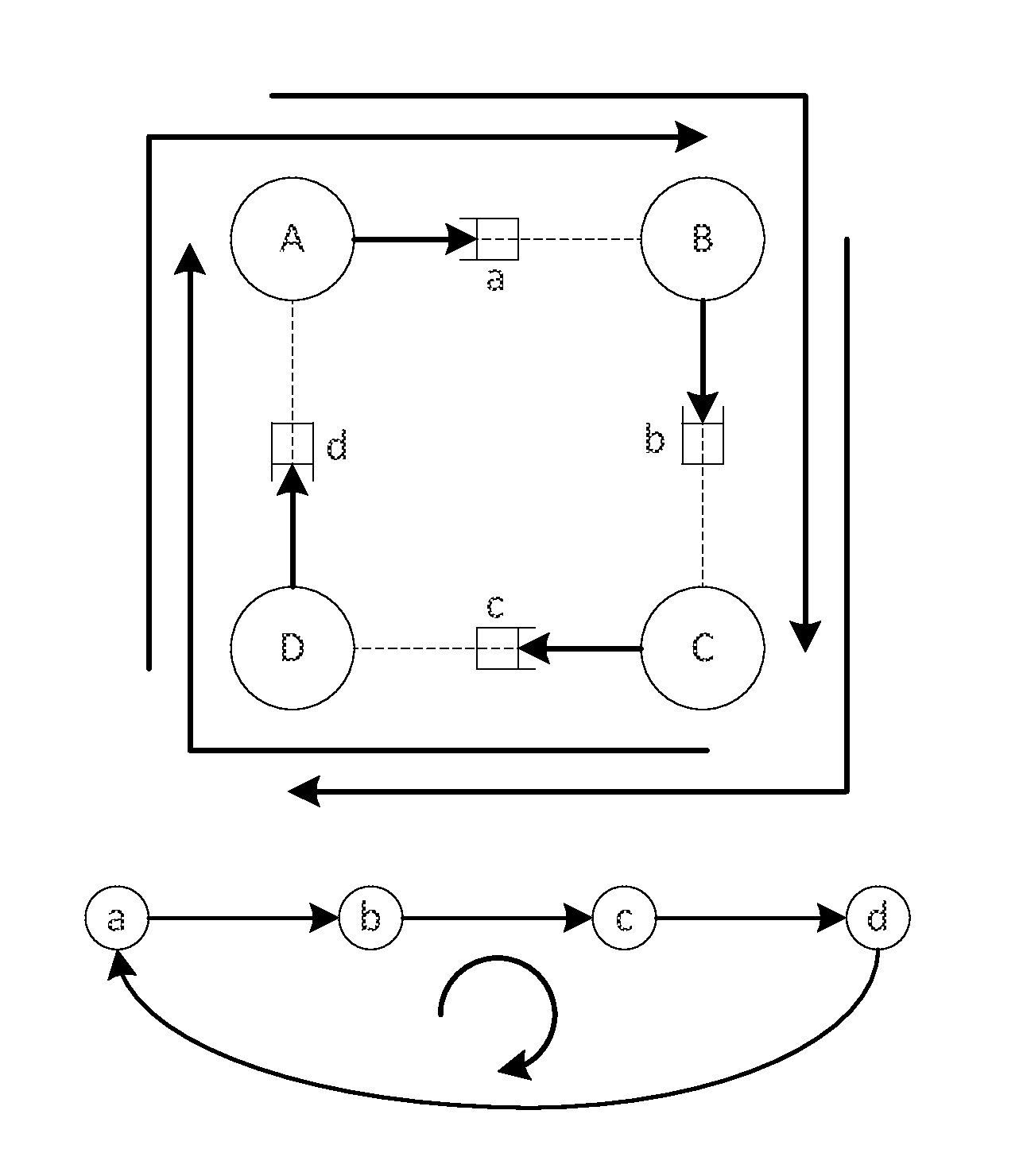

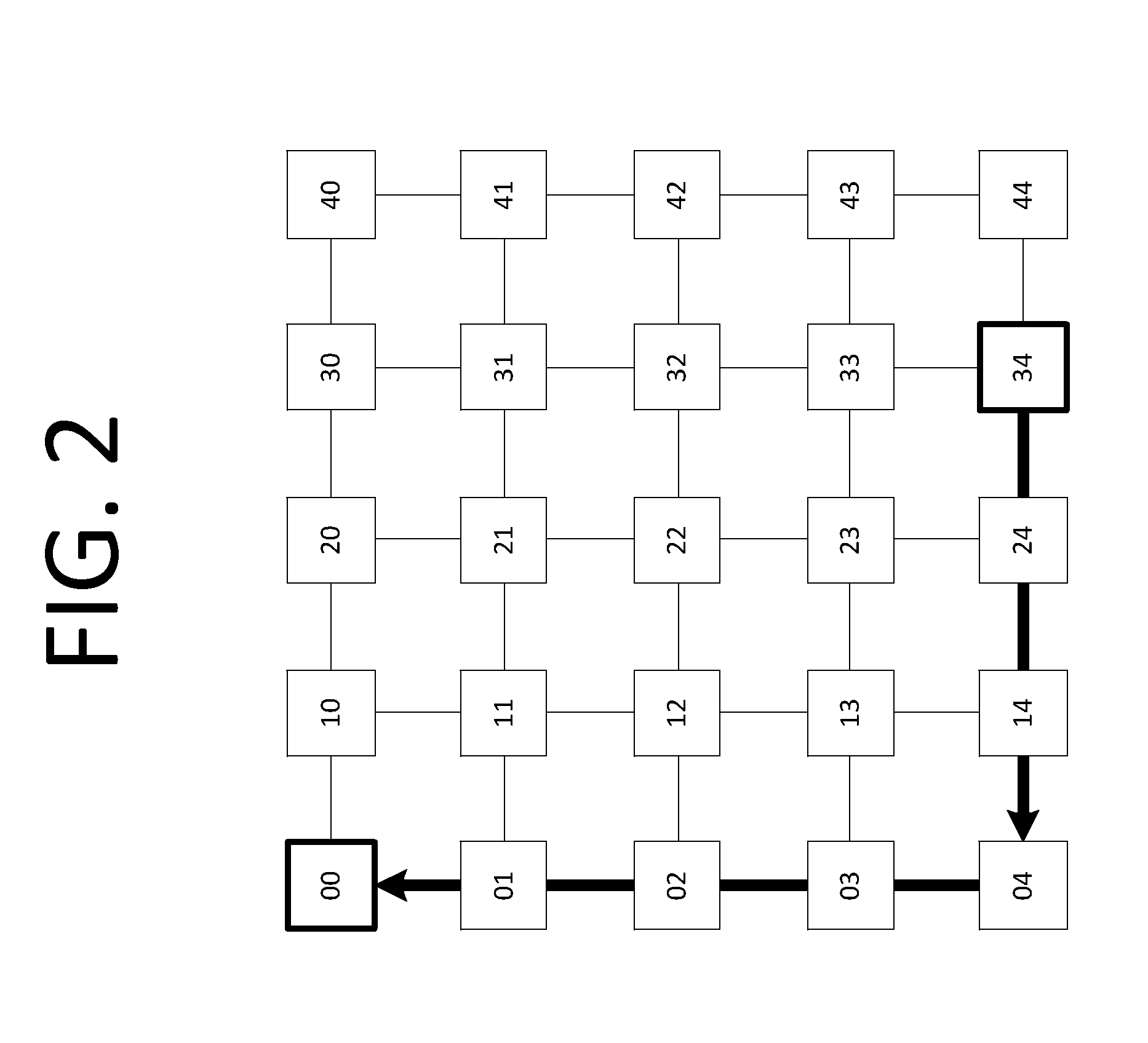

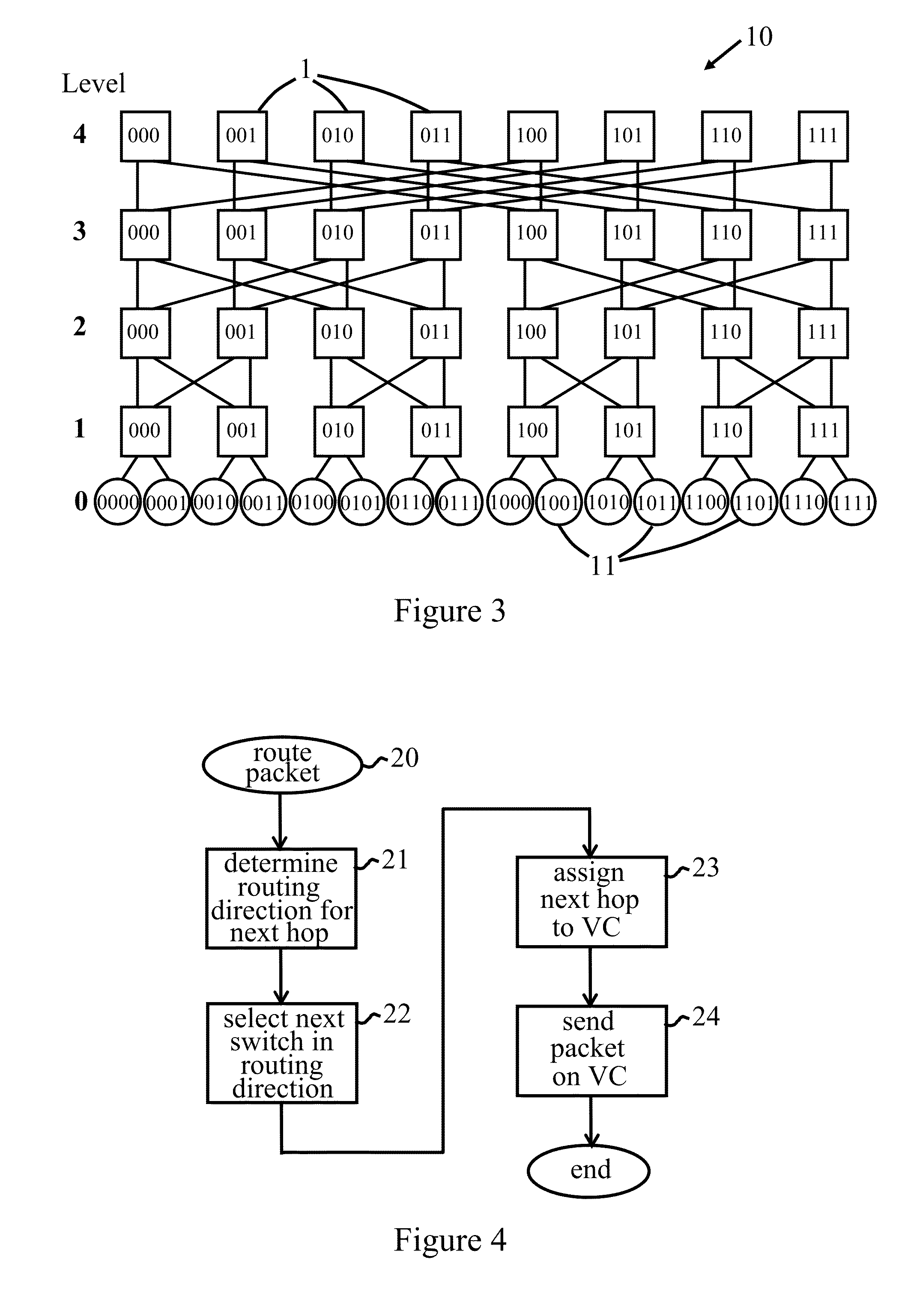

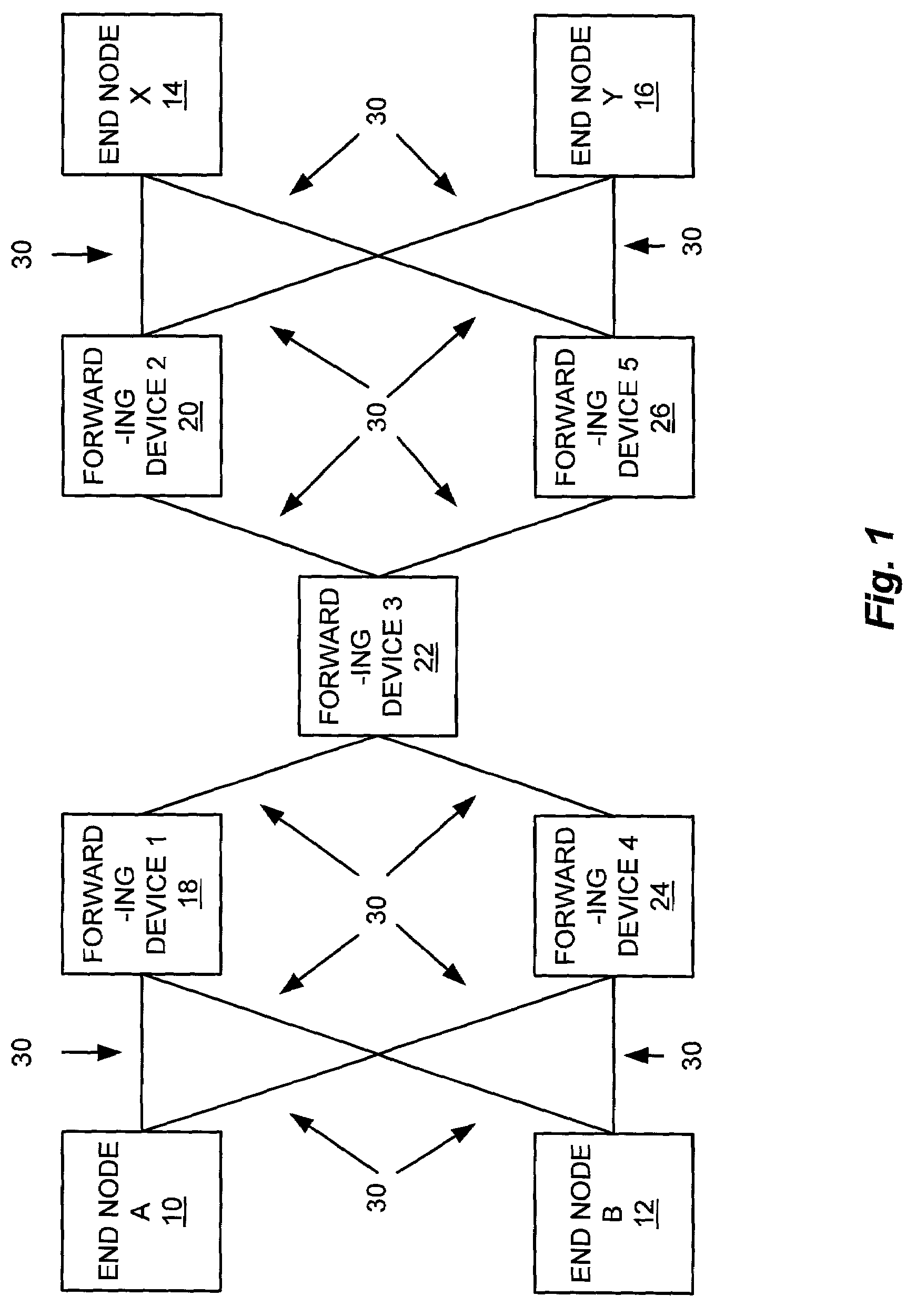

Deadlock free network routing

InactiveUS20080285458A1Extended routeOvercome problemsError preventionTransmission systemsDeadlock freeNetwork routing

A method for establishing a routing scheme defining a path between any given pair of source node and destination node in a network including a plurality of nodes connected by links. The method comprises defining a plurality of virtual network layers, each virtual network layer comprising addresses for identifying each node, and channels for communicating between said nodes using said addresses, and defining a routing function for each layer, the routing scheme comprising all routing functions, each routing function comprising a set of source node / destination node pairs and a path connecting each pair. The routing function is defined by defining a cost function for each layer, said cost function being adapted to assign a high cost to any path creating a deadlock, using said cost function to assign a cost to each path in each layer connecting the source node / destination node pair, selecting the path with the lowest cost, and assigning the pair of source node / destination node and its selected path to the routing function of the layer that contains said selected path.According to this aspect of the invention, the number of virtual layers is defined initially, and the routing scheme is then generated using this number of layers. This provides complete control over the number of layers, so that it is possible to adjust the number of virtual layers to the capacity of the network.

Owner:SIMULA INNOVATIONS

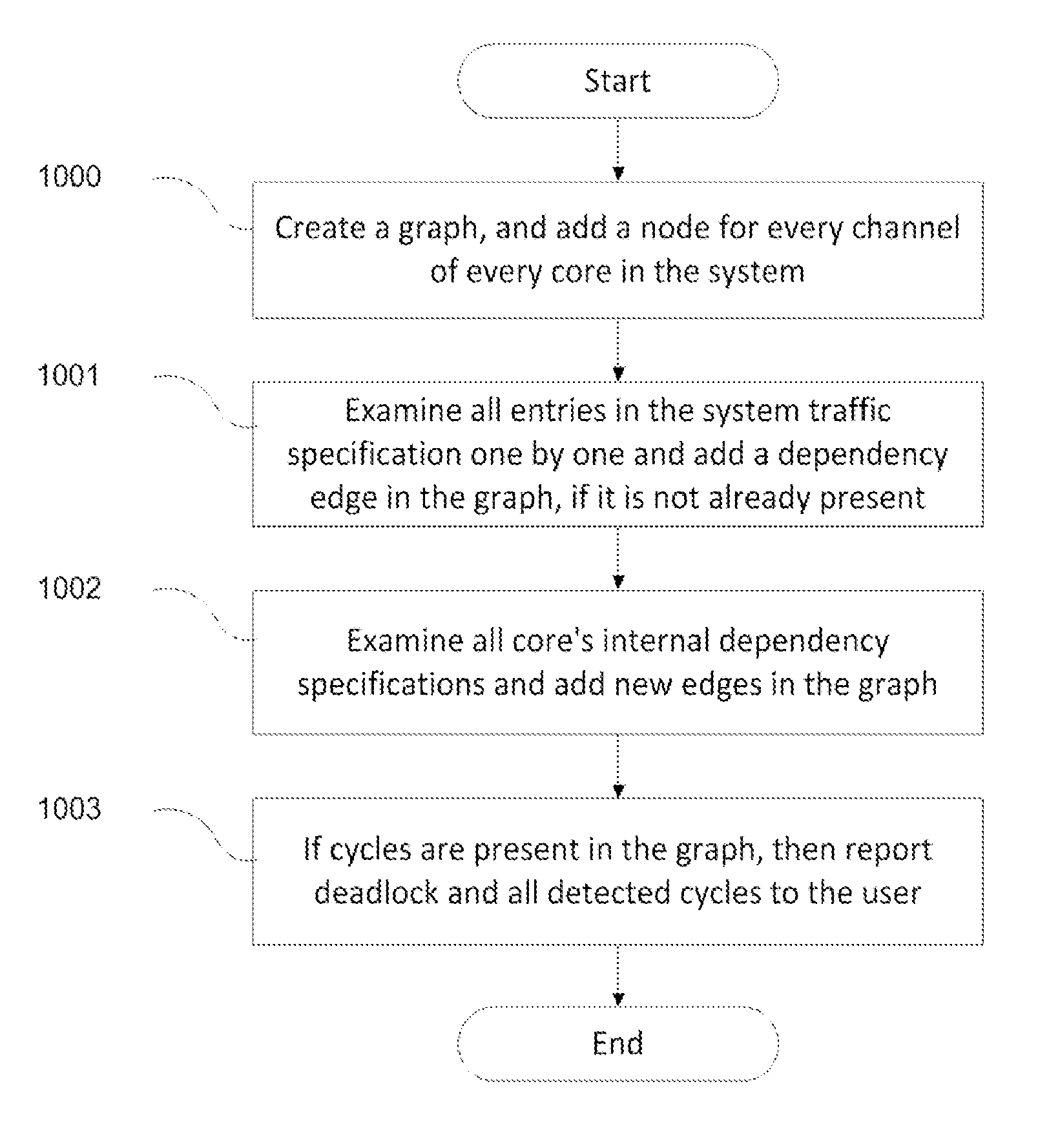

Automatic construction of deadlock free interconnects

Systems and methods for automatically building a deadlock free inter-communication network in a multi-core system are described. The example embodiments described herein involve deadlock detection during the mapping of user specified communication pattern amongst blocks of the system. Detected deadlocks are then avoided by re-allocation of channel resources. An example embodiment of the deadlock avoidance scheme is presented on Network-on-chip interconnects for large scale multi-core system-on-chips.

Owner:INTEL CORP

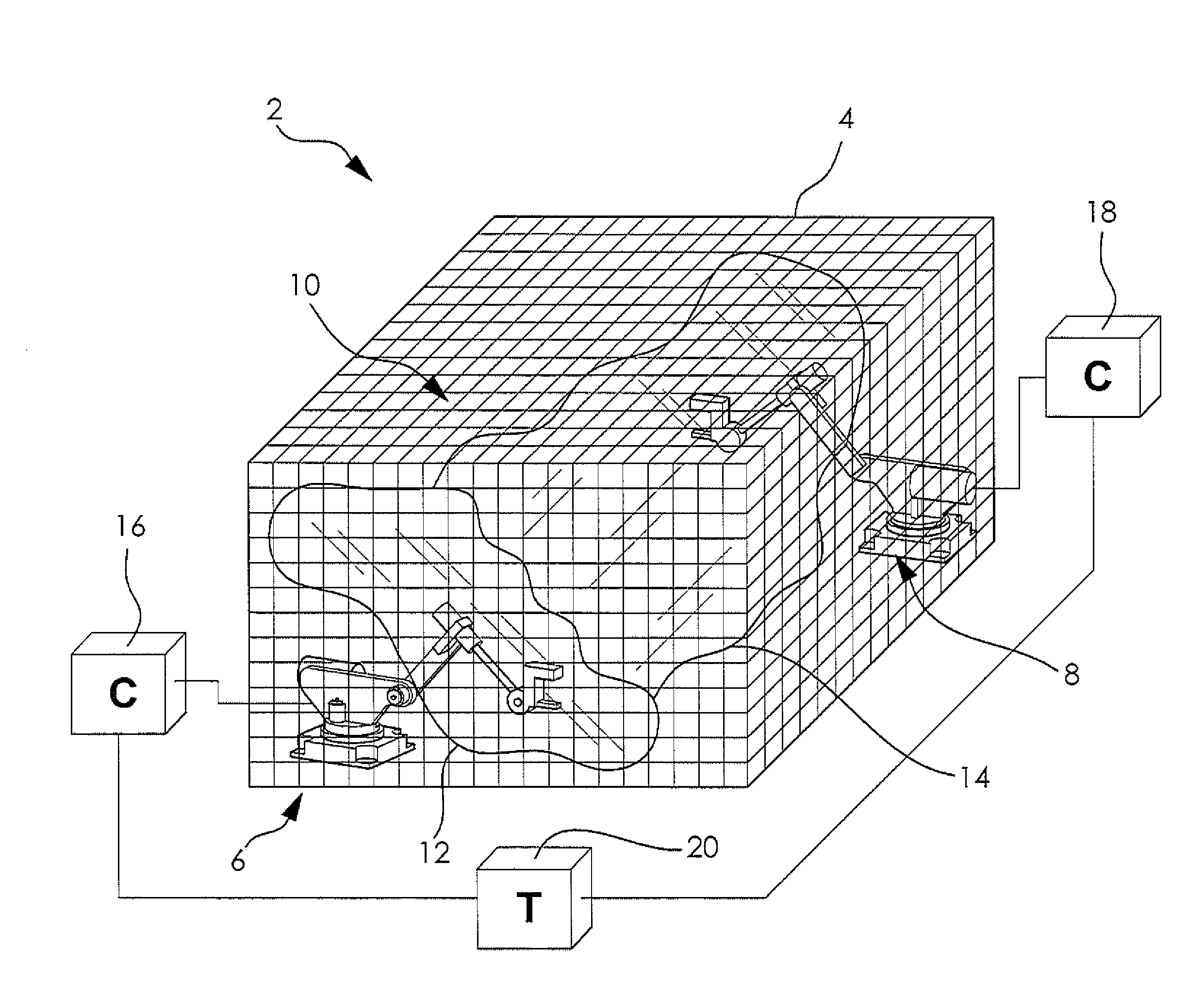

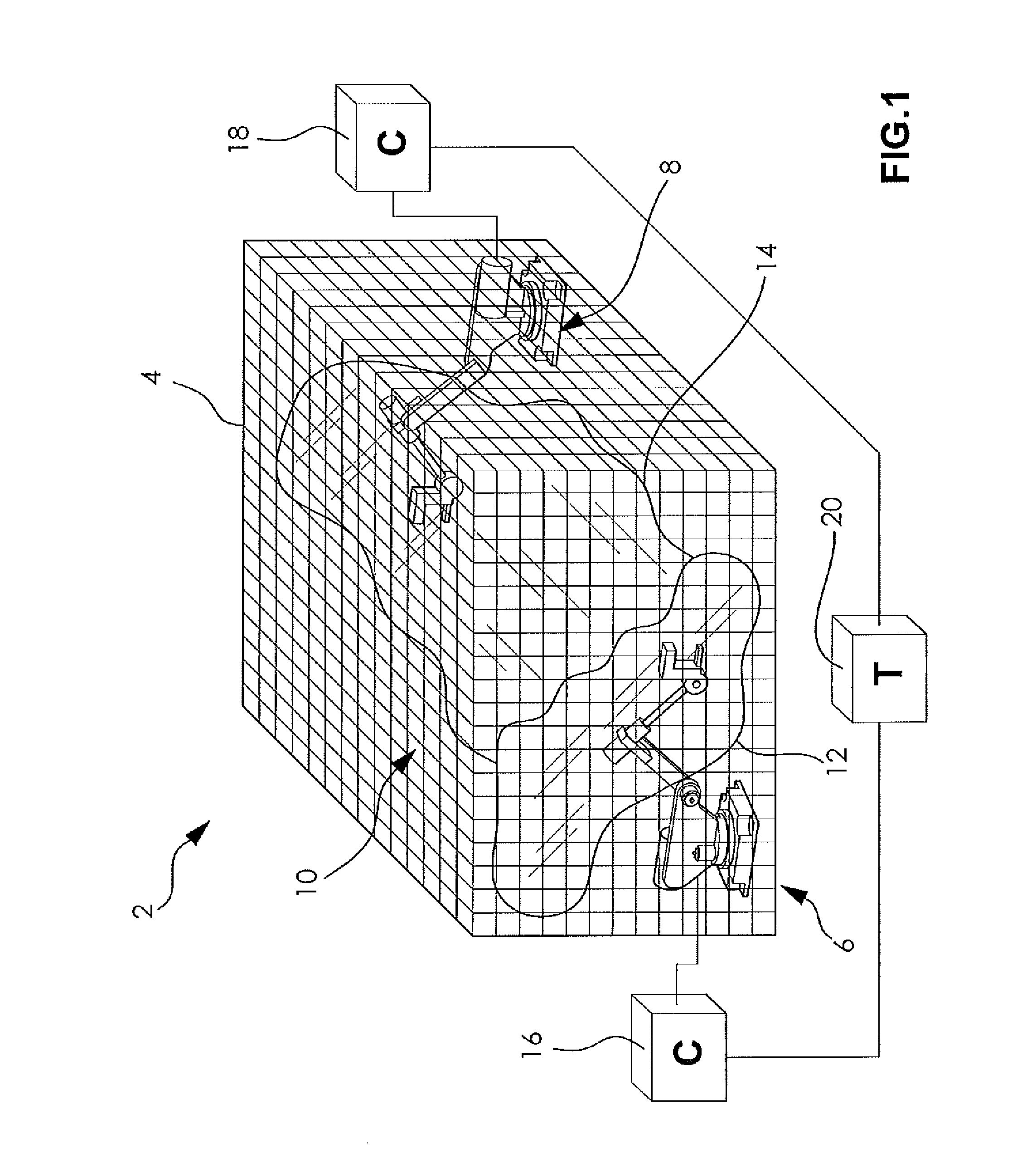

Method and system for automatically preventing deadlock in multi-robot systems

ActiveUS20120215351A1Avoid deadlockAvoid adjustmentProgramme-controlled manipulatorComputer controlWorkcellMultirobot systems

A system and method for controlling avoiding collisions and deadlocks in a workcell containing multiple robots automatically determines the potential deadlock conditions and identifies a way to avoid these conditions. Deadlock conditions are eliminated by determining the deadlock-free motion statements prior to execution of the motions that have potential deadlock conditions. This determination of deadlock-free motion statements can be done offline, outside normal execution, or it can be done during normal production execution. If there is sufficient CPU processing time available, the determination during normal production execution provides the most flexibility to respond to dynamic conditions such as changes in I / O timing or the timing of external events or sequences. For minimal CPU impact the determination is done offline where many permutations of programming sequences can be analyzed and an optimized sequence of execution may be found.

Owner:FANUC ROBOTICS NORTH AMERICA

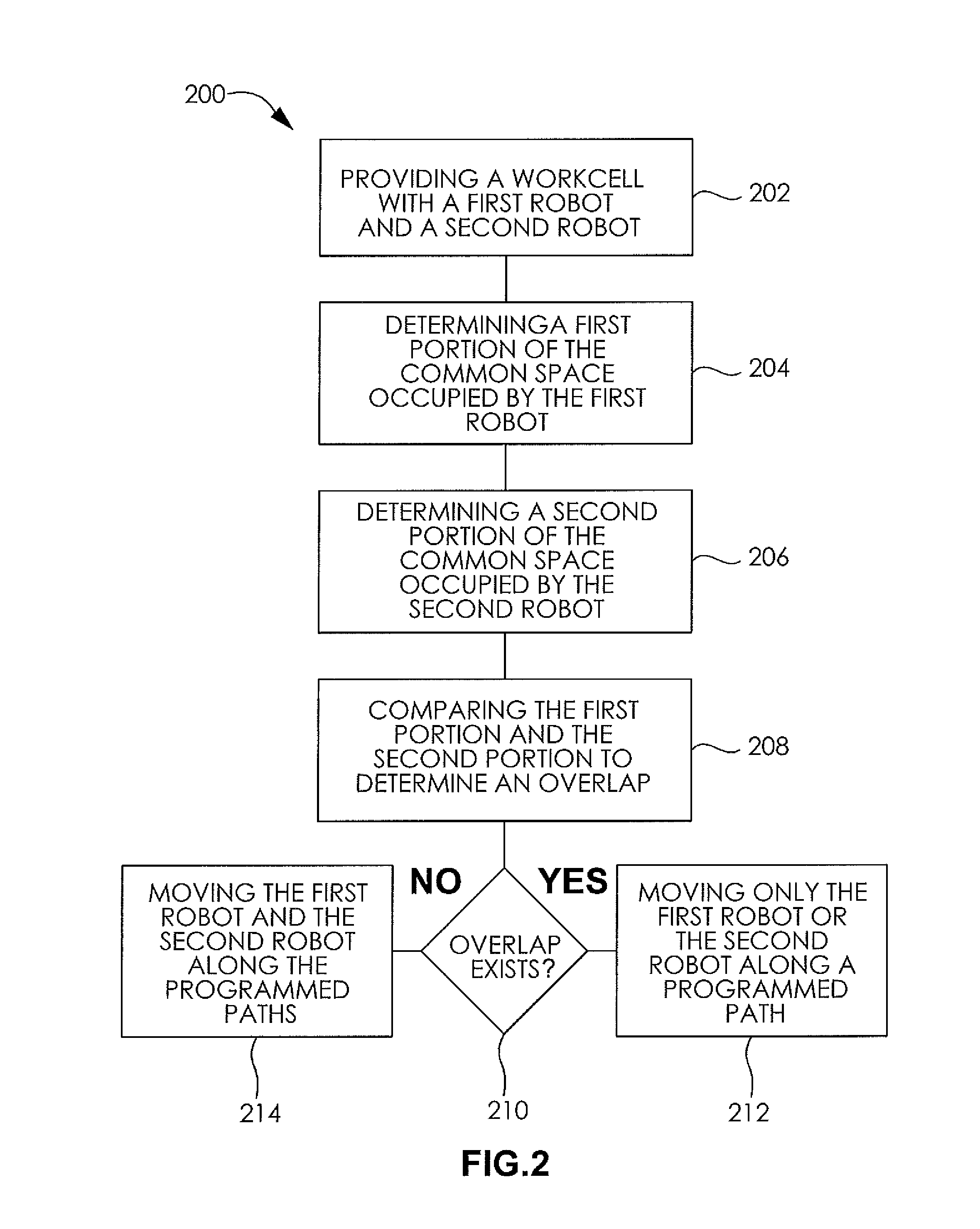

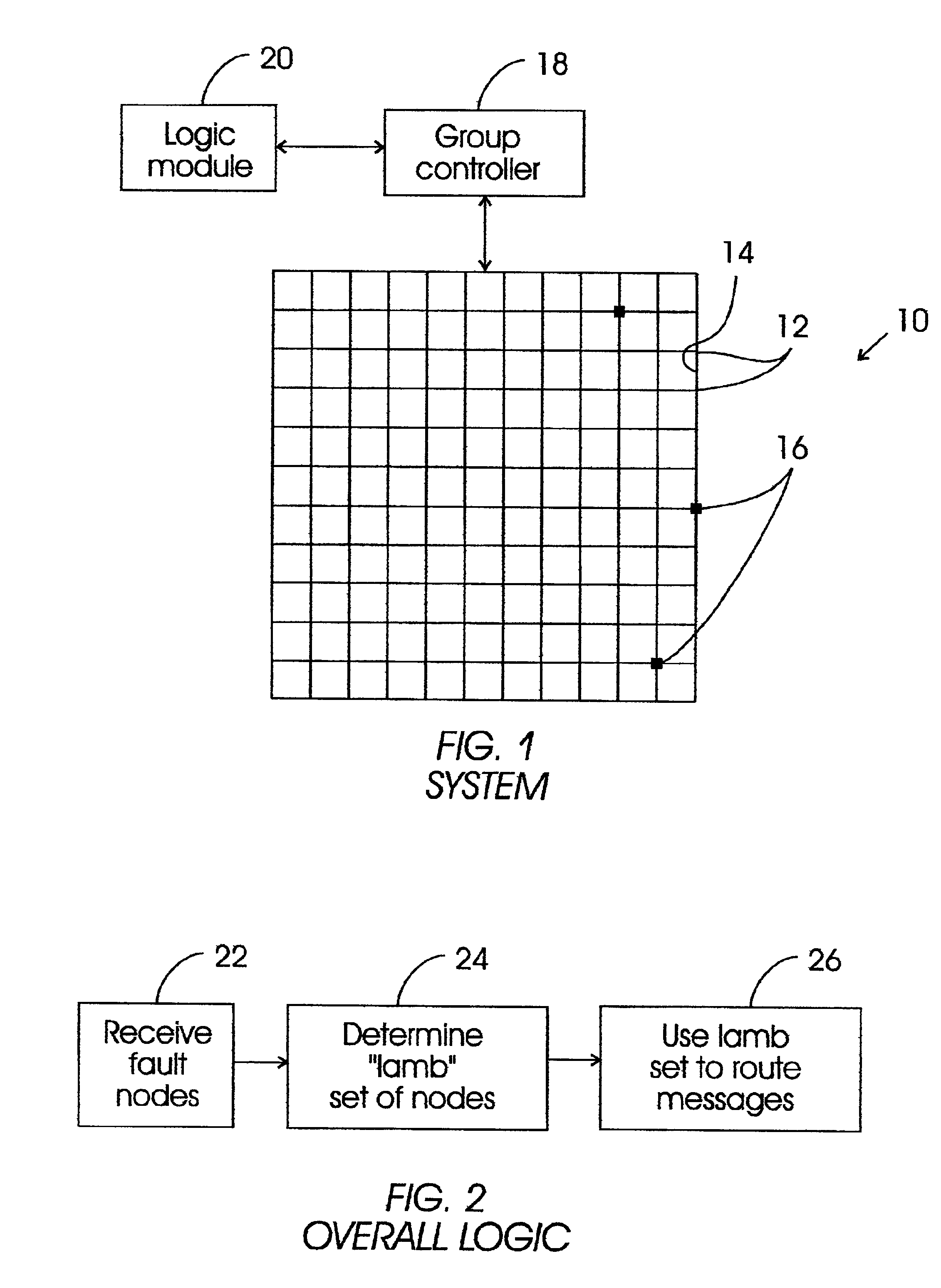

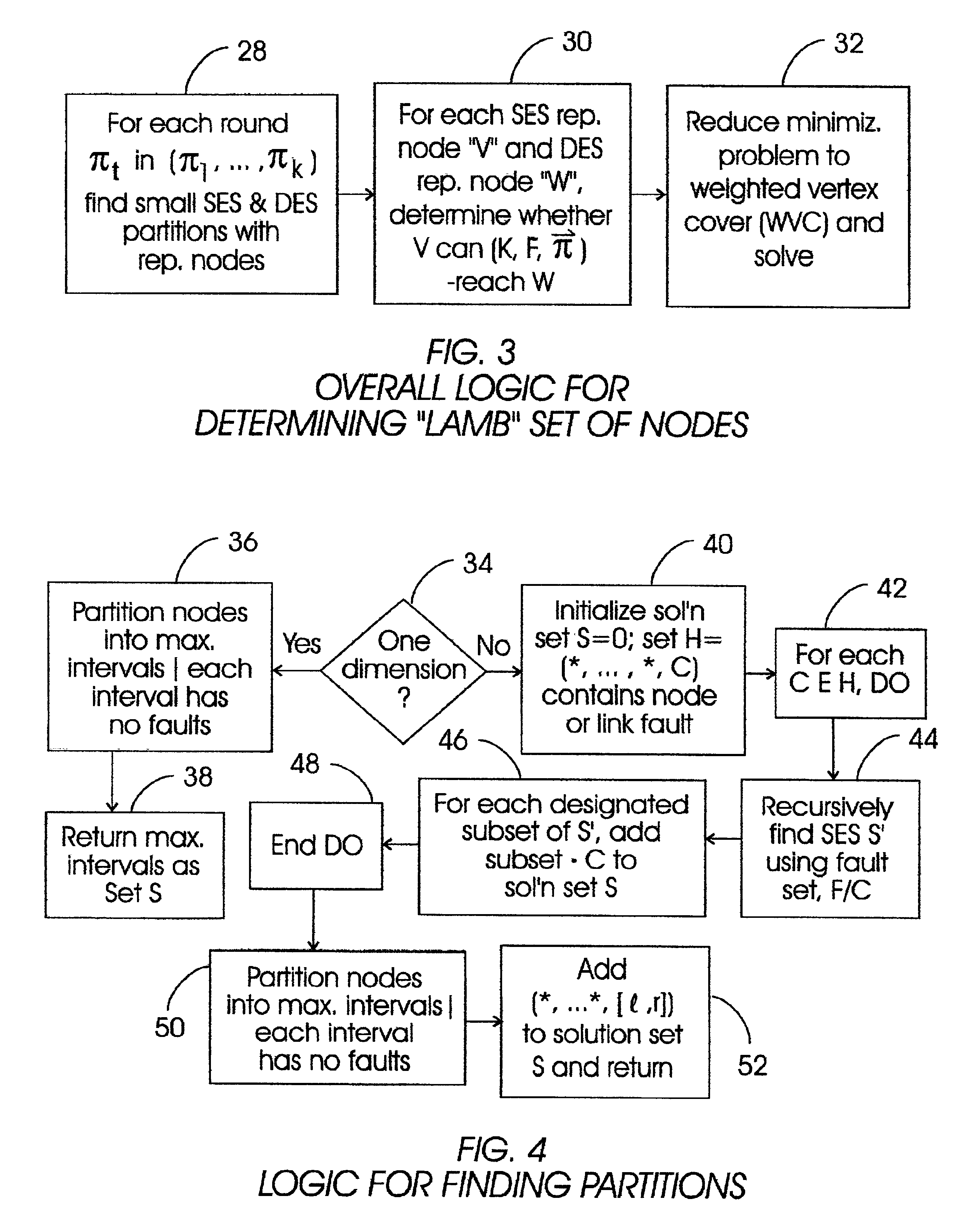

System and method for fault tolerance in multi-node system

InactiveUS6918063B2Facilitating fault toleranceMinimize the numberError preventionFrequency-division multiplex detailsFault toleranceMessage routing

A method and system for promoting fault tolerance in a multi-node computing system that provides deadlock-free message routing in the presence of node and / or link faults using only two rounds and, thus, requiring only two virtual channels to ensure deadlock freedom. A lamb set of nodes for use in message routing is introduced, with each node in the lamb set being used only as points along message routes, and not for sending or receiving messages.

Owner:IBM CORP

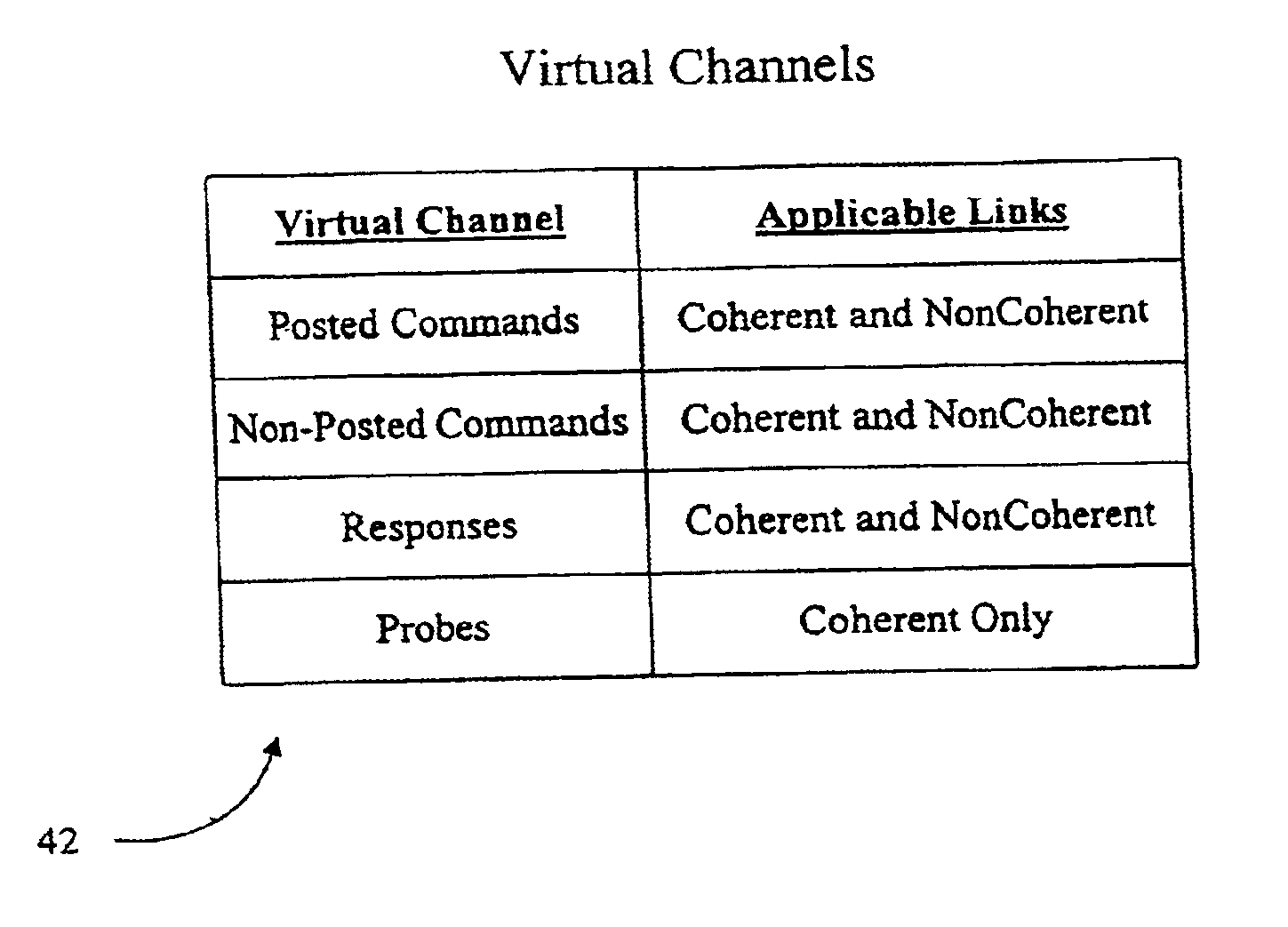

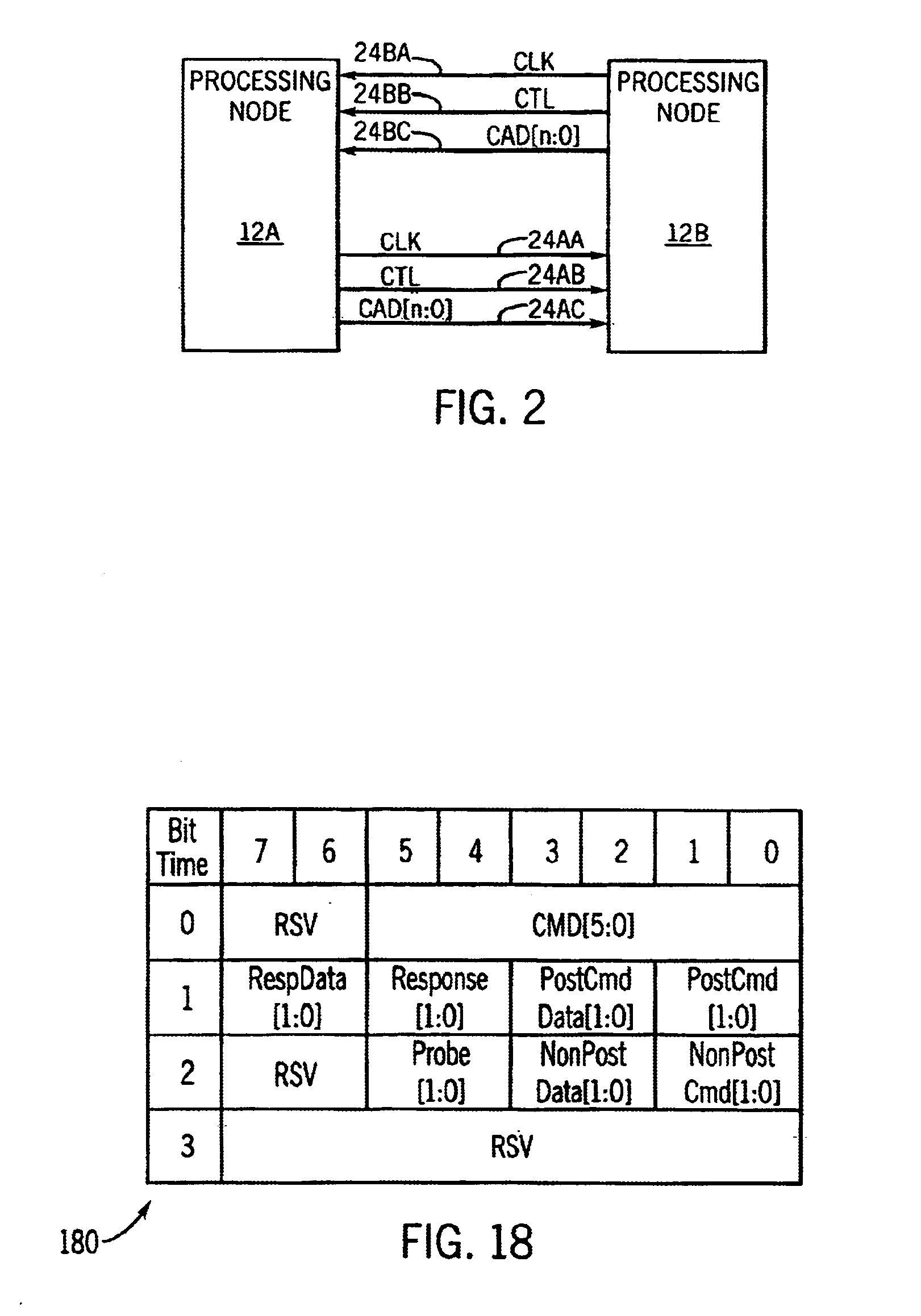

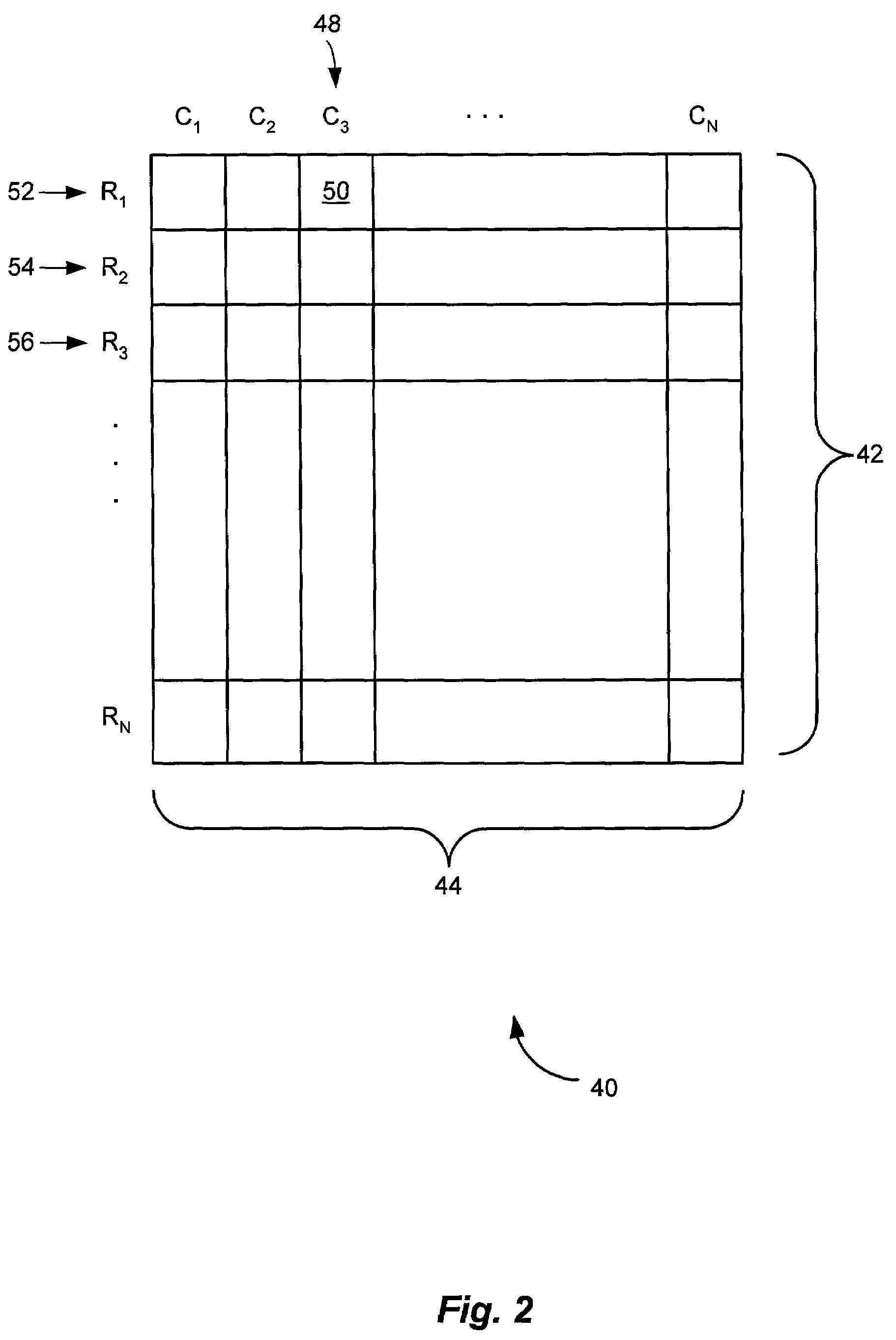

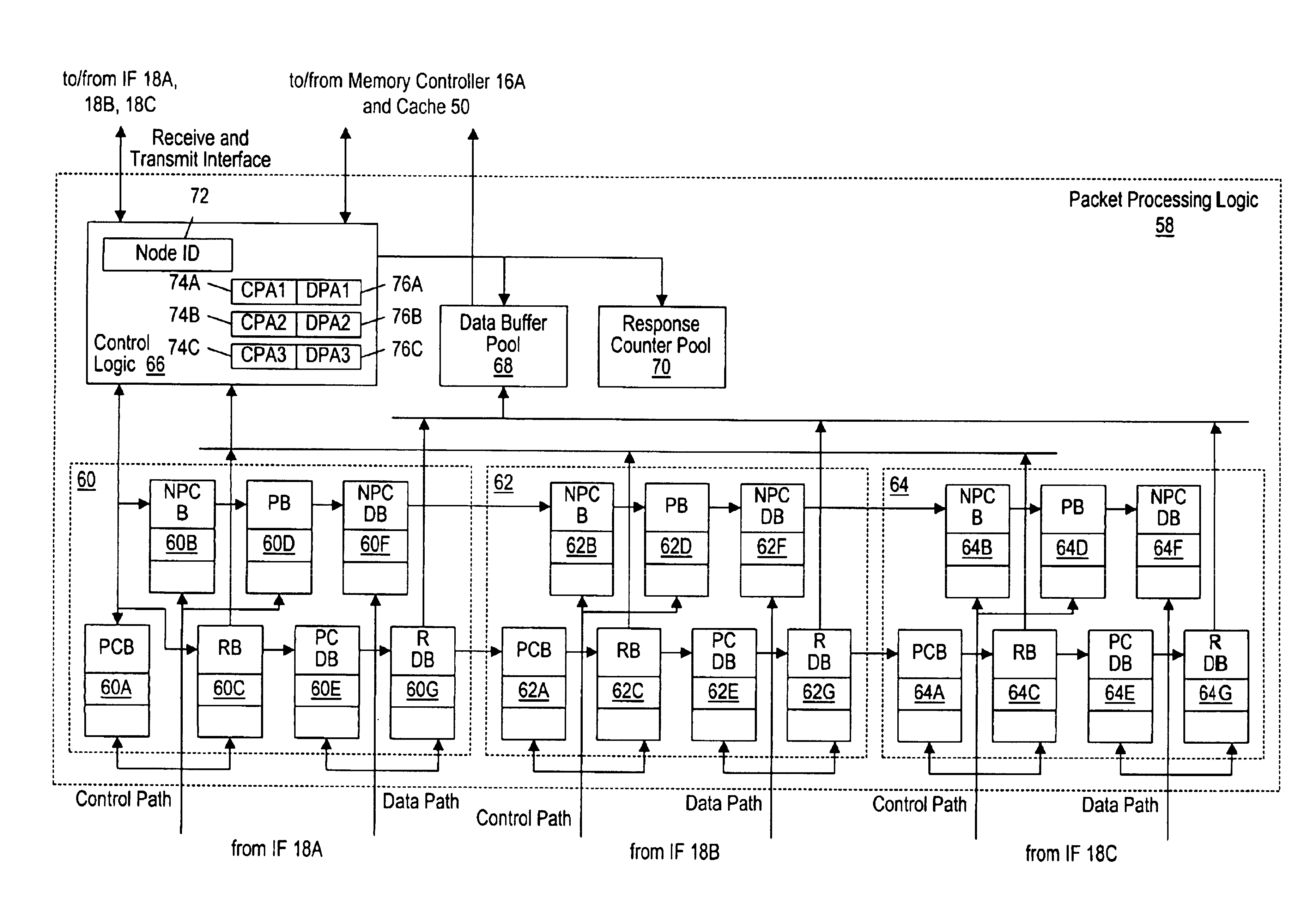

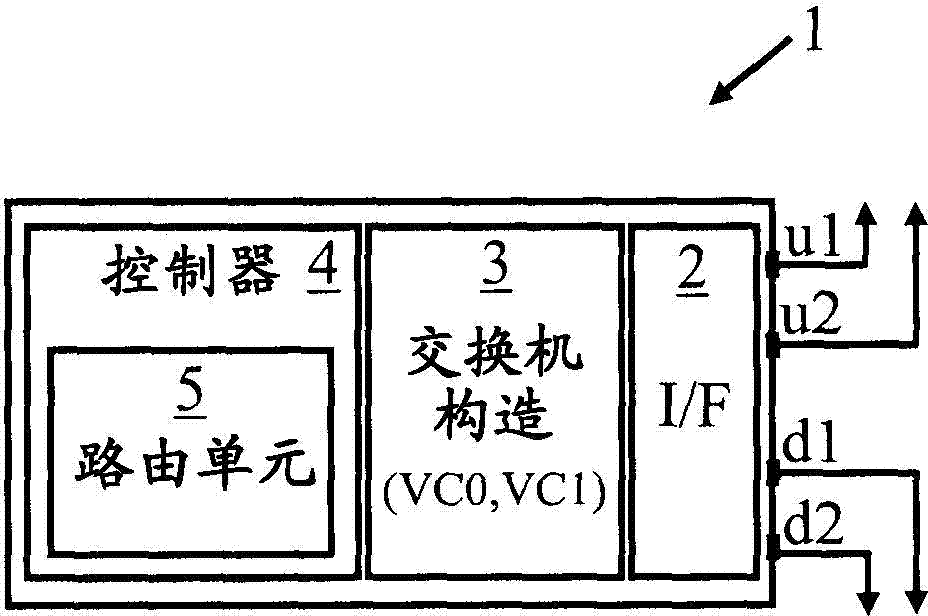

Virtual channels and corresponding buffer allocations for deadlock-free computer system operation

InactiveUS6938094B1Deadlock-free operationEffective spaceMemory adressing/allocation/relocationData switching by path configurationDistribution controlComputerized system

A computer system employs virtual channels and allocates different resources to the virtual channels. Packets which do not have logical / protocol-related conflicts are grouped into a virtual channel. Accordingly, logical conflicts occur between packets in separate virtual channels. The packets within a virtual channel may share resources (and hence experience resource conflicts), but the packets within different virtual channels may not share resources. Since packets which may experience resource conflicts do not experience logical conflicts, and since packets which may experience logical conflicts do not experience resource conflicts, deadlock-free operation may be achieved. Additionally, each virtual channel may be assigned control packet buffers and data packet buffers. Control packets may be substantially smaller in size, and may occur more frequently than data packets. By providing separate buffers, buffer space may be used efficiently. If a control packet which does not specify a data packet is received, no data packet buffer space is allocated. If a control packet which does specify a data packet is received, both control packet buffer space and data packet buffer space is allocated.

Owner:ADVANCED MICRO DEVICES INC

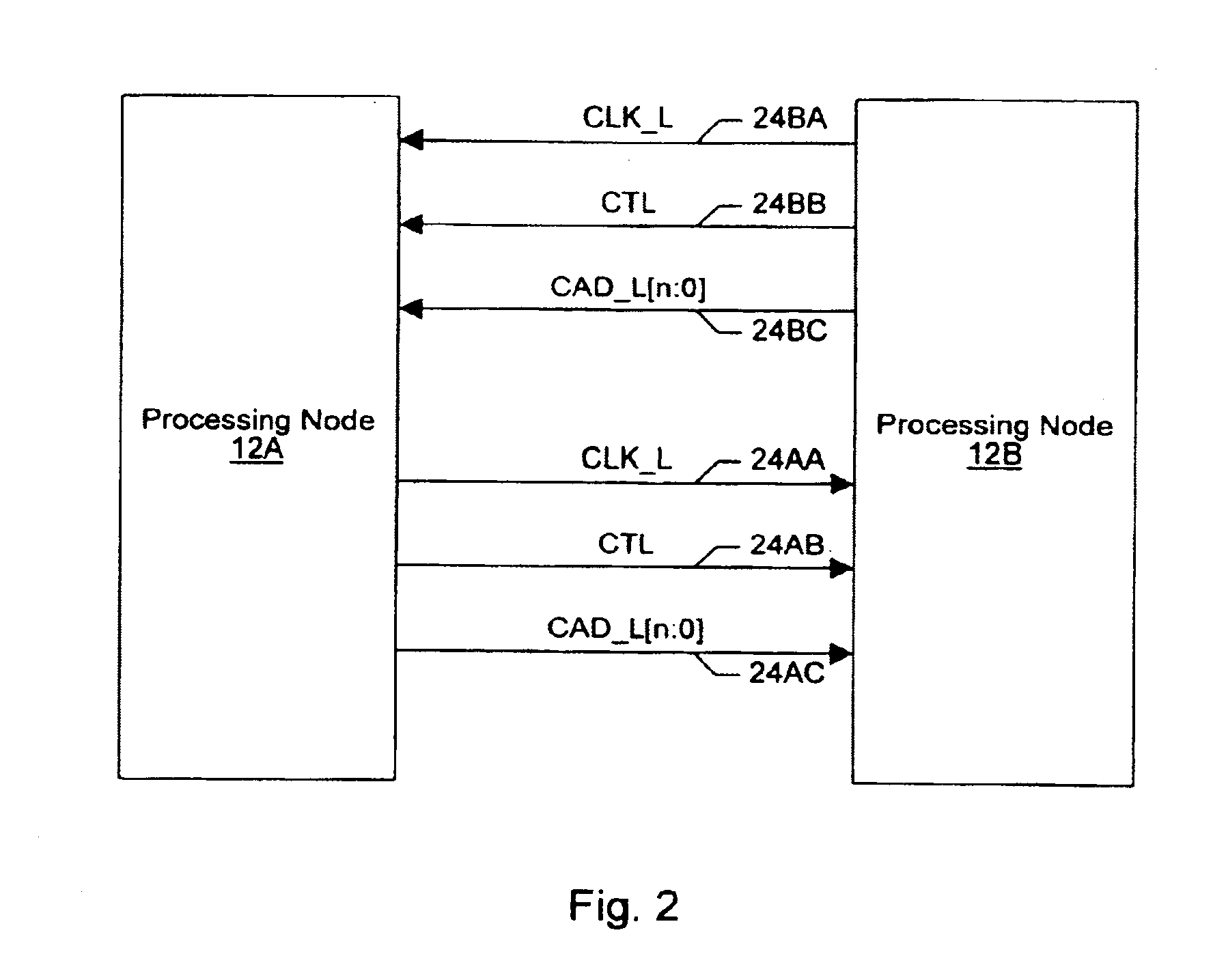

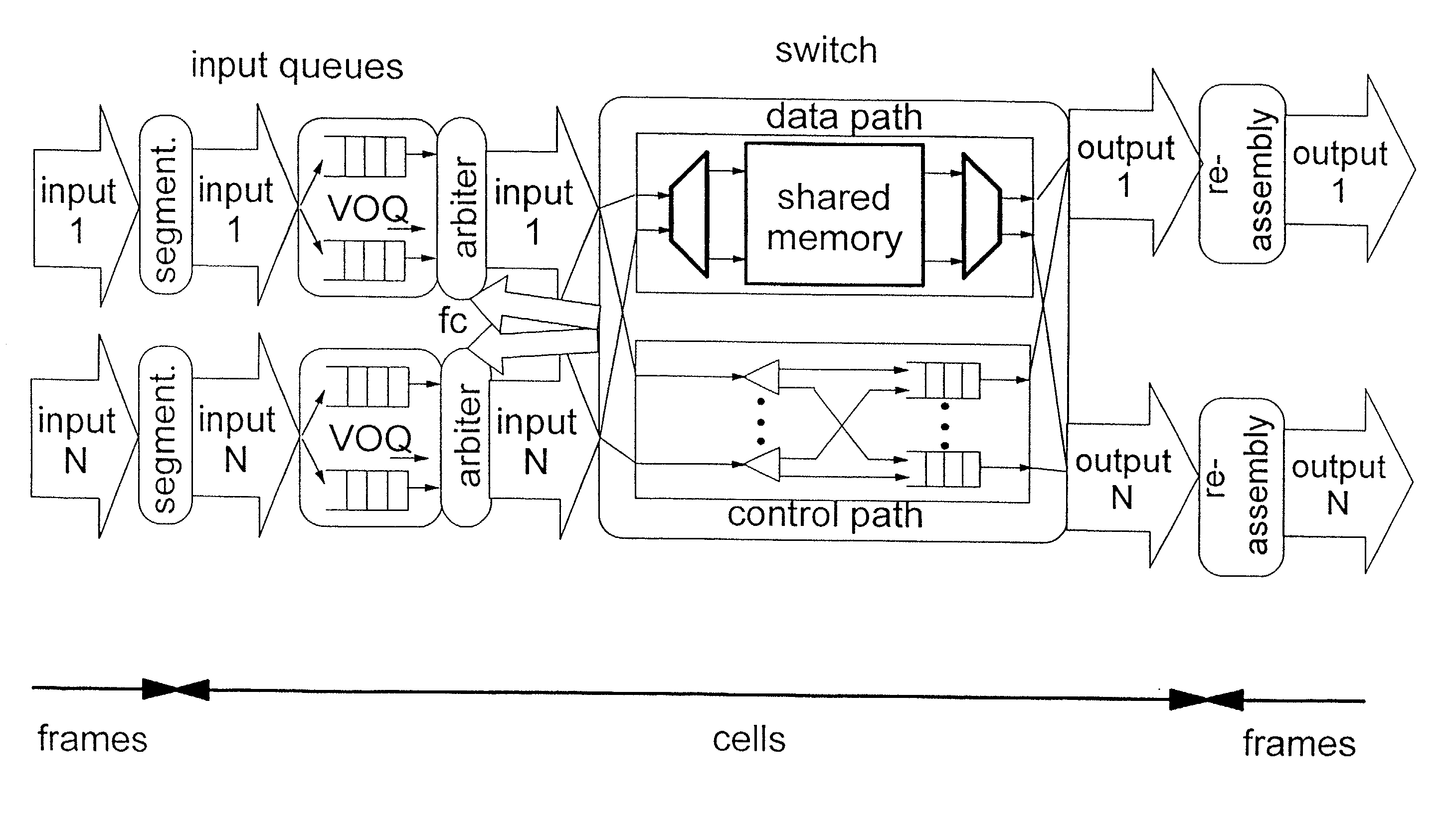

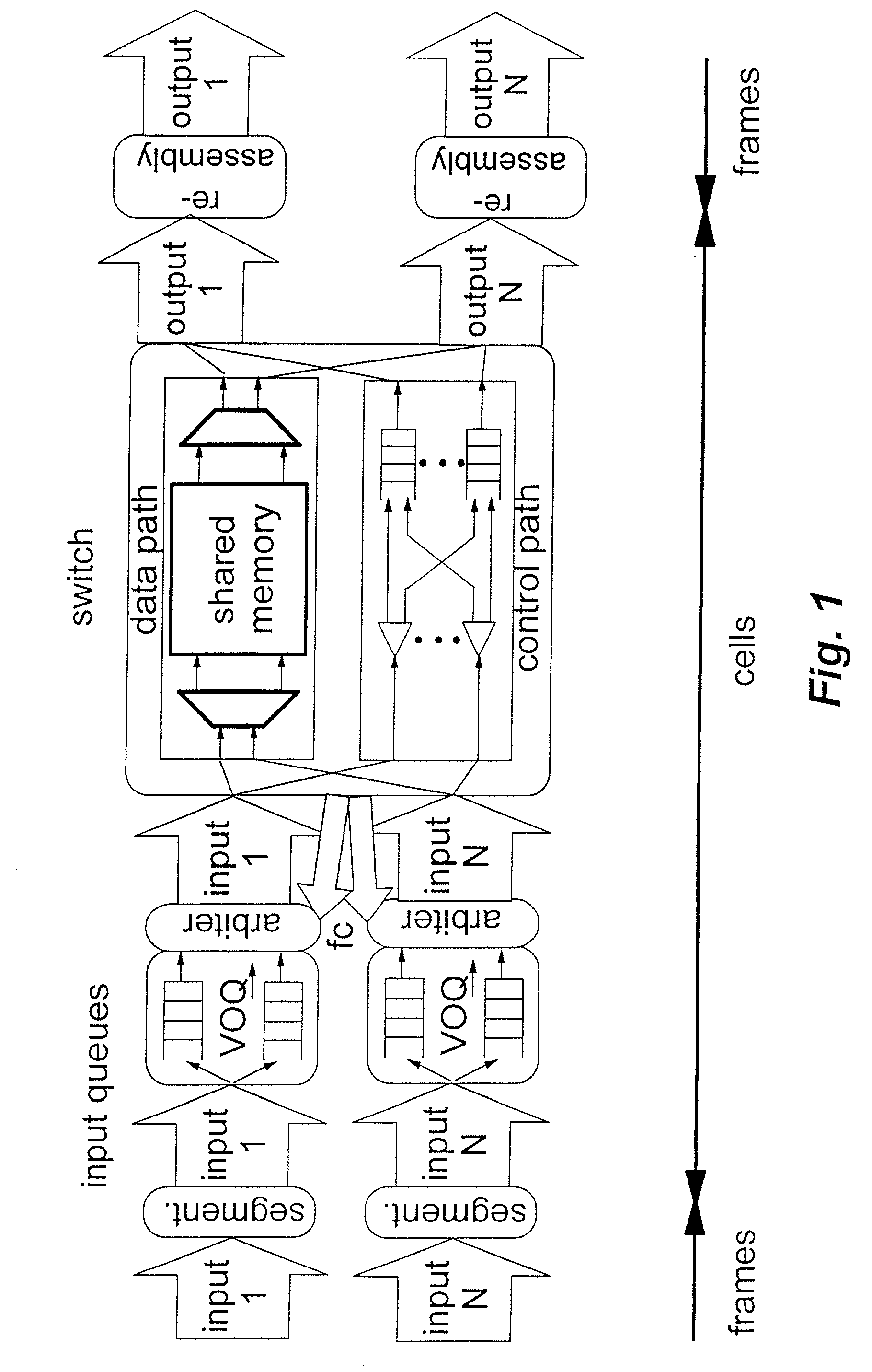

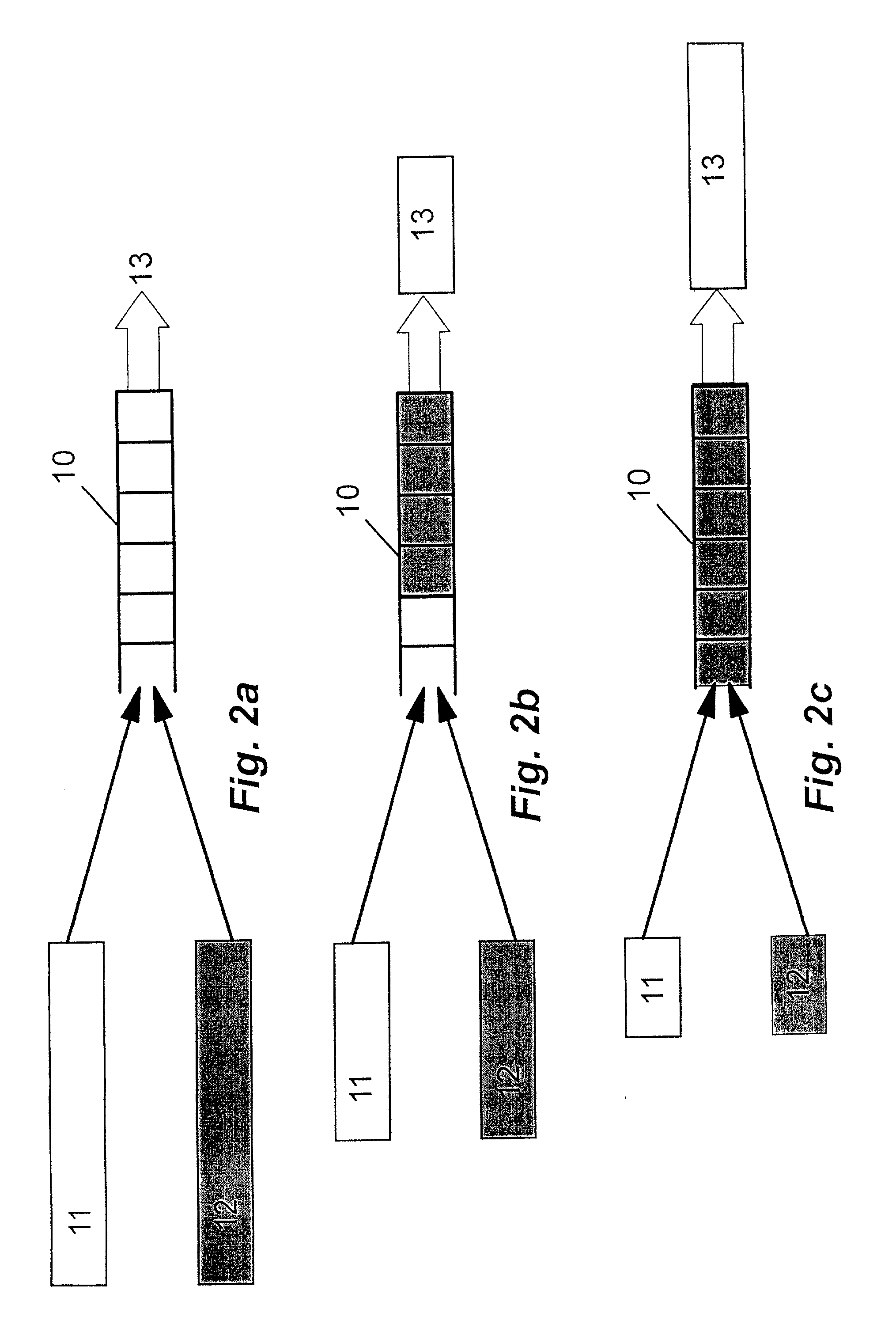

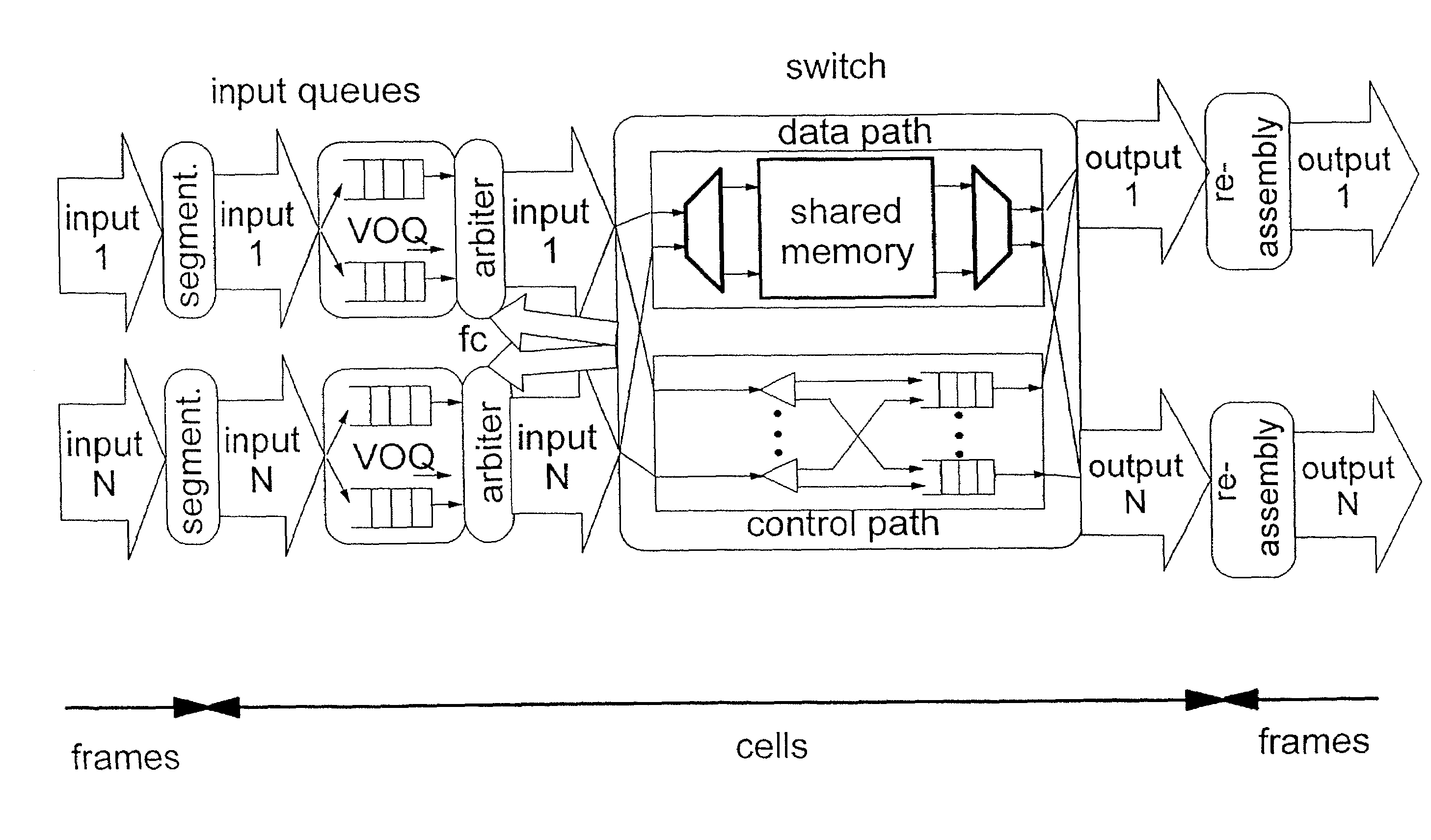

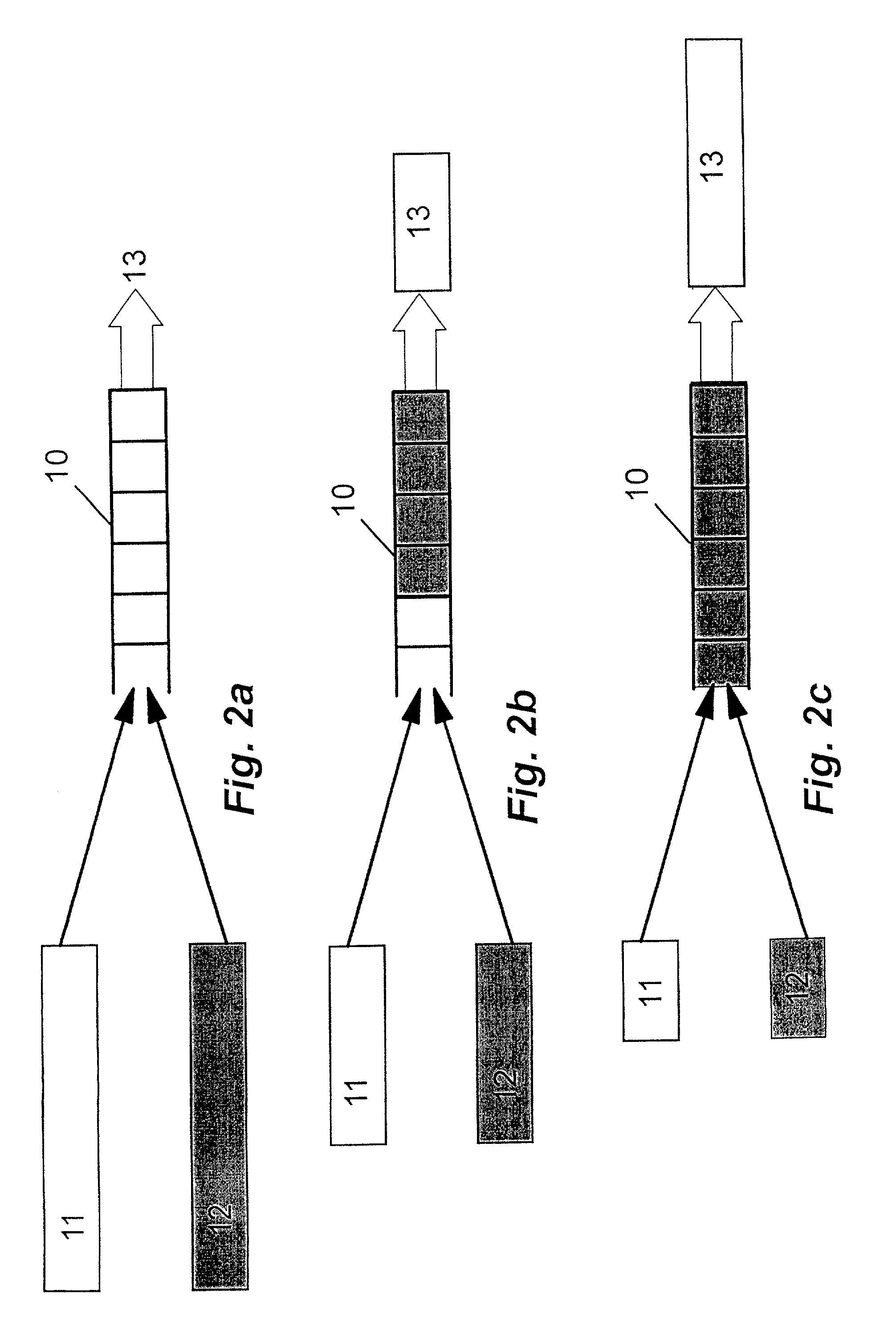

Method and structure for variable-length frame support in a shared memory switch

InactiveUS20020196778A1Cost efficientTime-division multiplexData switching by path configurationContinuationElectronic network

The present invention relates to switching in electronic networks. Many data transmission protocols and technologies used in such networks, such as TCP / IP and Ethernet, use variable-length packets for transmission. Often however, the nodes that make up these networks typically contain high-speed cell switches that only support fixed-size data units. To support variable-length packets in such a fixed-size cell switch non-interleaving switching and transmission must be offered. The present invention provides such a solution in essence by segmenting a variable-length frame into a plurality of fixed-length cells including a start-of-frame cell, one or more continuation cell(s), and an end-of-frame cell and routes said fixed-length cells through said switch, thereby providing, at an output of said switch, subsequent and deadlock-free transmission of consecutive cells of a certain frame, and block any cell of a different frame from interleaving. This leads to better average delay characteristics and removes the need for packet reassembly.

Owner:IBM CORP

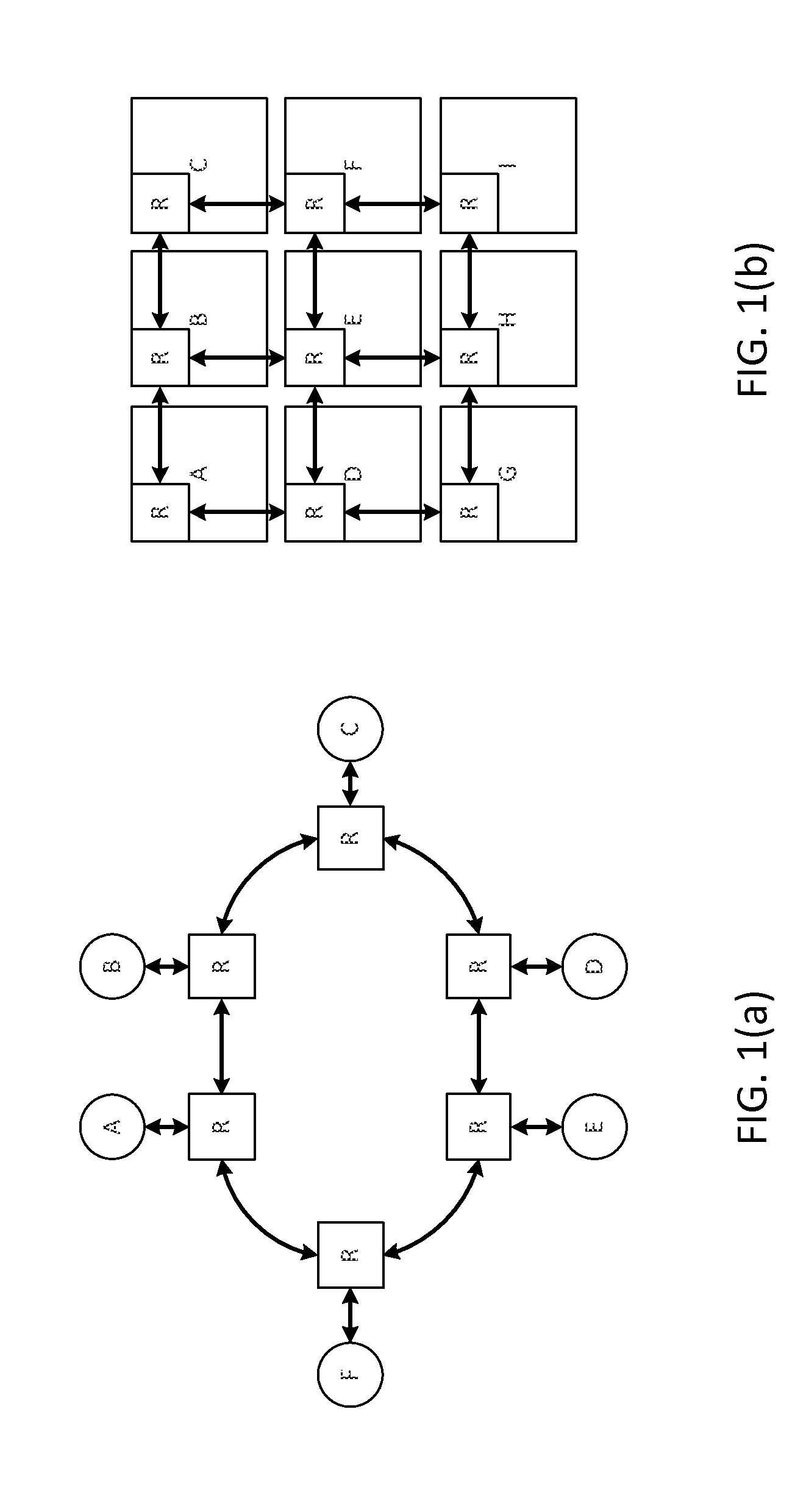

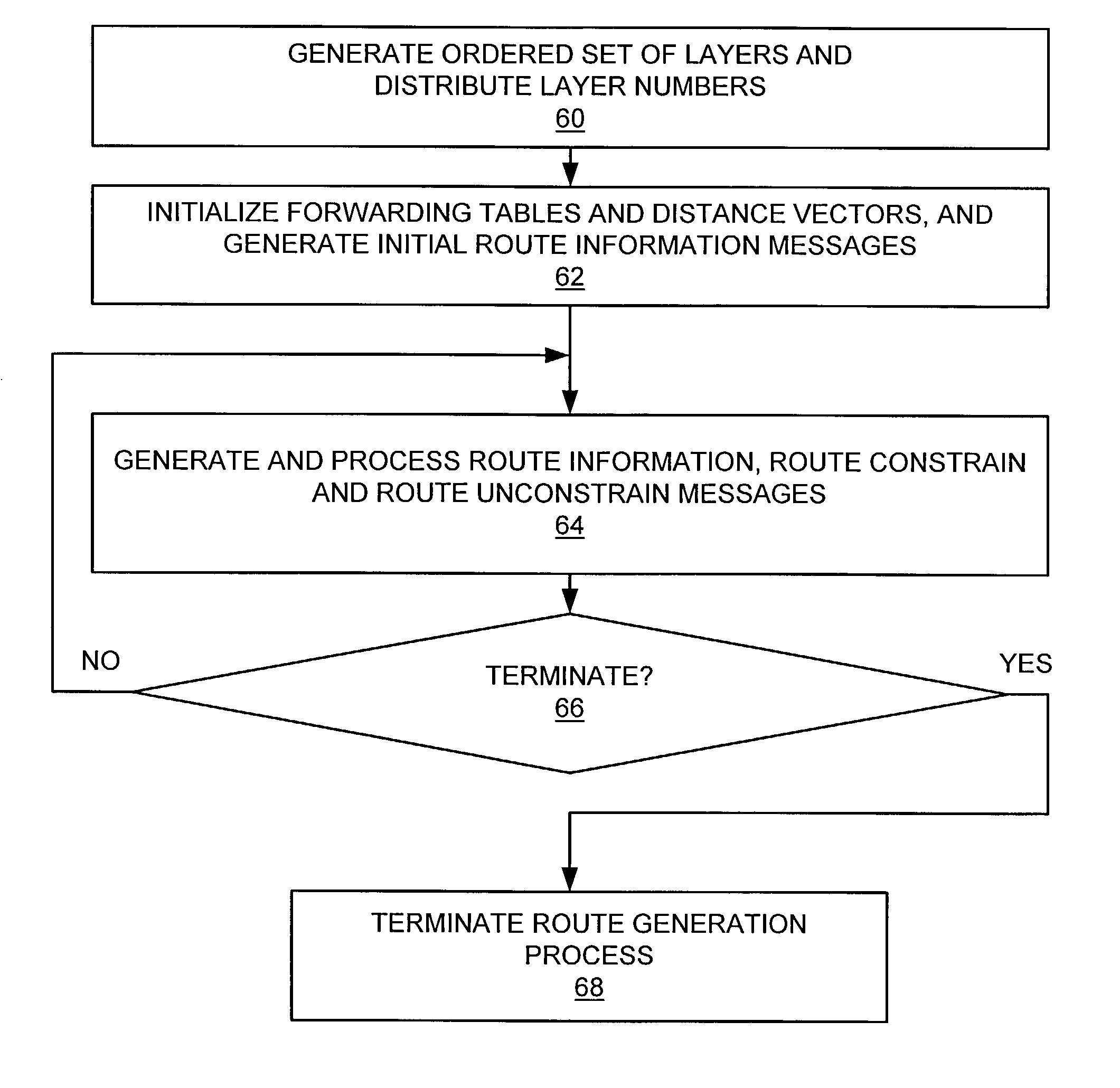

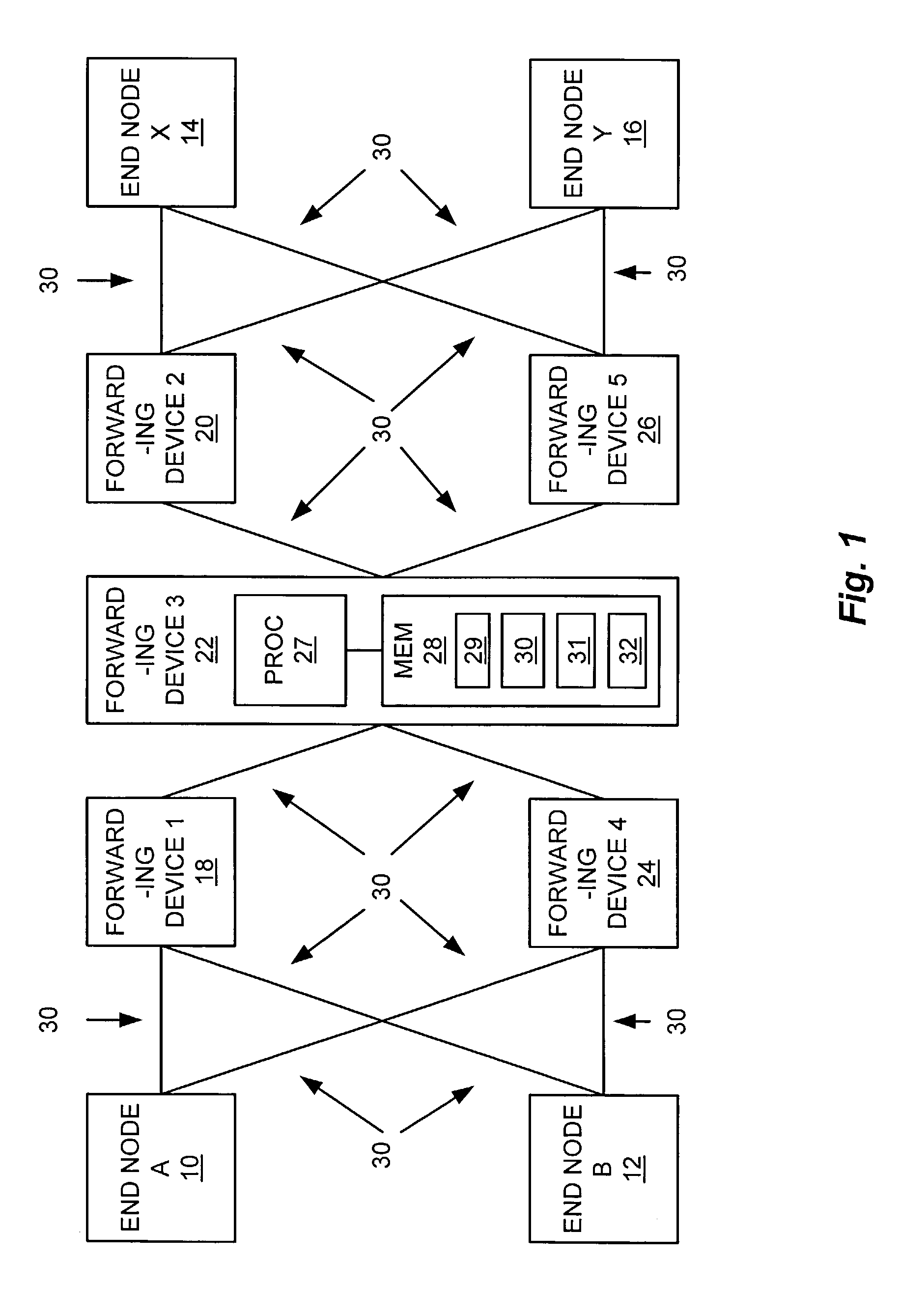

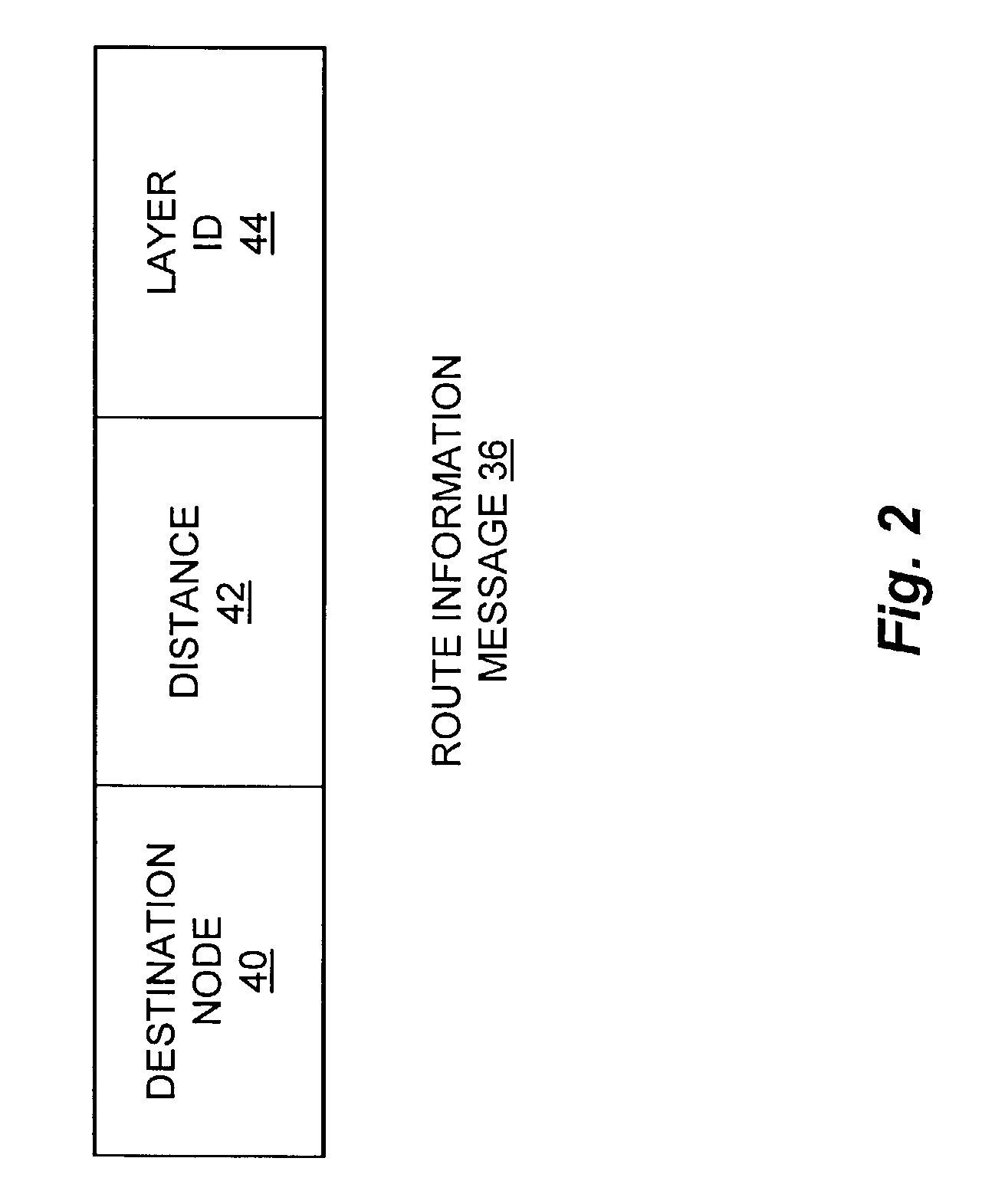

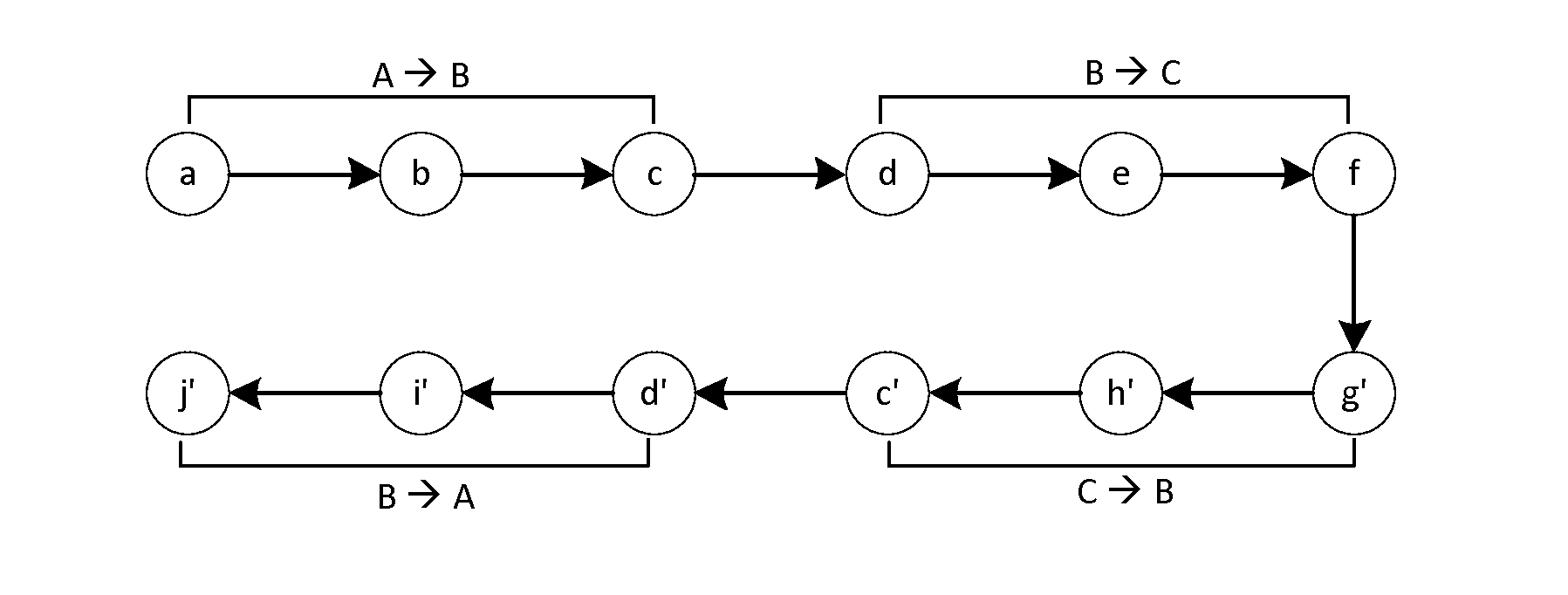

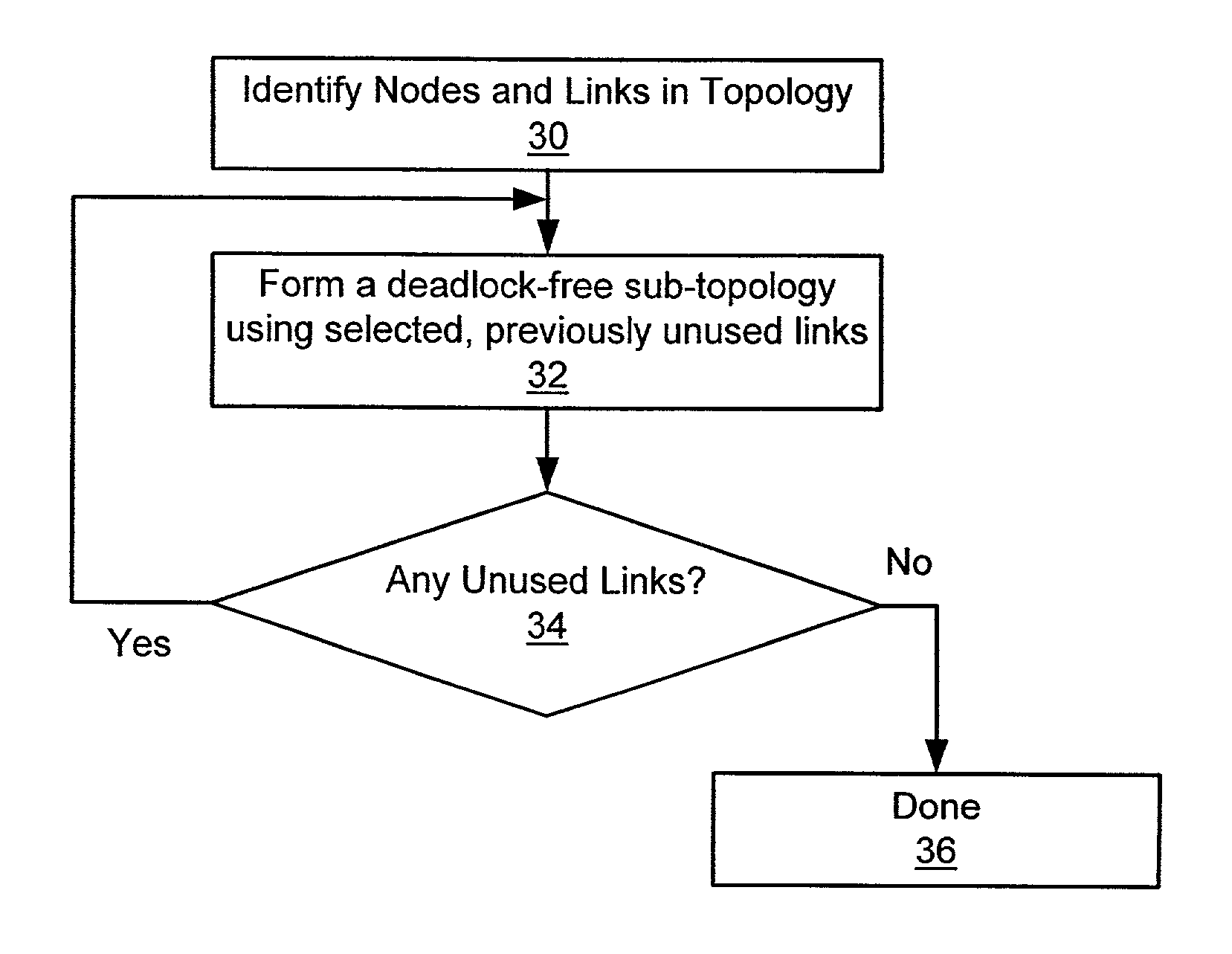

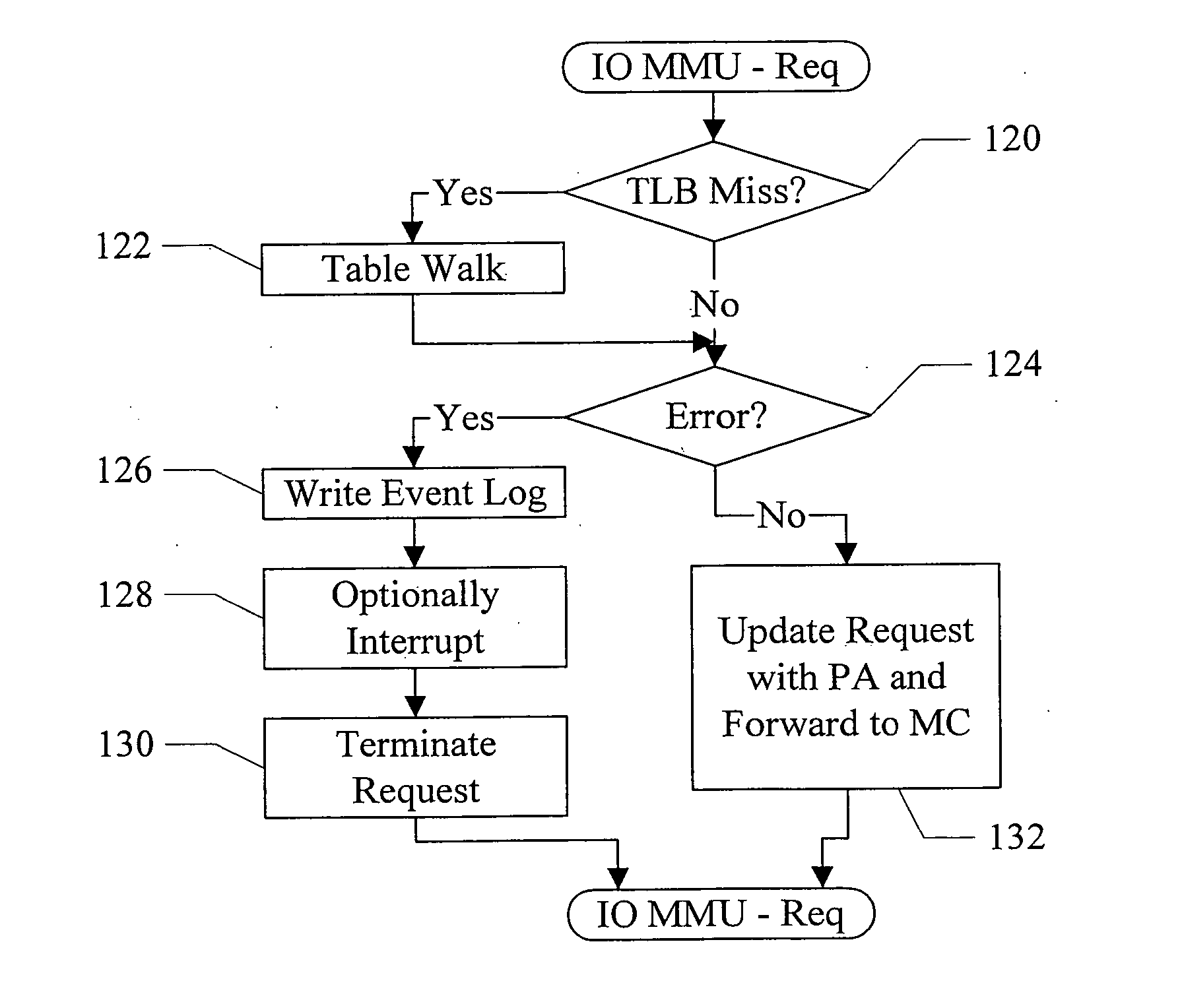

Calculation of layered routes in a distributed manner

A distributed system and method generate “layered routes” that reflect a layered representation of a network, which representation provides deadlock-free routes. The layered representation consists of an ordered set of layers, where each layer is a deadlock-free sub-topology of the network. In determining routes, the links used in each route are constrained to be taken from layers of non-decreasing order as the route extends from source to destination. A device that determines a better or equal cost path to a destination node with respect to its current path to that node sends a route information message to its neighbor devices. The receiver of a route information message may then accept the message and begin using the new path described by the message, or reject the message without using the new path.

Owner:ORACLE INT CORP

Automatic construction of deadlock free interconnects

ActiveUS9244880B2Architecture with single central processing unitData switching networksDeadlock freeNetworks on chip

Systems and methods for automatically building a deadlock free inter-communication network in a multi-core system are described. The example embodiments described herein involve deadlock detection during the mapping of user specified communication pattern amongst blocks of the system. Detected deadlocks are then avoided by re-allocation of channel resources. An example embodiment of the deadlock avoidance scheme is presented on Network-on-chip interconnects for large scale multi-core system-on-chips.

Owner:INTEL CORP

Deadlock-free routing in fat tree networks

Methods and apparatus are provided for routing data packets between source and destination switches in a fat tree network. For each packet, a route is selected having three or less routing phases such that the route follows a shortest path across the network between the source and destination switches. The data packet is transmitted from the source switch to the destination switch, via the route, on one of first and second virtual channels unless the route includes a predetermined one of a down-up turn and an up-down turn. If the route includes the predetermined one of a down-up turn and an up-down turn, the data packet is transmitted, via the route, on the first virtual channel up to the switch 1 at which the turn occurs and on the second virtual channel from that switch. This provides full-connectivity in fat tree networks with deadlock free operation.

Owner:IBM CORP

Method and structure for variable-length frame support in a shared memory switch

InactiveUS7050440B2Data switching by path configurationStore-and-forward switching systemsContinuationElectronic network

The present invention relates to switching in electronic networks. Many data transmission protocols and technologies used in such networks, such as TCP / IP and Ethernet, use variable-length packets for transmission. Often however, the nodes that make up these networks typically contain high-speed cell switches that only support fixed-size data units. To support variable-length packets in such a fixed-size cell switch non-interleaving switching and transmission must be offered. The present invention provides such a solution in essence by segmenting a variable-length frame into a plurality of fixed-length cells including a start-of-frame cell, one or more continuation cell(s), and an end-of-frame cell and routes said fixed-length cells through said switch, thereby providing, at an output of said switch, subsequent and deadlock-free transmission of consecutive cells of a certain frame, and block any cell of a different frame from interleaving. This leads to better average delay characteristics and removes the need for packet reassembly.

Owner:INT BUSINESS MASCH CORP

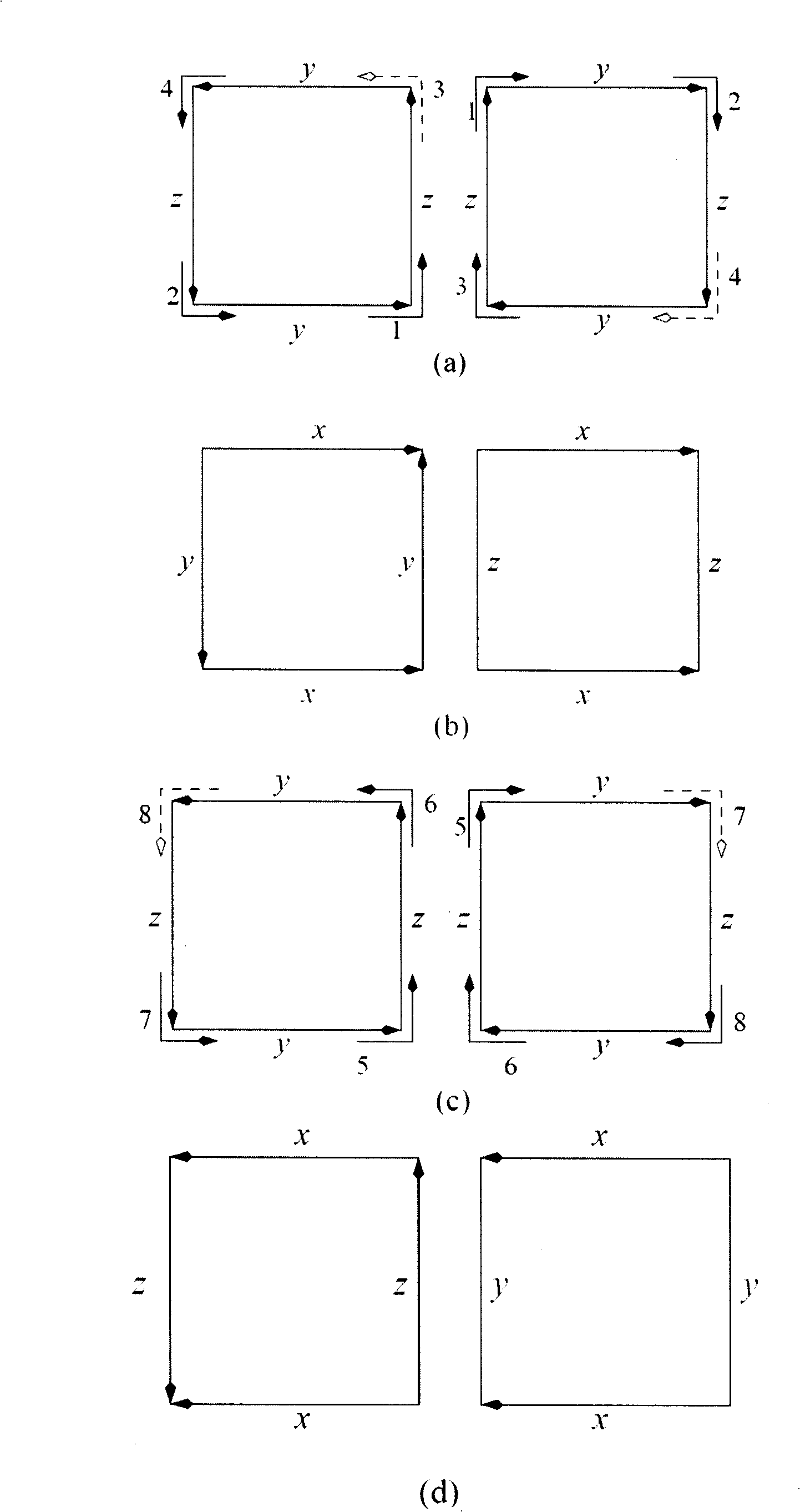

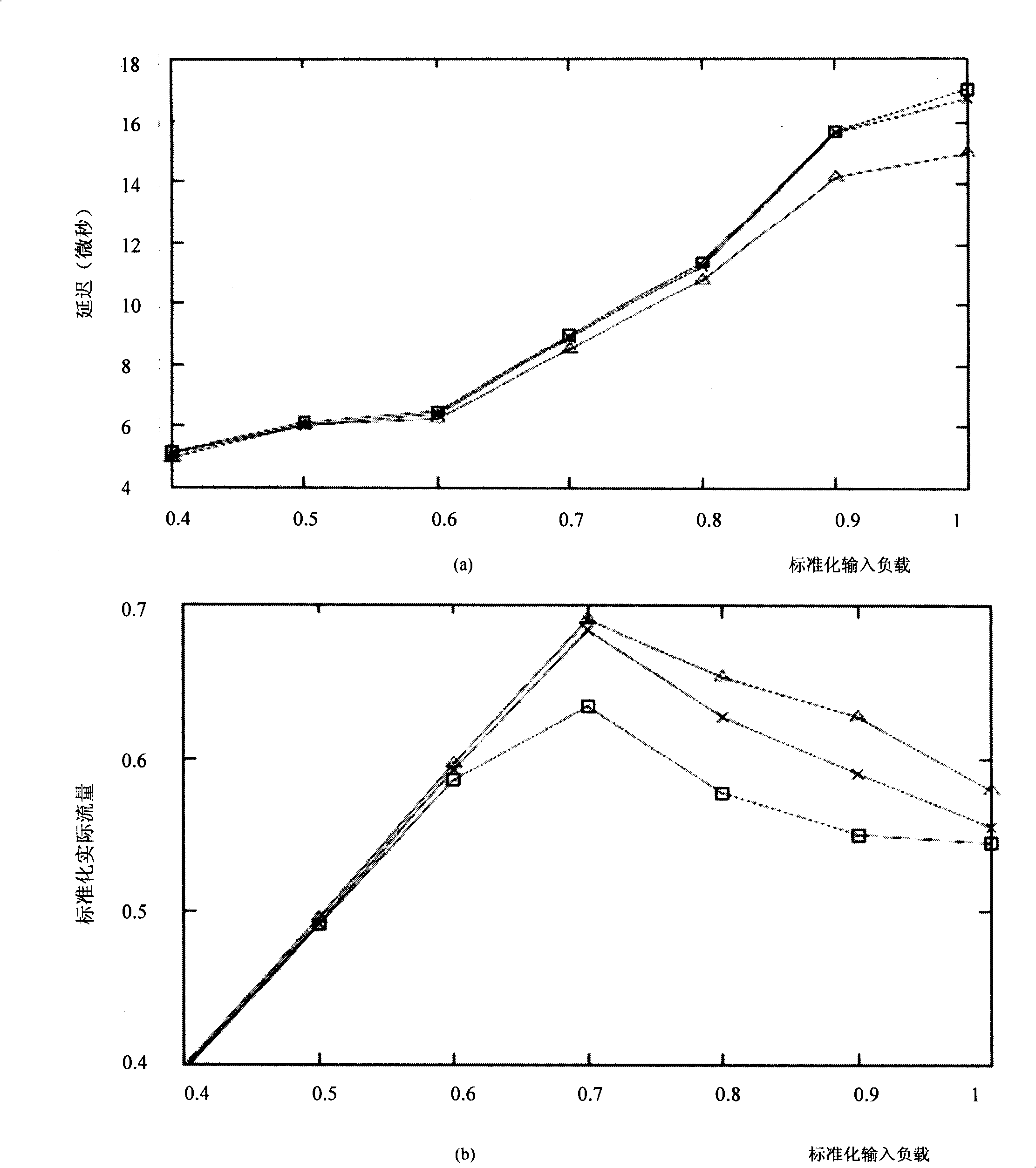

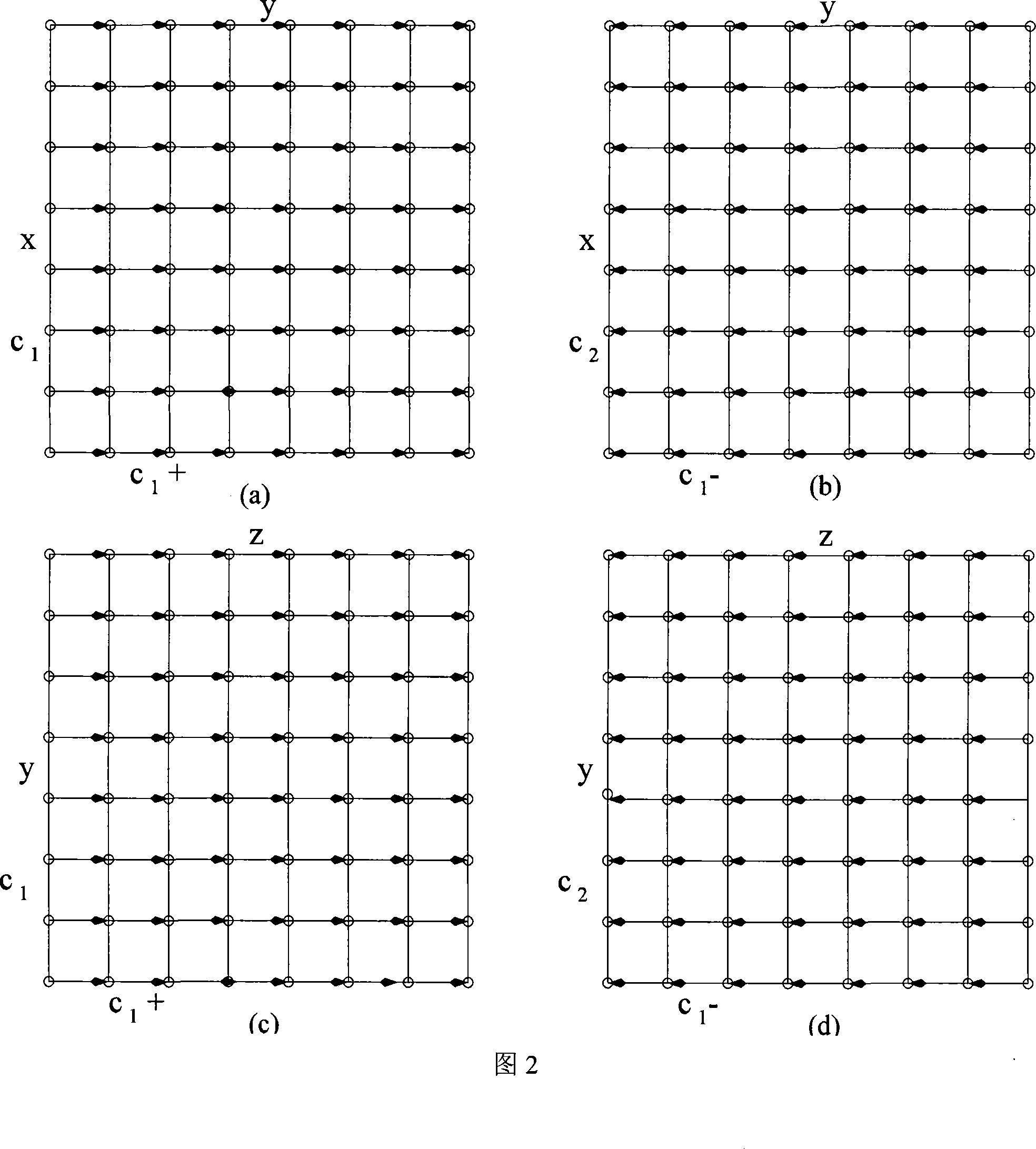

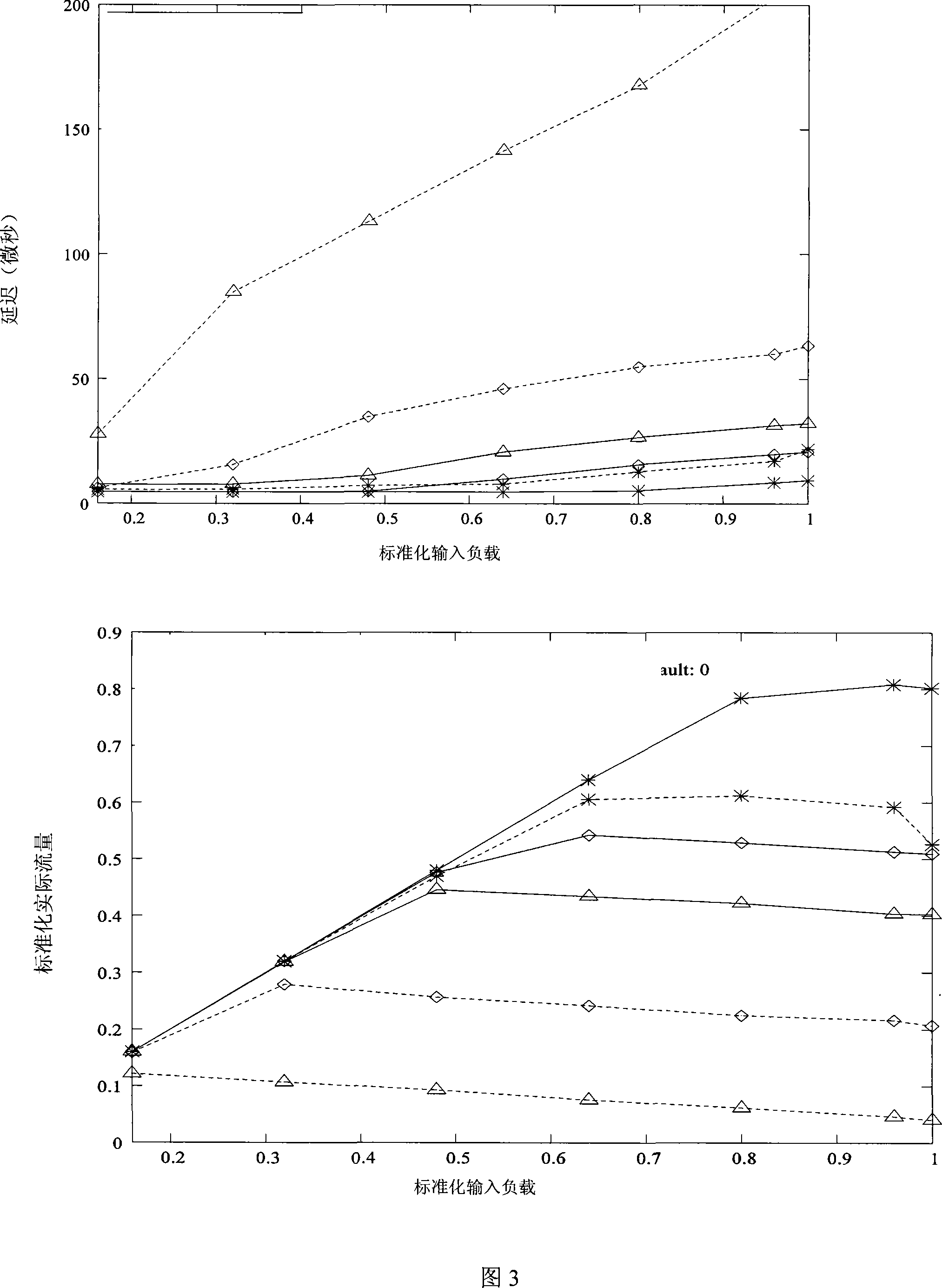

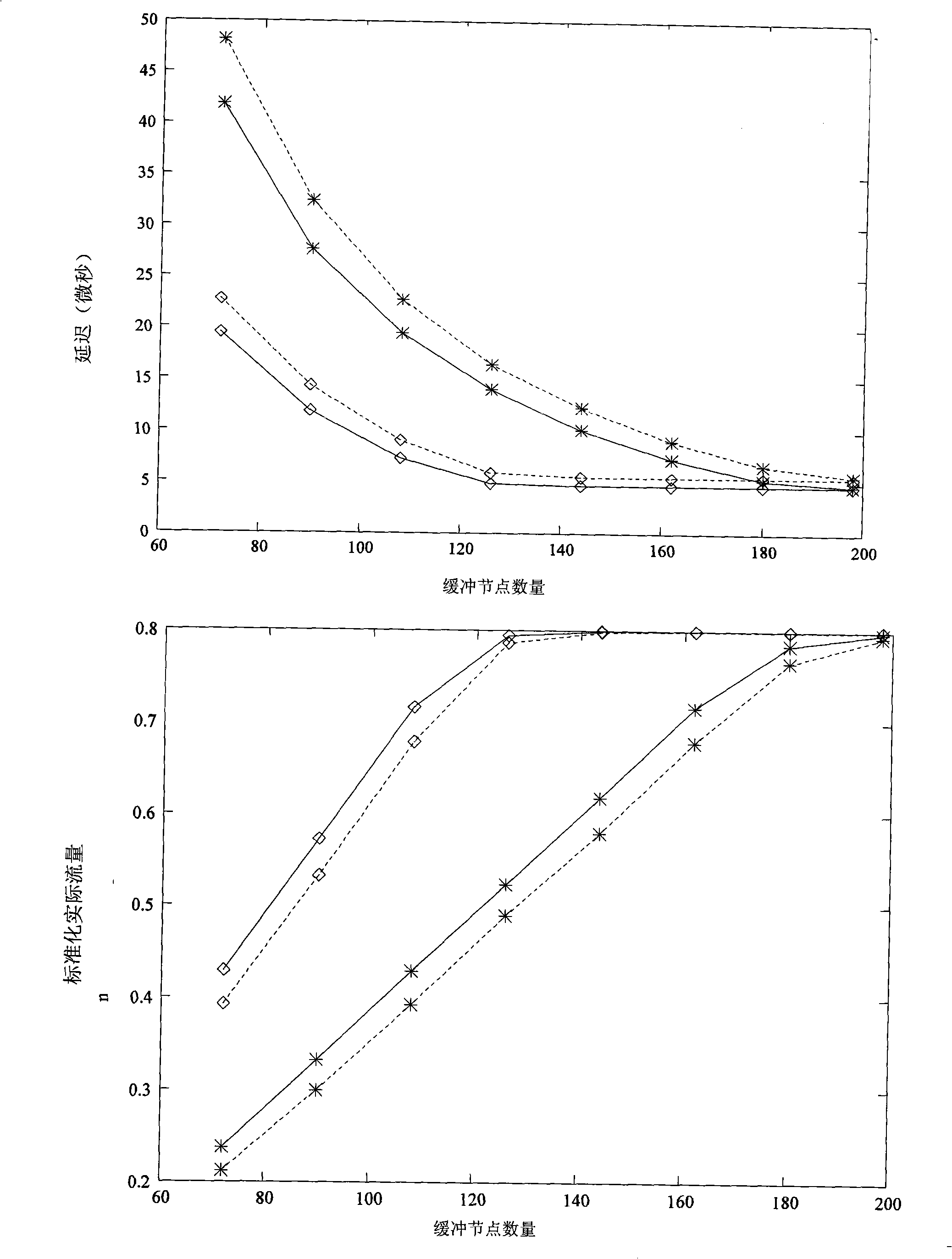

Adaptive routing method without dead lock in three-dimensional torus network

InactiveCN101335704AHigh trafficImprove transmission performanceData switching networksFault toleranceTraffic capacity

The invention relates to a deadlock-free self-adapting routing method of a three-dimensional torus network and belongs to the field of distributed high-performance fault-tolerance computing technology. The method is characterized in that each physical channel is divided into two virtual channels from the middle, and the two virtual channels are both two-way channels distributed into four virtual subnets of the three-dimensional torus network; some virtual channels are allowed to be shared among different subnets. Turning models are used so as to avoid possible deadlocks in and among the subnets and achieve higher self-adoption. Compared with the traditional Duato protocol and GOAL method, the method of the invention can significantly improve the practical network traffic and reduce transmission delay so as to improve the transmission performance of the entire network when the standardized input load and fault node quantity in the network increase.

Owner:TSINGHUA UNIV

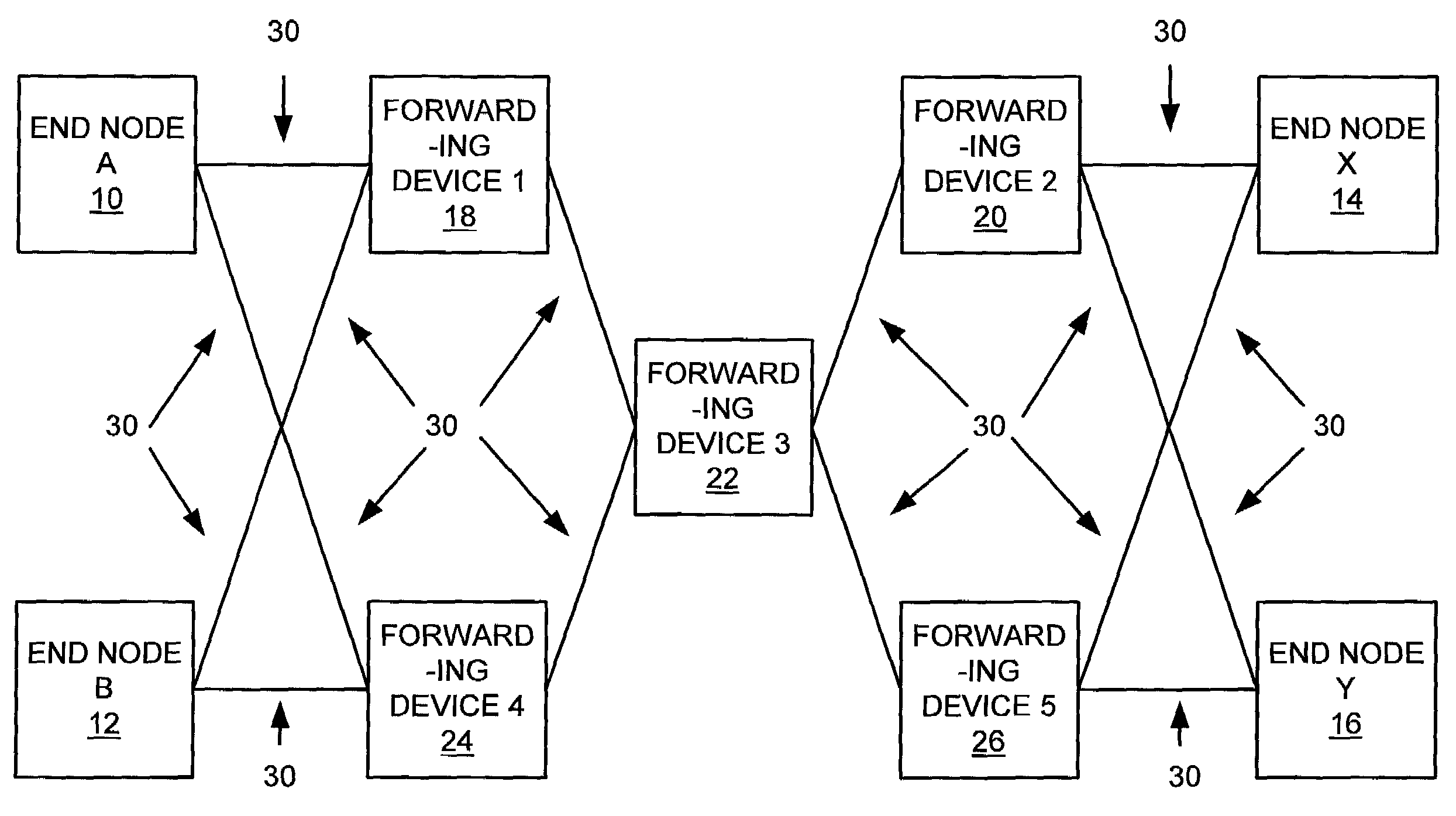

Method of optimizing network capacity and fault tolerance in deadlock-free routing

ActiveUS7200117B2Increase capacityImprove performanceError preventionTransmission systemsFailoverFault tolerance

A system for selecting routing information from a routing table describing alternative routes between end nodes. The routing table represents a set of minimum cost, deadlock-free routes between end nodes. The selected routing information is included in forwarding tables, and sent to networking devices in the network. The selected routing information is optimized for at least one network performance metric, such as overall network capacity or fault tolerance. Capacity optimization is obtained by selecting from alternative routes stored within the routing table such that the standard deviation of the number of routes flowing over each link in the network is minimized. Fault tolerance optimization is achieved by selecting from the alternative routes stored in the routing table such that the selected route for a given end node pair has a “failover” route with a maximum number of dissimilar links from the selected route.

Owner:ORACLE INT CORP

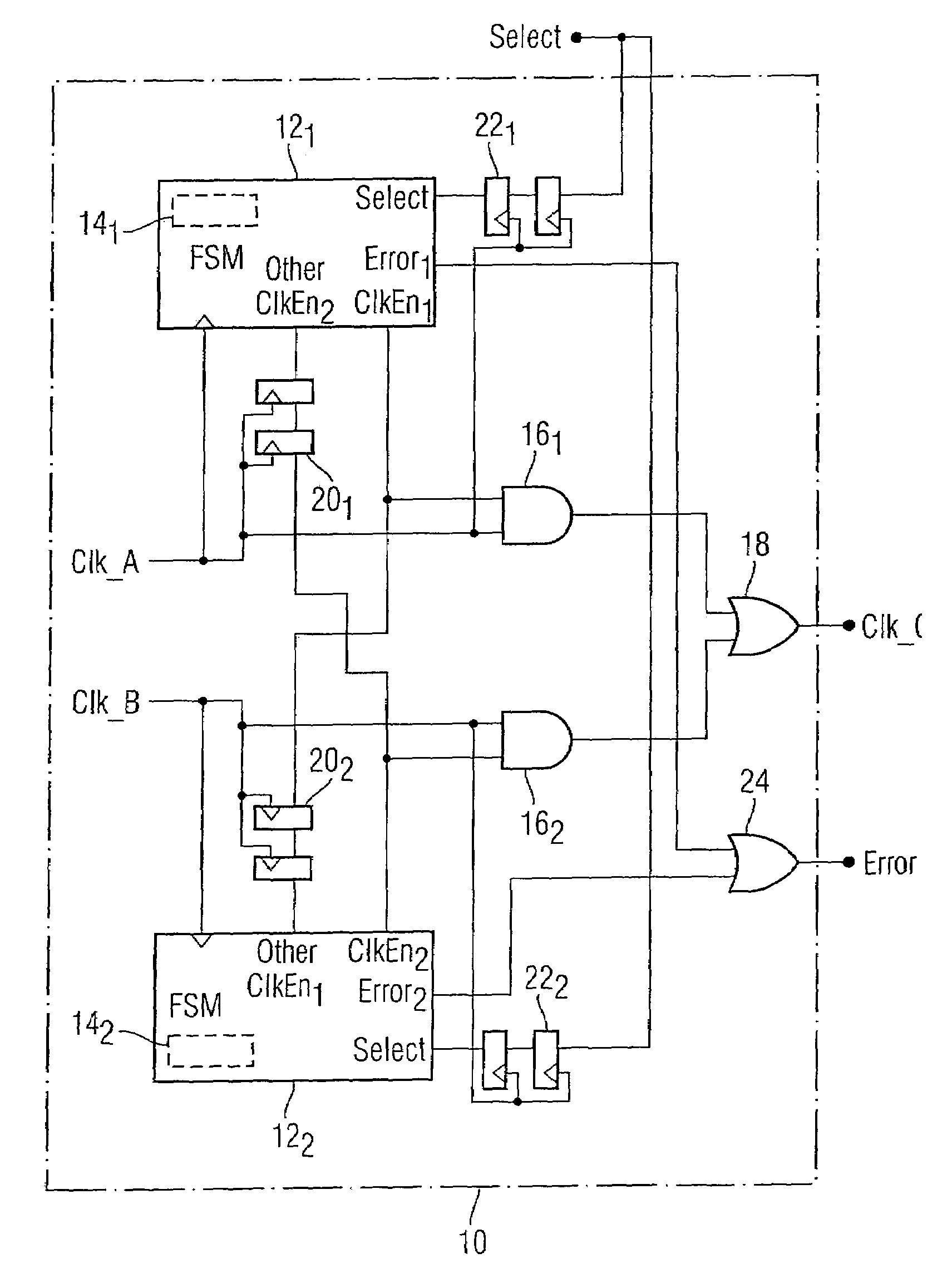

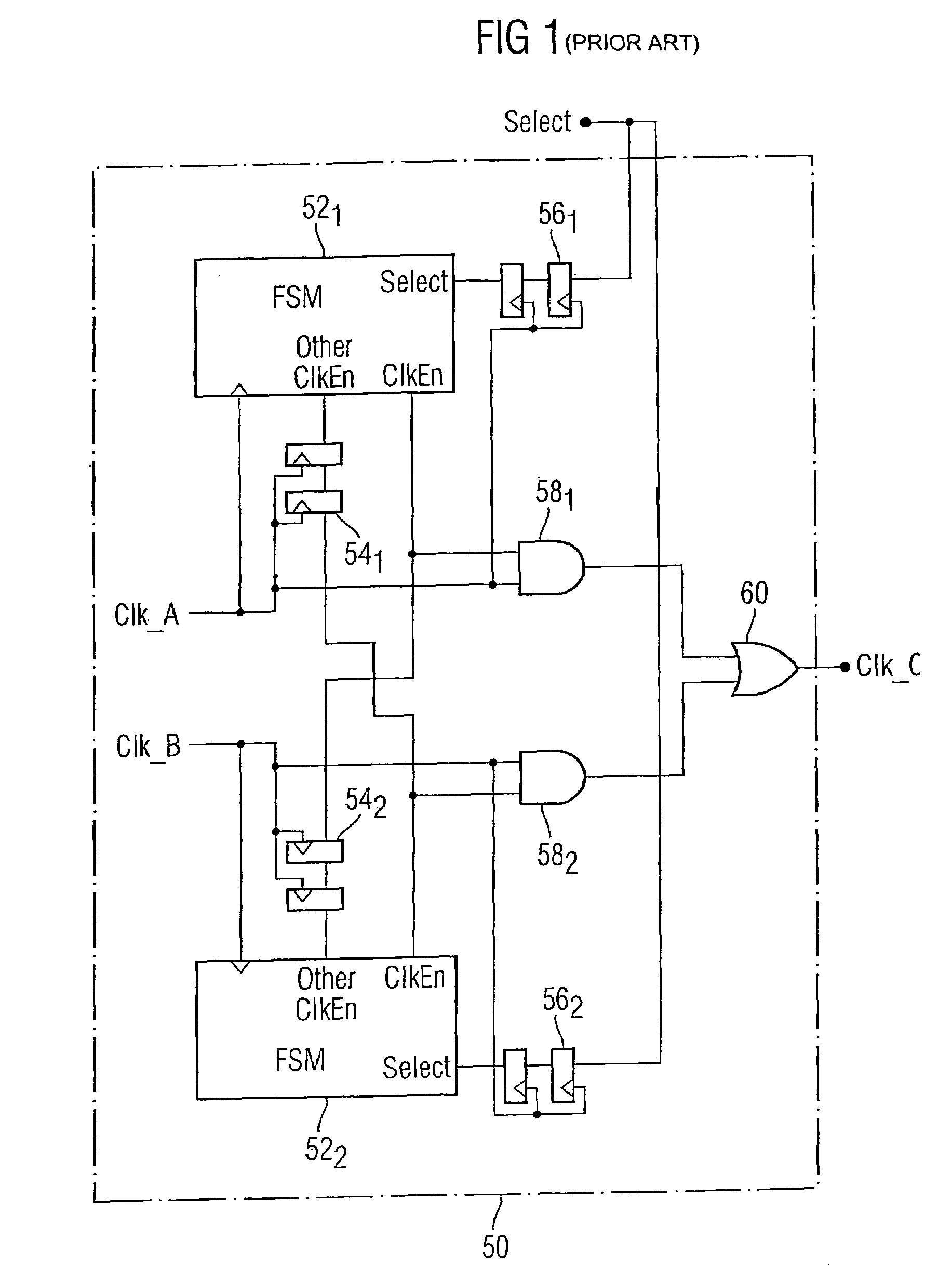

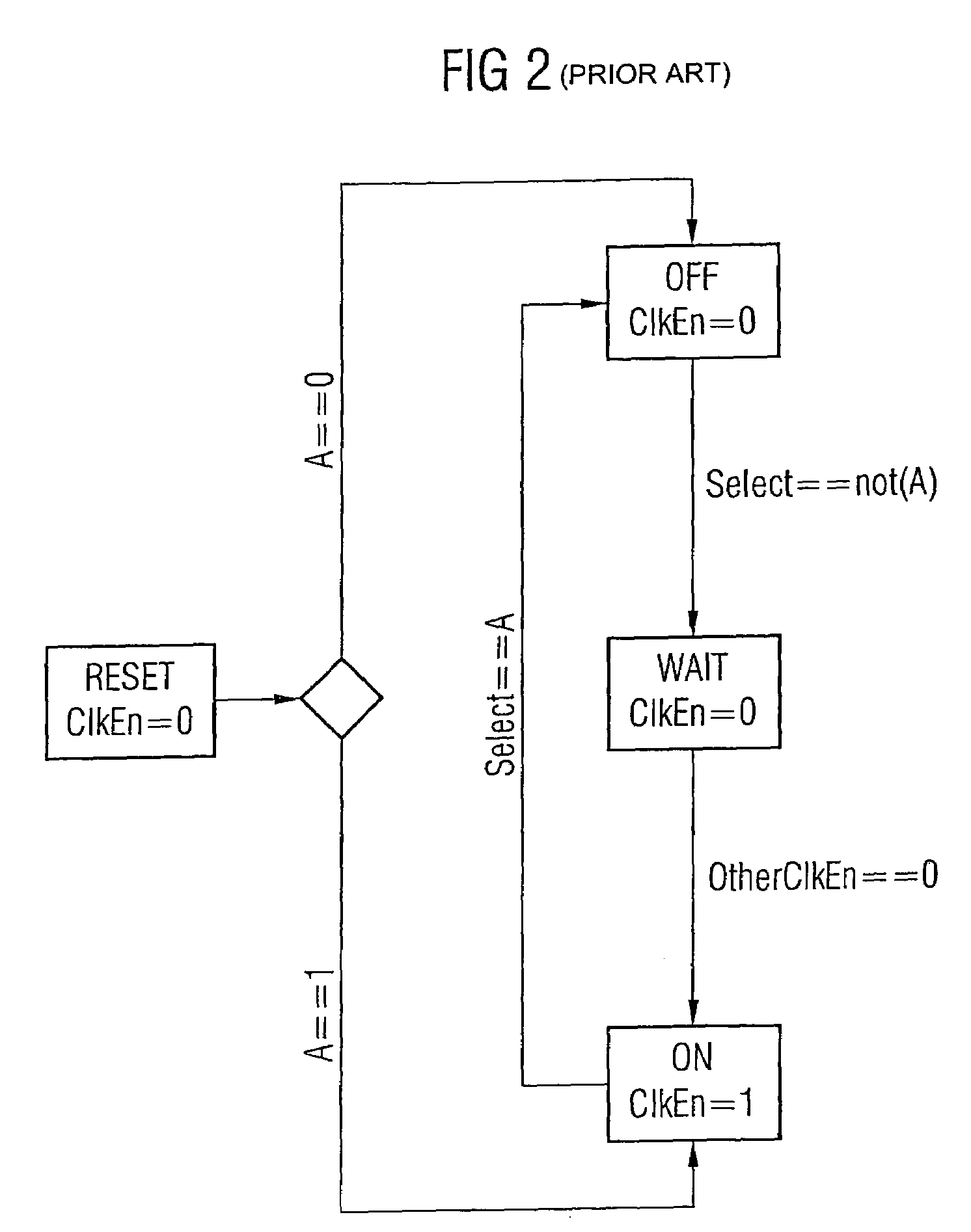

Digital clock switching means

A digital clock switching circuit and method is disclosed and is operable to deadlock-free switch a digital clock source for an integrated circuit. The circuit includes a first finite state machine associated with a first clock source and a second finite state machine associated with a second clock source. The finite state machines are connected to each other and monitor the current state of the other finite state machine. Each finite state machine receives an input select signal to control which clock source should be active and passed to a clock output. Each finite state machine includes a counter, wherein the counter associated with the active clock source is initialized to a first predetermined value when the input select signal indicates a switching off of the active clock source. The finite state machine associated with the active clock source enters a CHECK state and varies a count at each clock cycle. If the other finite state machine verifies a presence of its clock source before the counter reaches a second predetermined value the switch of the active clock source is effected.

Owner:INFINEON TECH AG

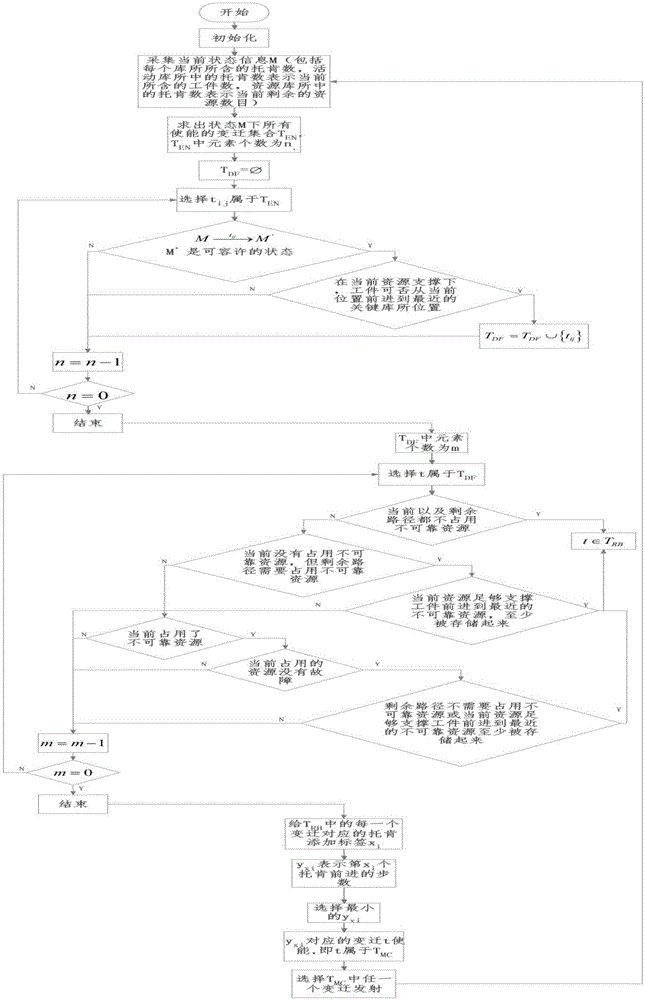

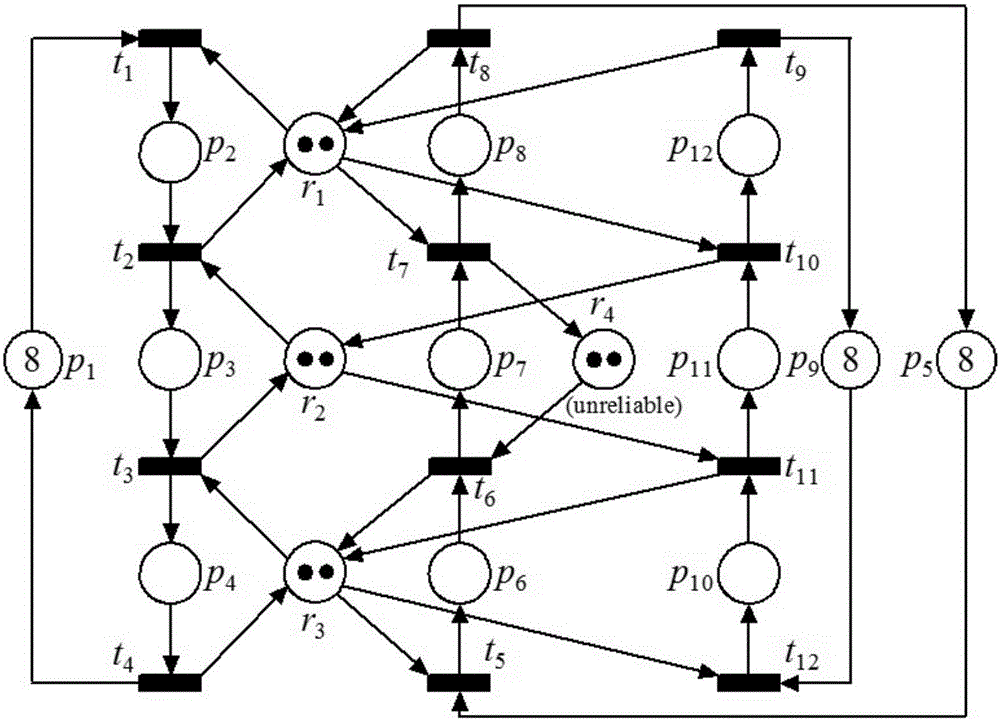

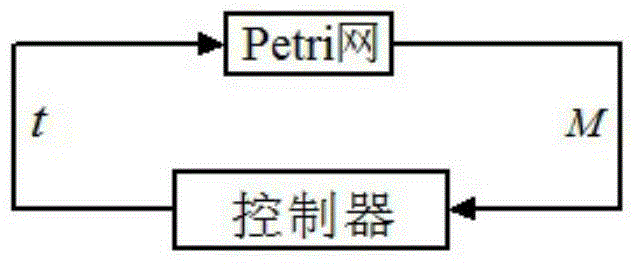

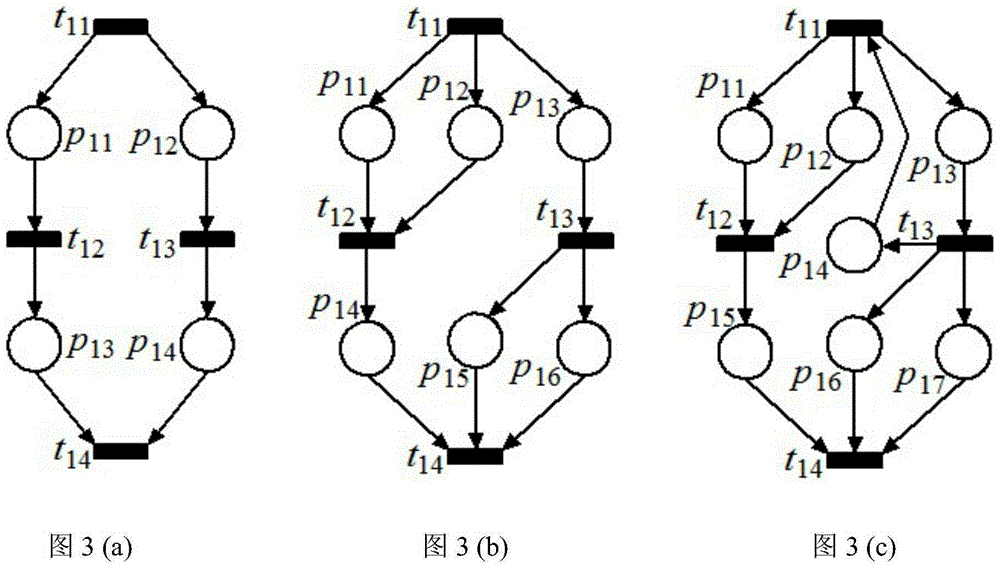

Petri-network-based control method for automatic manufacture system

ActiveCN105022377ARun fastAvoid deadlockTotal factory controlProgramme total factory controlImproved algorithmComputer science

The invention provides a petri-network-based control method for an automatic manufacture system. Through operation of a deadlock avoidance algorithm, a robustness enhancing algorithm and a concurrency improving algorithm, a group of transition set can be produced. Any transmission of transmission belonging to the set can meet requirements for zero deadlock, robustness and system concurrency improvement. After each transition is transmitted, the three algorithms need to be calculated again successively and a new transition set is produced. Through said circulation, a group of event sequence is produced dynamically in real time. According to the invention, when resource faults of a system occur, programs that do not need the fault resources are not blocked by programs that need the fault resources, so that smooth processing can continue and system concurrency can be improved.

Owner:XIDIAN UNIV

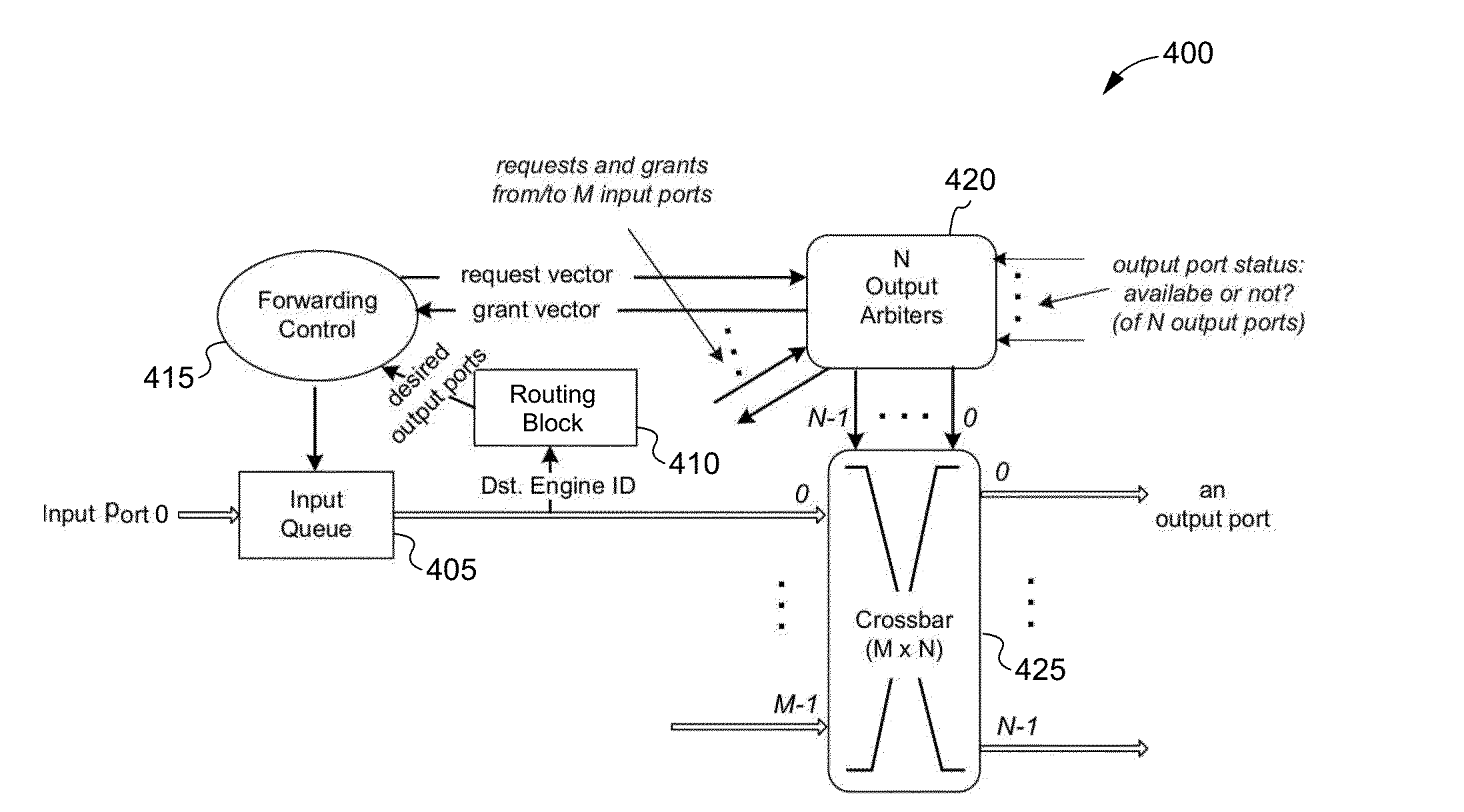

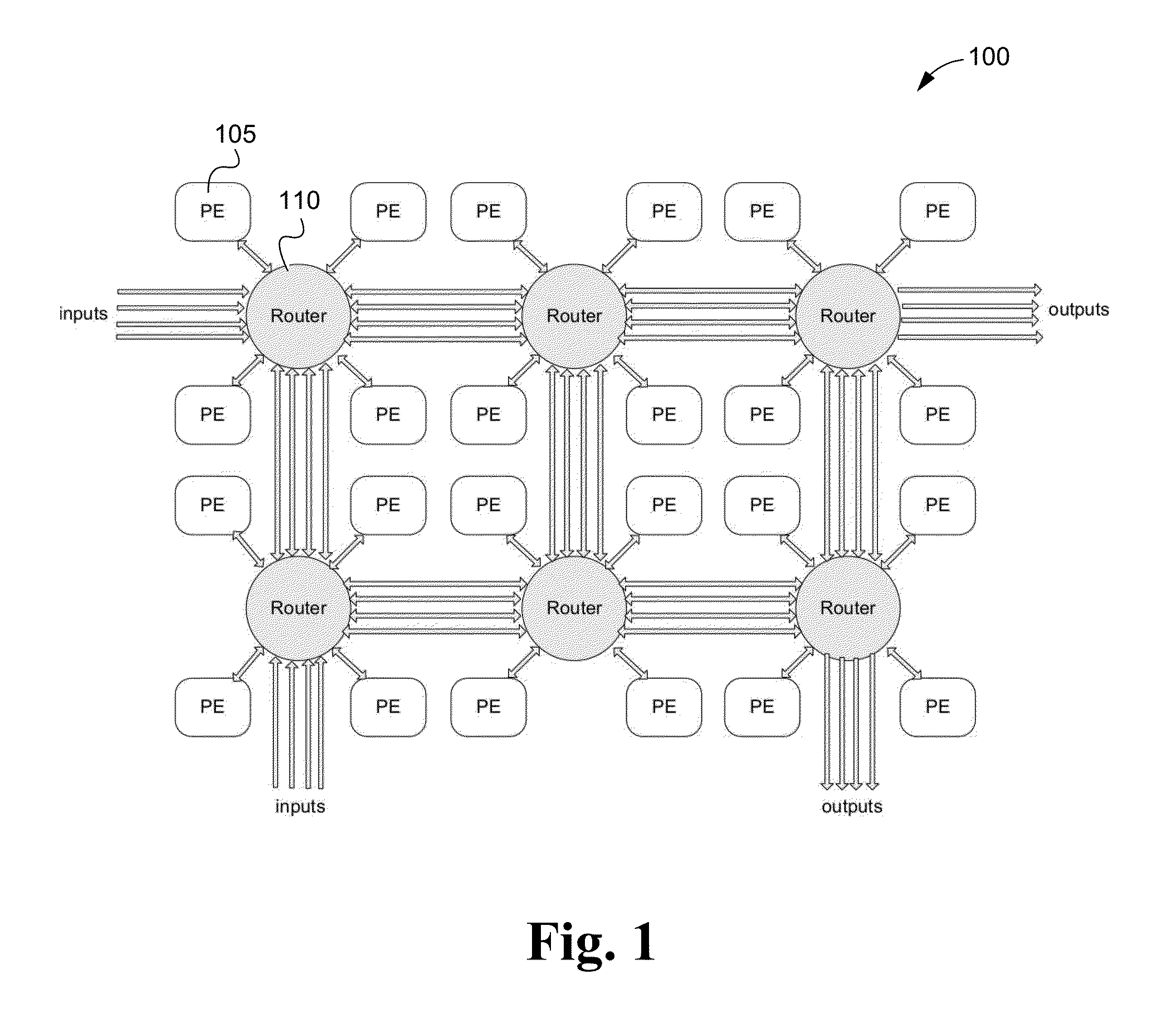

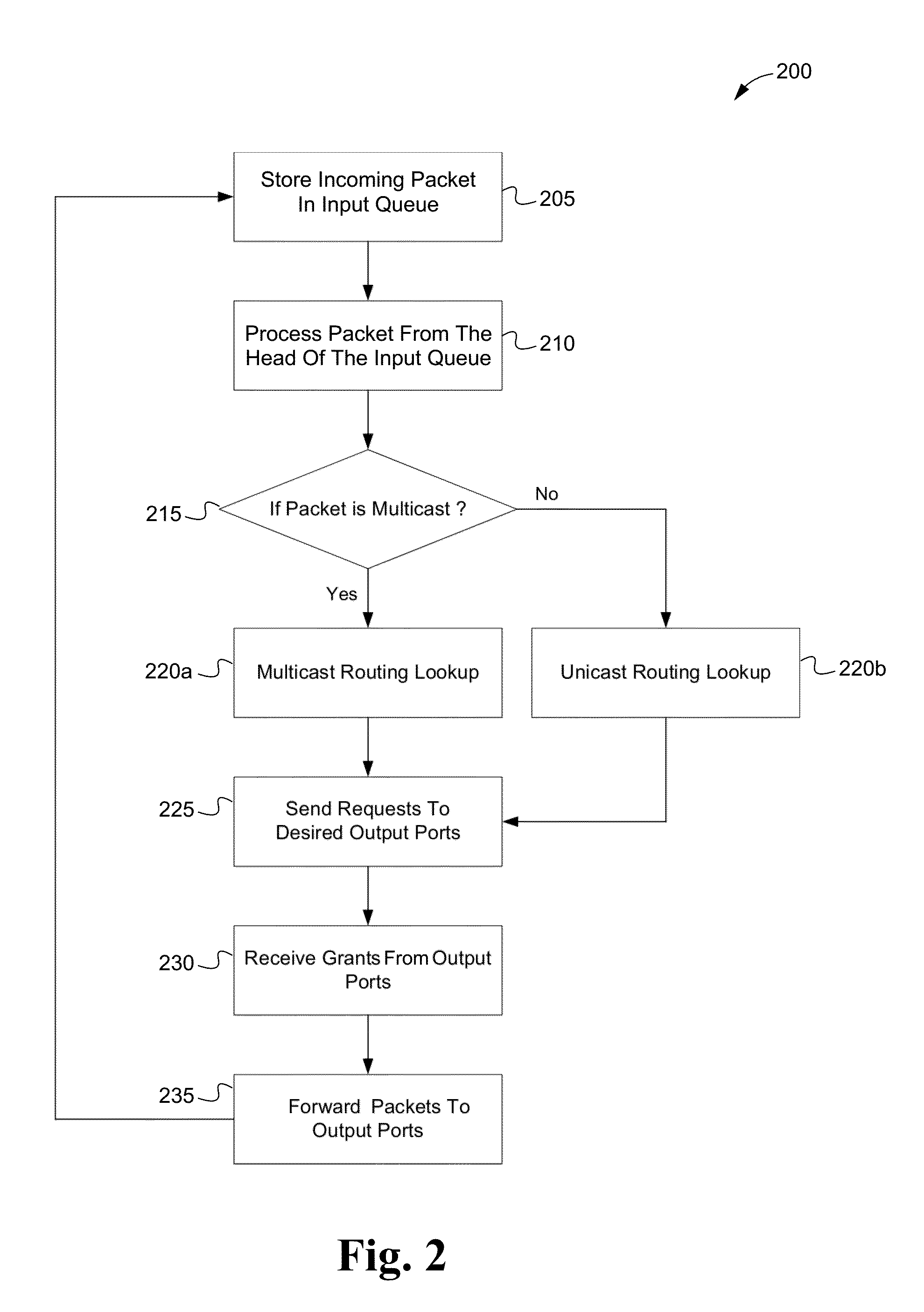

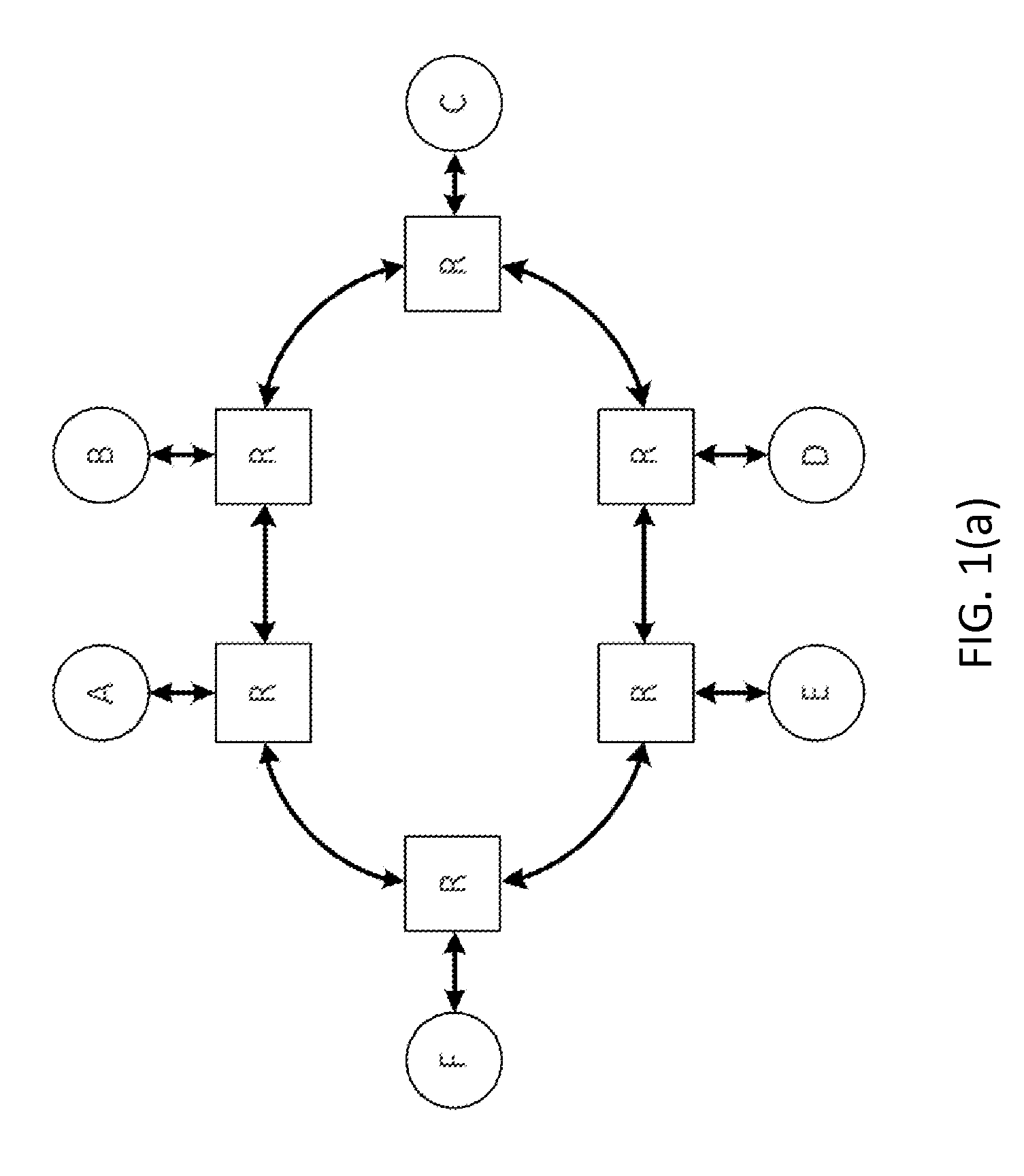

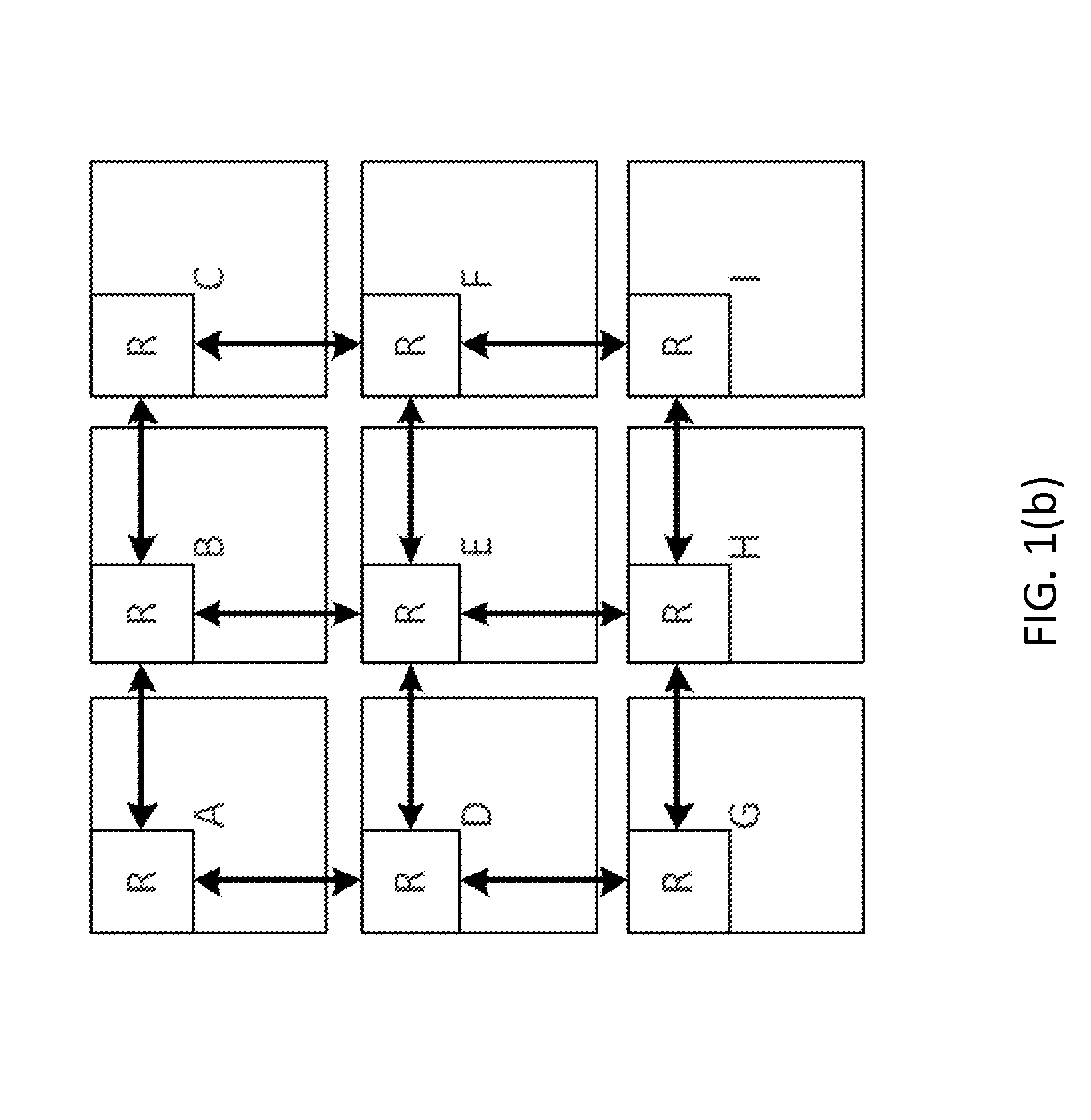

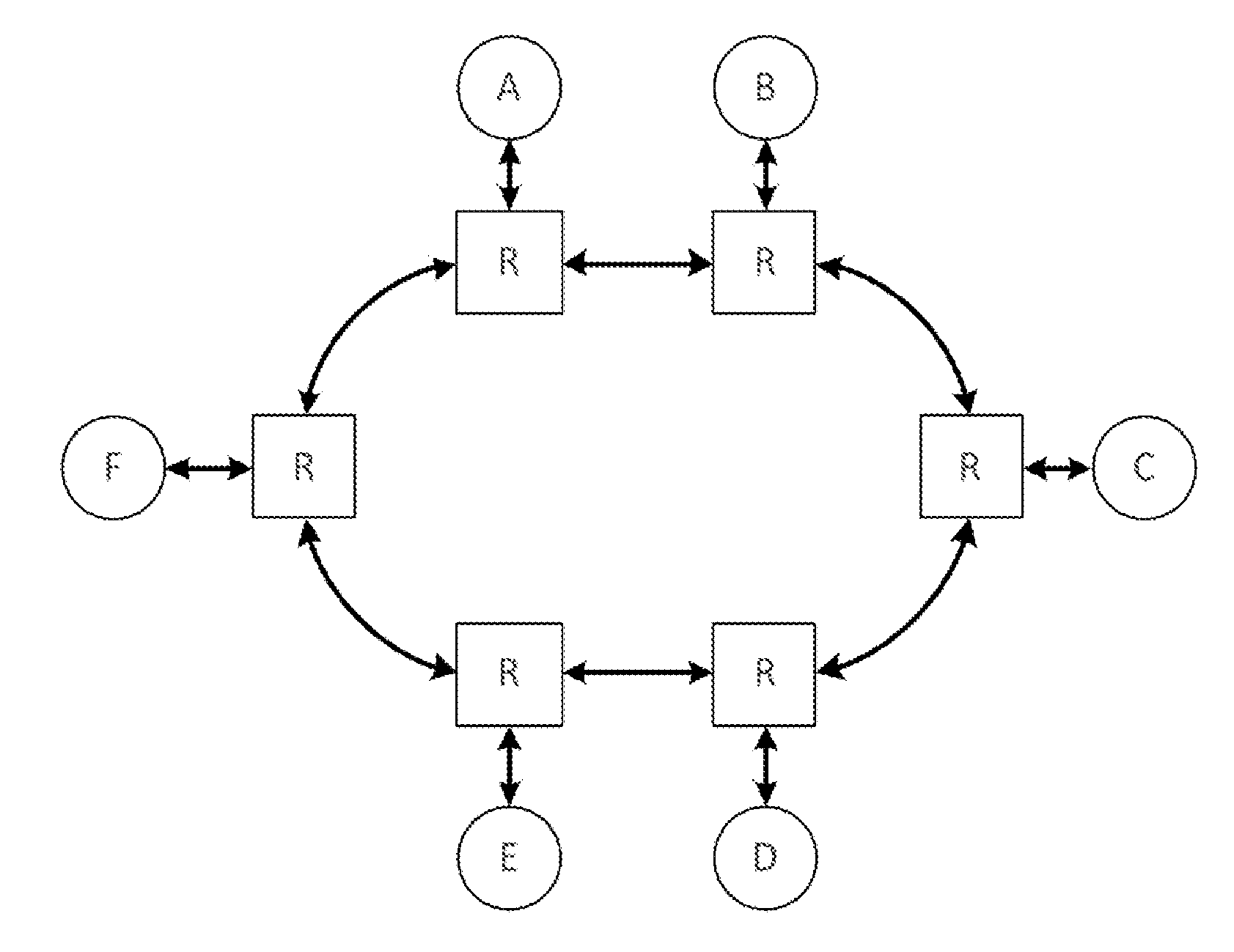

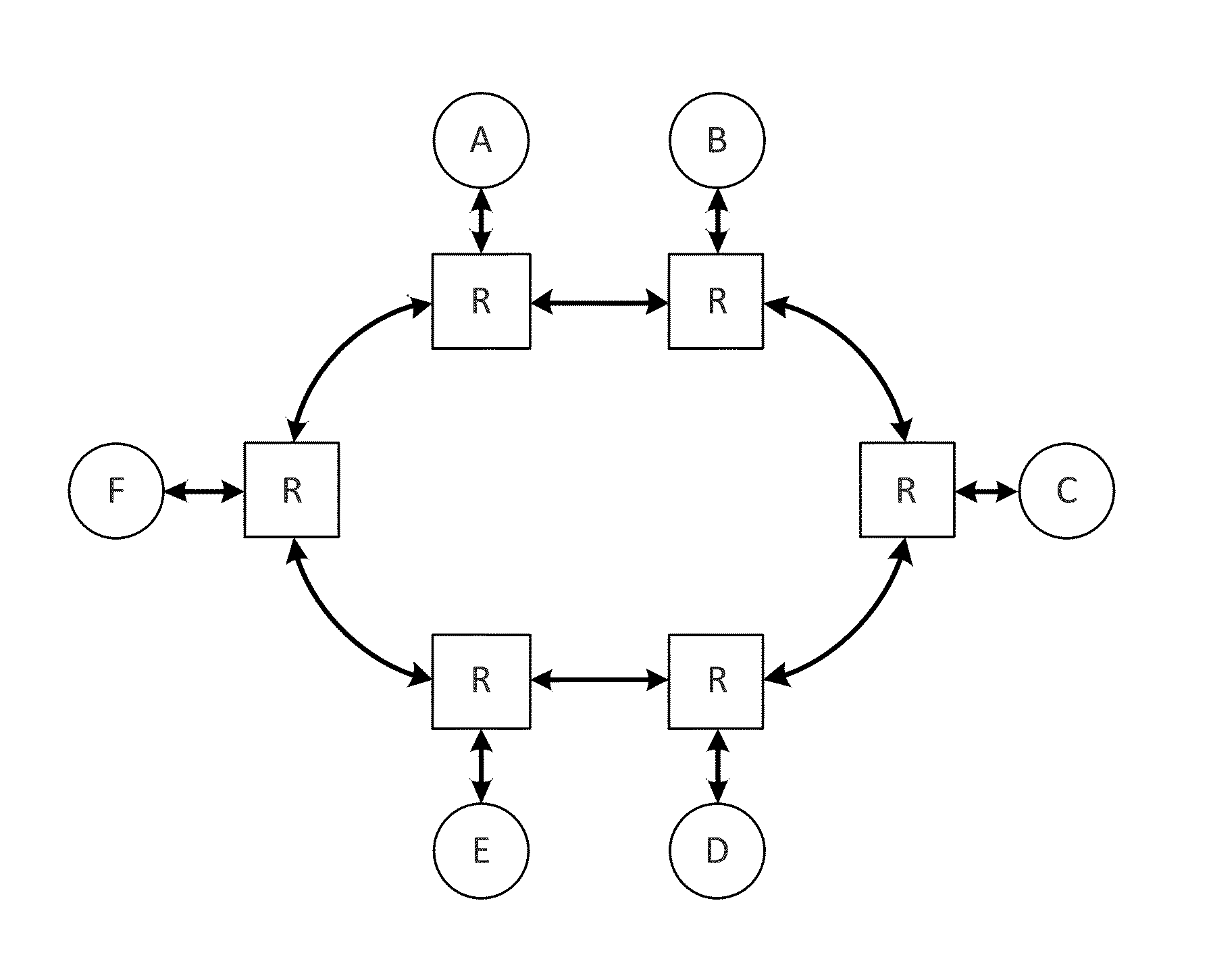

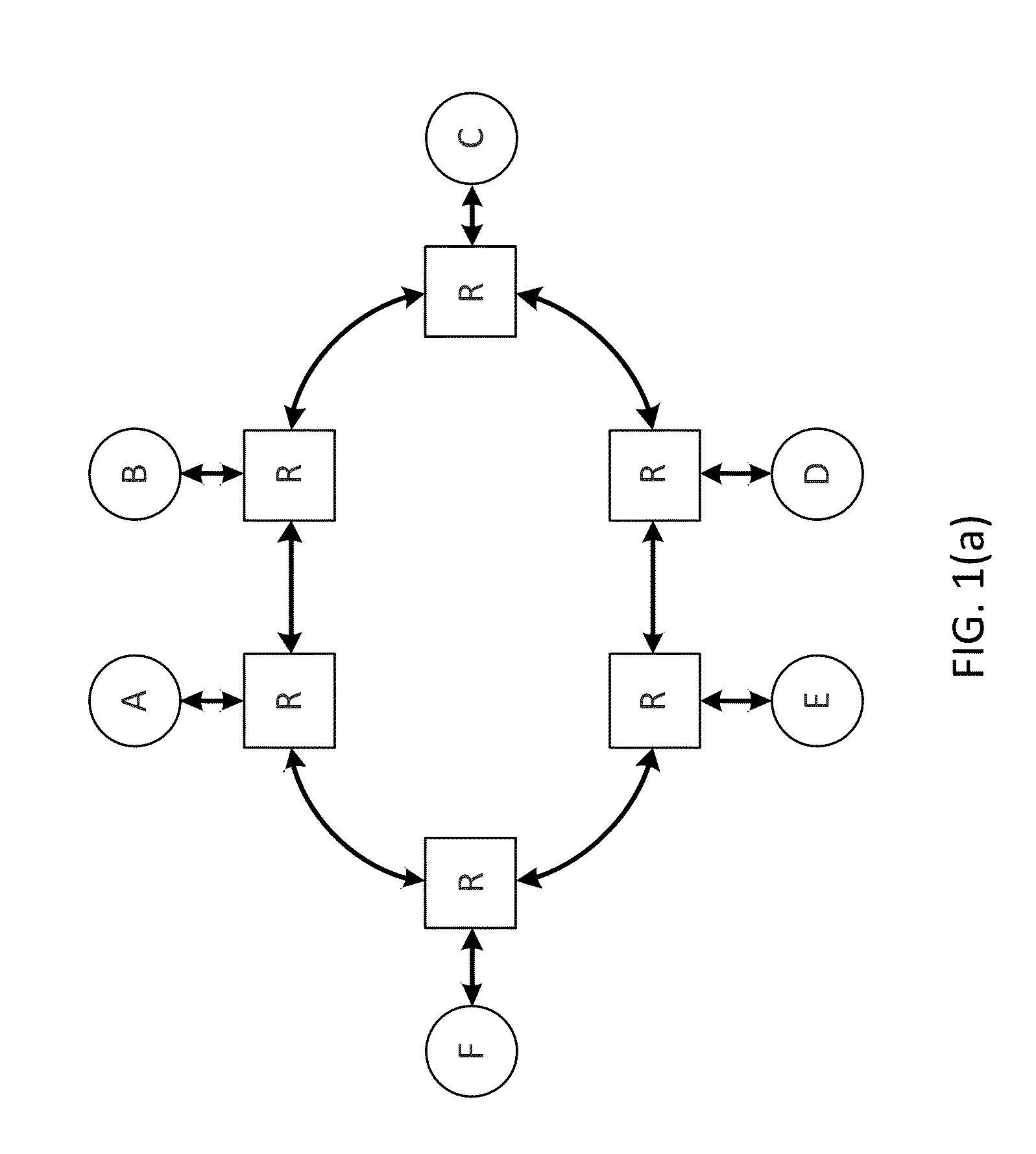

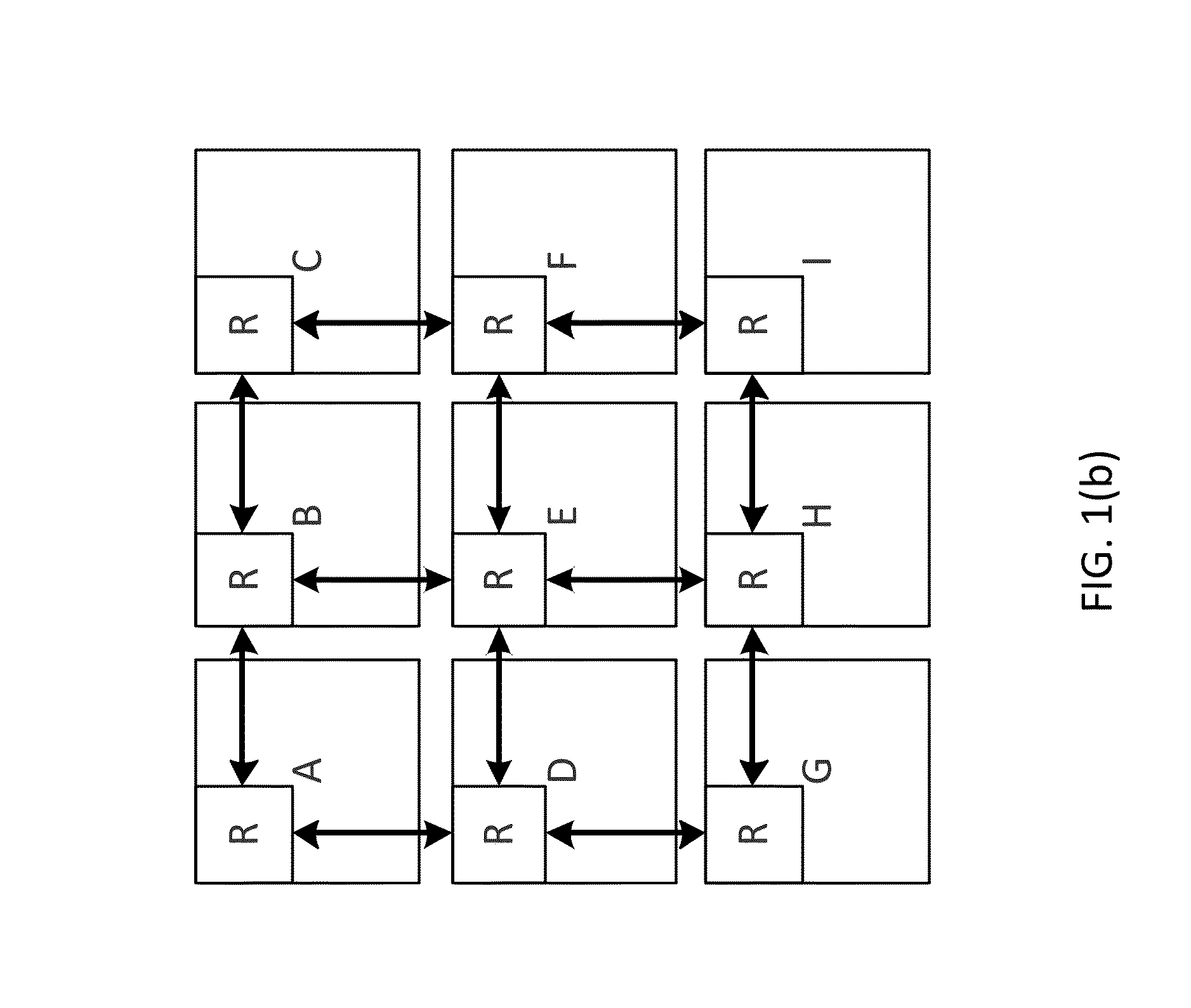

Matrix of on-chip routers interconnecting a plurality of processing engines and a method of routing using thereof

ActiveUS20150188848A1Reduce network congestionEasy networkingSpecial service provision for substationData switching by path configurationRouting tableNetwork packet

Embodiments of the present invention relate to a scalable interconnection scheme of multiple processing engines on a single chip using on-chip configurable routers. The interconnection scheme supports unicast and multicast routing of data packets communicated by the processing engines. Each on-chip configurable router includes routing tables that are programmable by software, and is configured to correctly deliver incoming data packets to its output ports in a fair and deadlock-free manner. In particular, each output port of the on-chip configurable routers includes an output port arbiter to avoid deadlocks when there are contentions at output ports of the on-chip configurable routers and to guarantee fairness in delivery among transferred data packets.

Owner:MARVELL ASIA PTE LTD

Response virtual channel for handling all responses

InactiveUS6888843B2Deadlock-free operationReduce the amount of hardwareStore-and-forward switching systemsElectric digital data processingNetwork packetComputerized system

A computer system employs virtual channels and allocates different resources to the virtual channels. Packets which do not have logical / protocol-related conflicts are grouped into a virtual channel. Accordingly, logical conflicts occur between packets in separate virtual channels. The packets within a virtual channel may share resources (and hence experience resource conflicts), but the packets within different virtual channels may not share resources. Since packets which may experience resource conflicts do not experience logical conflicts, and since packets which may experience logical conflicts do not experience resource conflicts, deadlock-free operation may be achieved. Additionally, nodes within the computer system may be configured to preallocate resources to process response packets. Some response packets may have logical conflicts with other response packets, and hence would normally not be allocable to the same virtual channel. However, by preallocating response-processing resources, response packets are accepted by the destination node. Thus, any resource conflicts which may occur are temporary (as the response packets which make forward progress are processable). Viewed in another way, response packets may be logically independent if the destination node is capable of processing the response packets upon receipt. Accordingly, a response virtual channel is formed to which each response packet belongs.

Owner:GLOBALFOUNDRIES INC

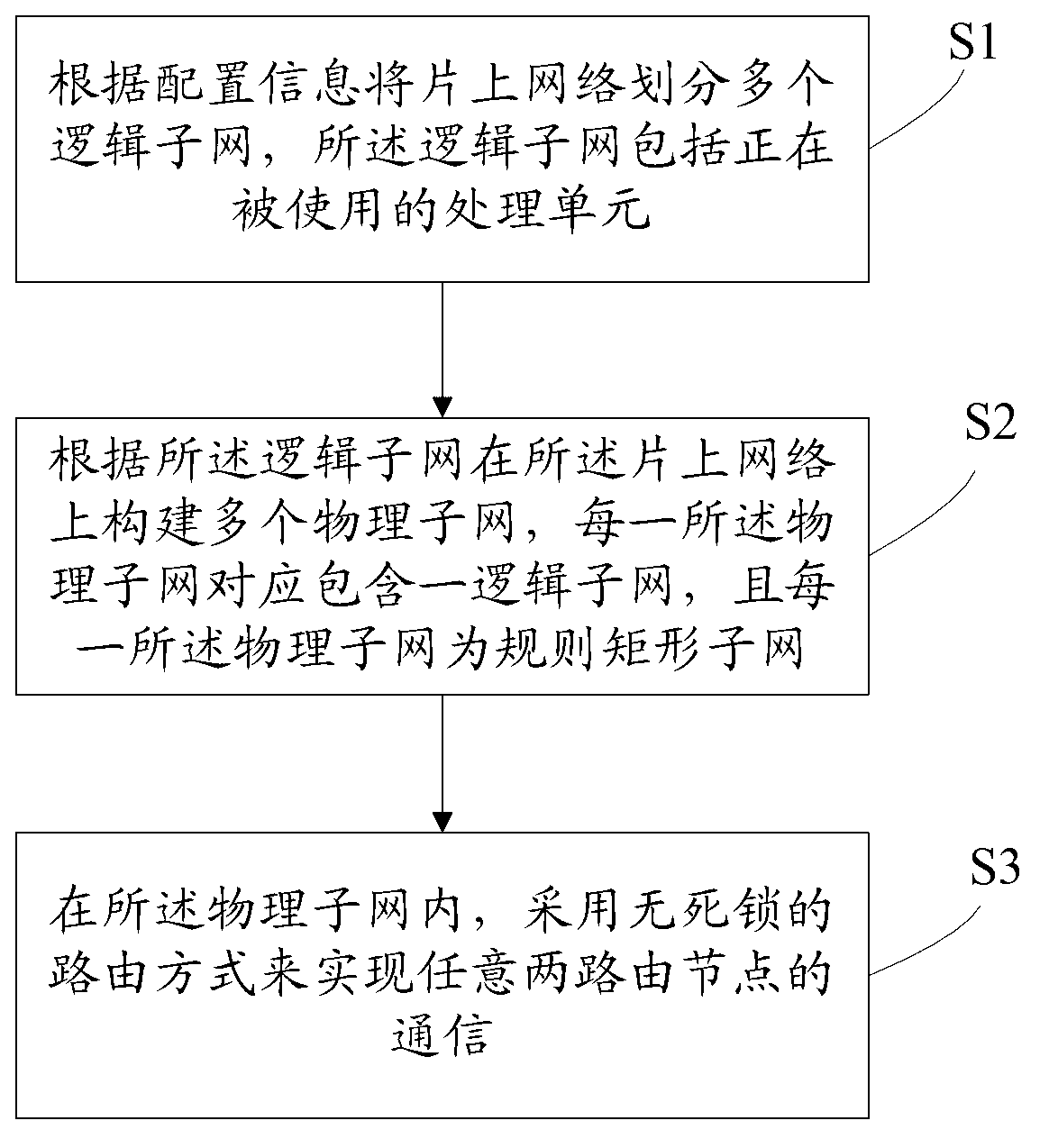

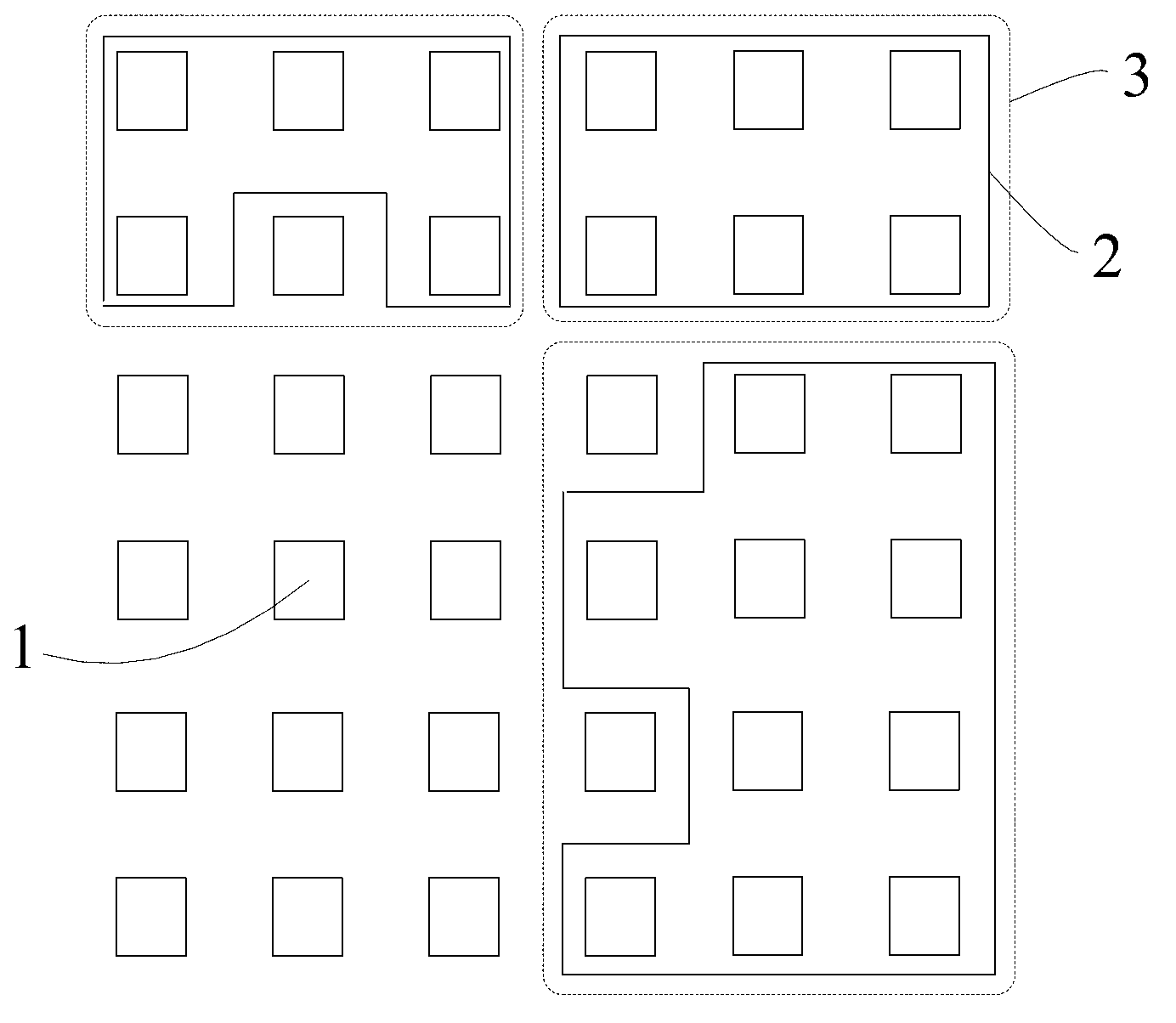

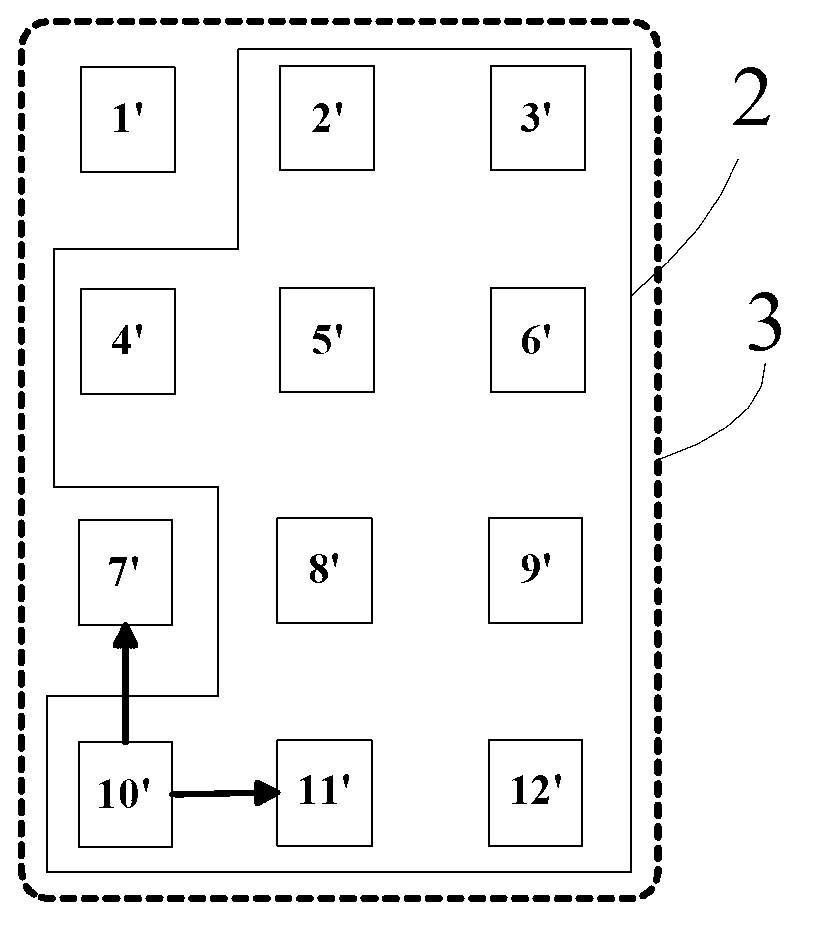

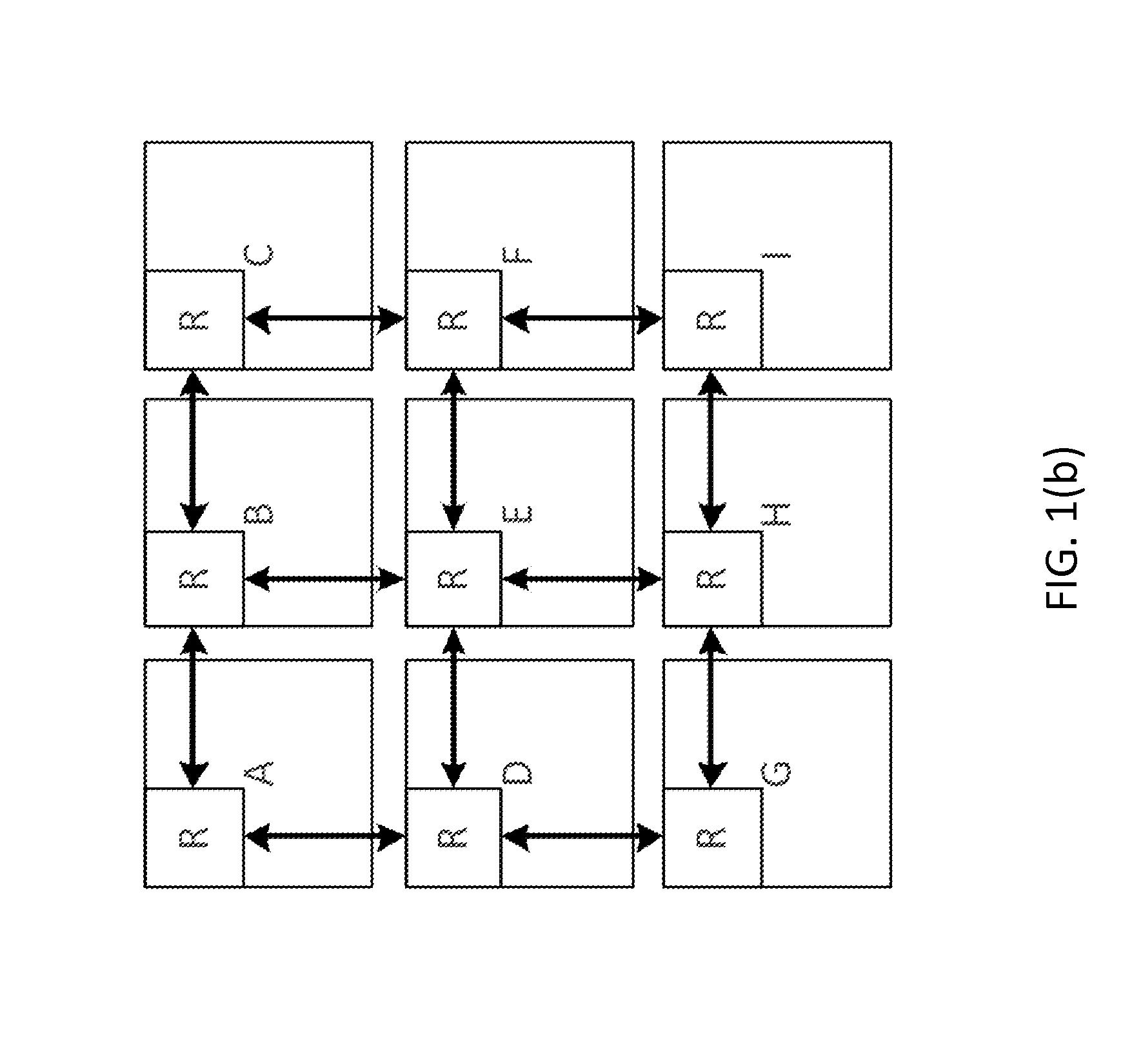

Dynamic reconfigurable subnetting method and system based on network on chip

InactiveCN102799560AAvoid influenceIncrease profitDigital computer detailsElectric digital data processingDeadlock freeNetworks on chip

The invention provides a dynamic reconfigurable subnetting method and system based on a network on a chip, wherein the method comprises the following steps: step S1, the network on chip is partitioned into a plurality of logic subnets according to the configuration information, wherein the logic subnets include processing units which are used right now; step S2, a plurality of physical subnets are constructed on the network on chip according to the logic subnets, wherein each physical subnet correspondingly comprises one logic subnet, and each physical subnet is a regular rectangular subnet; and step S3, a deadlock-free routing mode is adopted to realize the communication between every two routing nodes in the physical subnets. The method can be used for effectively supporting any upper-layer resource partition strategies, the utilization rate of resources on a chip is fully increased, finally, the utilization rate of computing resources in a many-core processor system is effectively increased, and the performance of the many-core processor is improved.

Owner:SHANGHAI JIAO TONG UNIV

Automatic deadlock detection and avoidance in a system interconnect by capturing internal dependencies of IP cores using high level specification

InactiveUS9009648B2Save resource costData switching networksSpecial data processing applicationsDeadlock freeNetworks on chip

Owner:INTEL CORP

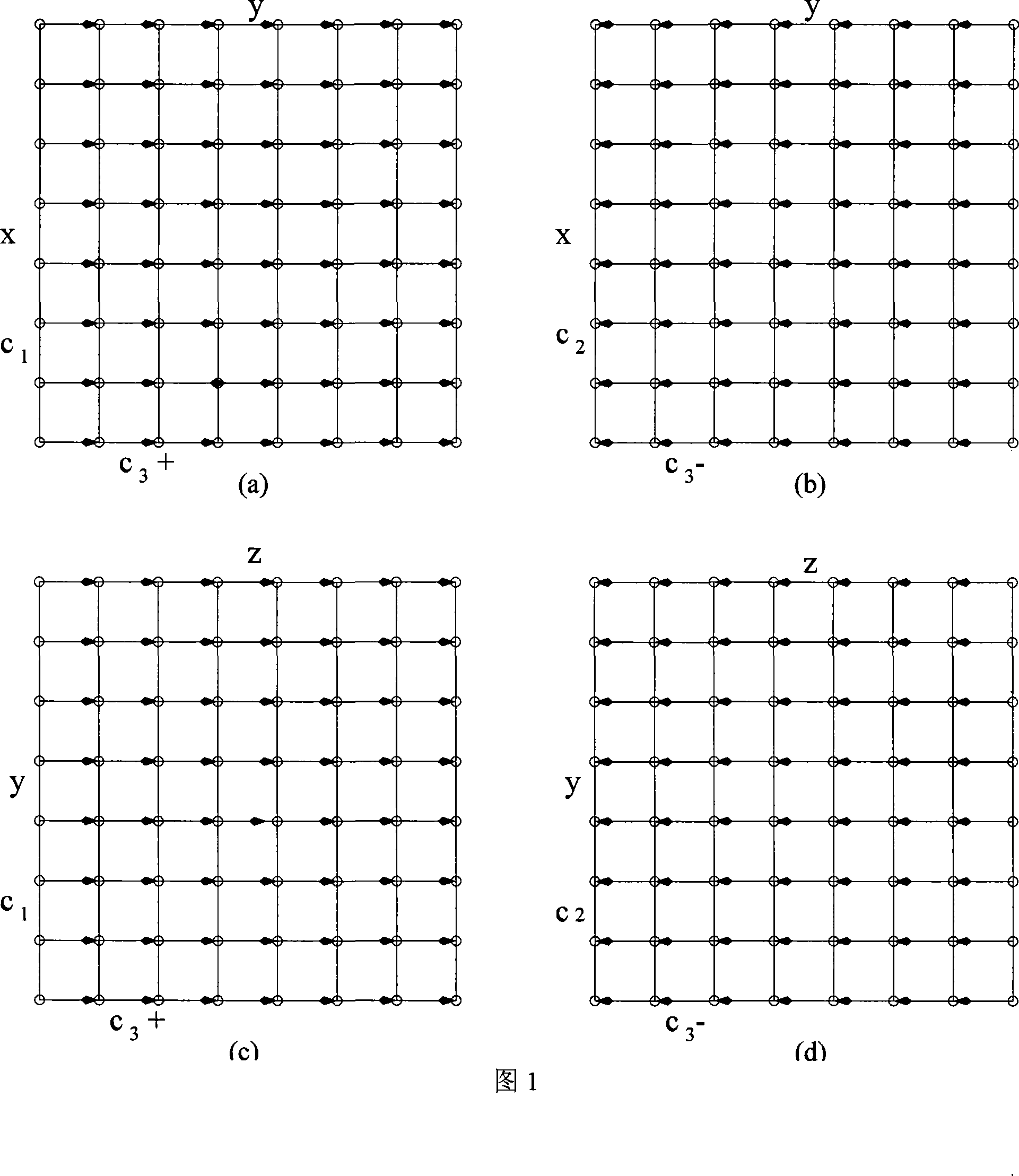

Non lock routing method for k-element N-dimension mesh

InactiveCN101242372AHigh trafficImprove transmission performanceData switching networksFault toleranceIdle channel

The invention relates to a deadlock-free routing method in K-ary N-dimension mesh network, belonging to the field of distributed high performance fault tolerant computing technology. Each physical channel between nodes is divided into two virtual channels which are two-way channels and distributed to rising subnet and falling subnet of each plane in N-dimension mesh network. The method avoids deadlock which may be formed between arbitrary adjacent planes by overlapping technology, and reaches highest adaptability by the highest dimension idle channel; the smallest connecting component created by planes on the basis further improves fault-tolerance performance. Compared with traditional PAR method and Gomez method, as standard input load and network fault node number increased, the invention can obviously improve network actual flow and reduce transmission delay, thus improving the transmission performance of the whole network.

Owner:TSINGHUA UNIV

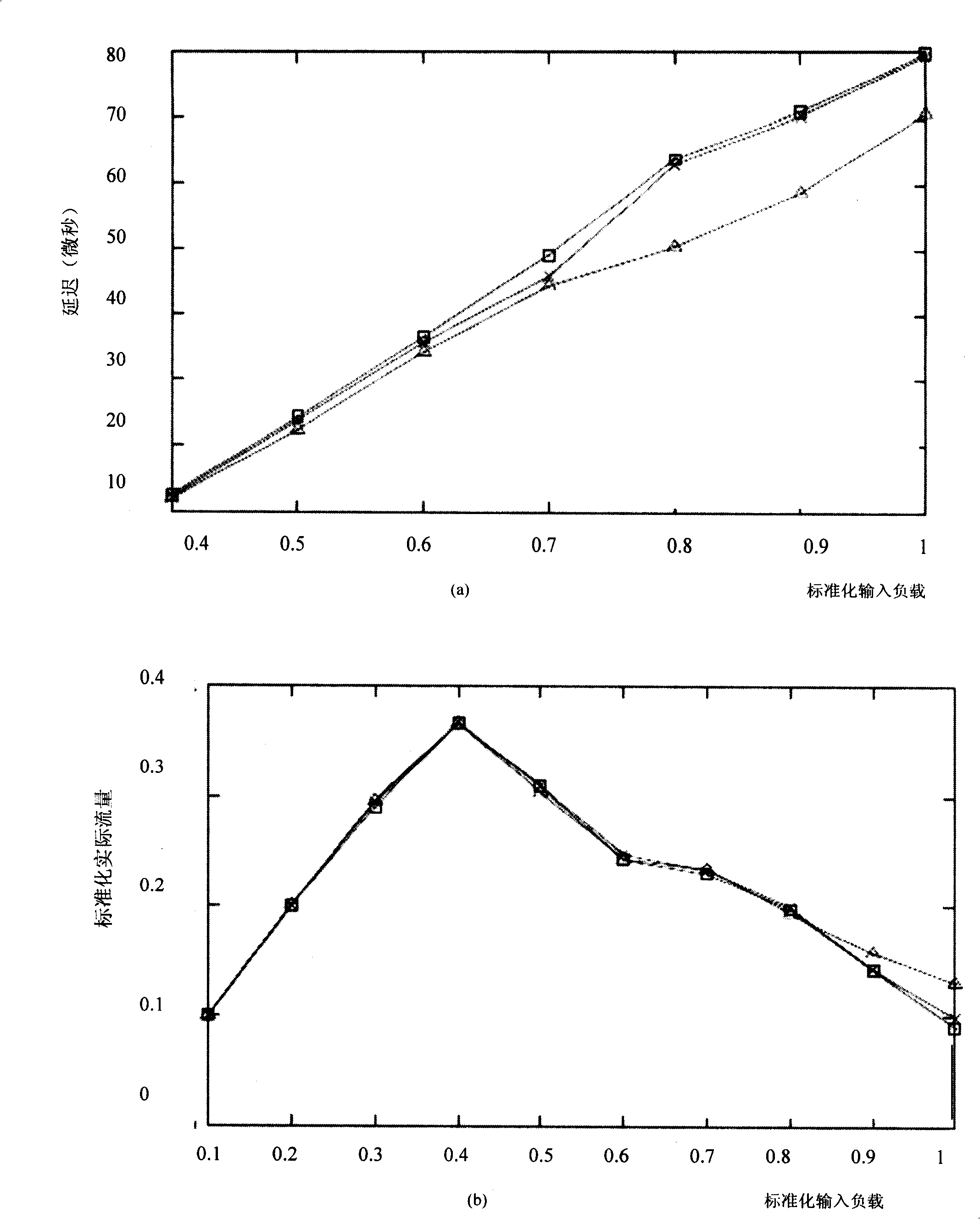

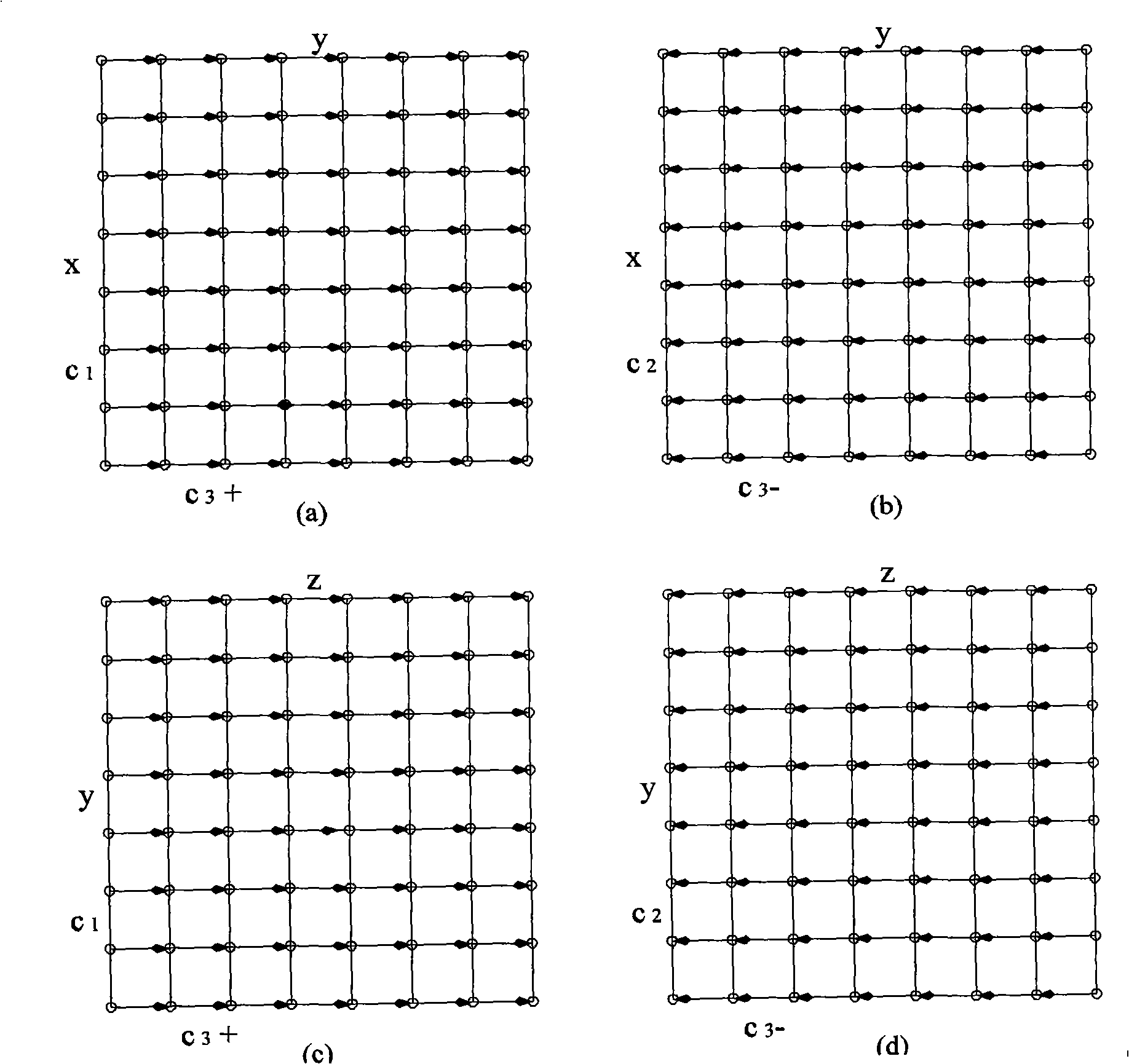

No dead lock plane self-adapted routing method in 3-D mesh

InactiveCN101267394AHigh trafficImprove transmission performanceData switching networksFault toleranceDiagonal

A deadlock free plane self-adapting routing method in a three-dimensional mesh network belongs to the distributing high performance fault tolerance computing technology field, characterized in that each physical passage between nodes are divided into two virtual passages which are both two-way passages; dividing the three-dimensional mesh network into xy and yz planes, each of which is divided into an ascending sub network and a descending sub network, routing on the xy plan from x direction; when an offset in x direction is zero, routing by jumping to the yz plane, a message having degree of freedom in two directions on shortest path to a destination node, selecting a neighboring node that is safe to route; when there is only one candidate direction, routing around in non-shortest path direction, then returning to the shortest path to route; the invention uses a malfunction module to establish a minimal communication component malfunction module for the plane, to respectively search for unsafe nodes in two diagonal directions of each node in the plane, to select safe route in the offset direction between present node and the destination node; the invention improves transmission performance of the network obviously.

Owner:TSINGHUA UNIV

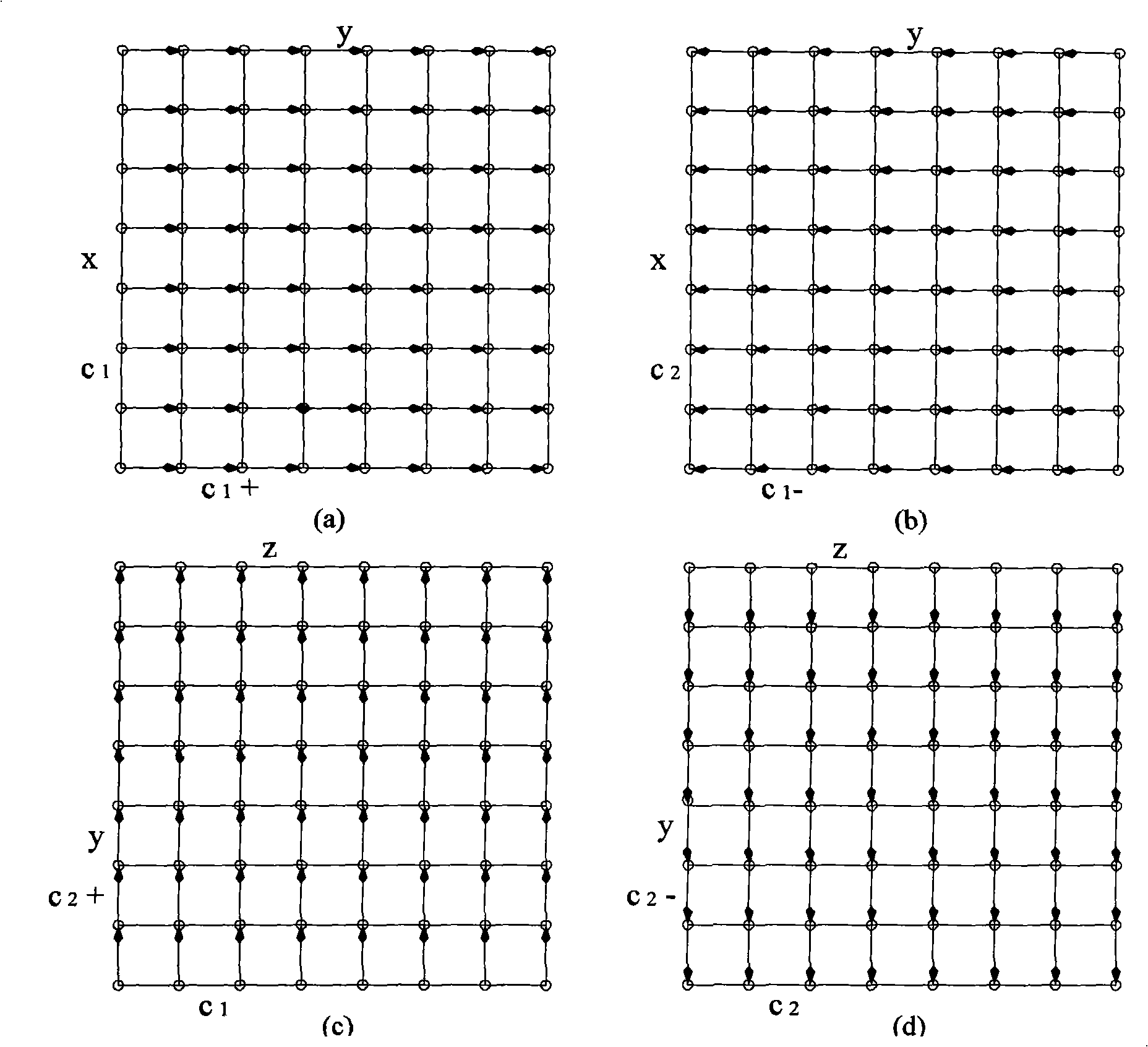

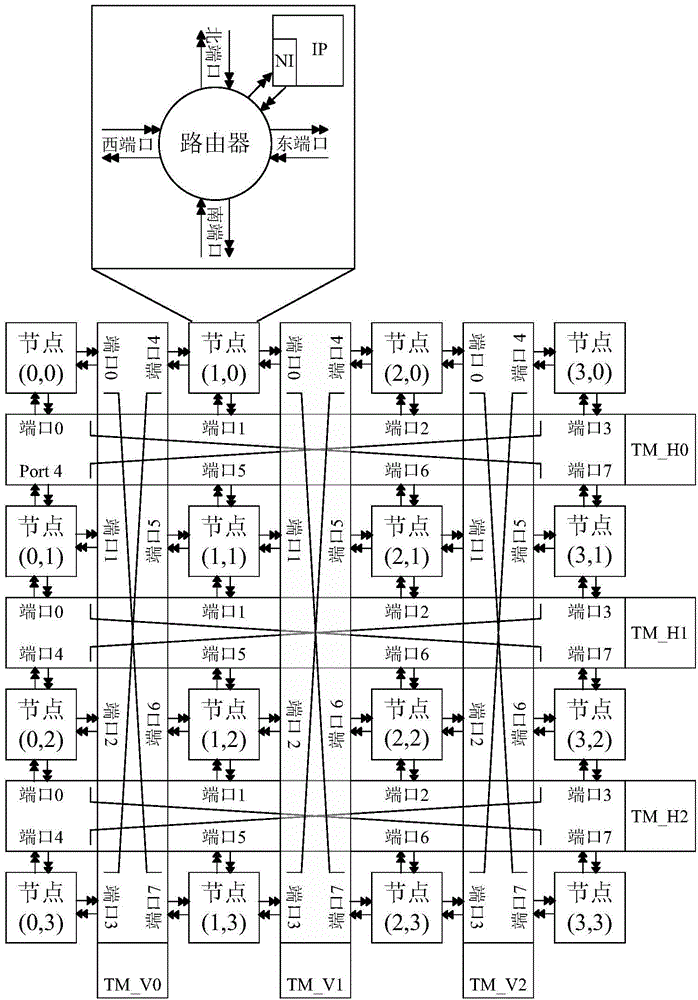

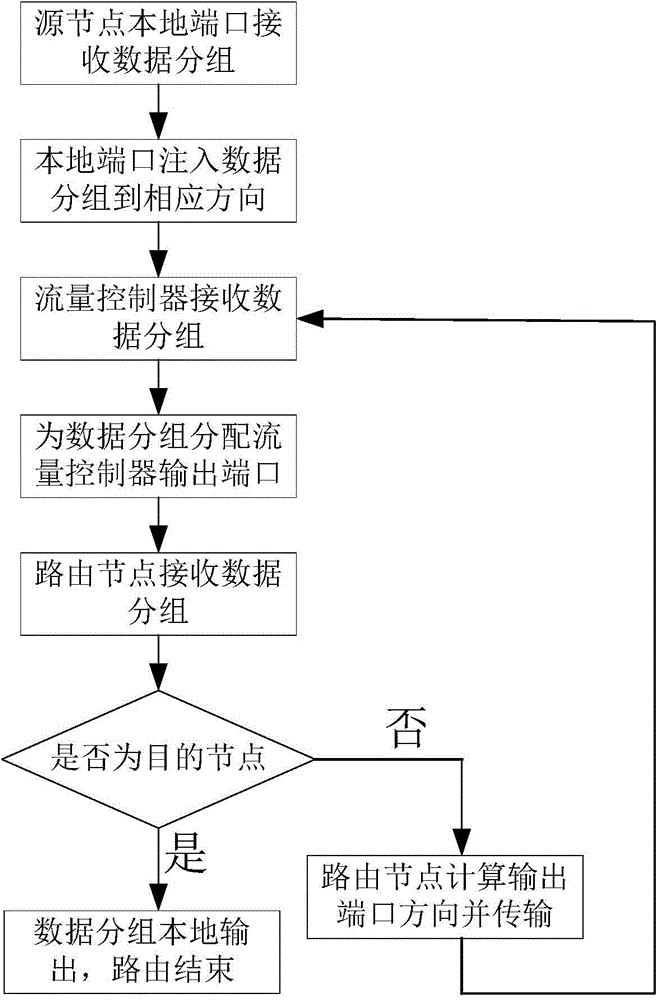

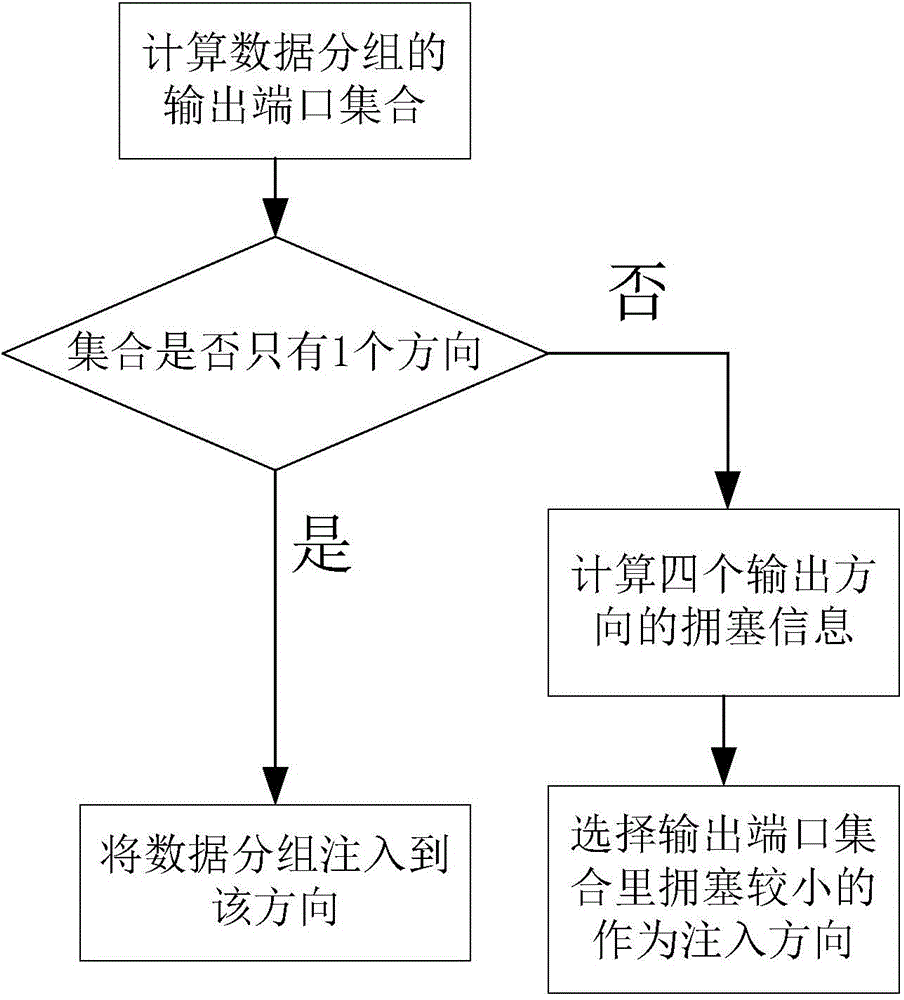

Self-adaptive routing method of two-dimensional network-on-chip topological structure

ActiveCN104901899AReduce congestionImprove performanceArchitecture with single central processing unitData switching networksTraffic capacityStructure of Management Information

The invention discloses a self-adaptive routing method of a two-dimensional network-on-chip topological structure, and is used for solving the problems that a conventional two-dimensional network-on-chip routing method cannot effectively avoid congestion nodes or hardware expenditure is large and efficiency is low and thereby causing low network performance when congestion nodes are avoided. The self-adaptive routing method adopts a method of combining injection direction selection and flow controller output port allocation. Specific steps of the self-adaptive routing method provided by the invention are as follows: 1. a local port of a source node receives a data packet; 2. the data packet is injected; 3. a flow controller receives the data packet; 4. a flow controller output port is allocated; 5. a routing node receives the data packet; 6. whether the routing node is a destination node is judged; 7. the routing node calculates an output port direction; and 8. the data packet is transmitted to a local output port of the destination node. The routing method is a self-adaptive routing method which has a good congestion control capability, is deadlock-free and is small in hardware expenditure.

Owner:XIDIAN UNIV

Automatic deadlock detection and avoidance in a system interconnect by capturing internal dependencies of IP cores using high level specification

InactiveUS20140204735A1Save resource costError preventionFrequency-division multiplex detailsNetworks on chipDeadlock free

Systems and methods for automatically building a deadlock free inter-communication network in a multi-core system are described. The example implementations described herein involve a high level specification to capture the internal dependencies of various cores, and using it along with the user specified system traffic profile to automatically detect protocol level deadlocks in the system. When all detected deadlock are resolved or no such deadlocks are present, messages in the traffic profile between various cores of the system may be automatically mapped to the interconnect channels and detect network level deadlocks. Detected deadlocks then may be avoided by re-allocation of channel resources. An example implementation of the internal dependency specification and using it for deadlock avoidance scheme is presented on Network-on-chip interconnects for large scale multi-core system-on-chips.

Owner:INTEL CORP

Identification of internal dependencies within system components for evaluating potential protocol level deadlocks

InactiveUS20150016257A1Error preventionFrequency-division multiplex detailsParallel computingDeadlock free

Systems and methods for automatically building a deadlock free inter-communication network in a multi-core system are described. The example implementations described herein involve automatically generating internal dependency specification of a system component based on dependencies between incoming / input and outgoing / output interface channels of the component. Dependencies between incoming and outgoing interface channels of the component can be determined by blocking one or more outgoing interface channels and evaluating impact of the blocked outgoing channels on the incoming interface channels. Another implementation described herein involves determining inter-component communication dependencies by measuring impact of a deadlock on the blocked incoming interface channels of one or more components to identify whether a dependency cycle is formed by blocked incoming interface channels.

Owner:INTEL CORP

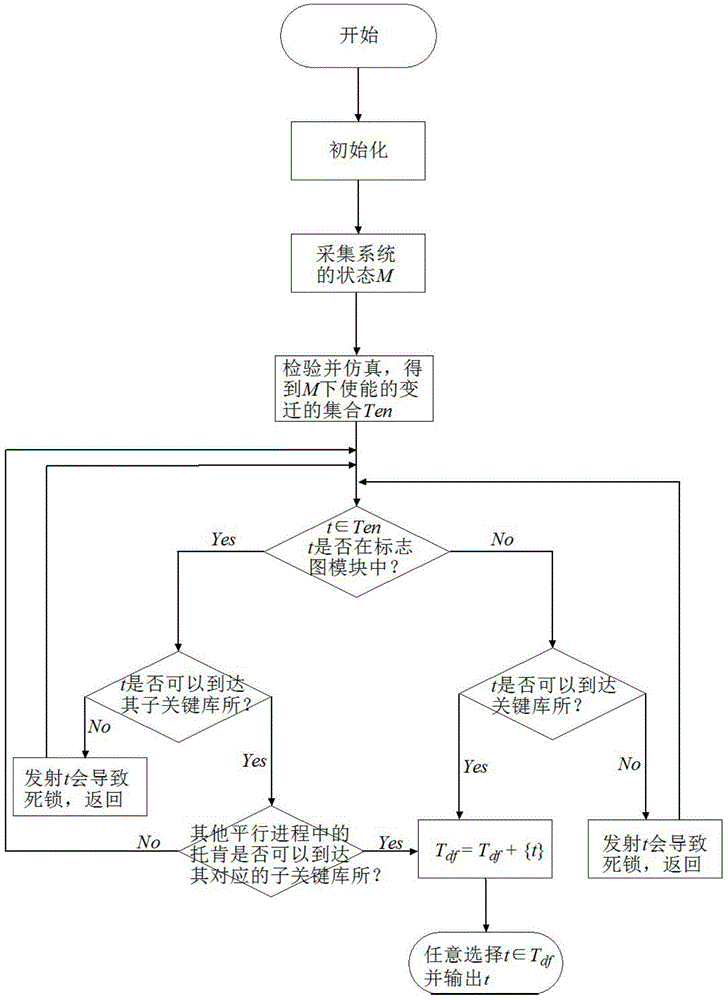

Distributed control method of automatic manufacturing system

ActiveCN105184385AEnsure deadlock-freeDeadlock-free guaranteeForecastingTotal factory controlDeadlock freeMachining

The invention relates to an automatic manufacturing system for inserting assembly operation into a flexible machining path, in particular, a distributed control method of the automatic manufacturing system. The method includes the following steps that: a set Ten of enabling transitions is obtained according to the current state of the system; whether each element in Ten can ensure deadlock-free operation of the system is judged, and judgment is carried out through the following manners that: a transmitting element t is simulated, and t belongs to Ten, and according to the position of t, if current resources can support corresponding tokens to arrive at key libraries / sub key libraries of a key library unity, it requires to ensure that the tokens of other parallel processes of assembly operation can all arrive at respective sub key libraries corresponding to the tokens according to the condition of the key library unity, and therefore, t belongs to Tdf; and after all transitions are detected, Tdf is obtained, and the transmitting element t belongs to Tdf, and the method enters a next state, re-judgment is carried out. With the distributed control method of the invention adopted, the system can be free of deadlock assuredly, and high permissibility can be obtained as far as possible, and prediction and control can be carried out simultaneously, and real-time and online control can be realized.

Owner:XIDIAN UNIV

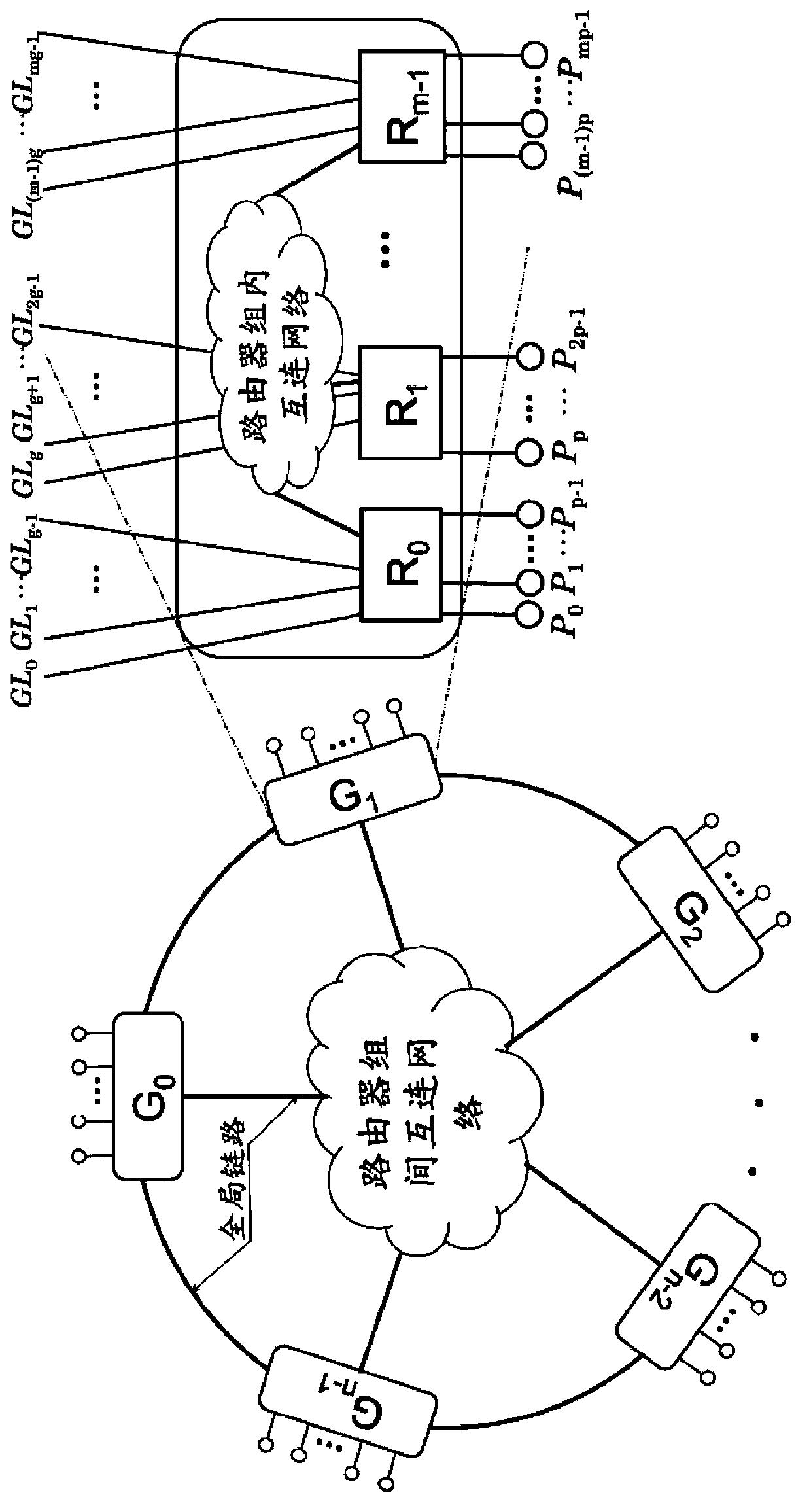

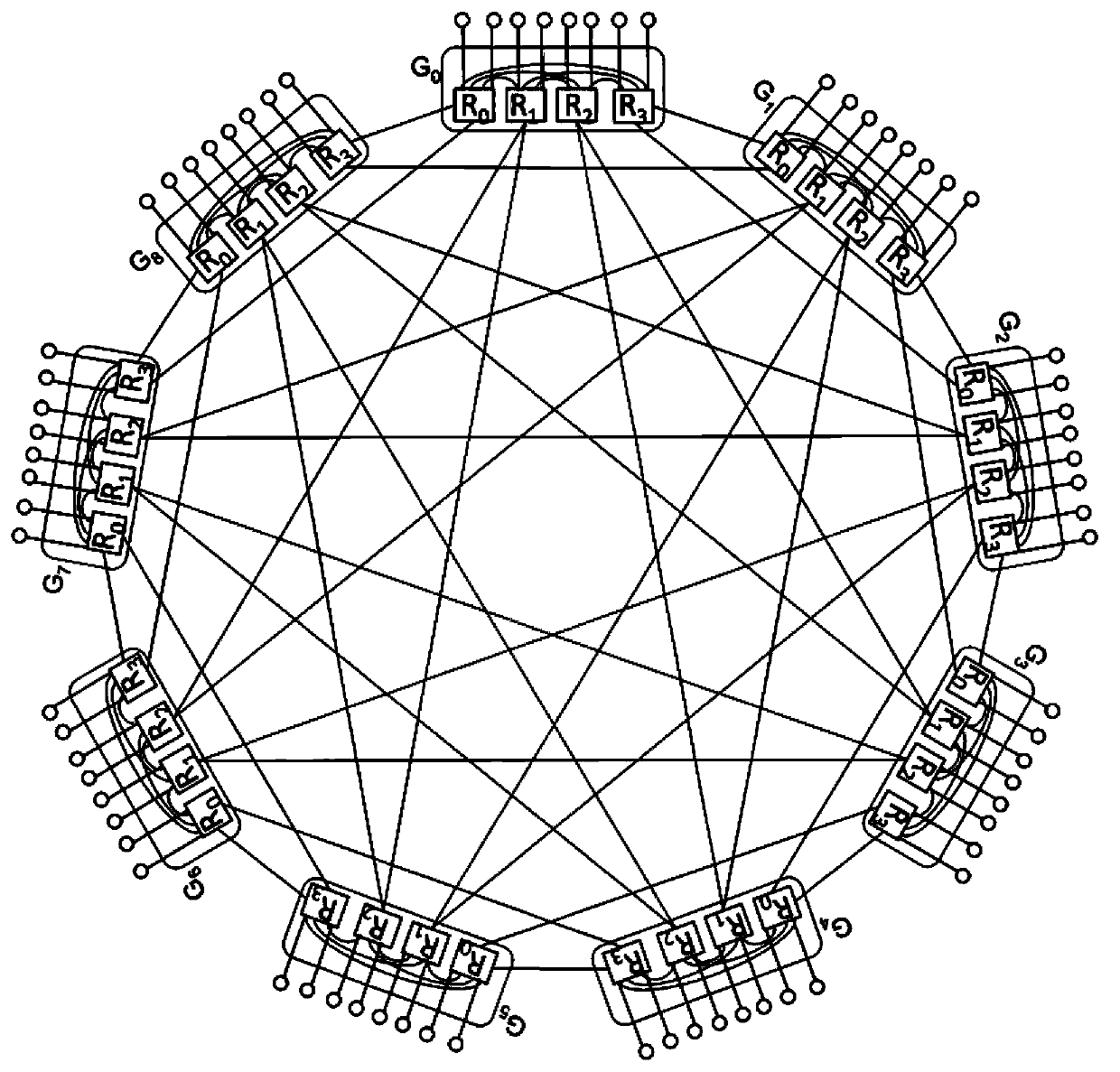

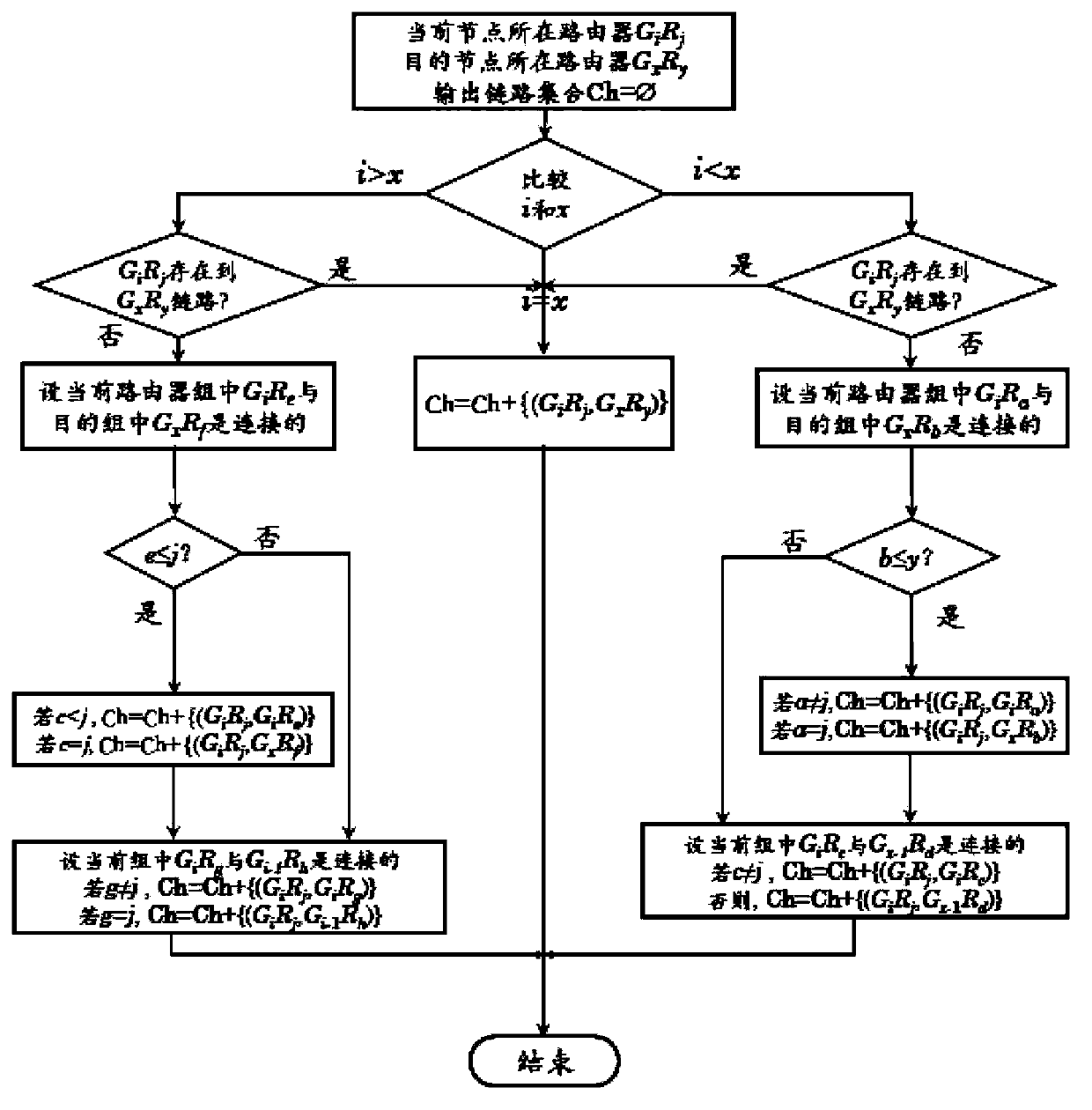

Interconnection network system and self-adaptation routing method

The invention discloses an interconnection network system. The system is characterized in that routers in the system is divided into n router groups which are in complete connection, and each router group comprises one or more routers which are in complete connection. A self-adaptation routing method based on the novel interconnection network system is characterized in that the routers in the system are labeled, deadlock-free partial self-adaption routing can be achieved by special label decreasing direction priority algorithms or label increasing direction priority algorithms without using virtual passages, and the communication step length between optional processor nodes is not more than five. The invention further provides a complete self-adaptation routing method, deadlock-free complete self-adaptation routing can be achieved by utilizing the deadlock-free characteristics of the partial self-adaptation routing method aided by a novel flow control mechanism.

Owner:TSINGHUA UNIV

Deadlock-free routing of data packets in fat tree networks

ActiveCN103873367AAvoid deadlockLoad balancingData switching networksDeadlock freeReal-time computing

Deadlock-free routing of data packets between source and destination switches in a fat tree network is provided. For each packet, a route is selected having three or less routing phases such that the route follows a shortest path across the network between the source and destination switches. The data packet is transmitted from the source switch to the destination switch, via the route, on one of first and second virtual channels unless the route includes a predetermined one of a down-up turn and an up-down turn (see e.g. figures 7 and 8). If the route includes the predetermined turn, the data packet is transmitted, via the route, on the first virtual channel up to the switch at which the turn occurs and on the second virtual channel from that switch. Direct fat tree networks, in which end nodes are connected to switches in a plurality of levels of the fat tree topology, are also provided.

Owner:IBM CORP

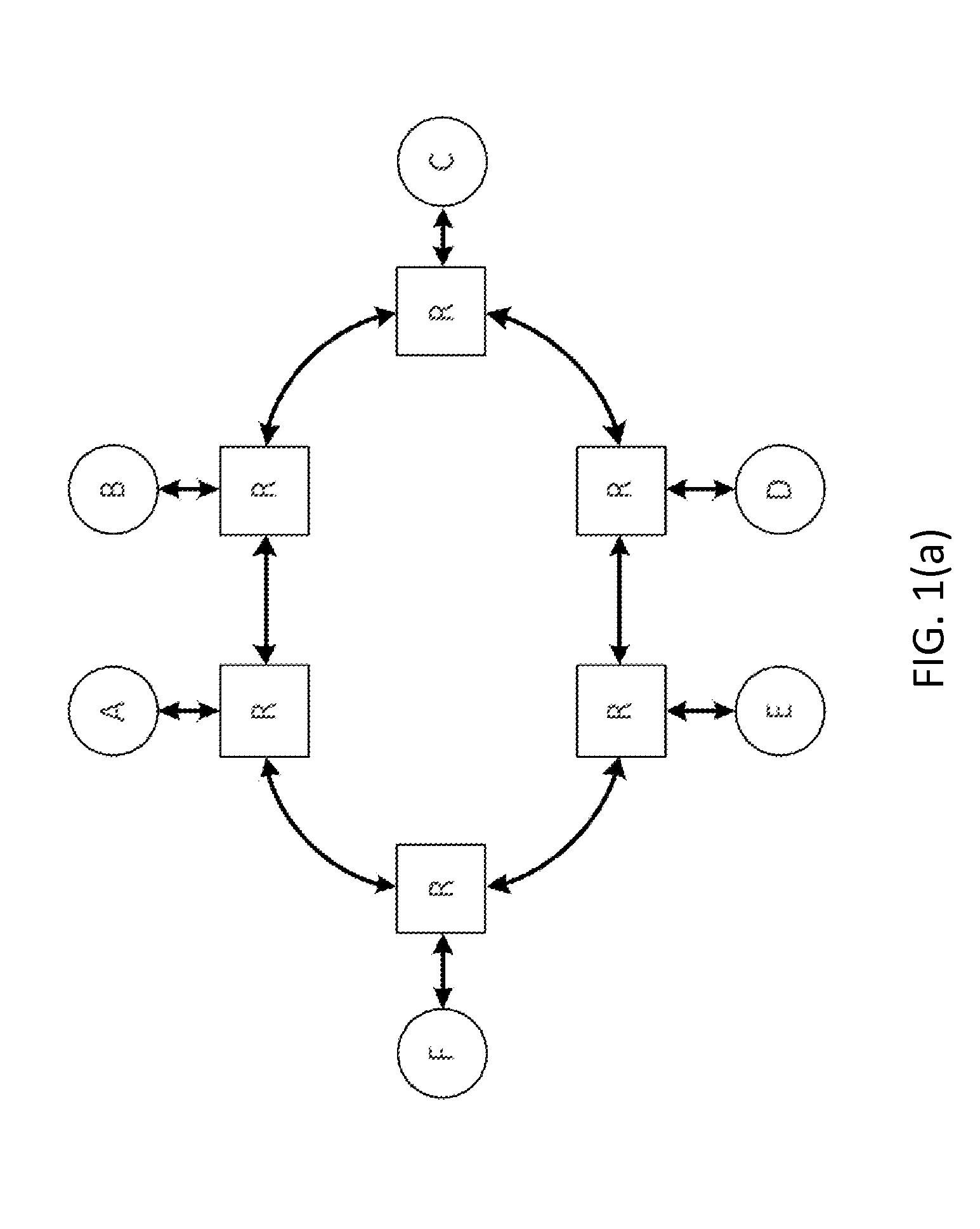

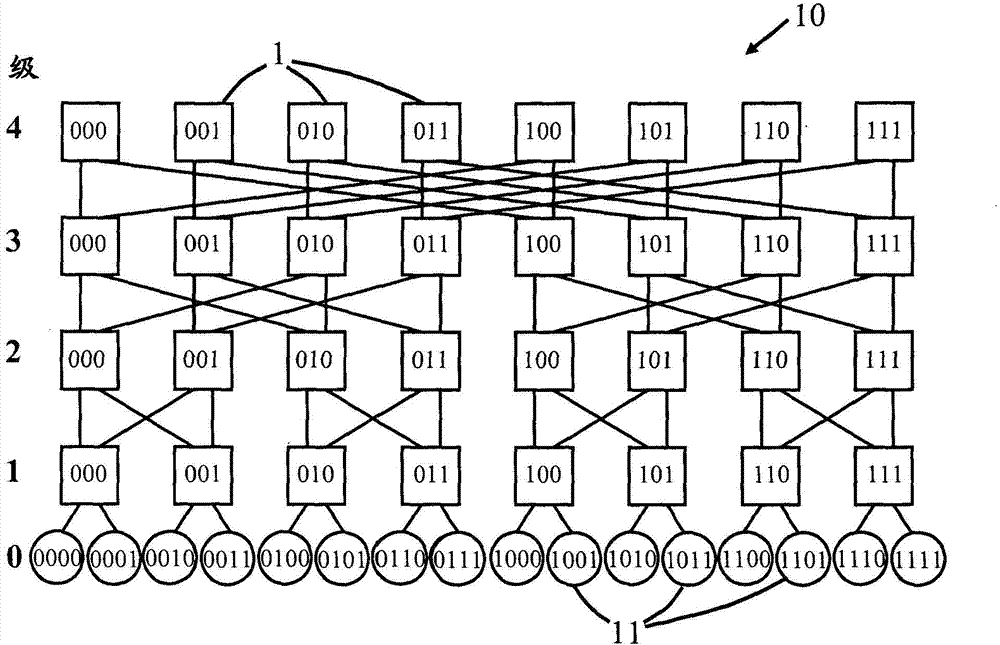

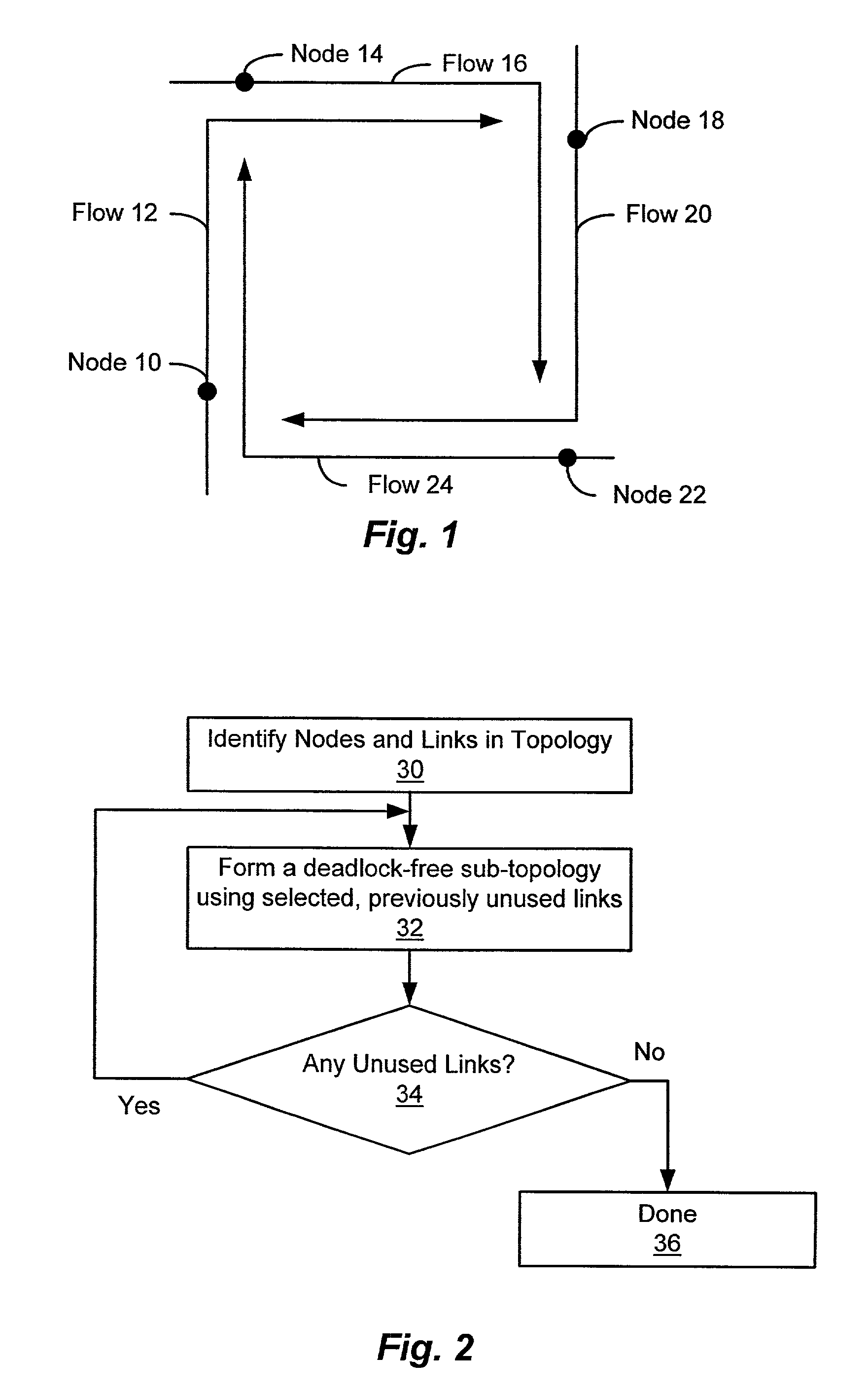

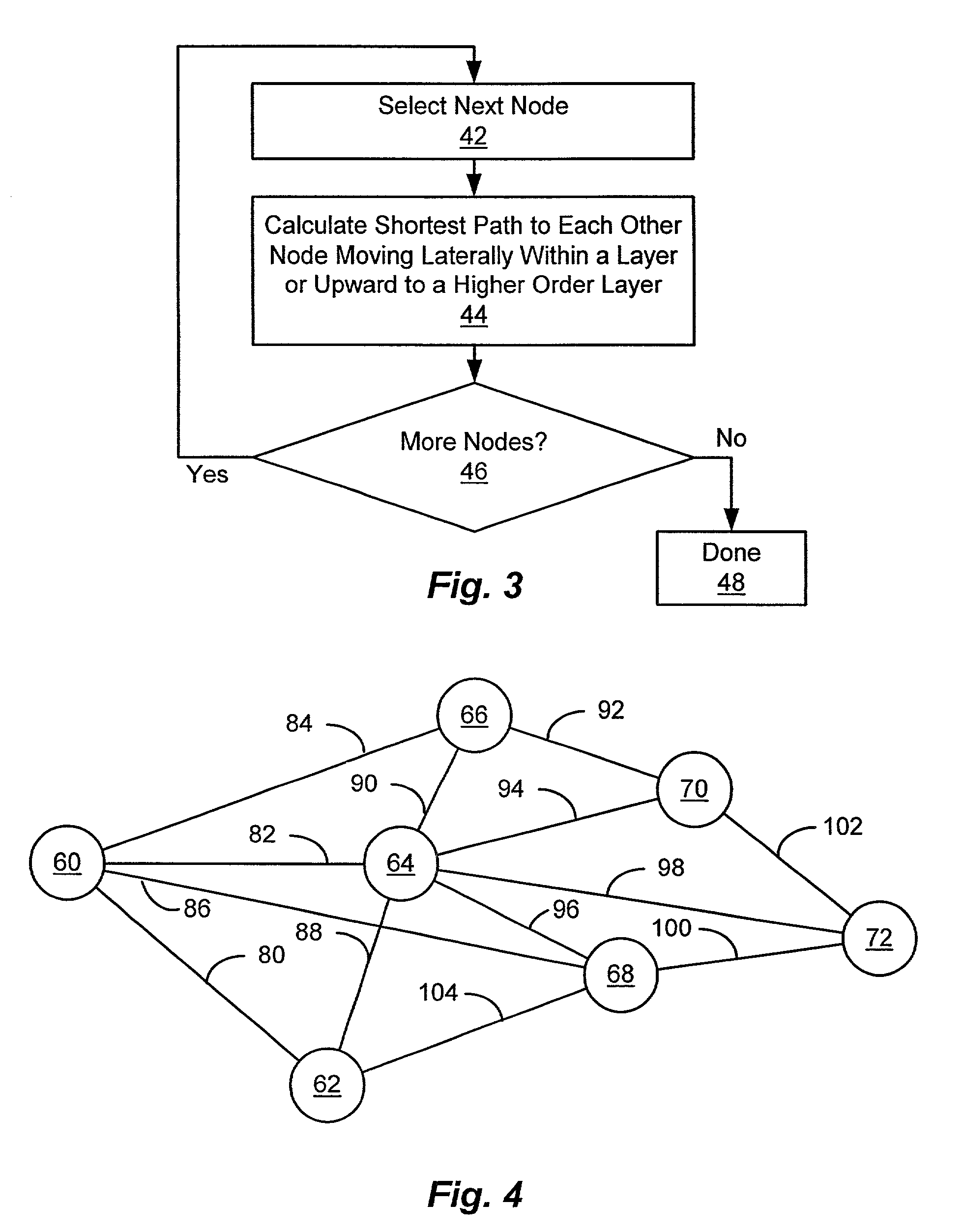

System and method for deadlock-free routing on arbitrary network topologies

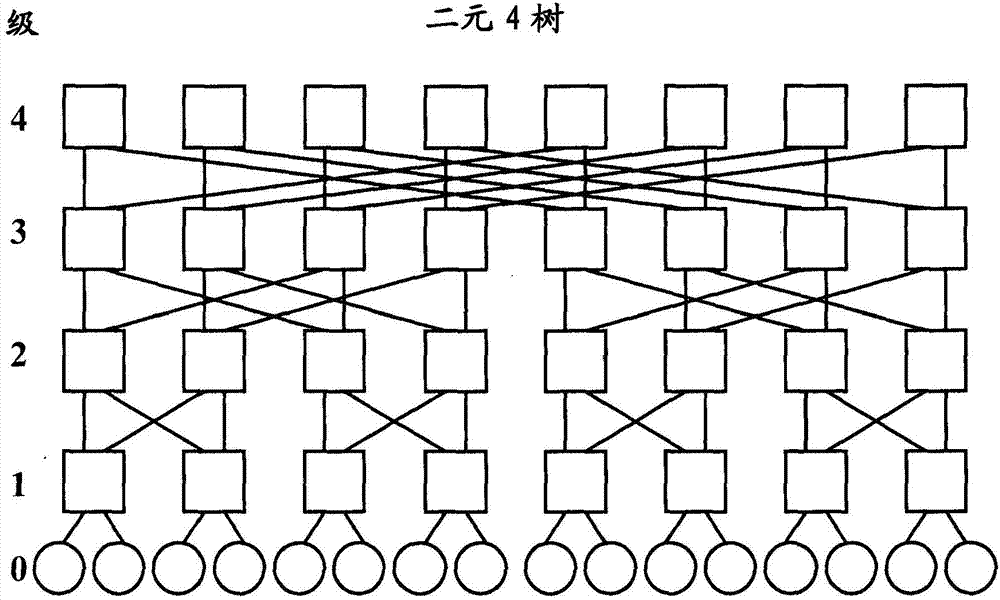

ActiveUS6992988B2Avoid deadlockMultiplex system selection arrangementsData switching by path configurationDeadlock freeOrder set

A system and method for calculating a deadlock-free free set of paths in a network generates an ordered set of deadlock-free sub-topologies, referred to as “layers.” The ordered set of layers is then used to determine a deadlock-free set of paths through the network by performing a shortest-path route calculation with the following constraint: starting at any given layer, for each node, proceed to calculate a shortest path to every other node in the graph where, at any node being utilized to assess a given minimum path, the path may move to any higher-ordered layer, but may not return to a lower-ordered layer.

Owner:ORACLE INT CORP

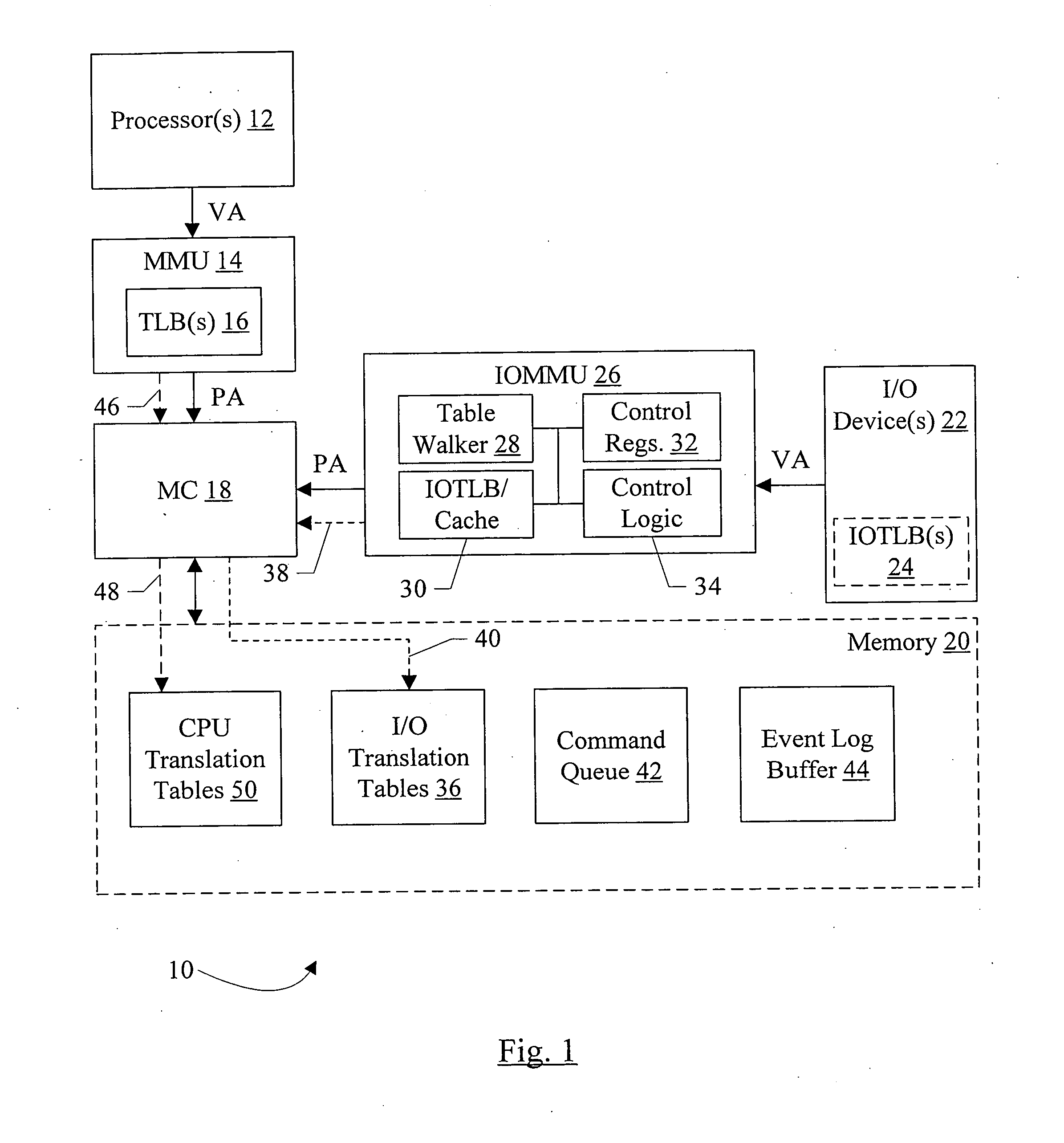

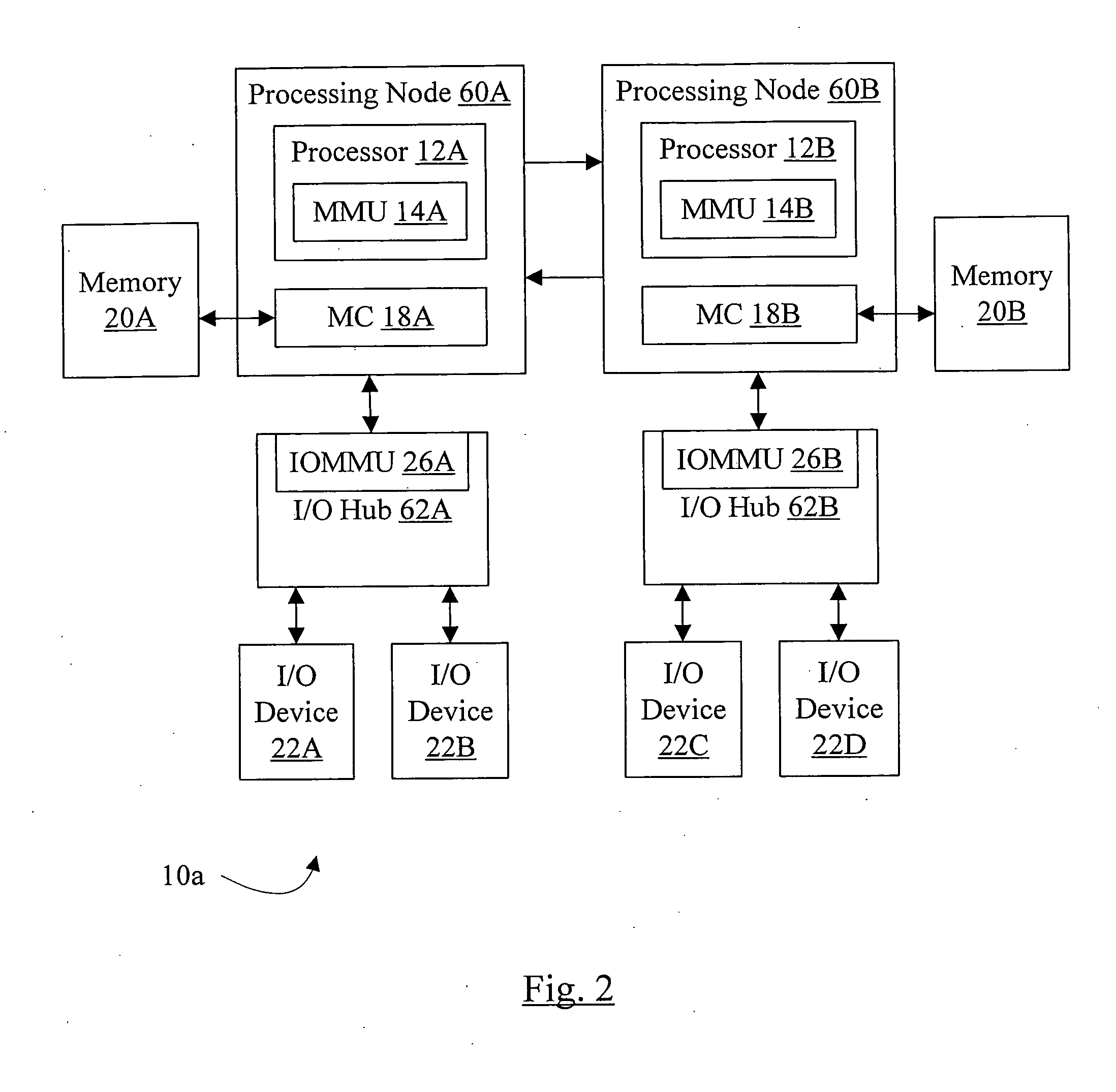

Ensuring deadlock free operation for peer to peer traffic in an input/output memory management unit (IOMMU)

ActiveUS20070038799A1Memory adressing/allocation/relocationMicro-instruction address formationManagement unitTerm memory

In one embodiment, an input / output memory management unit (IOMMU) comprises a cache to cache translation data from memory; and a control unit coupled to the cache. The control unit is configured to implement address translation and memory protection for memory requests sourced by one or more input / output (I / O) devices. The memory requests sourced by the I / O devices travel in one or more first virtual channels, and the control unit is configured to transmit memory requests sourced by the control unit in at least a second virtual channel separate from the first virtual channels.

Owner:ADVANCED MICRO DEVICES INC