Multiple real-time reconfiguration adaptor used in test of field-programmable gate array device

A gate array and reconfiguration technology, applied in measurement devices, instruments, measurement circuits, etc., can solve problems such as low test efficiency, volatile power-down, configuration download, etc., to improve test efficiency and reduce configuration time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

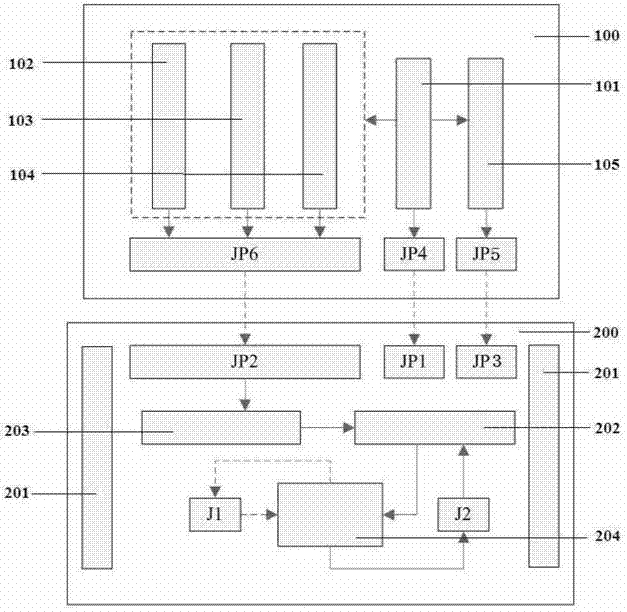

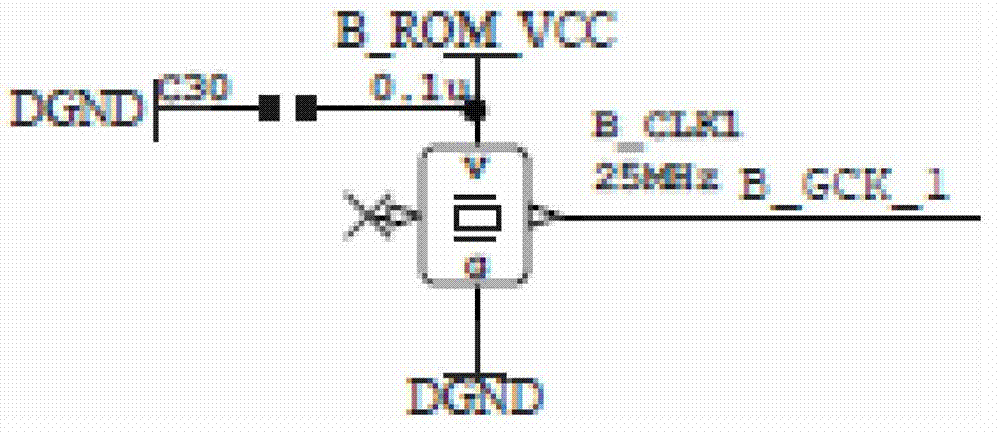

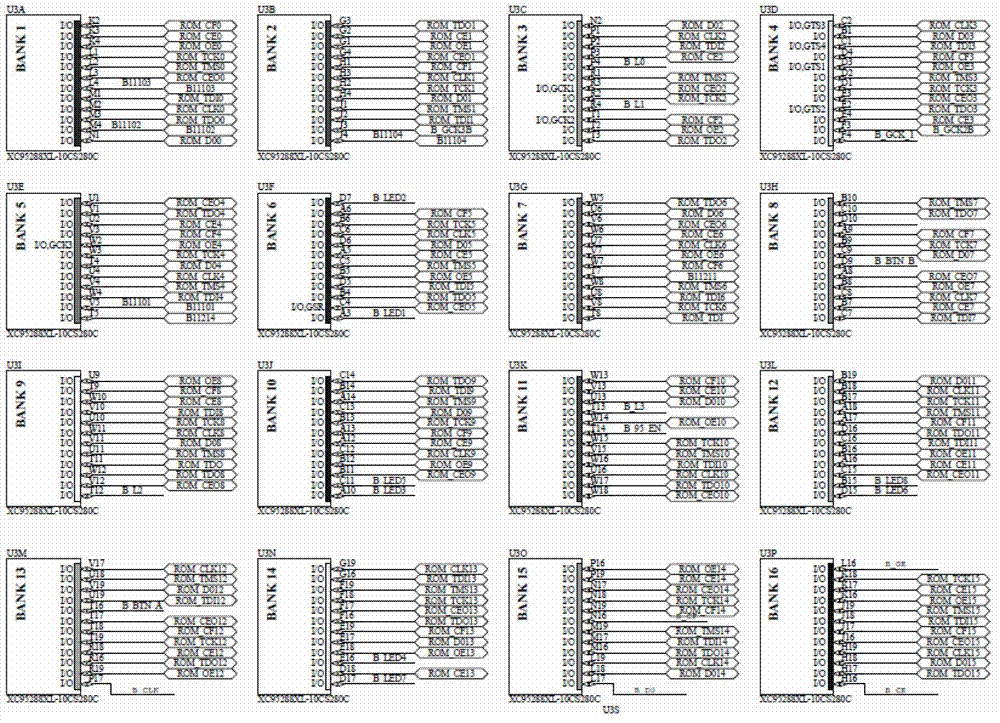

[0021] The multiple real-time reconfiguration adapter for field programmable gate array device testing described in the embodiment of the present invention includes two parts: a development support board and a configuration test board. Among them, the main function of the development support board: when the configuration file (that is, the EDA code) generated after programming the programmable logic resources of the field programmable gate array device is downloaded from the microcomputer to the configuration memory array through the JTAG interface, the development support The board is connected to the side of the configuration test board to provide power supply, clock input signal, configuration control signal, field prog...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More