Low-expenditure distributing structure and distributing method of network-on-chip router

An on-chip network and router technology, applied in the field of communication, can solve the problems of bandwidth limitation, repeatability, and the bus cannot support simultaneous communication of IP cores, etc., so as to avoid repeatability and reduce area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with the accompanying drawings.

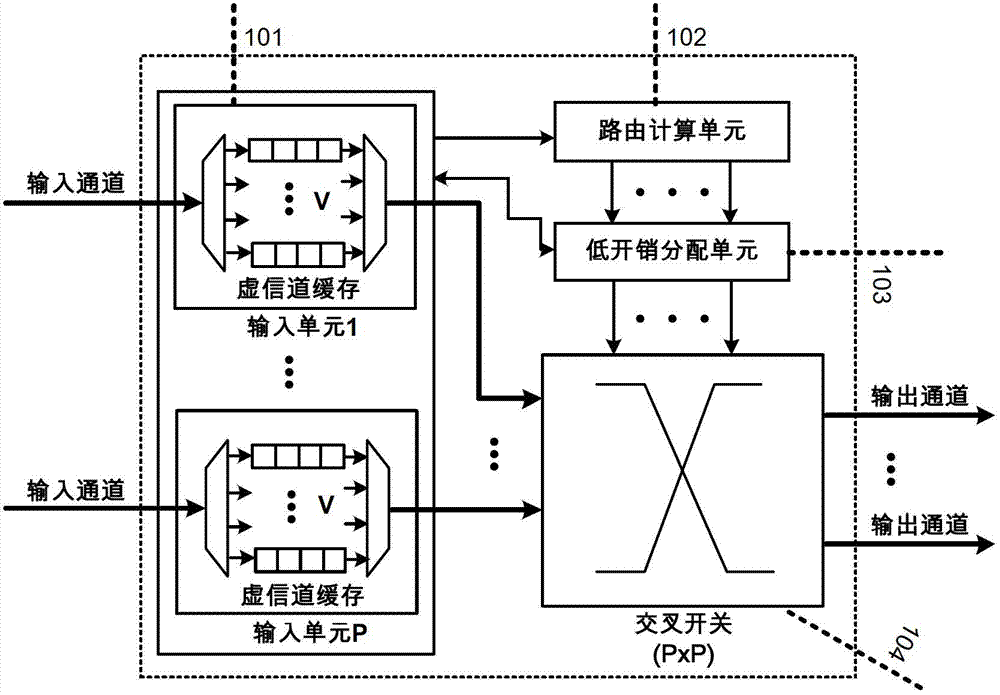

[0029] see figure 1 , the virtual channel router of the present invention includes P input units 101, a routing calculation unit 102, a low-overhead distribution unit 103 and a crossbar switch 104, and the difference from the traditional virtual channel router is that the traditional virtual channel router consists of P The input unit, a routing calculation unit, a virtual channel allocation unit, a switch allocation unit and a crossbar switch, wherein the virtual channel allocation and switch allocation are two separate modules, the virtual channel allocation unit and the switch allocation unit constitute the traditional virtual channel allocation unit. channel router allocation structure, and the present invention directly combines virtual channel allocation and switch allocation into one module, that is, the low-overhead allocation unit 103 .

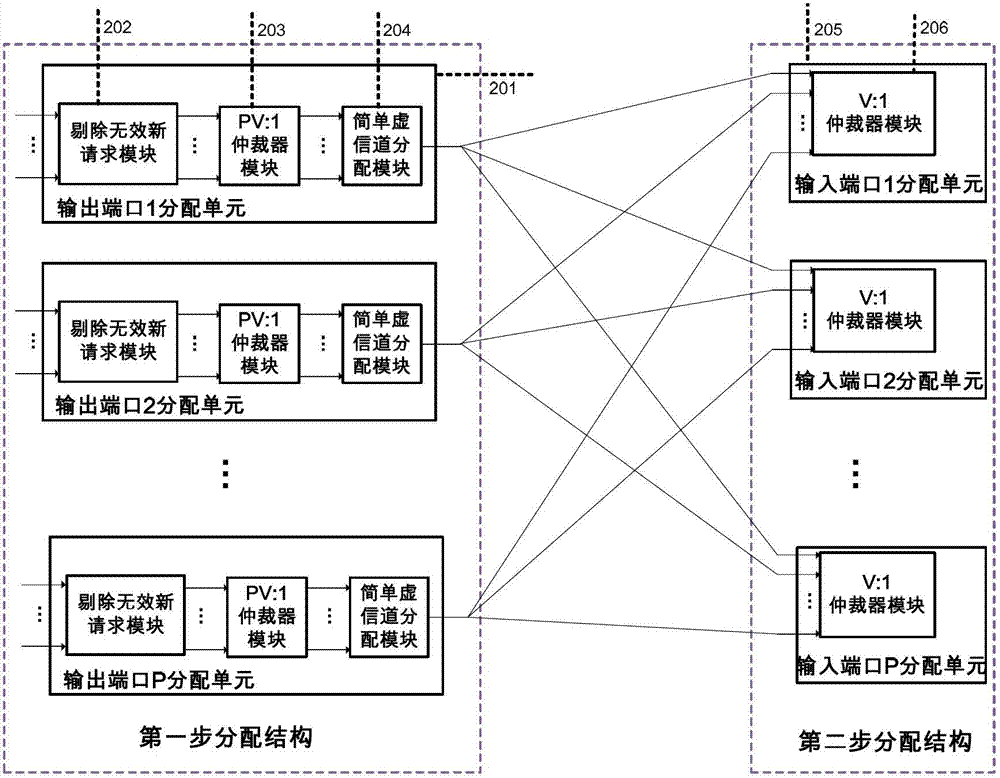

[0030] refer to fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More