Memory output circuit

A transistor and node technology, applied in the field of memory, can solve the problems of time delay of storage data output, multi-time, and reduce the operation speed of the storage output circuit 100, so as to reduce the output delay and improve the operation speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] Certain terms are used in the description and claims to refer to particular components. Those skilled in the art should understand that hardware manufacturers may use different terms to refer to the same component. The specification and claims do not use the difference in name as a way to distinguish components, but use the difference in function of components as a criterion for distinguishing. The "comprising" mentioned throughout the specification and claims is an open term, so it should be interpreted as "including but not limited to". In addition, the term "coupled" herein includes any direct and indirect means of electrical connection. Therefore, if it is described that the first device is coupled to the second device, it means that the first device may be directly electrically connected to the second device, or indirectly electrically connected to the second device through other devices or connection means.

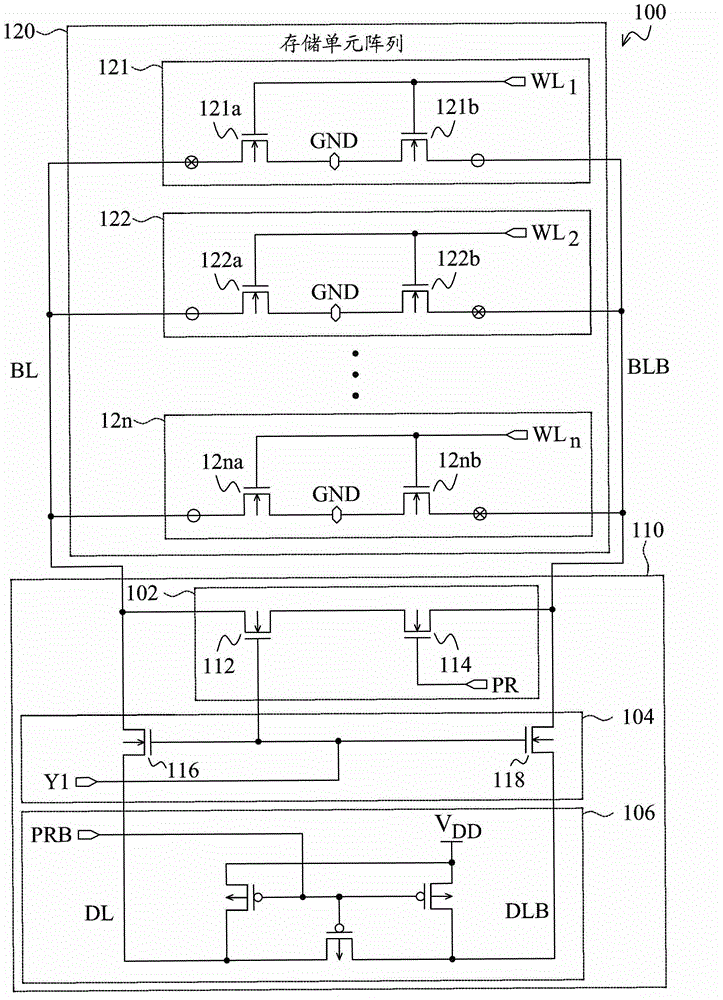

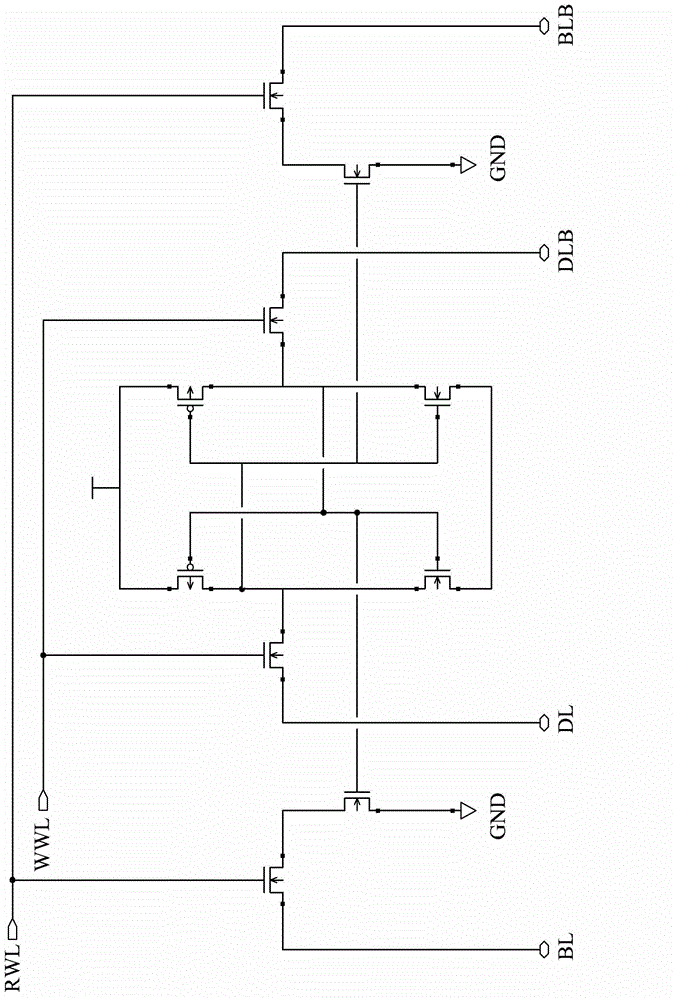

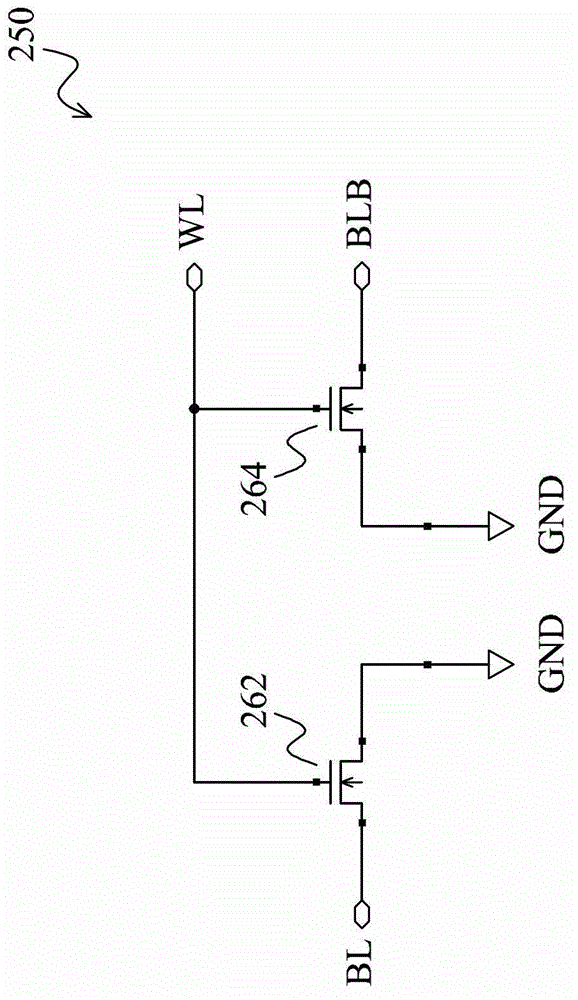

[0018] The invention provides a memory circuit, which...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More