Patents

Literature

47results about How to "Reduce output delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

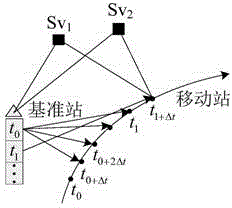

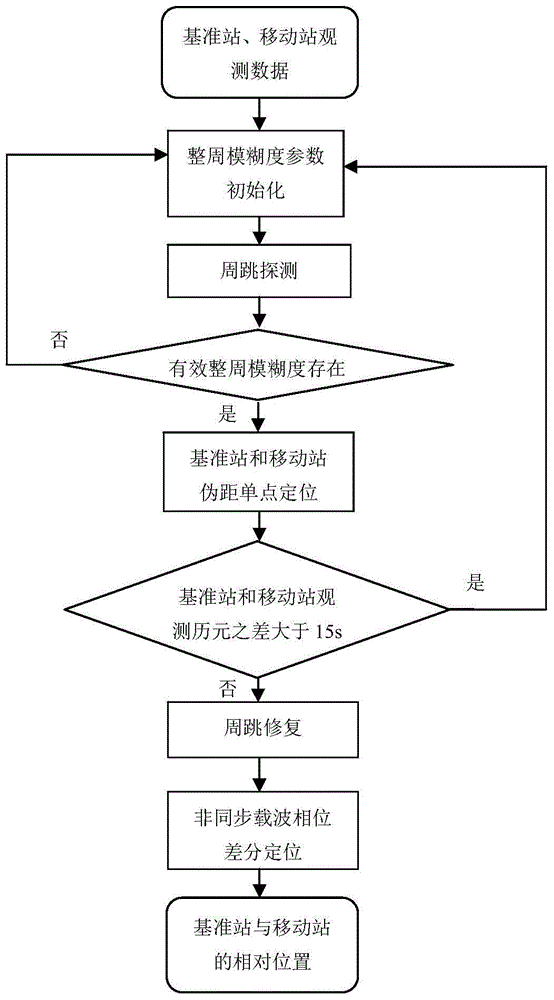

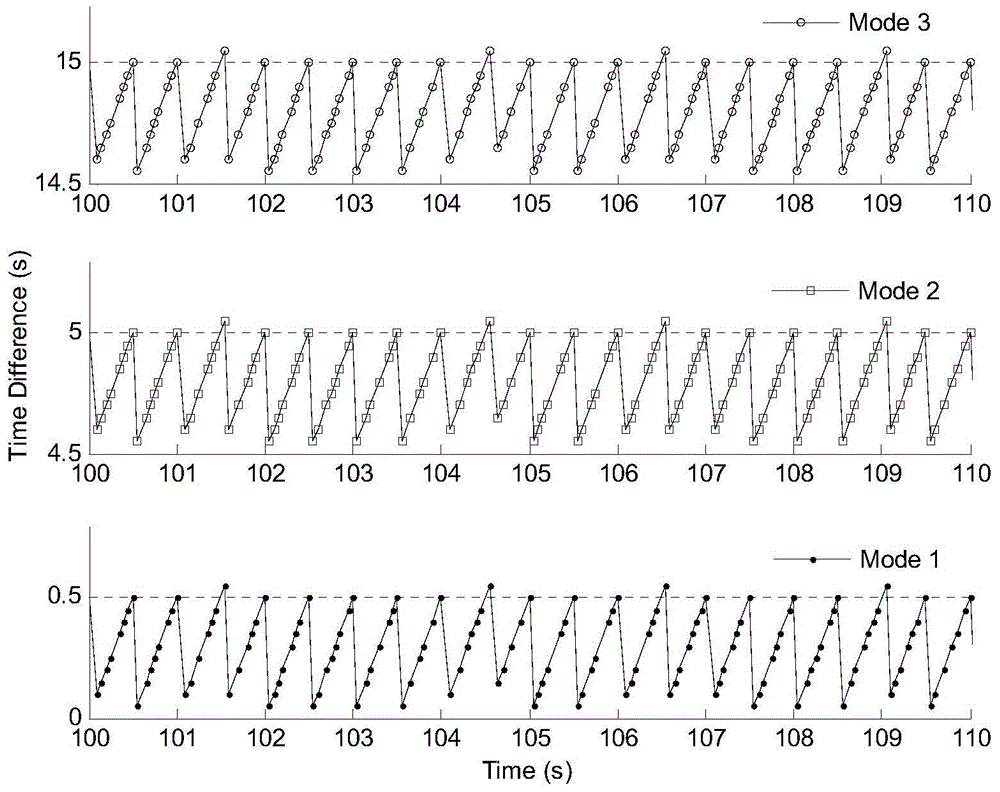

Real-time bayou precision relative positioning method

ActiveCN104536027AImprove real-time update rateReduce output delaySatellite radio beaconingTelecommunications linkAmbiguity

The invention belongs to the satellite positioning field and in particular relates to a real-time bayou precision relative positioning method. The real-time bayou precision relative positioning method particularly comprises the following steps: step I, initializing the integer ambiguity parameter; step II, carrying out cycle-slip detection; step III, performing pseudo-range single-point positioning; step IV, judging the difference of the observation epochs of a base station and a mobile station, calculating the difference of the observation epochs of the base station and the mobile station, if the difference value is more than 15s, returning to the step I, if not, entering the step V; step V, repairing cycle slip, calculating the integer ambiguity of a satellite which is subjected to cycle slip by use of the integer ambiguity of a satellite which is not subjected to cycle slip; step VI, solving the relative location of the base station and the mobile station. According to the method, the dynamic positioning real-time updating rate of the mobile station can be increased, the output delay of the positioning result of the mobile station can be reduced, the base station data is sampled and broadcast at low frequency, the requirements for the real-time performance and the reliability of a data communication link are reduced and the costs of the wireless communication equipment and the links are also reduced.

Owner:NAT UNIV OF DEFENSE TECH

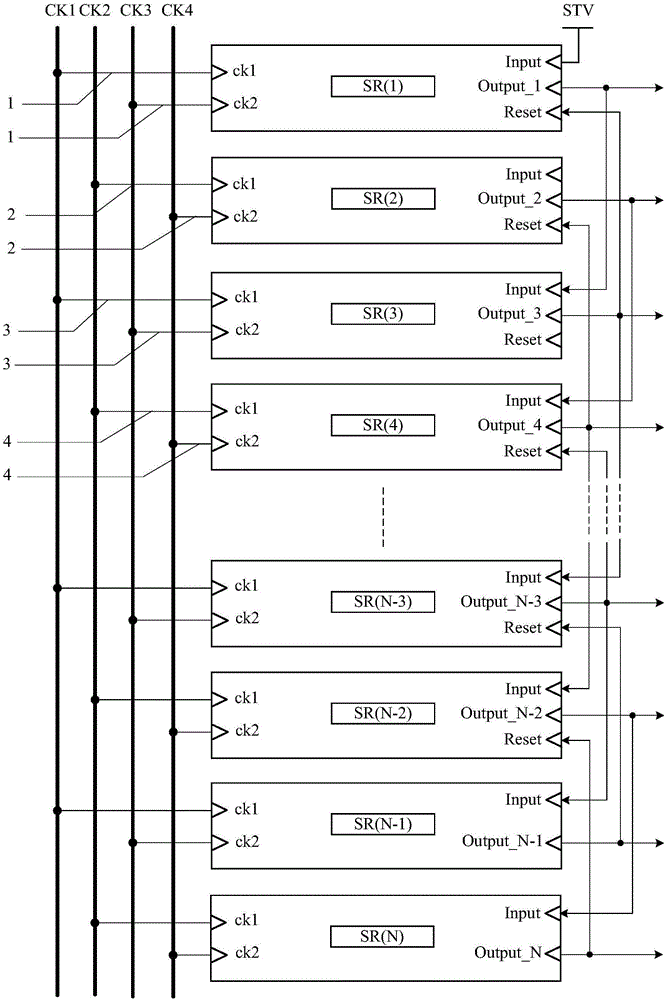

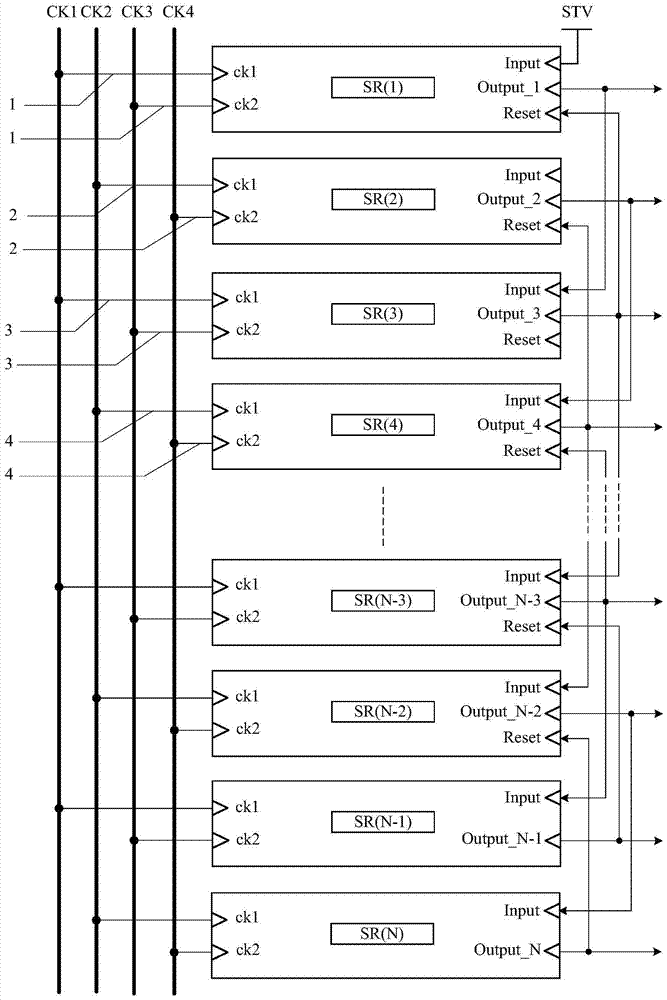

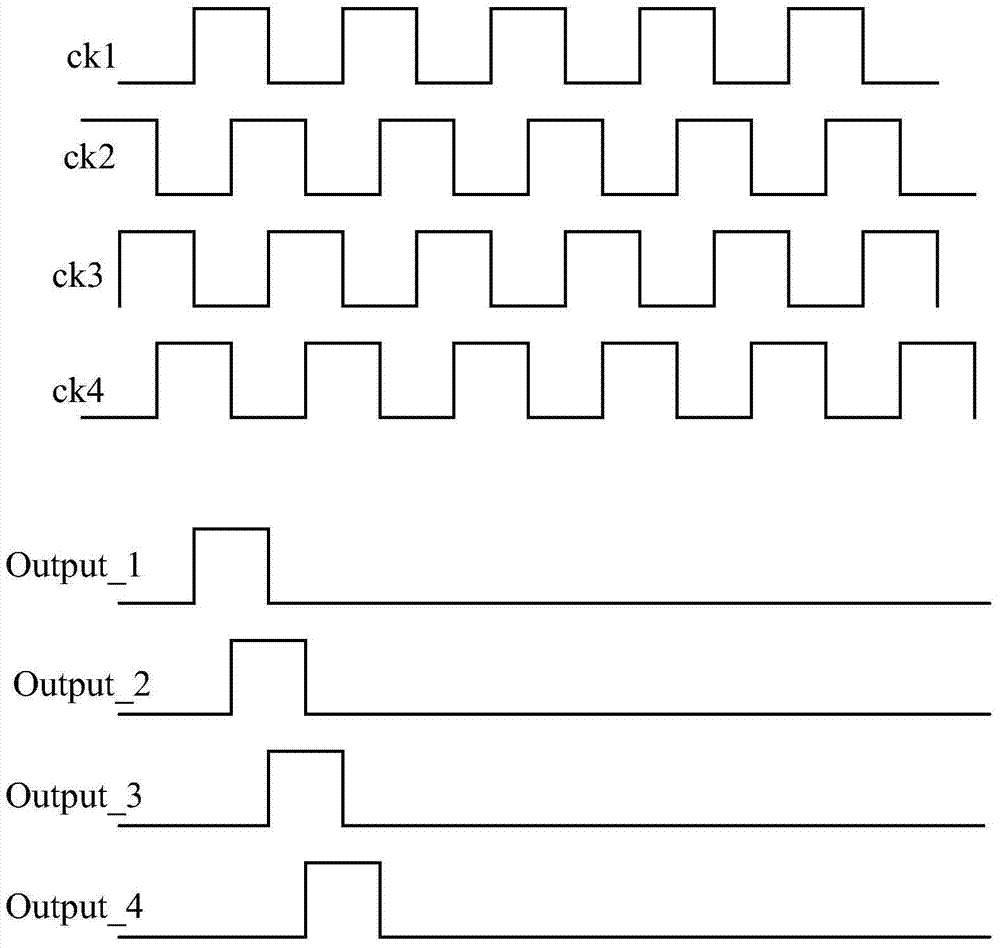

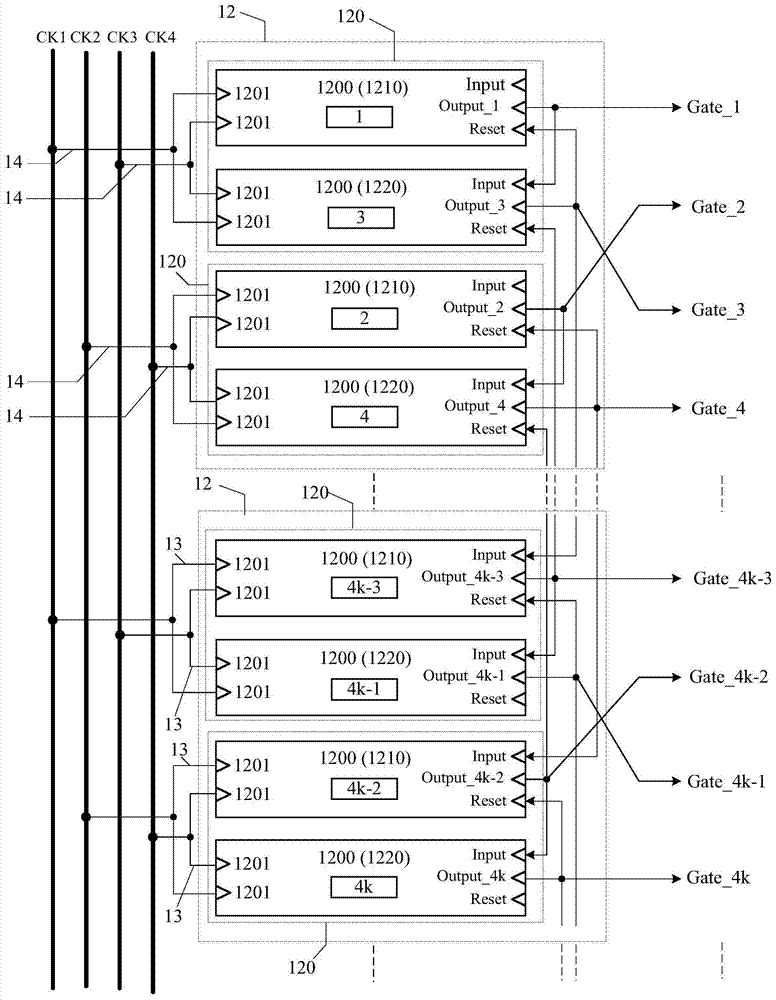

Array substrate, display panel and display device

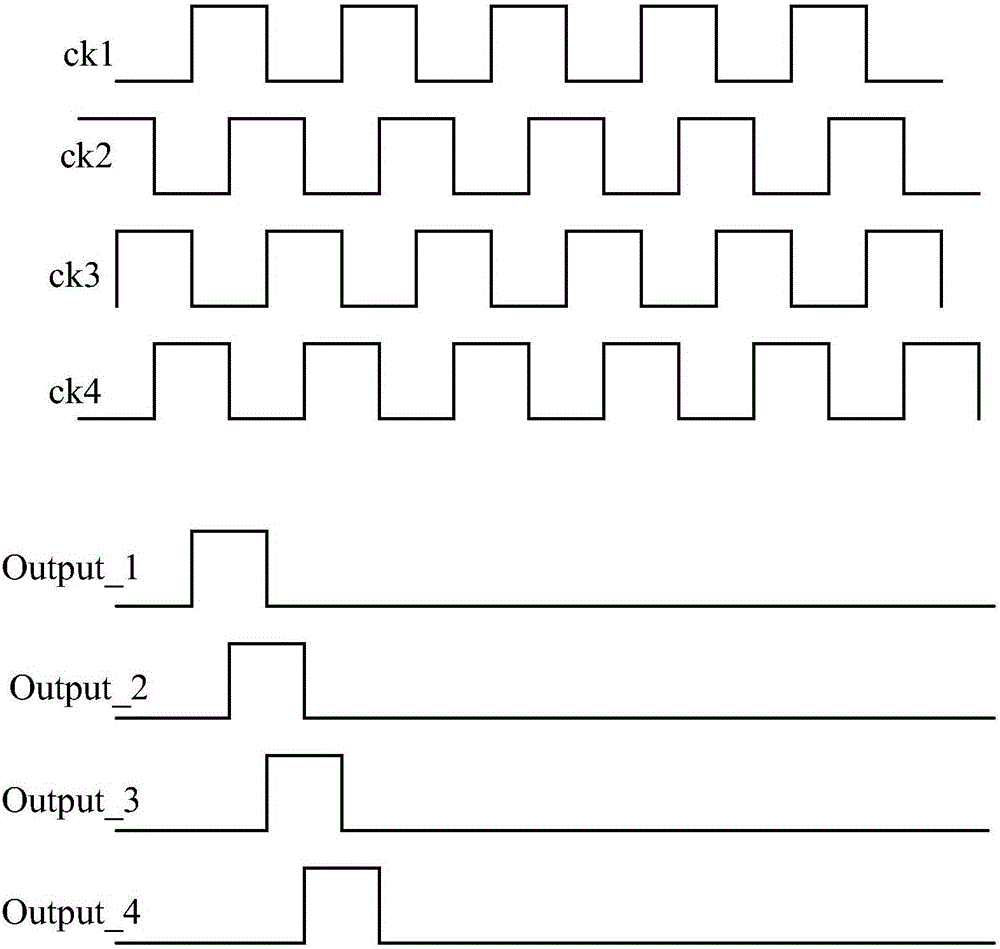

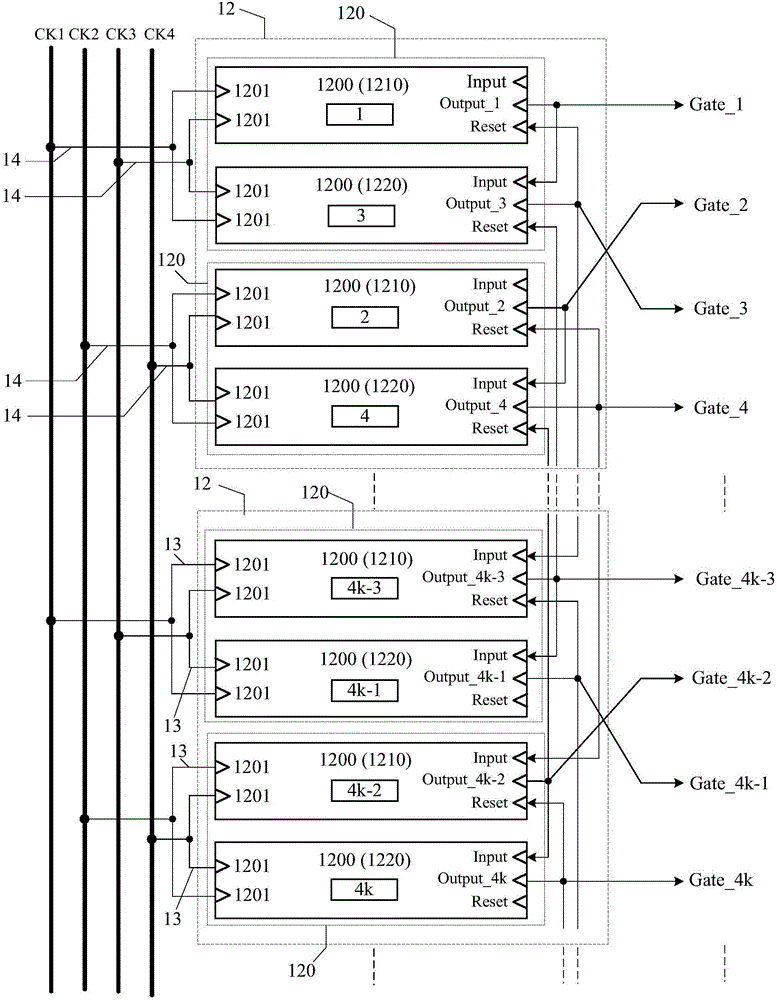

The invention discloses an array substrate, a display panel and a display device. A first type shift register unit and a second type shift register unit which are adjacent to each other serve as a subset, and the two shift register units in each subset are used for being connected with signals ends of the same clock signal wire through first leads, and the first leads are connected with corresponding clock signal wires through second leads. In this way, by adjusting the arranging sequence of the shift register units or reducing the clock signal wires, the overlapping between the leads and the clock signal wires is reduced, and the quantity of parasitic capacitances generated at the overlapping parts between the leads and the clock signal wires is further reduced, so that the delay of clock signals is reduced, and the output delay of the shift register units and the power consumption of a grid driving circuit are reduced.

Owner:BOE TECH GRP CO LTD +1

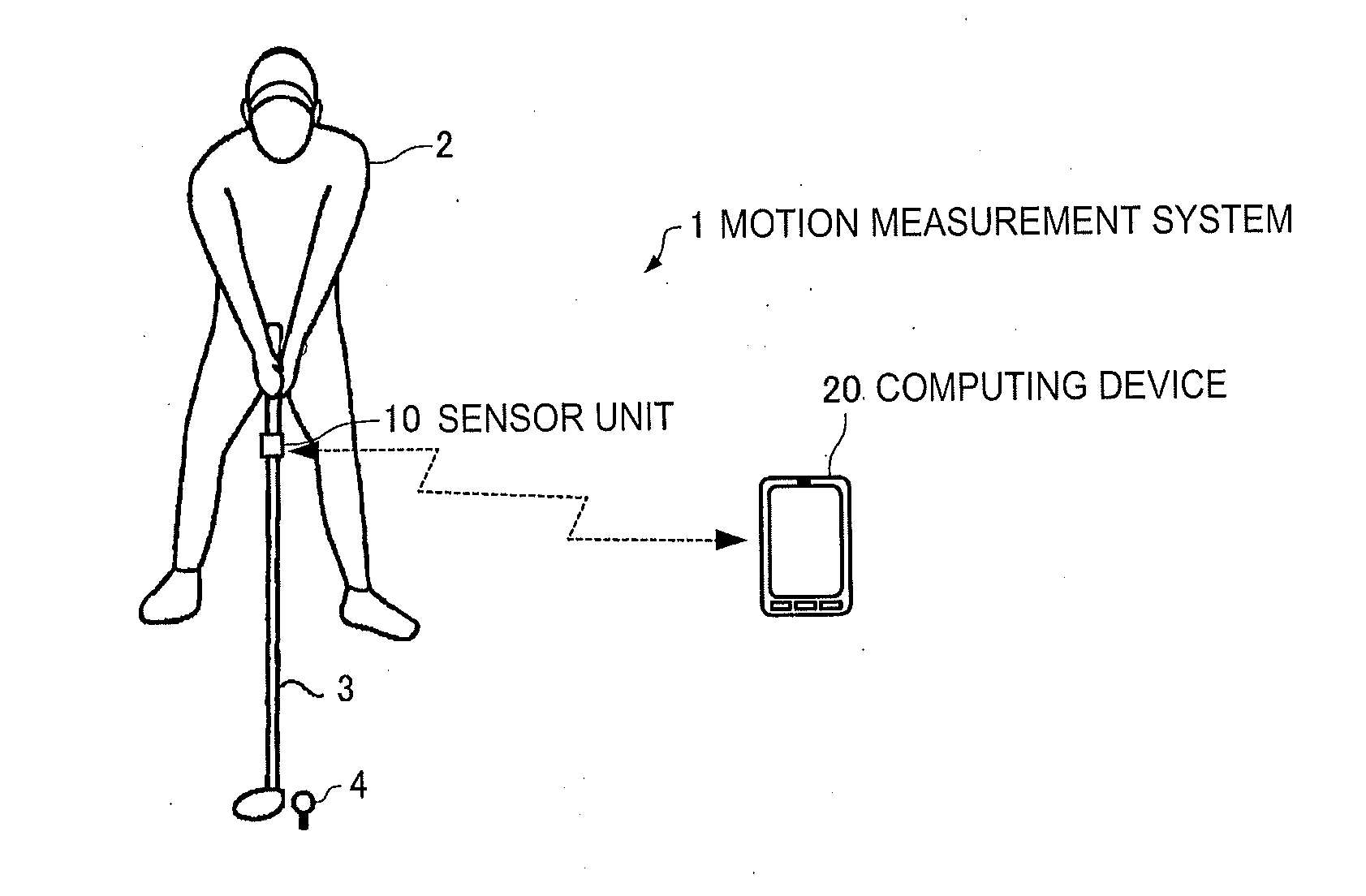

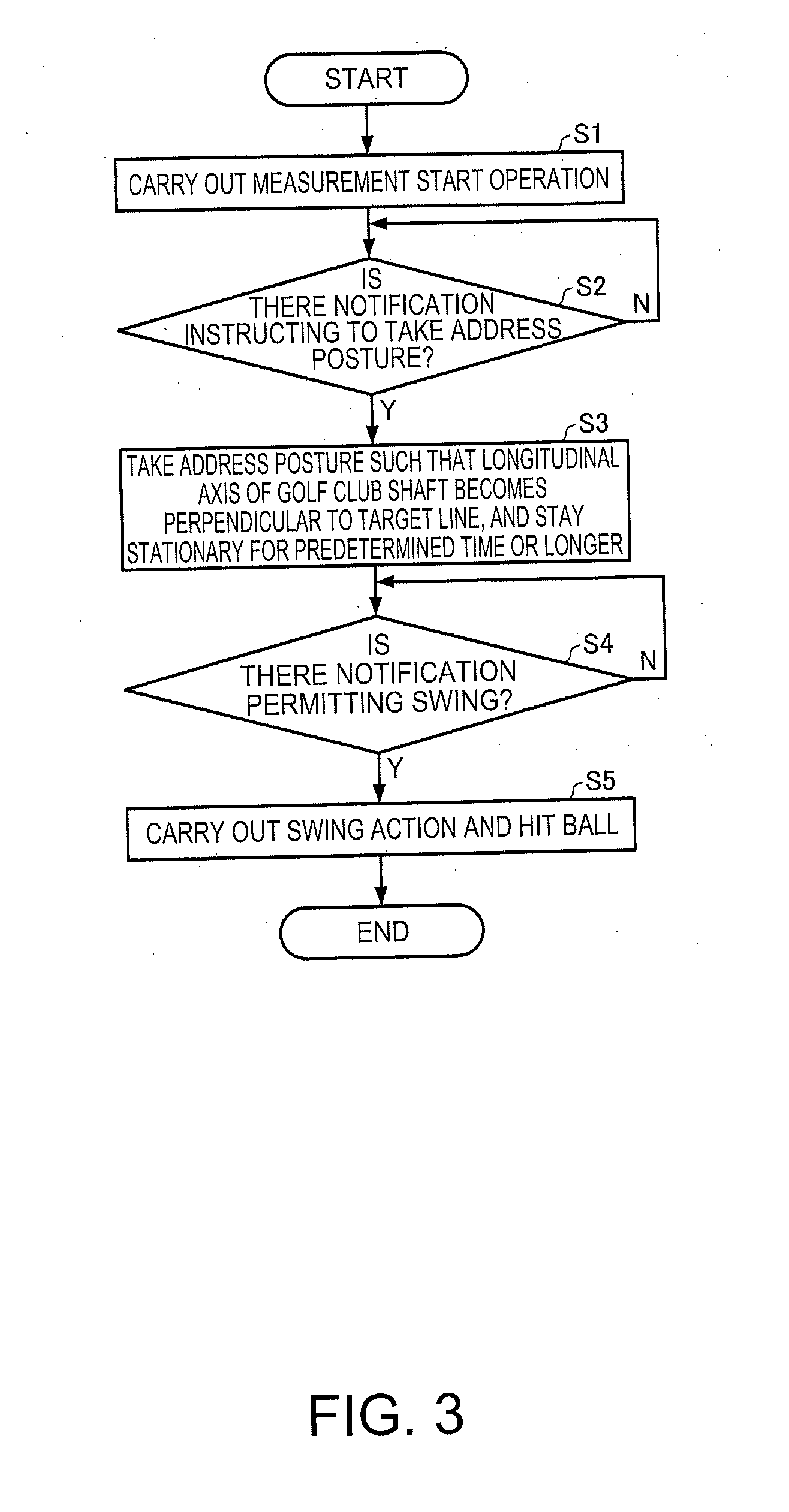

Sensor, motion measurement system, and method of motion measurement

InactiveUS20160089566A1Shorten the timeReduce output delayGymnastic exercisingDigital computer detailsMode switchMotion measurement

A sensor unit includes: a measuring unit; a first buffer which saves measured data measured by the measuring unit when outputting the measured data outside; a second buffer; and an output mode switching unit which switches an output mode for outputting the measured data outside. The output mode includes a real-time mode (first mode) in which the first buffer is overwritten with the measured data if there is no free space in the first buffer, and a buffering mode (second mode) in which the measured data is written in the second buffer if there is no free space in the first buffer and in which the measured data written in the second buffer is transferred to the first buffer if a free space is generated in the first buffer.

Owner:SEIKO EPSON CORP

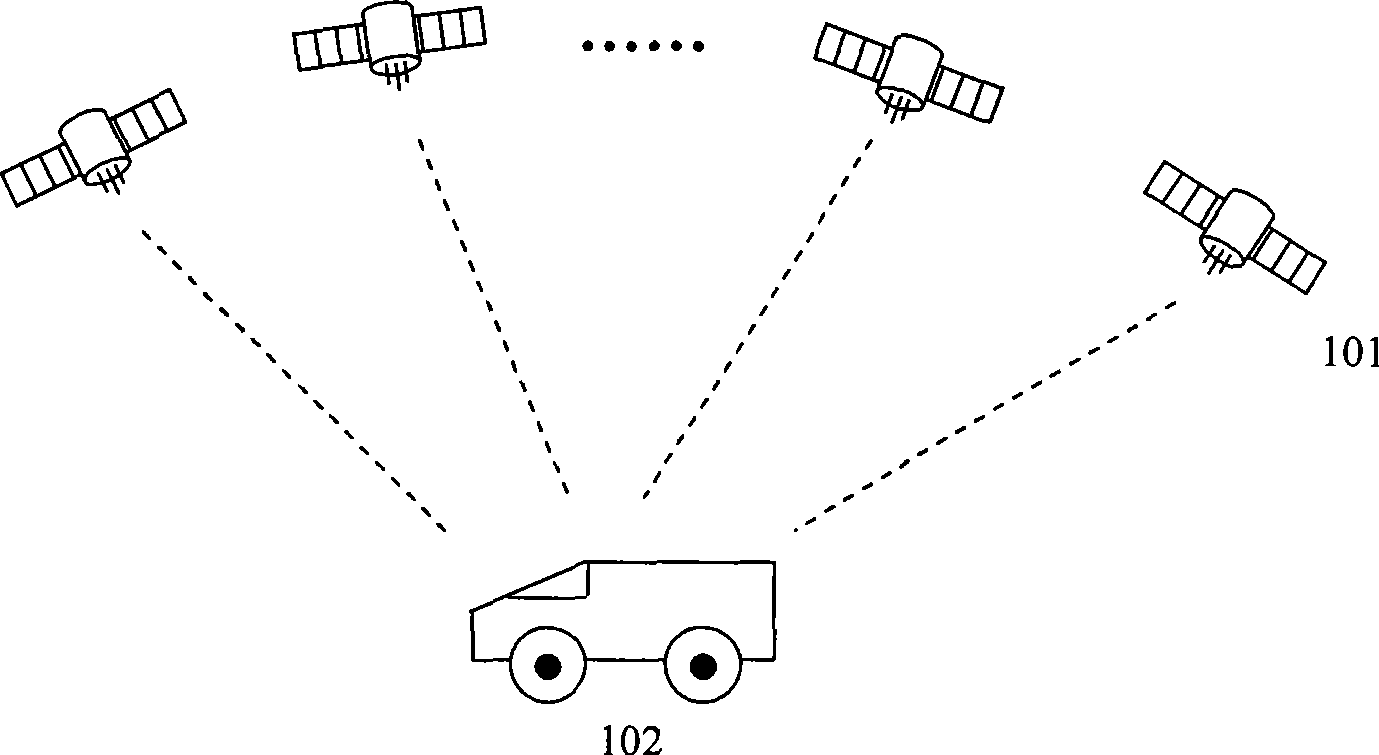

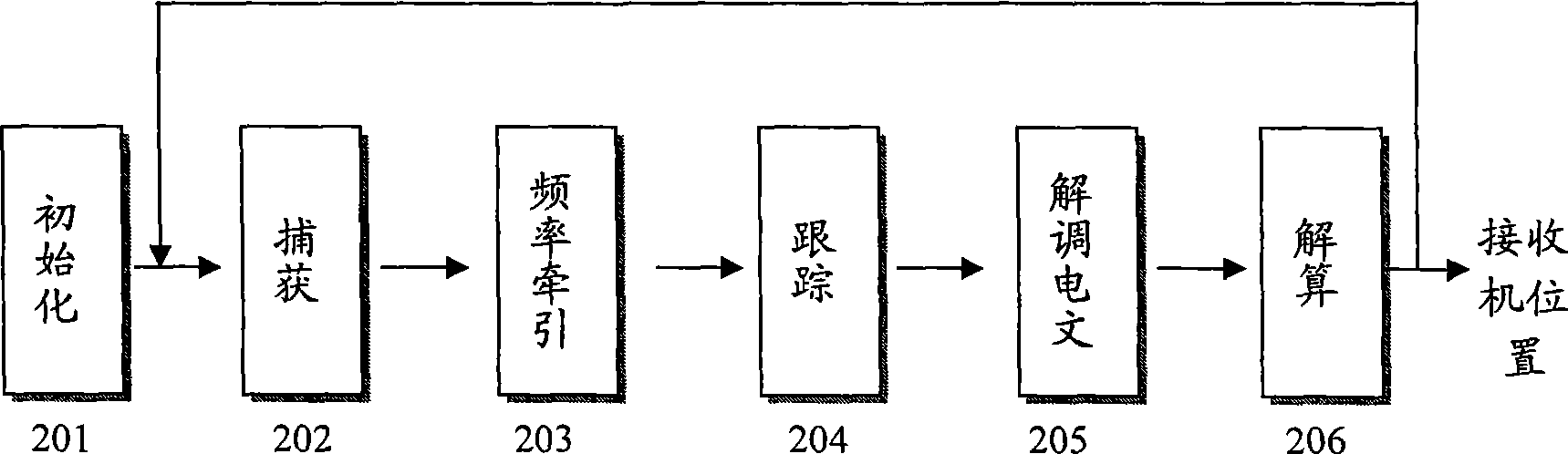

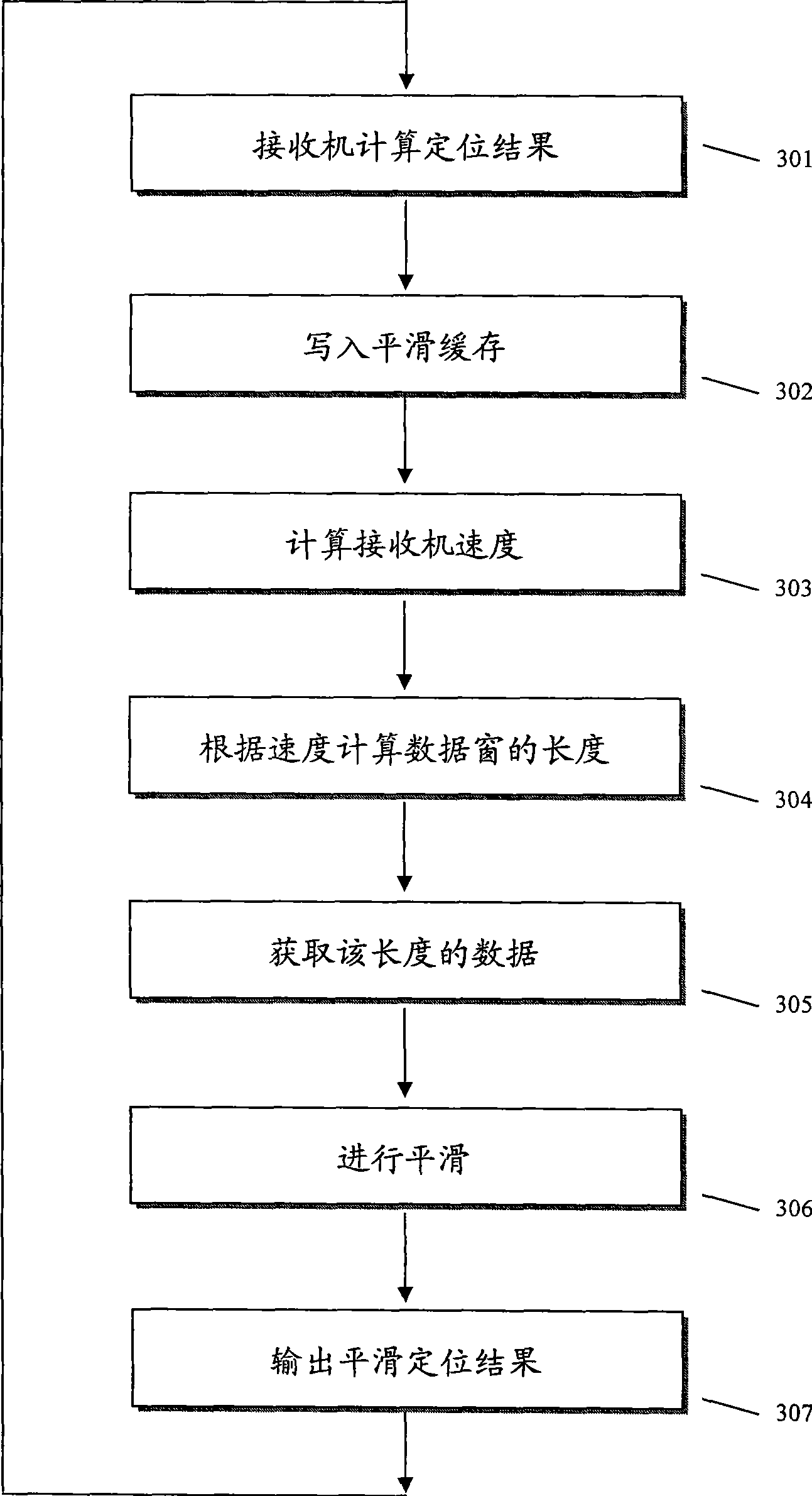

Self-adapting data window size smoothing method for positioning result of global positioning system

The invention discloses a smoothing method of self-adaptive data window length used for a GPS positioning result, and relates to the global satellite positioning and navigation field, such as a GPS. The method comprises the following steps: self-adaptively determining the smoothly sliding window length by a measured receiver speed, and smoothing by a corresponding smoothing method. The self-adaptive data window length smoothing method of the positioning result is applicable to the internal of baseband processing chips of any types of GPS receivers, as well as a receiver system with the GPS baseband processing chip as a core. The method can obviously enhance the positioning precision, reduce errors, and obviously reduce positioning result delay, and ensure real-time property of the positioning result. Compared with other methods, the method is simpler and more easily used, thus greatly reducing complexity and facilitating combination with other smoothing methods.

Owner:中微智创(北京)软件技术有限公司

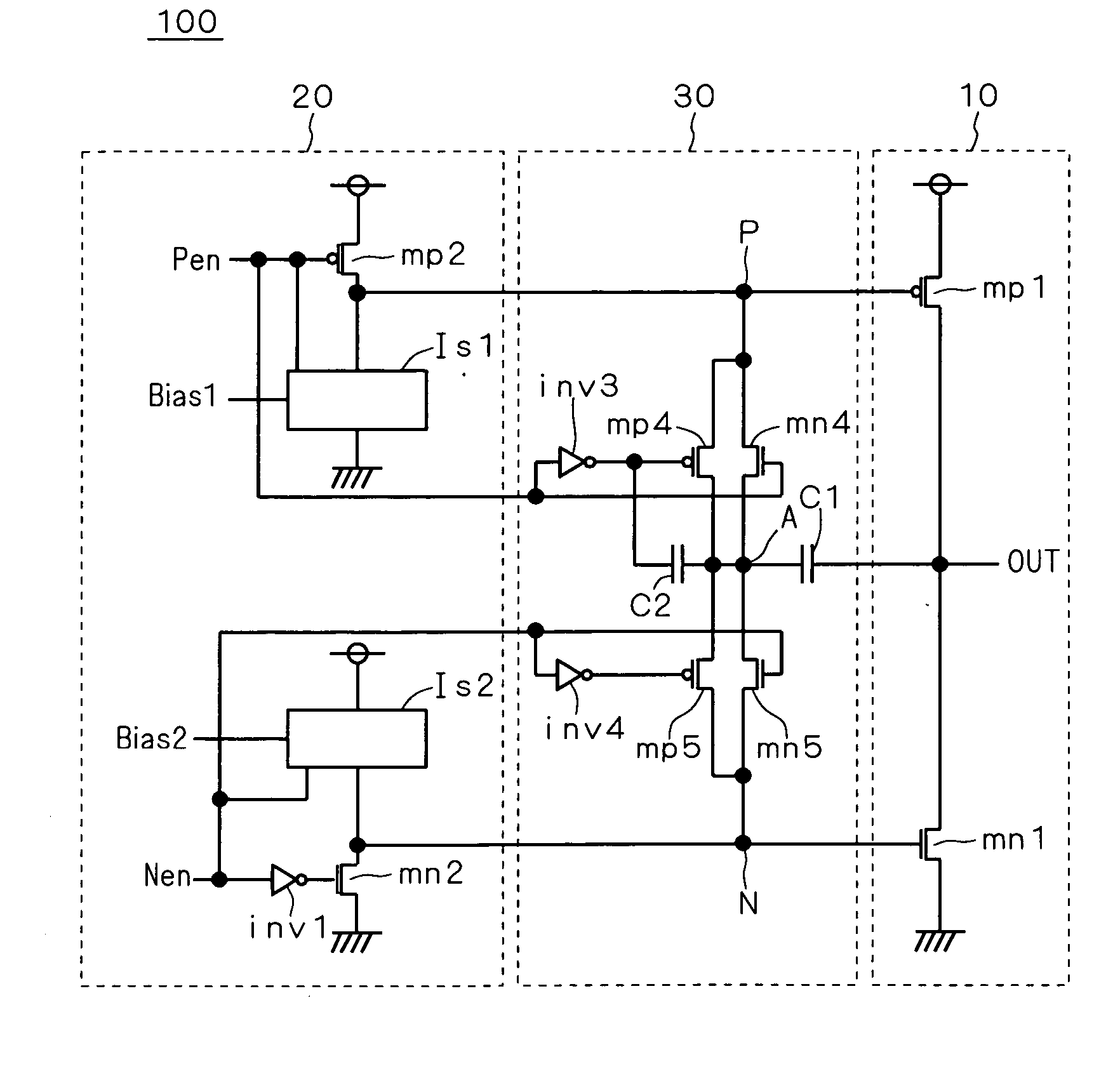

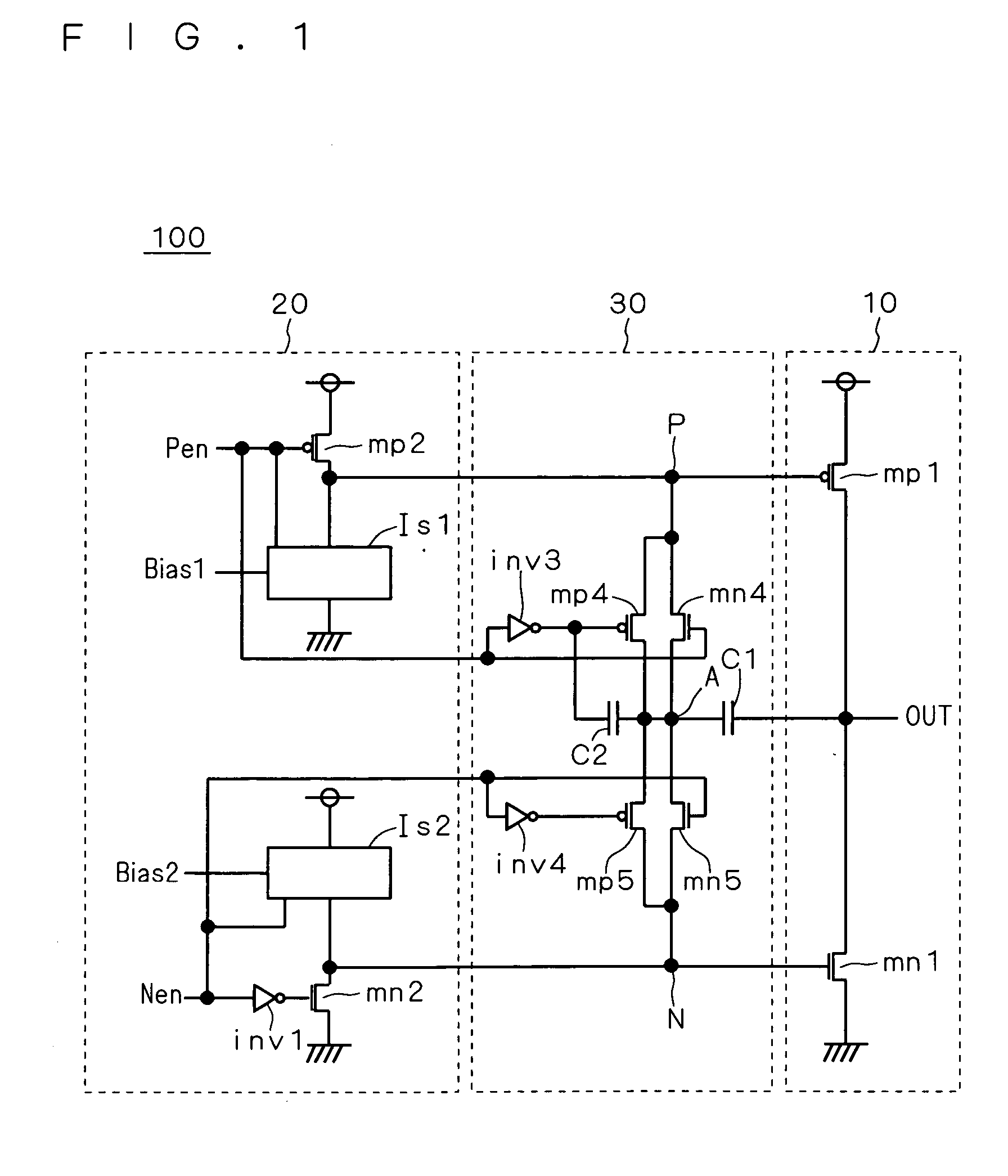

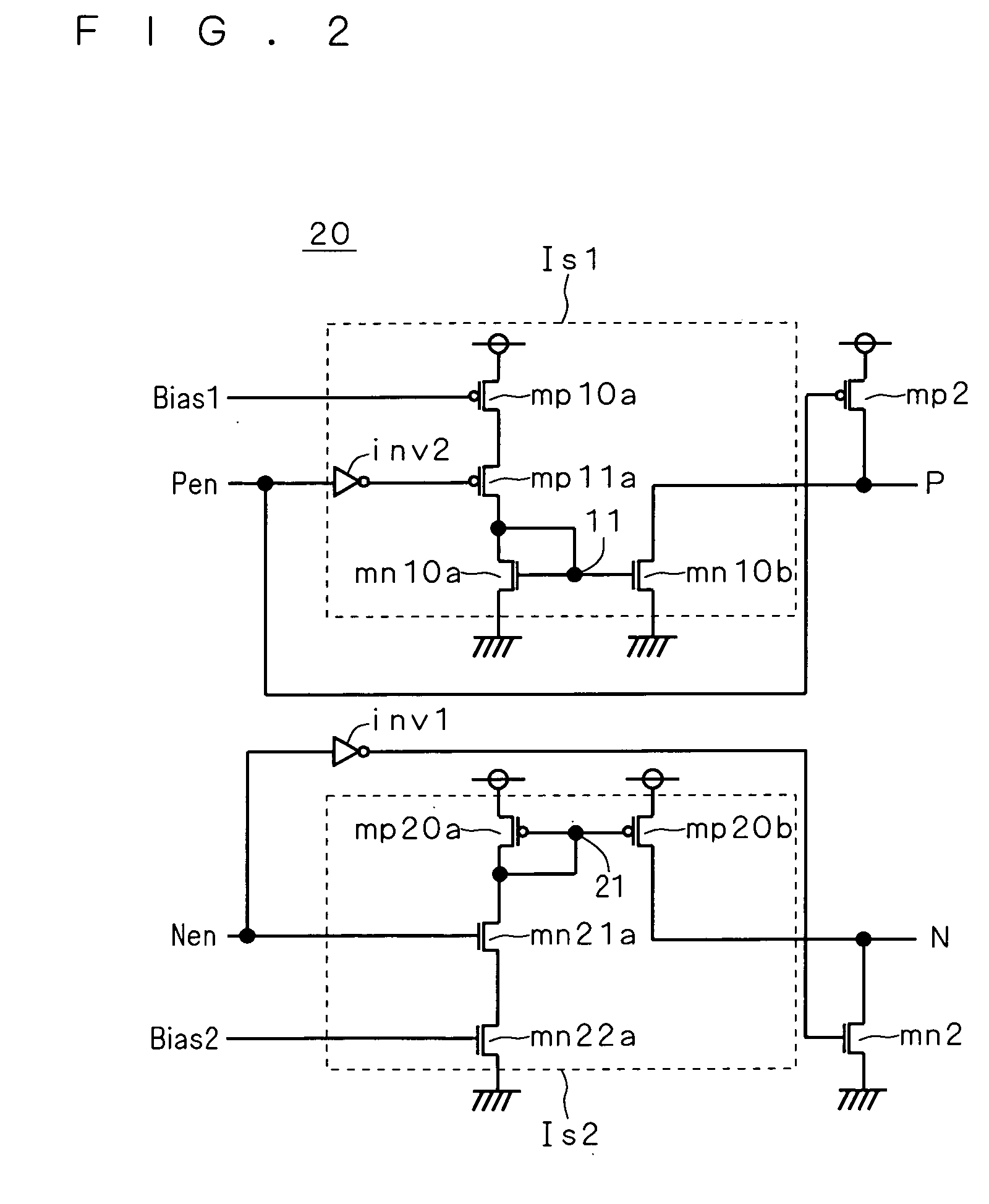

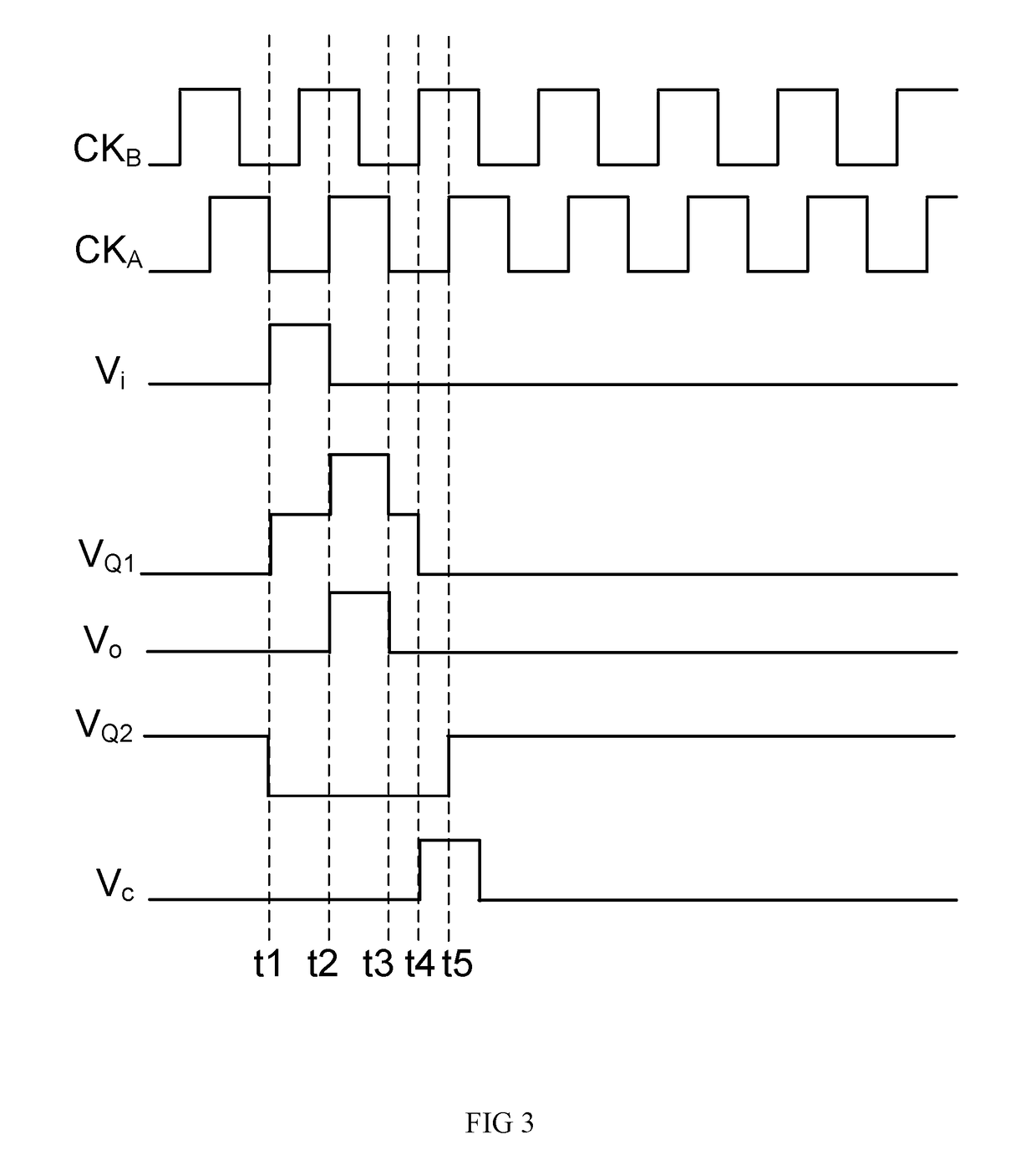

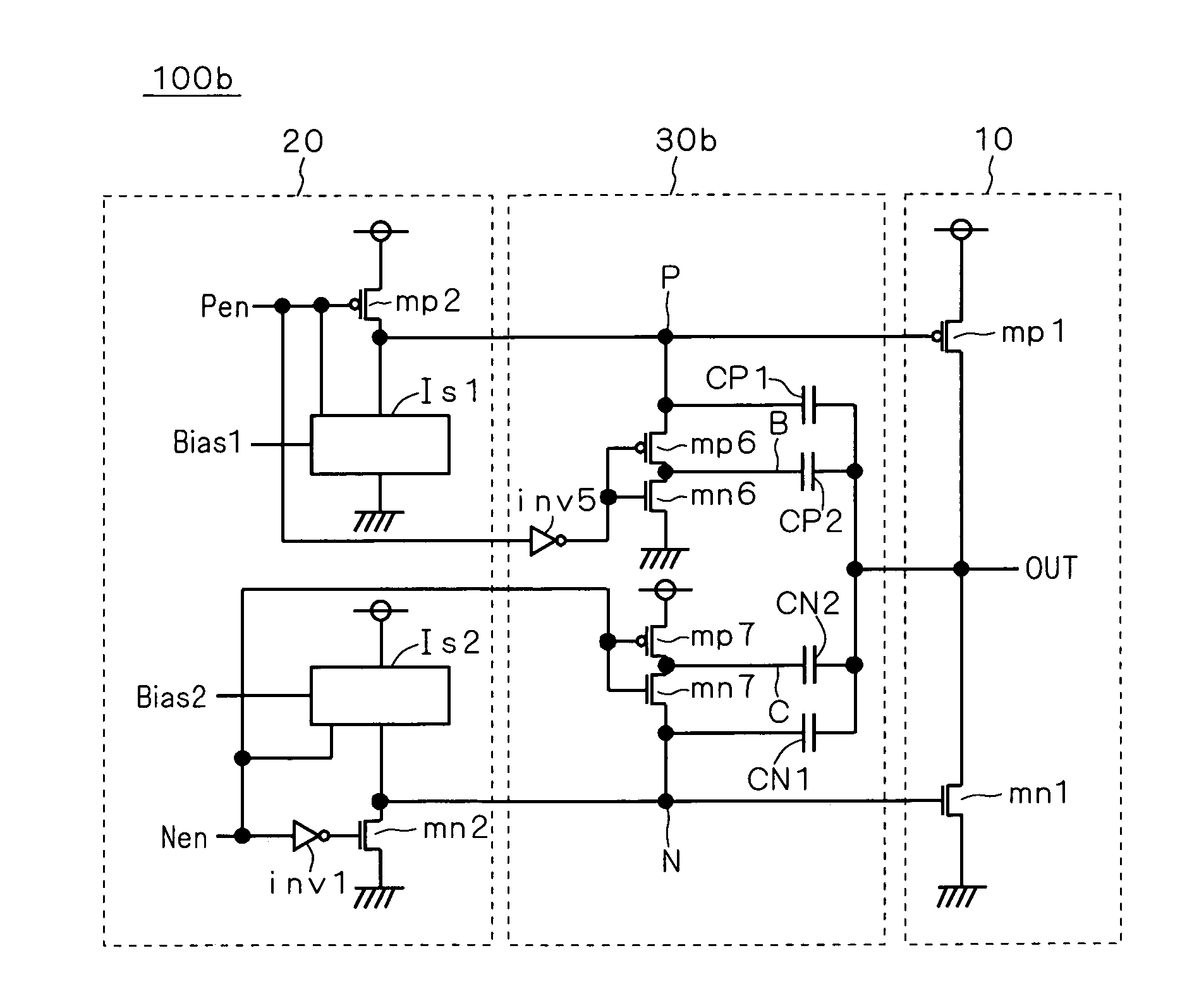

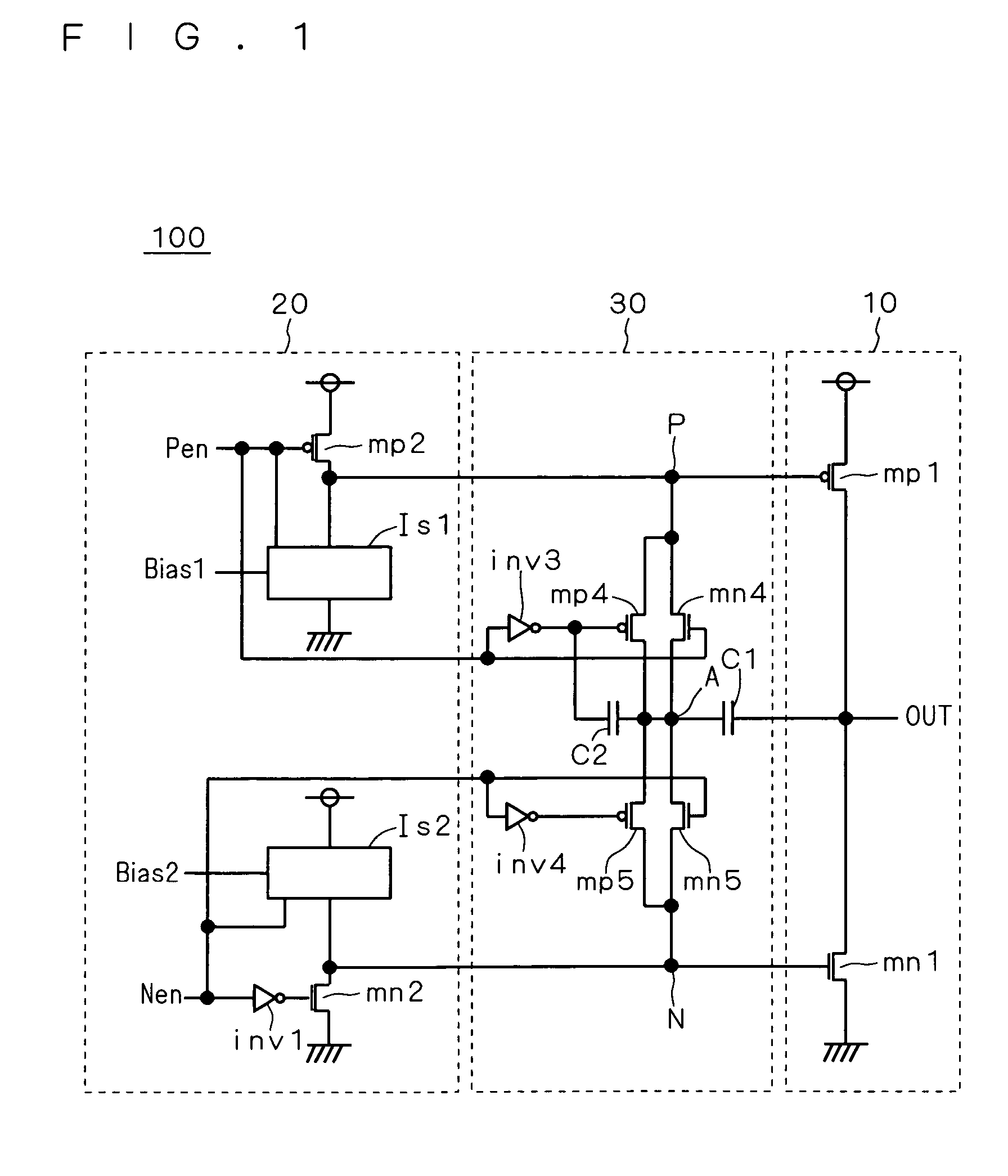

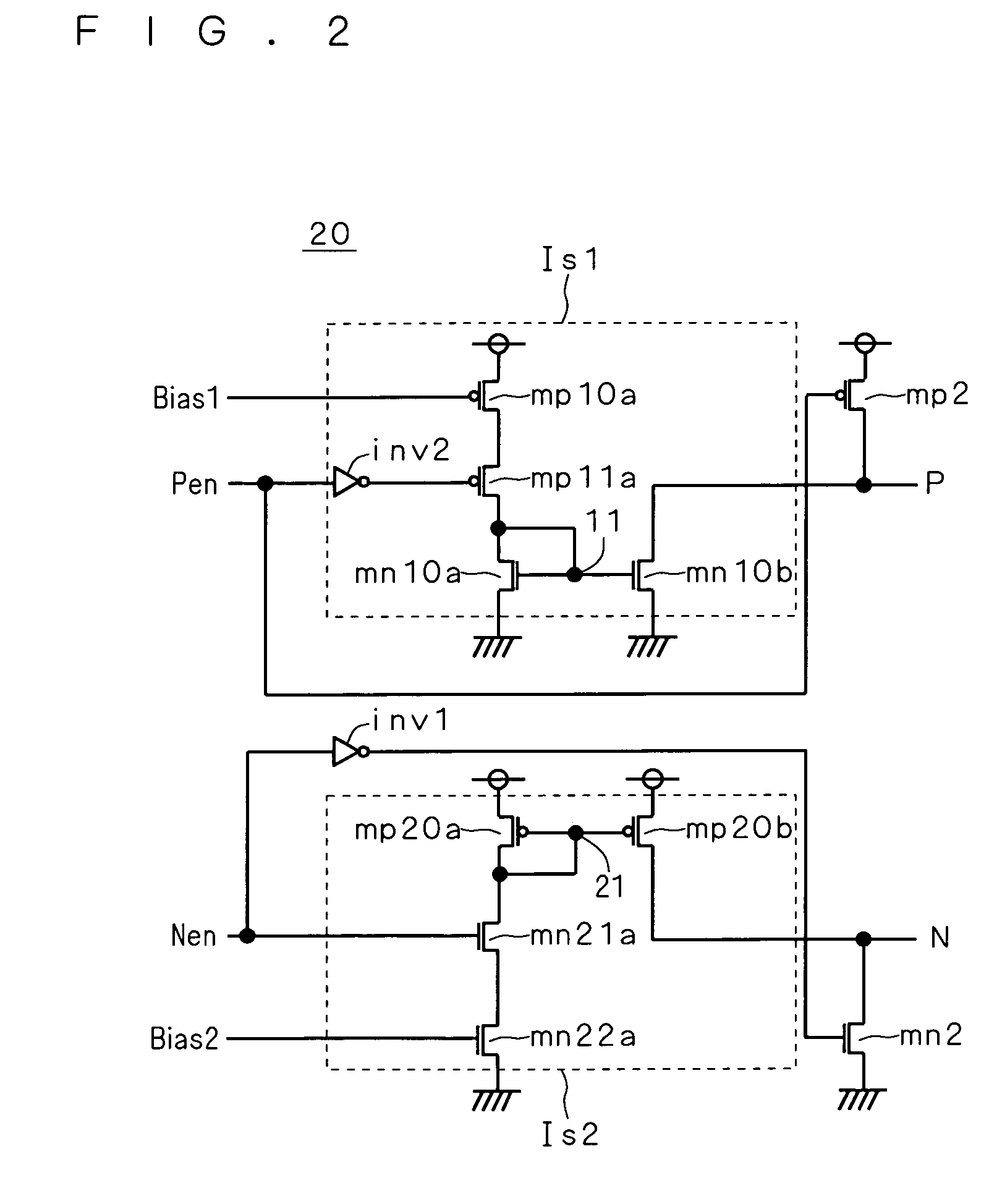

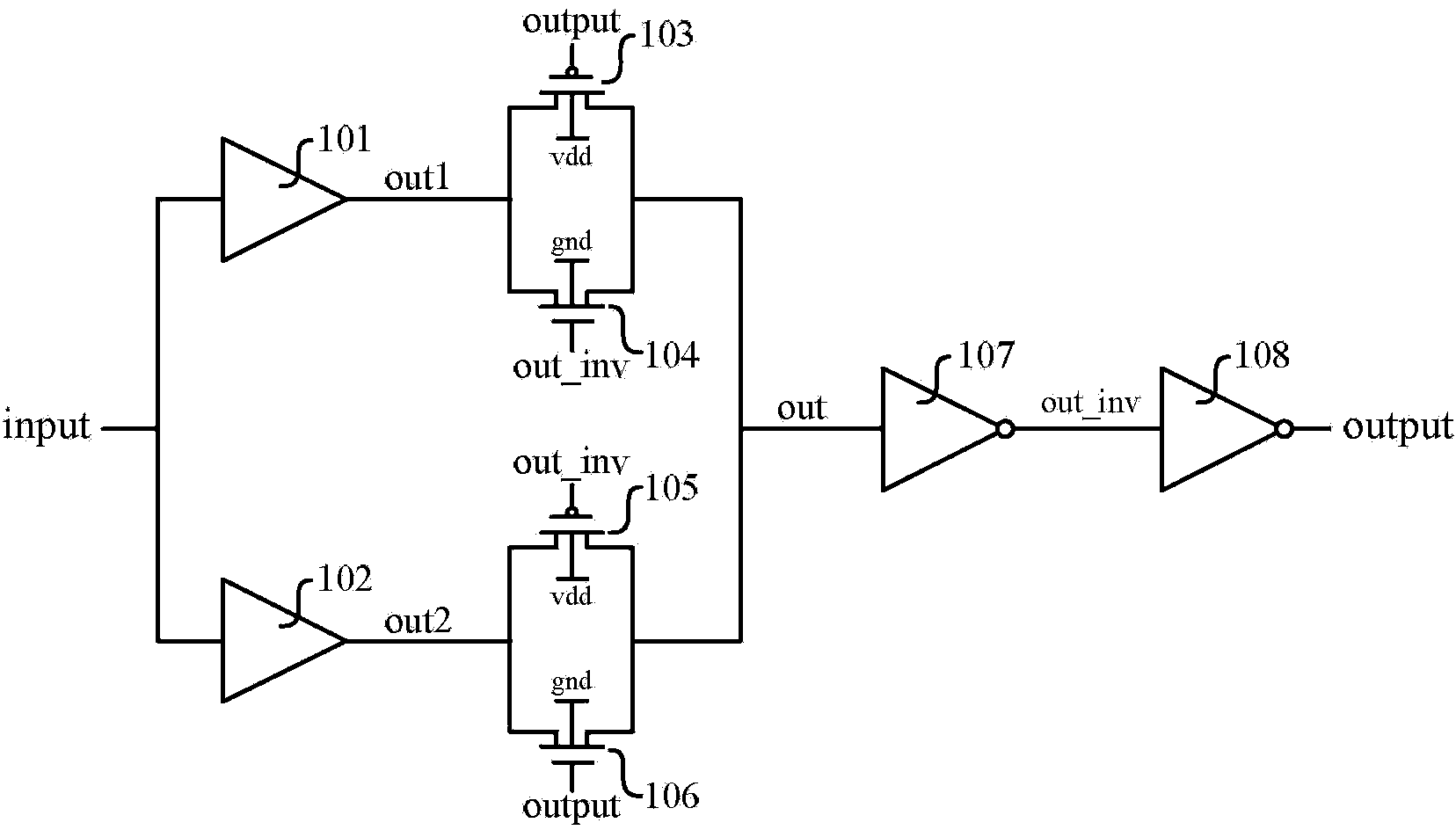

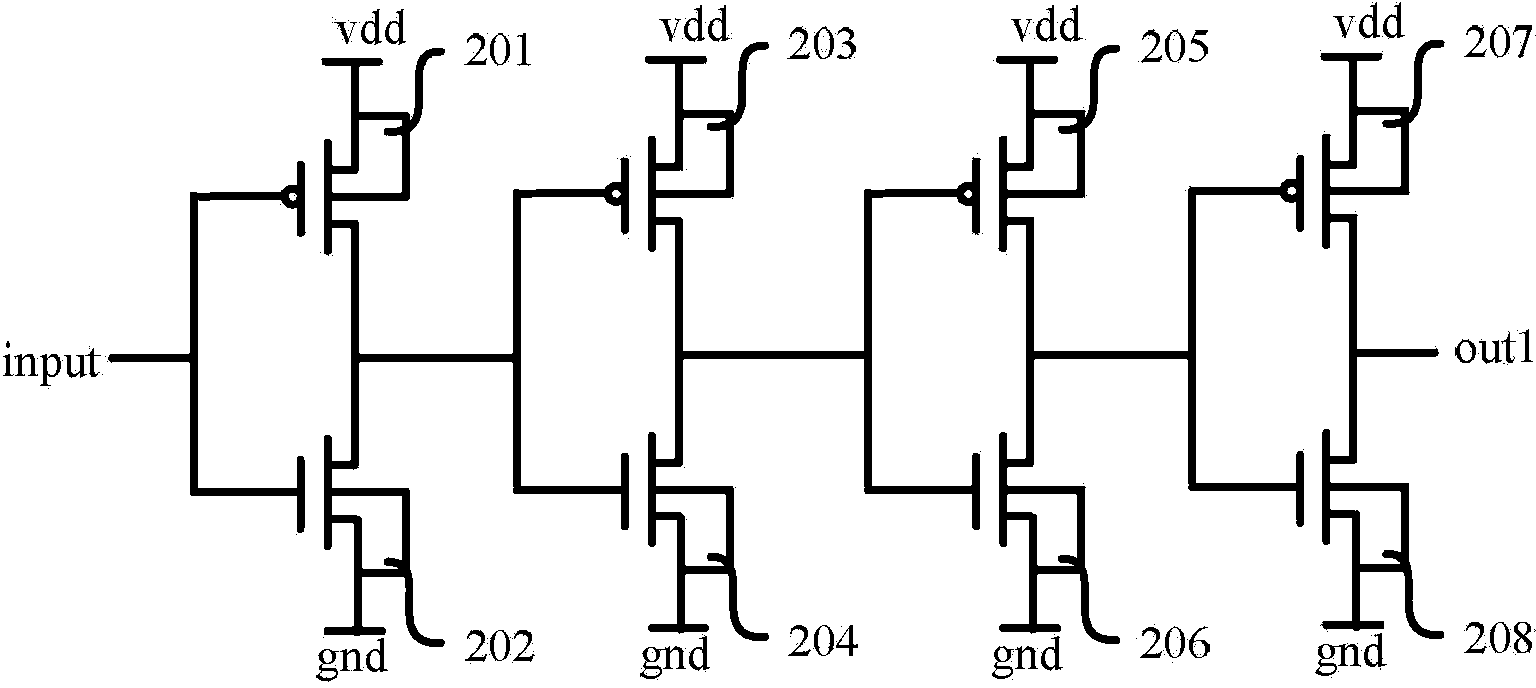

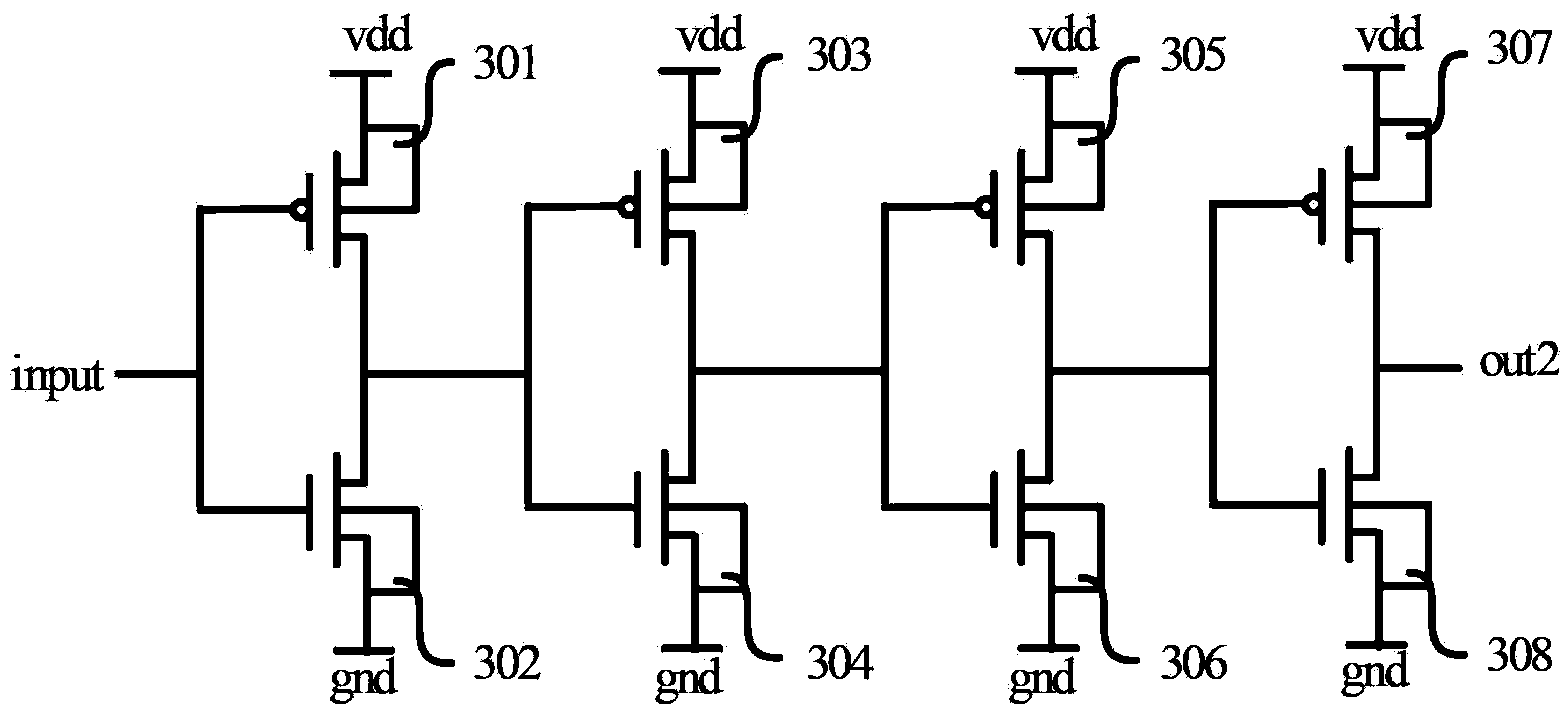

Output buffer circuit

ActiveUS20070057705A1Reduce output delayFast switching speedTransistorElectronic switchingCapacitanceCapacitor

When a first signal is switched from an L level to an H level and a second signal is switched from an H level to an L level, and a first constant current source cannot follow the switching immediately thereafter and has not yet been switched, a first node remains at an H level, so an output node remains at an L level. In such state, a second node having been connected to a third node of an H level before the switching becomes connected to the first node of an H level by the switching. At the same time, the output part of an inverter is switched from an H level to an L level, causing the second node to be switched from an H level to an L level as well via a capacitor. At this time, the potential of the first node is reduced to become equal to the second node, to make a transition to an L level.

Owner:RENESAS ELECTRONICS CORP

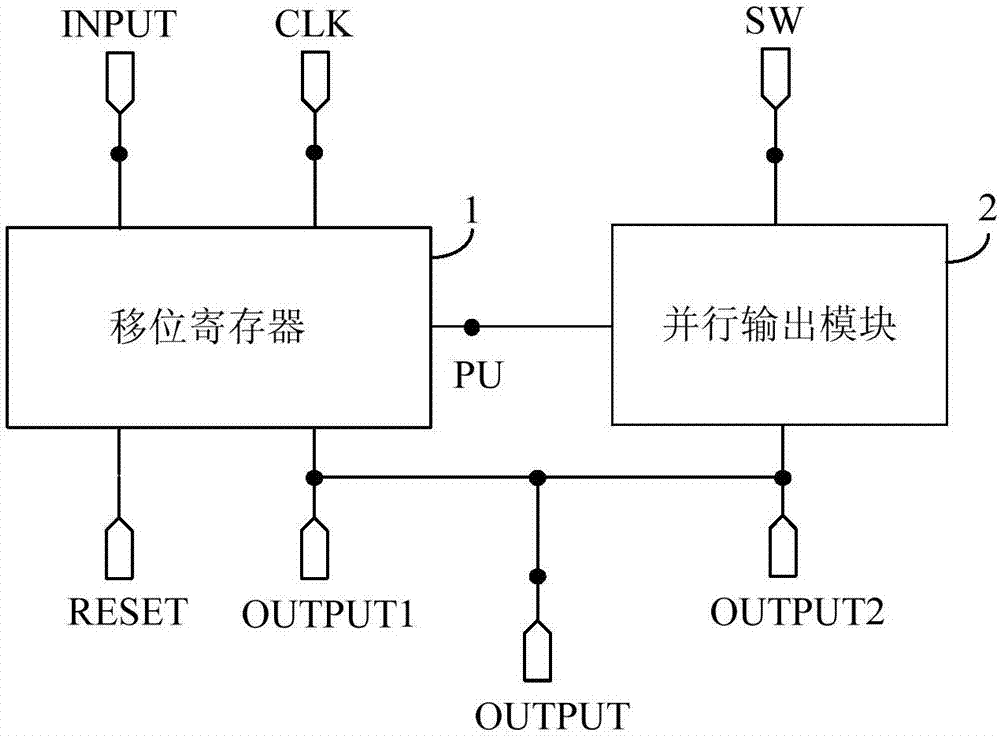

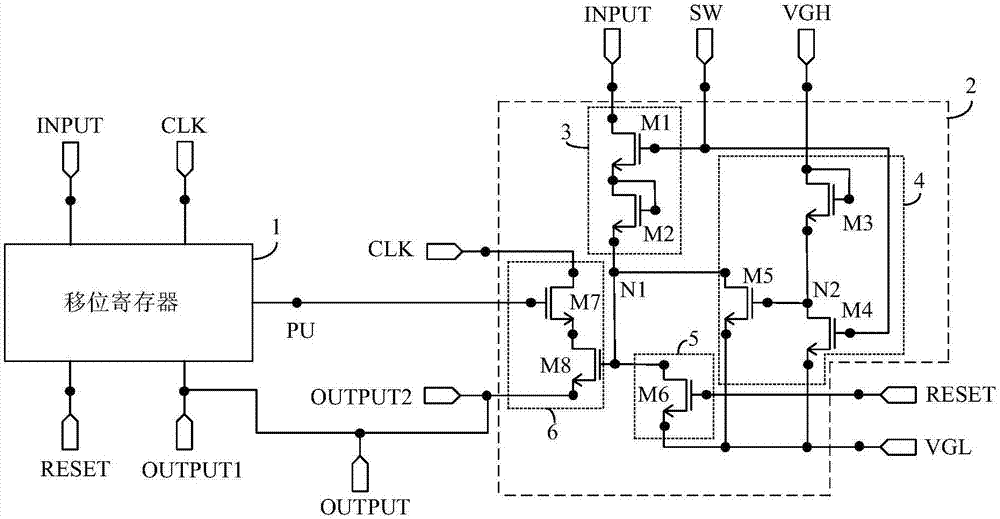

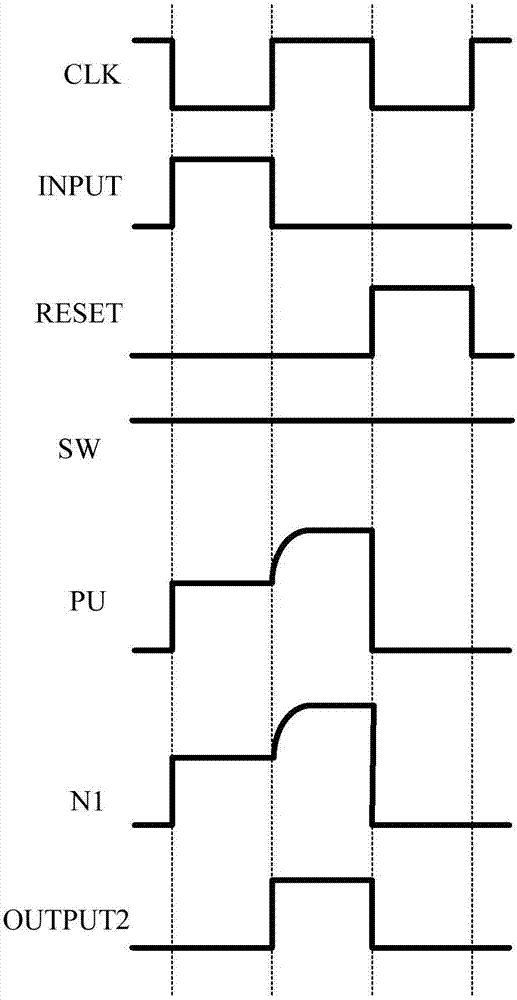

Gate driving unit and driving method thereof, gate driving circuit and displaying device

ActiveCN107993607AReduce output delayImprove charging efficiencyStatic indicating devicesDigital storageVIT signalsShift register

The invention discloses a gate driving unit and a driving method thereof, a gate driving circuit and a displaying device. The gate driving unit comprises a shift register and a parallel output module,wherein the parallel output module is both connected with a control voltage signal input end and a pull-up node in the shift register; a signal output end of the parallel output module and a signal output end of the shift register are both connected with a signal output end of the gate driving unit; the control voltage signal input end is used for providing a first control voltage signal to the parallel output module when an environment temperature is less than a preset temperature; the parallel output module is used for outputting a signal identical to the signal output by the signal outputend of the shift register under control of electric potential of the pull-up node and the first control voltage signal. According to the technical scheme disclosed by the invention, the parallel output module is controlled to output the signal identical to the signal output by the signal output end of the shift register in a low-temperature environment, so that output delay of the gate driving circuit is reduced, and the charging efficiency is promoted.

Owner:BOE TECH GRP CO LTD +1

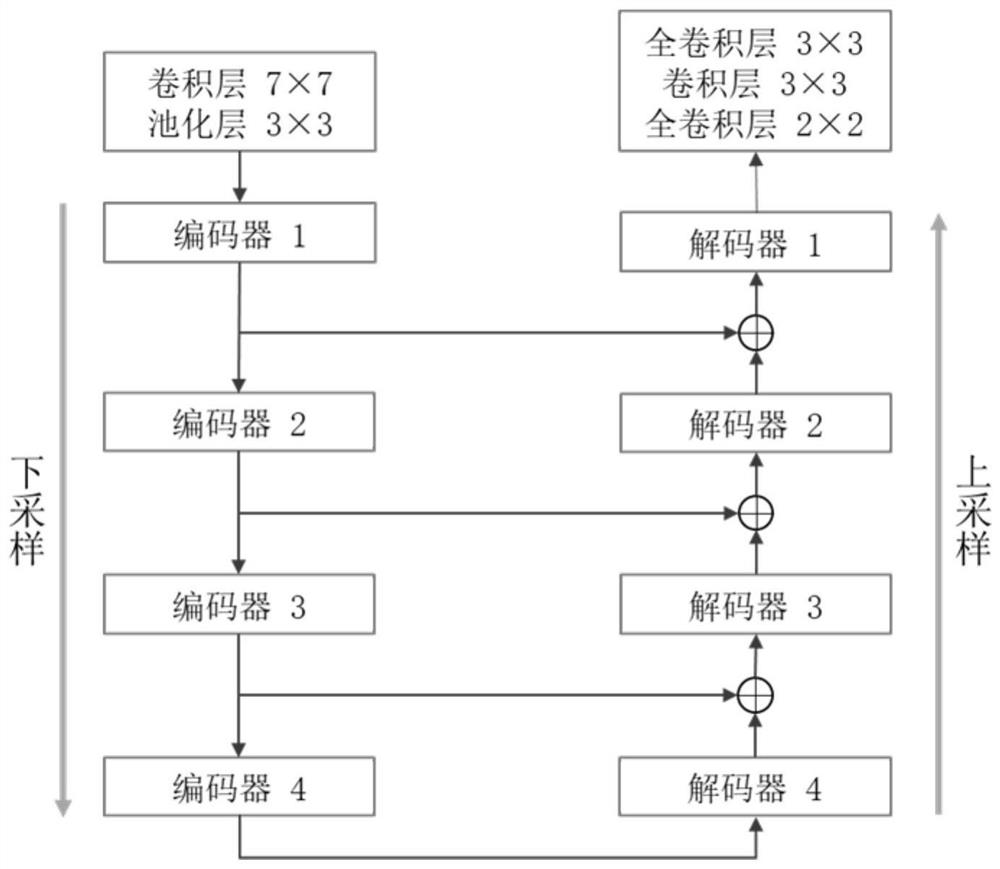

Instrument visual tracking method for laparoscopic minimally invasive surgery

ActiveCN113538522AImprove accuracyAccurate extractionImage enhancementImage analysisData setVisual perception

The invention discloses a surgical instrument visual tracking method for laparoscopic minimally invasive surgery, which is based on a deep learning method and comprises the following steps: firstly, a surgical instrument area is detected and segmented from a surgical video stream and extracting local features on the premise of not performing preoperative marking on a surgical instrument; the detection and positioning efficiency and the feature extraction accuracy of the surgical instrument are greatly improved; meanwhile, image enhancement processing is carried out on the region of interest by utilizing an image filtering algorithm and region screening, so that the recognition precision of a tracking target point is improved; secondly, a 2D-3D conversion relation between the surgical instrument and the target area is calculated through modeling and mathematical expression so as to determine depth perception information of an end effector of the surgical instrument and the target area; and finally, a real-time tracking program of the target point is realized by using a mask algorithm. A data set is established through clinical medicine guidance and used for training and testing a surgical instrument detection model, automatic detection and tracking of the laparoscopic surgical instrument are achieved, and the model is more practical.

Owner:GUANGDONG UNIV OF TECH

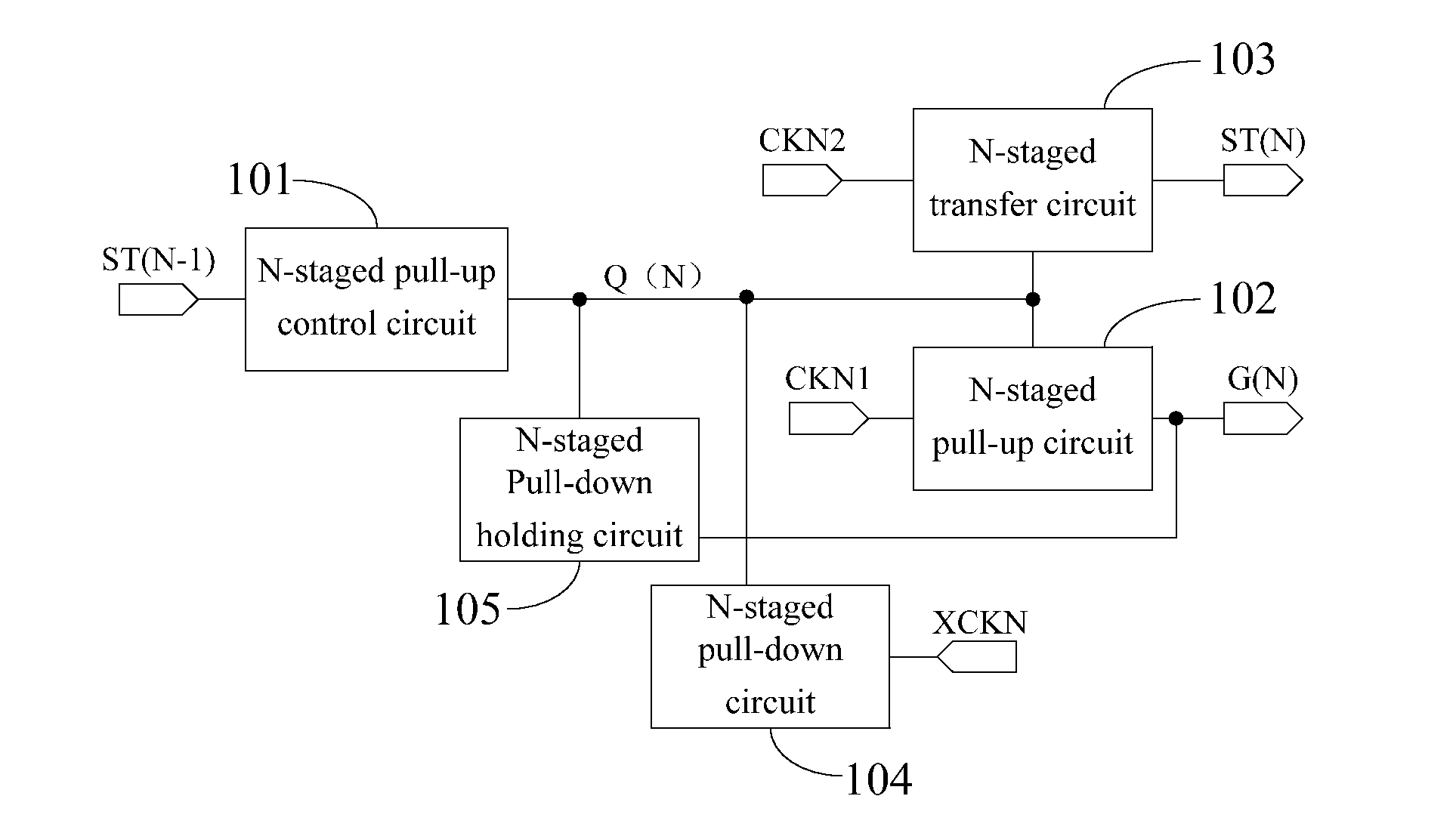

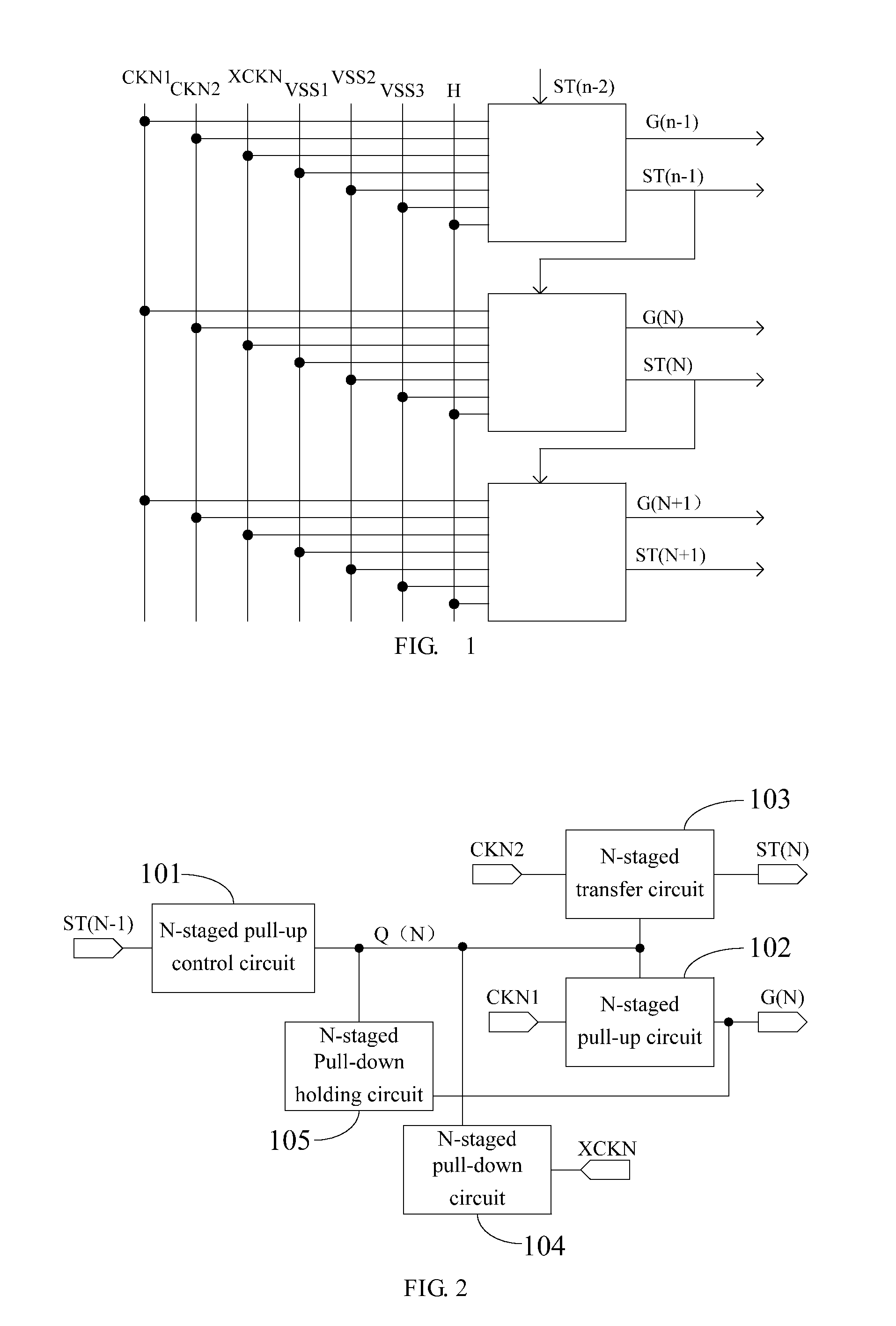

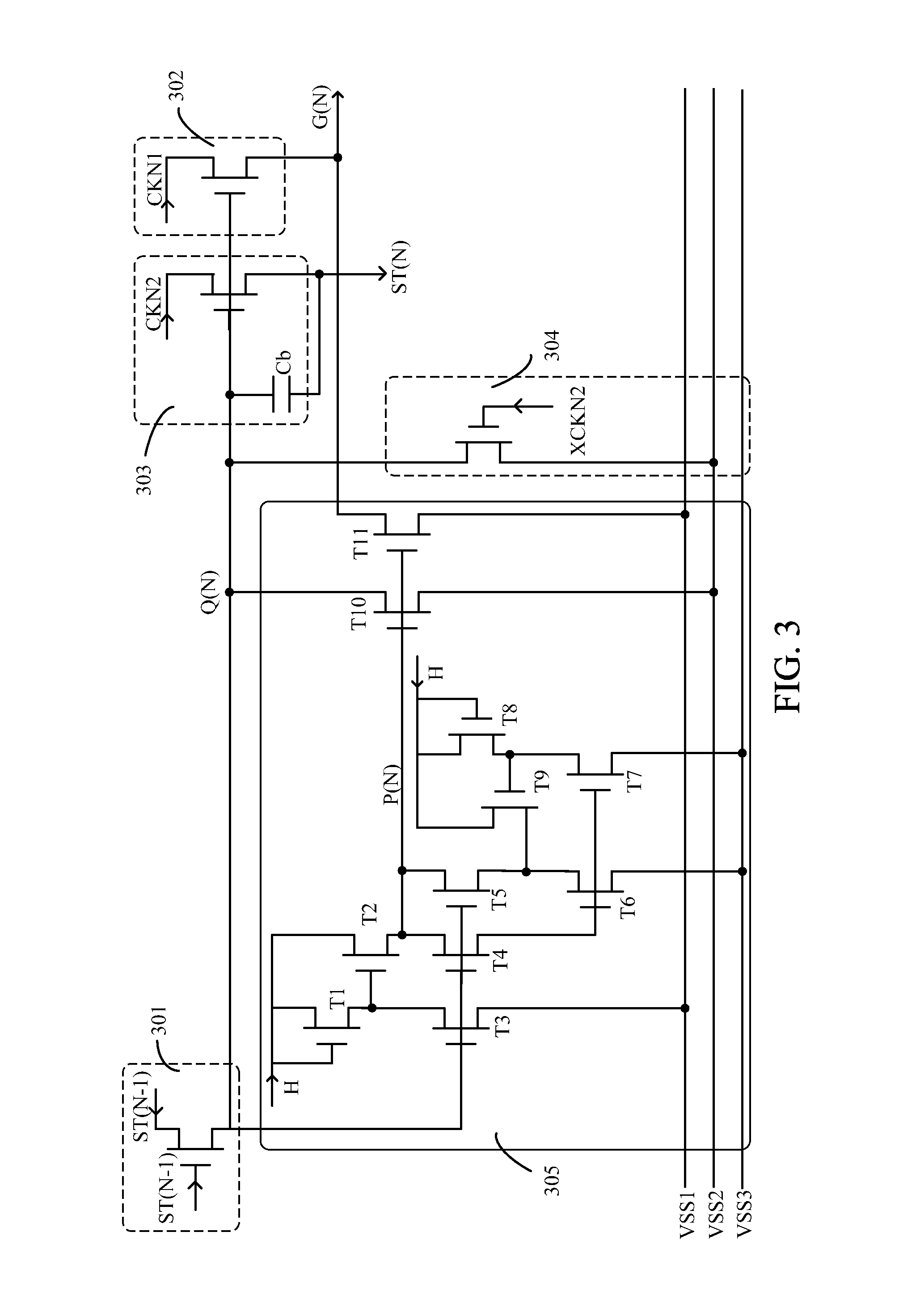

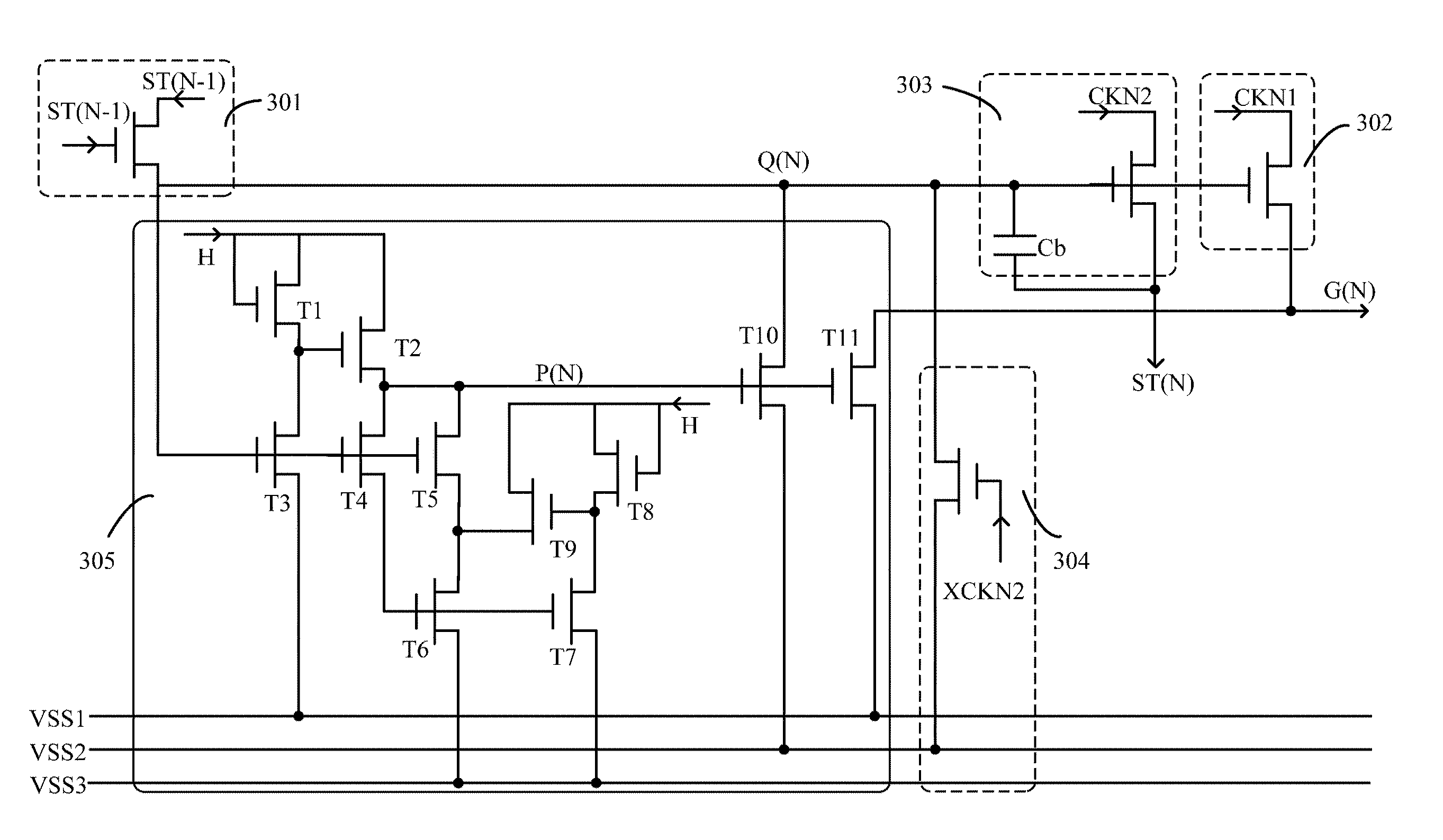

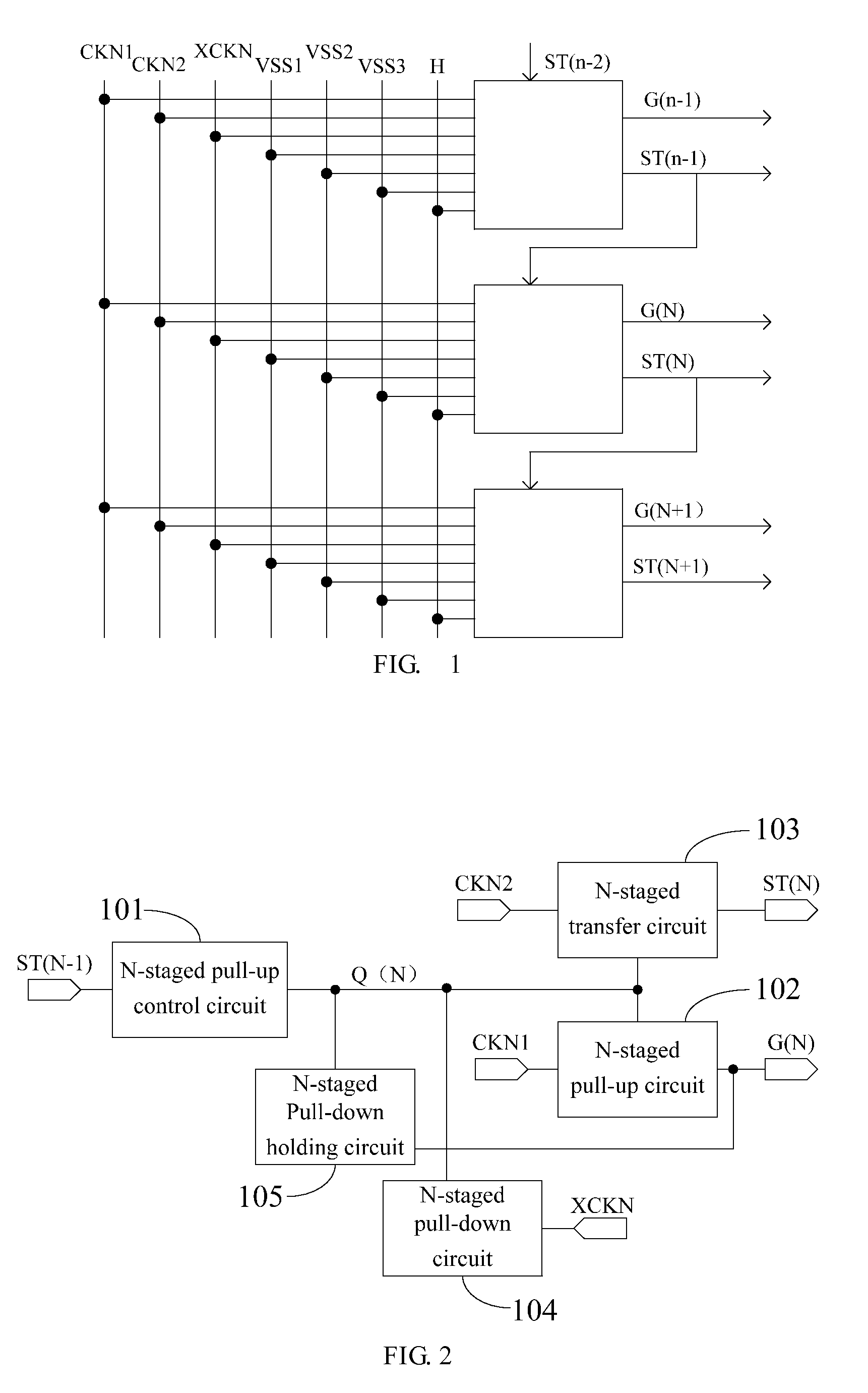

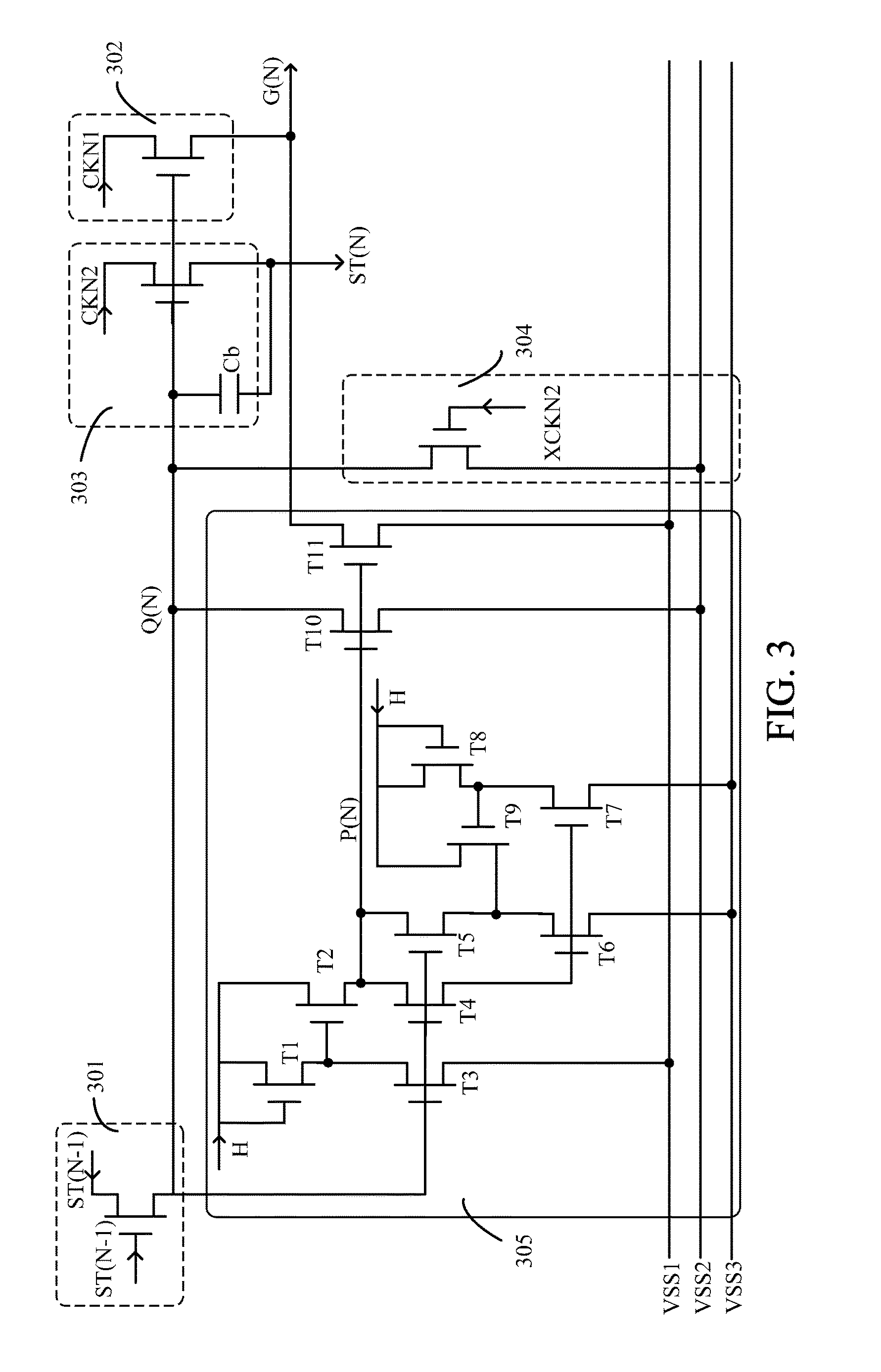

GOA Circuit and Liquid Crystal Display

ActiveUS20160307535A1Reduce output delayHigh voltage levelStatic indicating devicesElectricityLiquid-crystal display

A GOA circuit comprising GOA units and a liquid crystal display are disclosed. The N-staged GOA units charge the Nth-staged horizontal scanning line in the display region, and comprise N-staged pull-up control circuits, N-staged pull-up circuits, N-staged transfer circuits, N-staged pull-down circuits, and N-staged pull-down holding circuits. The N-staged pull-up circuits turn on when the Nth-staged gate signal point is at a high voltage level, receive a first clock signal and charge the N-staged horizontal scanning lines when the first clock signal is at a high voltage level. The N-staged transfer circuits receive a second clock signal when the Nth-staged gate signal point is at the high voltage level and output N-staged transfer signals to control the operation of the (N+1)-staged GOA units. The disclosure may ensure the scanning lines in the GOA circuit to be better charged for facilitating normal operation for each point in the circuit.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD +1

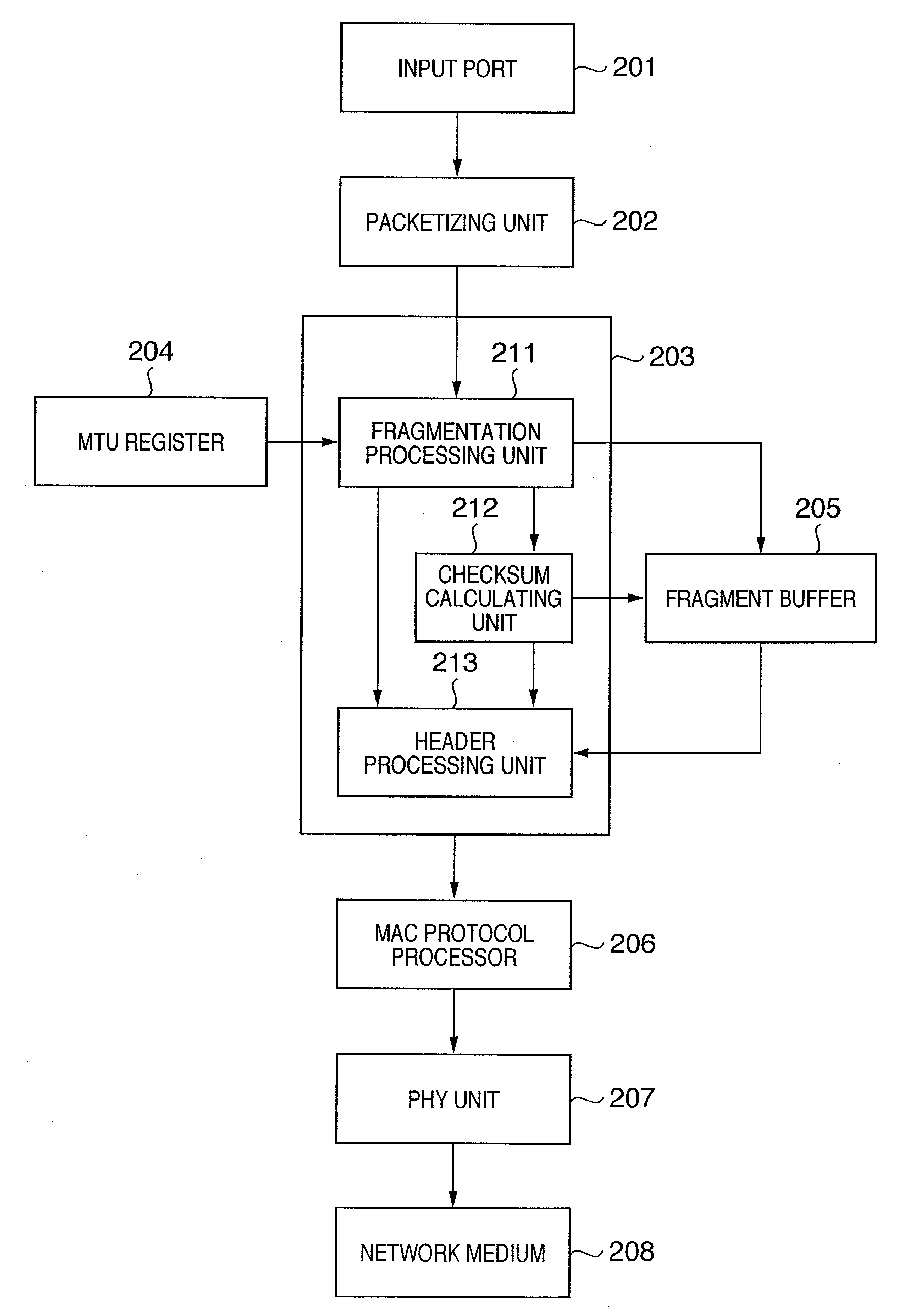

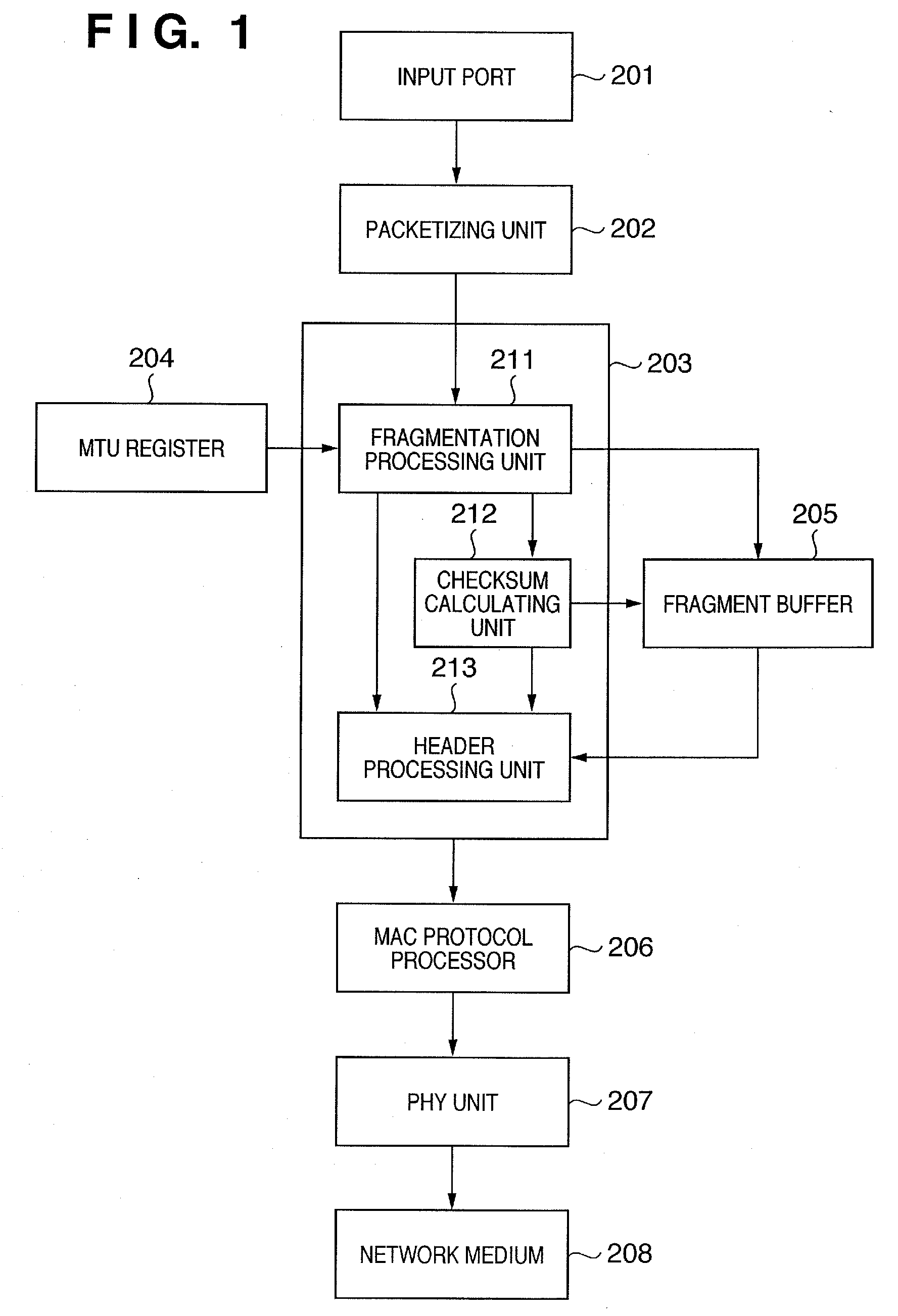

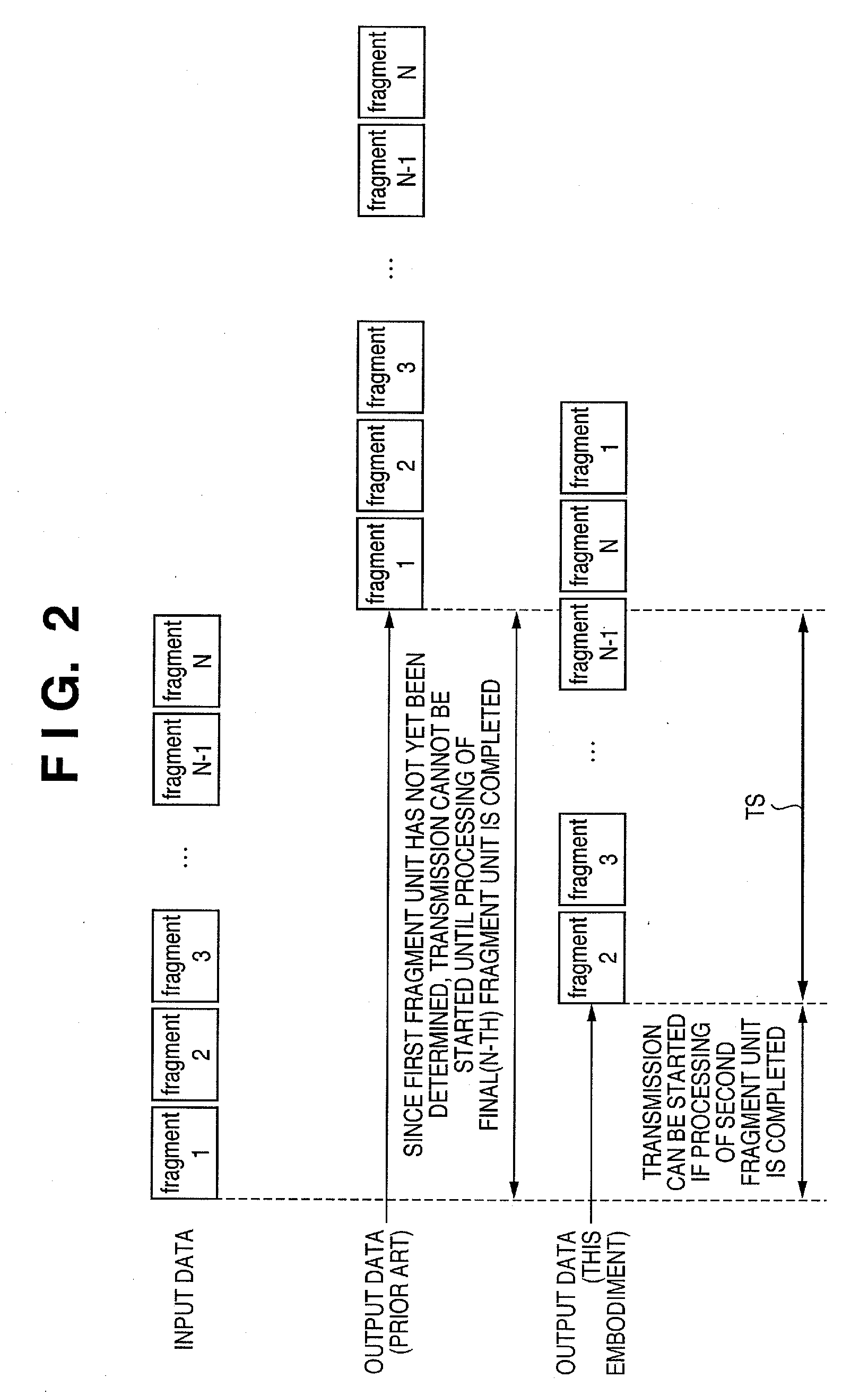

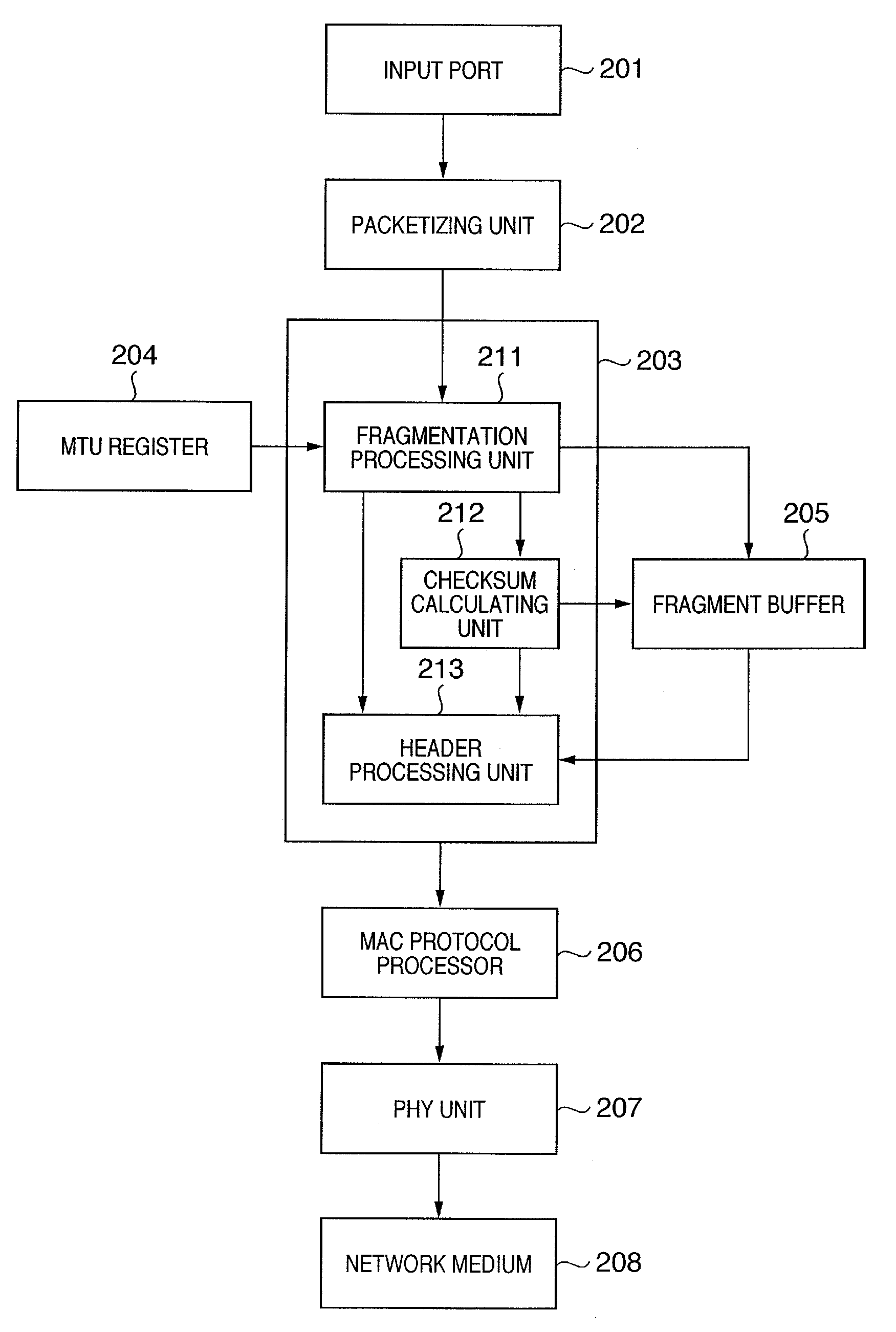

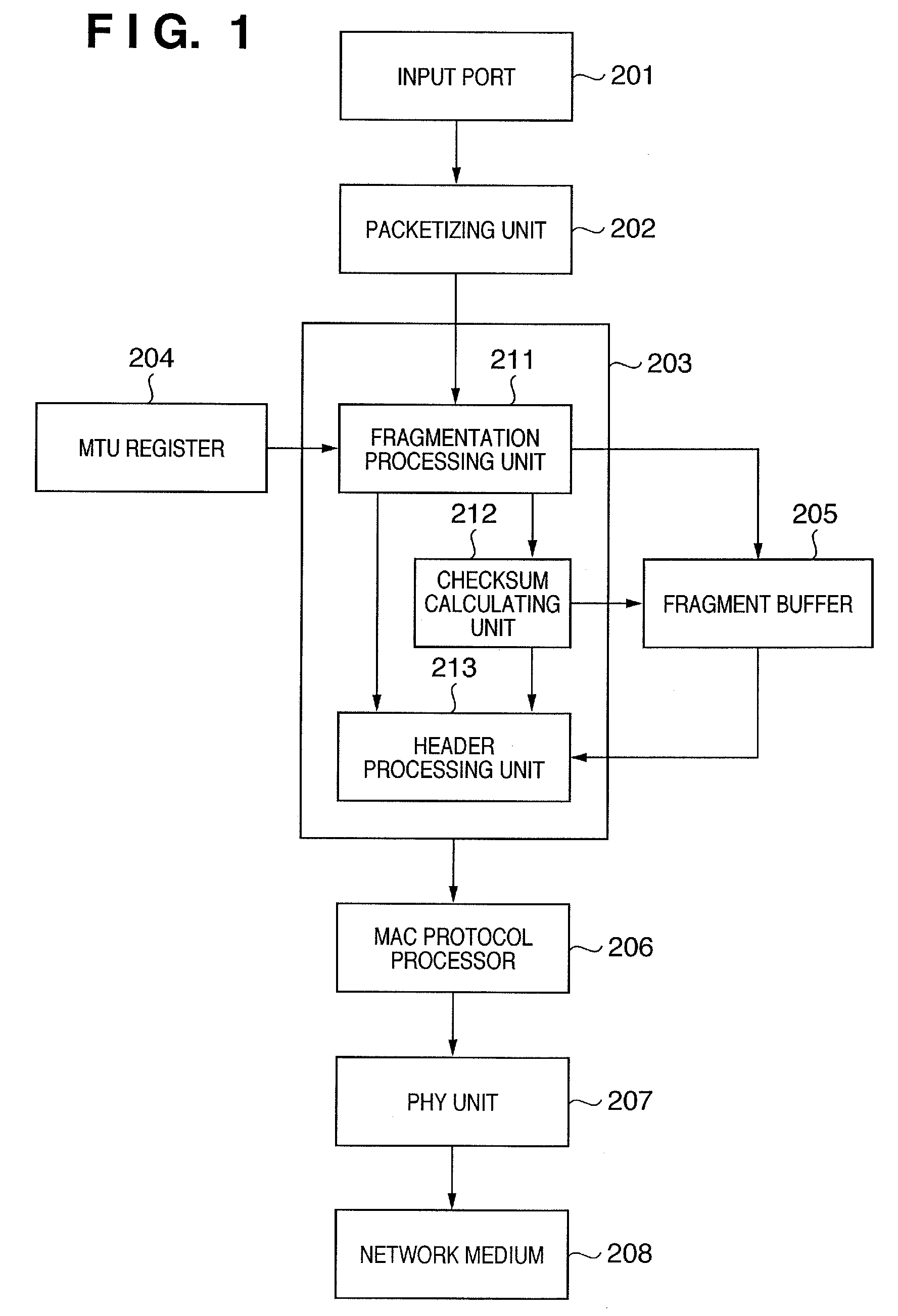

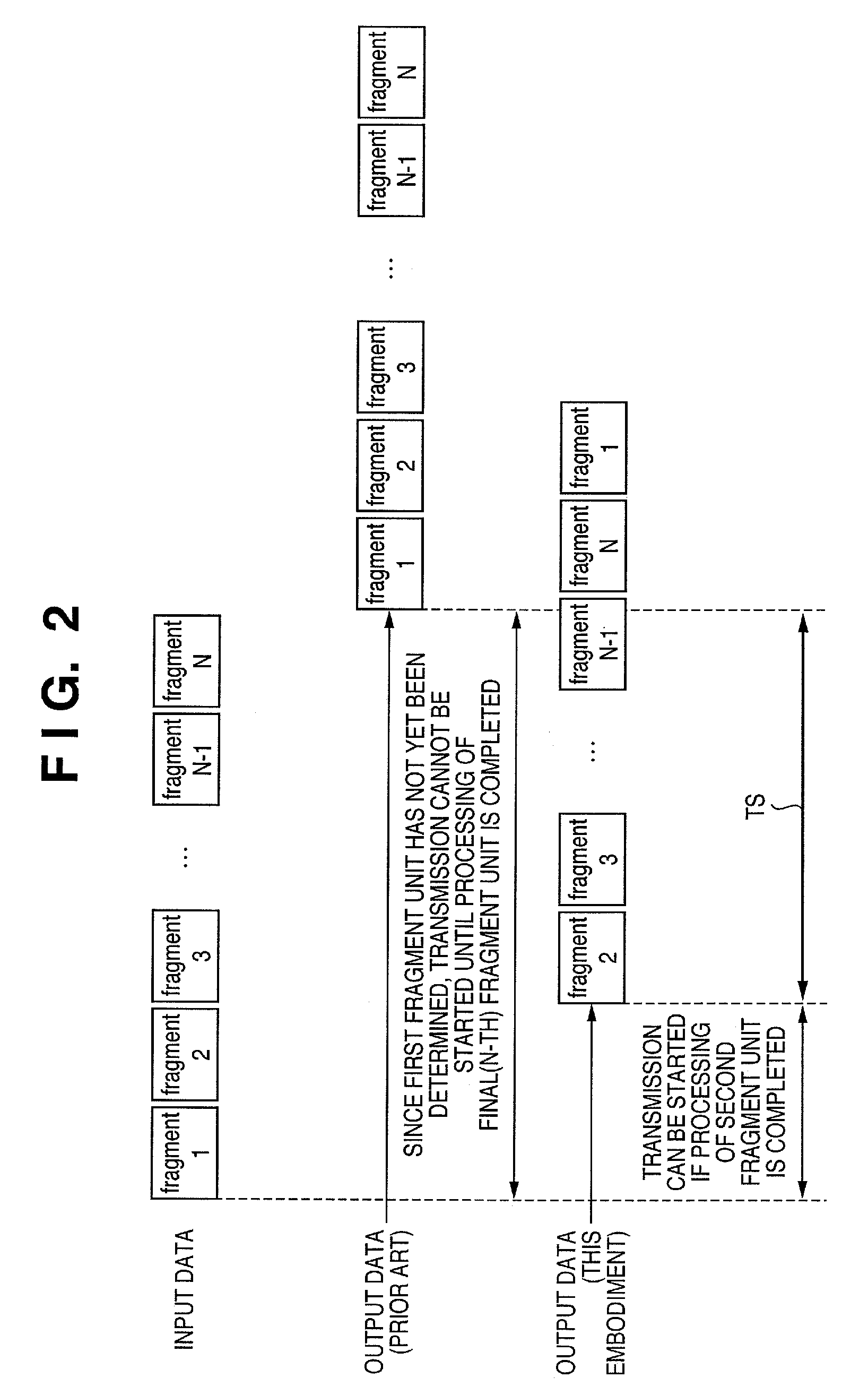

Communication apparatus and method

InactiveUS20090232162A1Reduce output delayTime-division multiplexData switching by path configurationReal-time computingNetwork packet

A delay in packet output due to packet fragmentation processing is reduced. If input data is output upon being subjected to fragmentation processing, fragmented data, from among a plurality of fragmented data items fragmented based upon a set value in an MTU register, which belongs to a first fragmented packet containing information that is based upon all fragmented packets is stored in a fragment buffer. After all fragmented packets from a second fragmented packet onward to which other fragmented data items belong are output, the first fragmented packet is output.

Owner:CANON KK

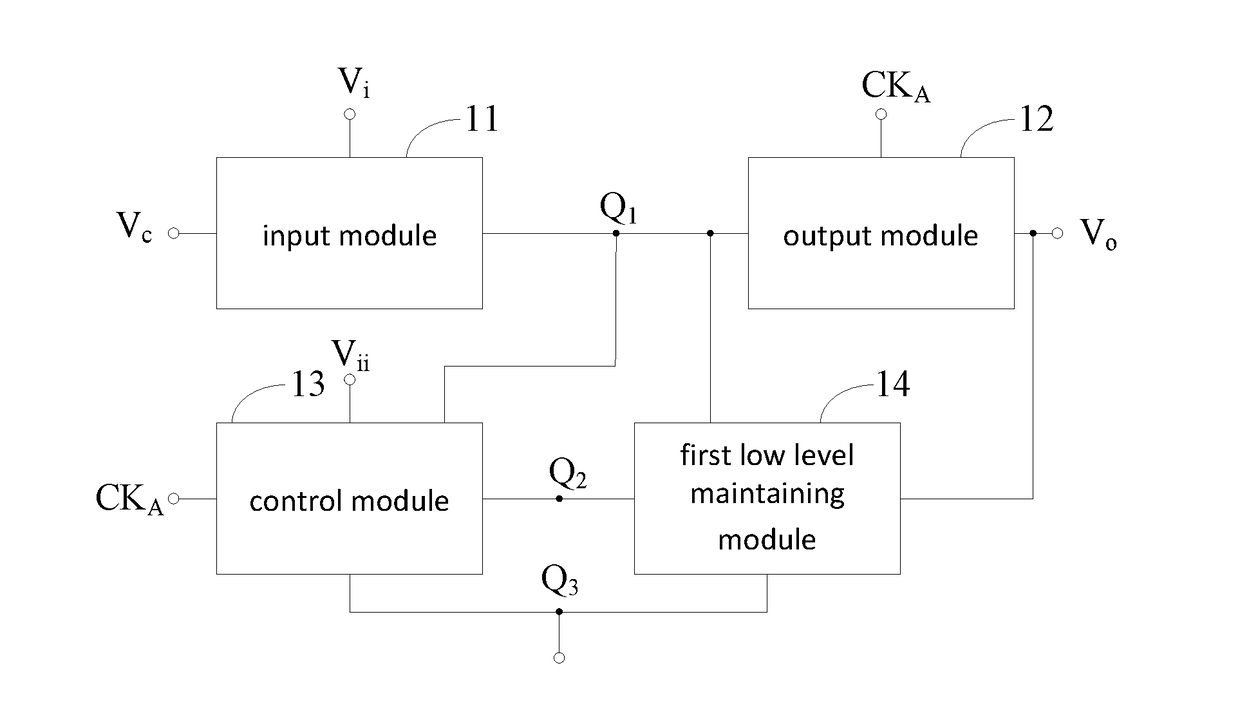

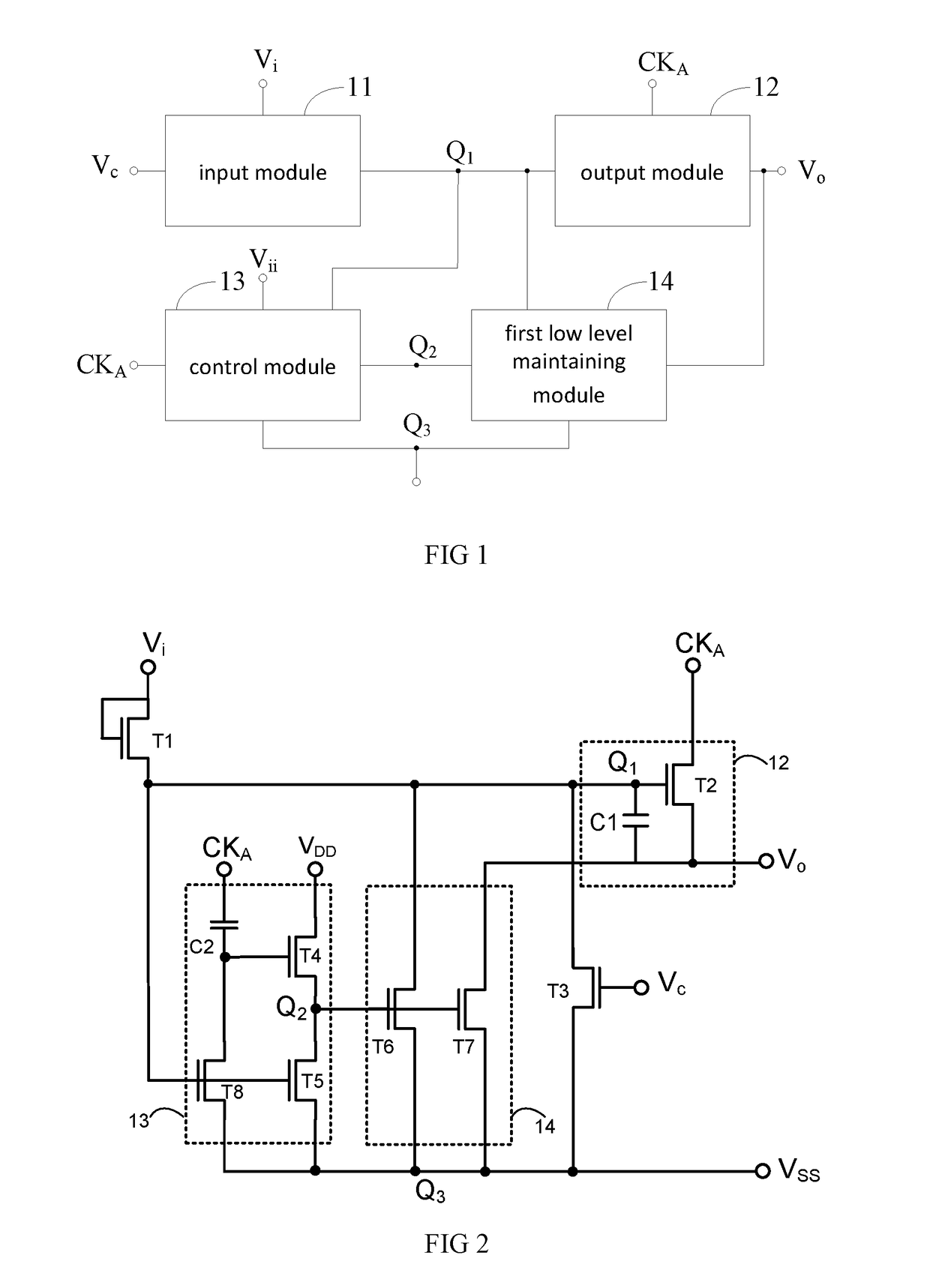

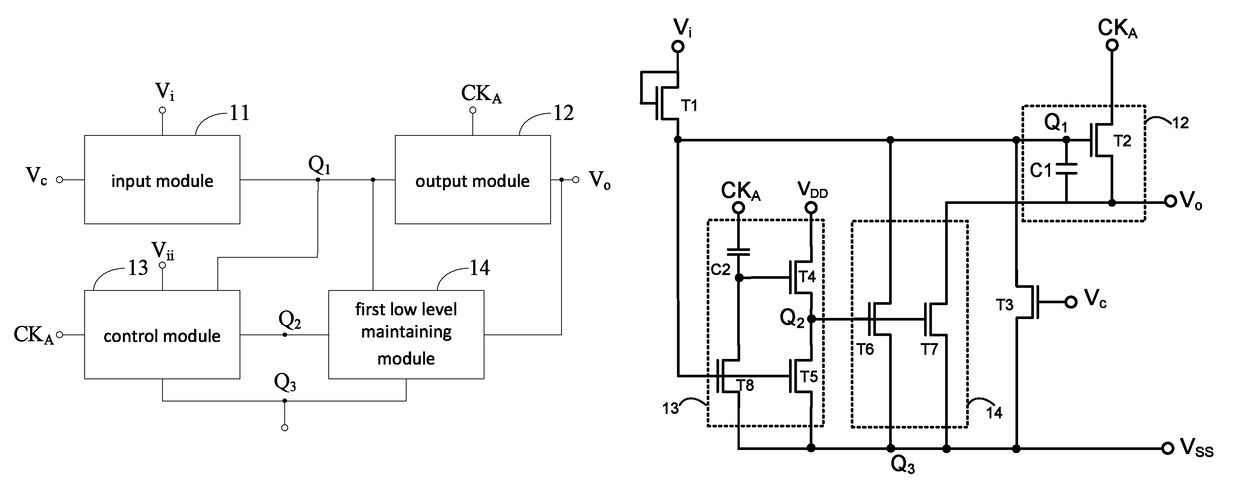

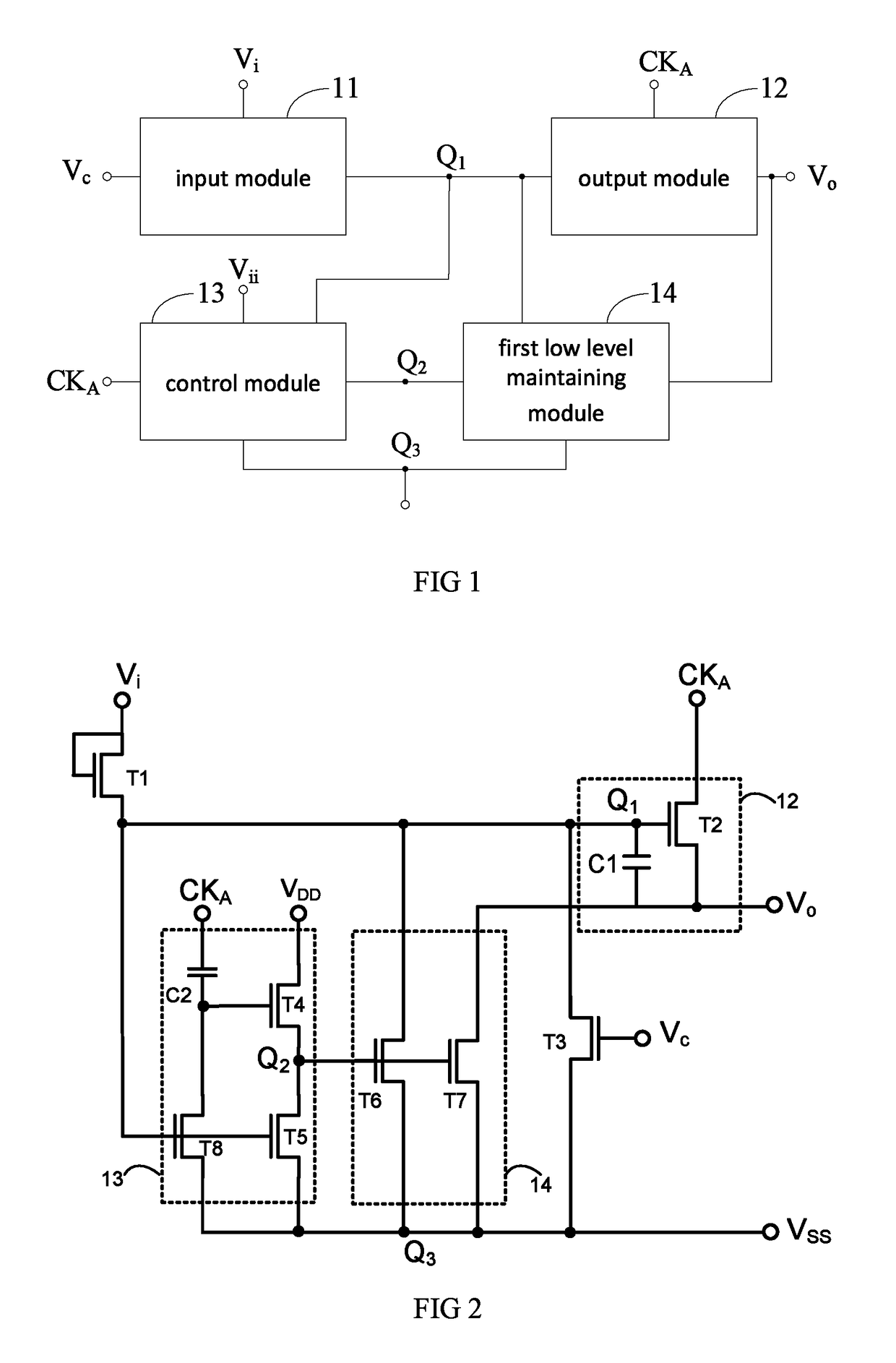

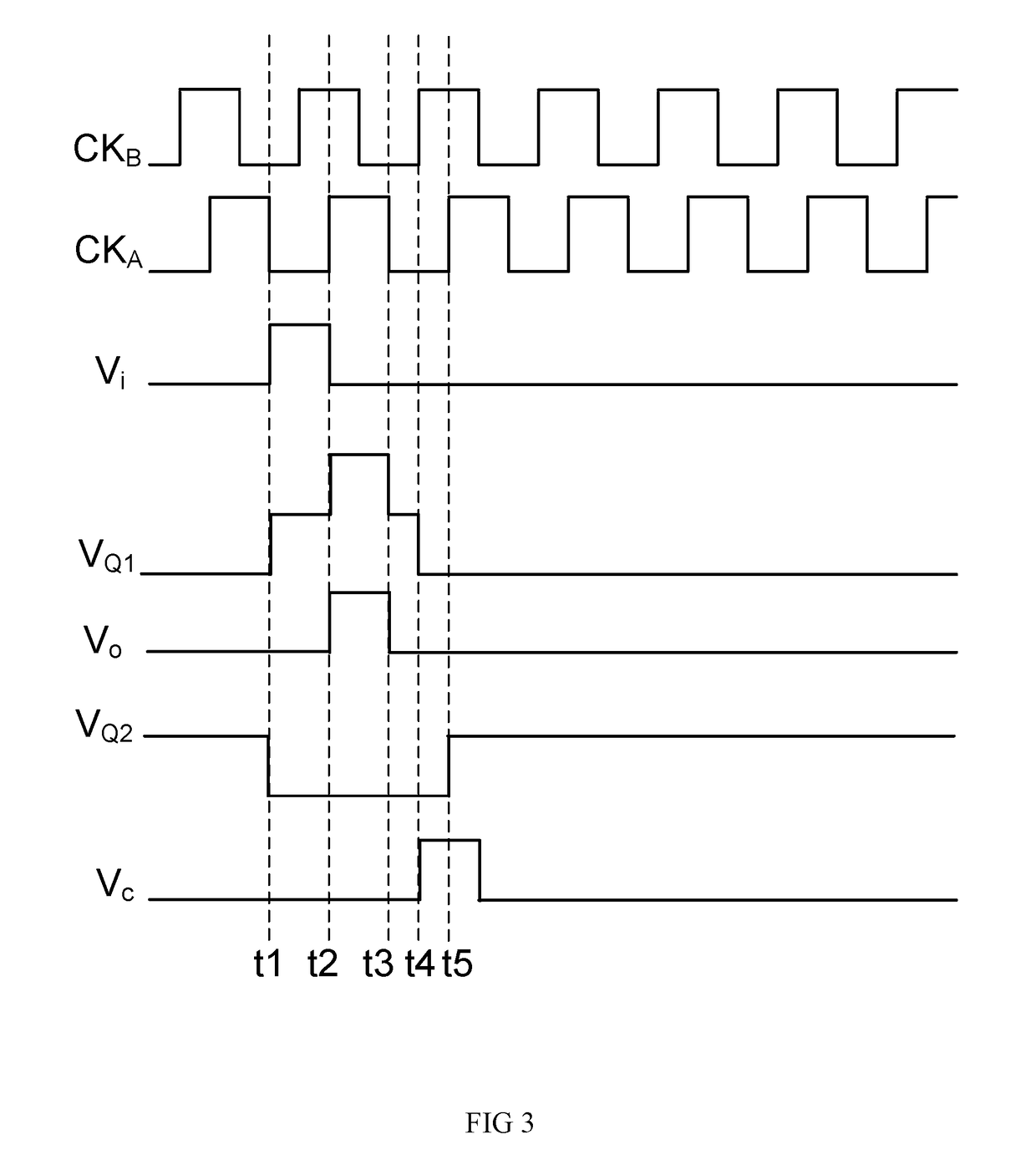

Gate driving circuits and display devices

ActiveUS20180061347A1Reduce output delayReduce leakageStatic indicating devicesDigital storageDisplay deviceDriving circuit

A gate driving circuit and a display device are disclosed. The gate driving circuit includes a control module for pulling down the level of the second control node to be at the low level before the gate strobe signals are outputted and during the output period of the gate cutoff signals. In this way, the second pull-down control end of the low level maintaining module is pulled down to be at the low levels, and the low level maintaining module is in the off state. In this way, the electrical leakage of the low level maintaining module may be reduced so as to decrease the output delay of the gate signals and to enhance the efficiency of the circuit.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Output buffer circuit

ActiveUS7656201B2Reduce output delayFast switching speedTransistorElectronic switchingEngineeringCapacitor

Owner:RENESAS ELECTRONICS CORP

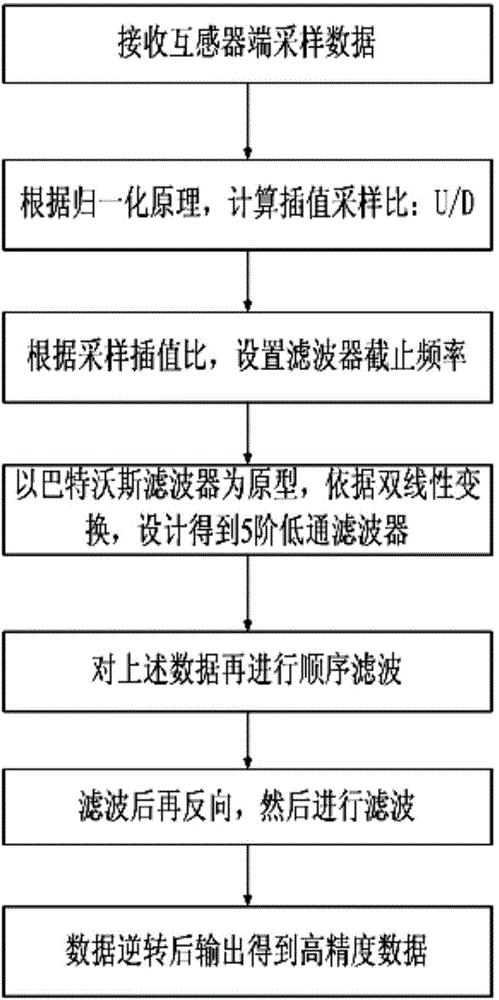

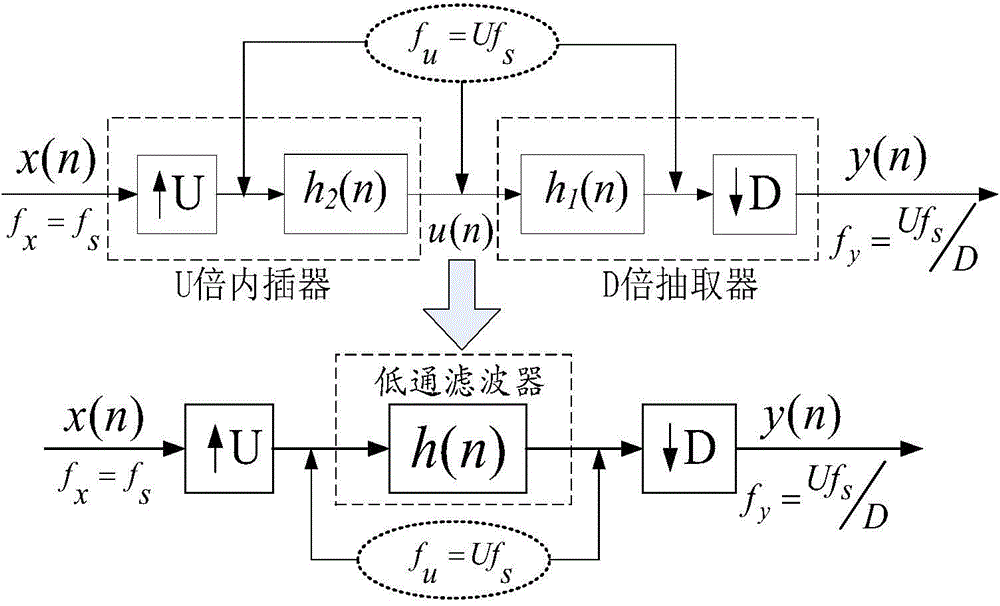

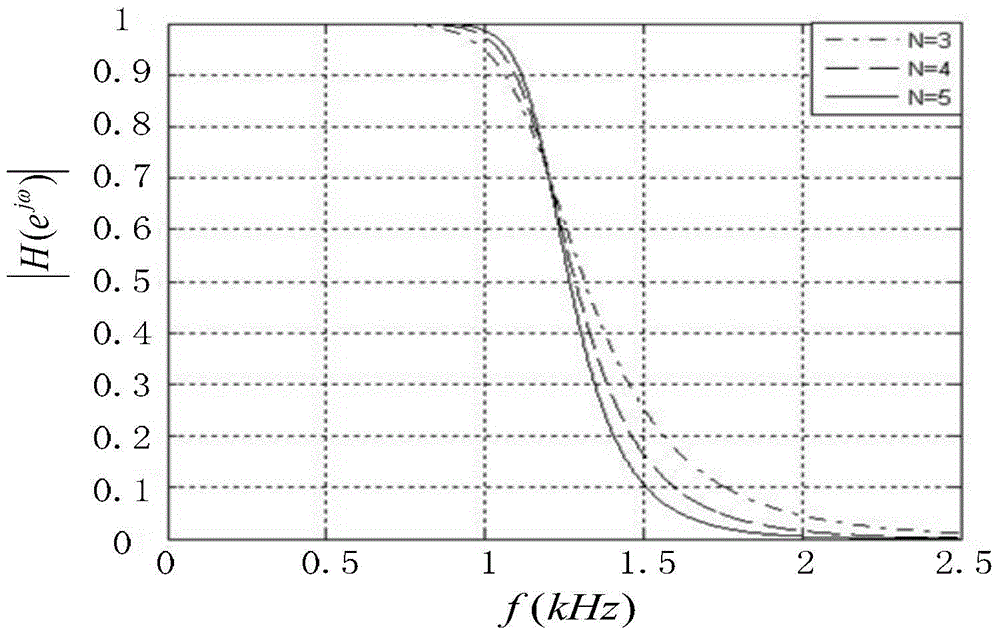

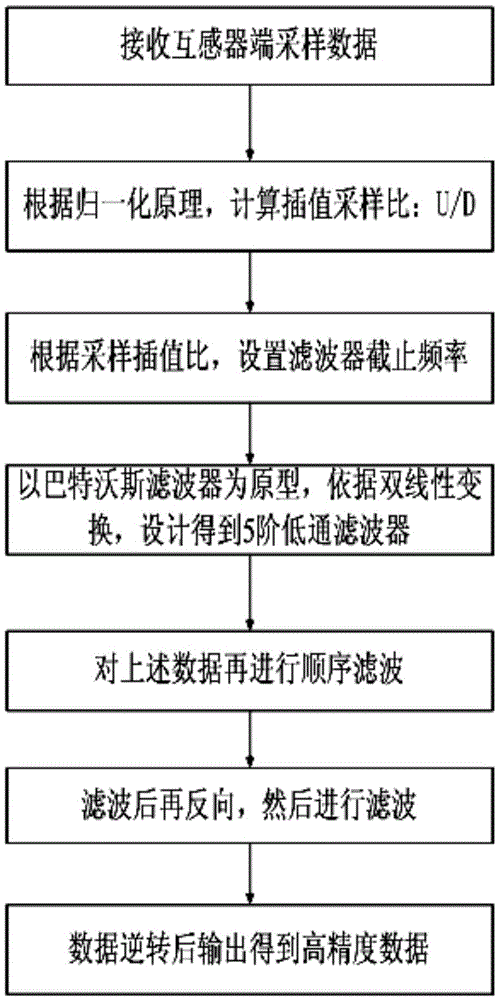

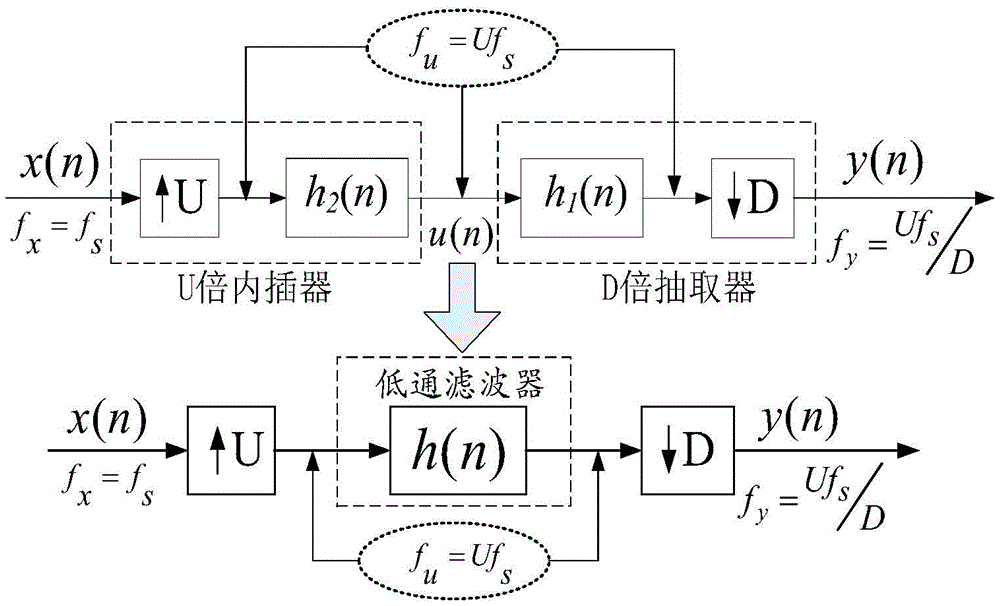

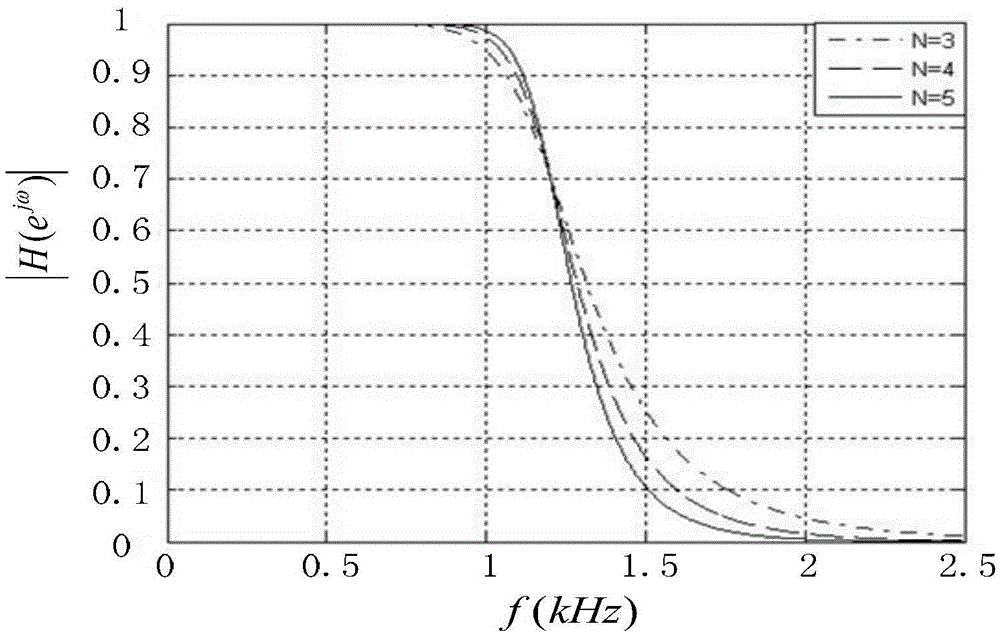

Rapid filtering method for conversion of multiple digital source sampling frequencies in photoelectric transformer

InactiveCN103607180AGood frequency selectionNo aliasing artifactsDigital technique networkAnti-aliasingLow-pass filter

The invention discloses a rapid filtering method for conversion of multiple digital source sampling frequencies in a photoelectric transformer. According to the rapid filtering method, conversion of any fractional multiple sampling frequencies is achieved by cascading interpolation and extraction, and based on a Butterworth analog filter, the cut-off frequency of the analog filter is calculated according to the different digital source sampling frequencies so that the anti-aliasing and anti-image effect can be achieved; an equation parameter of a low pass filter in a domain z is obtained by sampling bilinear transformation according to the principle of the maximum smoothness of a pass band of the filter and a narrowest transitional zone of the filter; the FRR method is adopted for filtering and reverse design, and the output signal sequence of the maximum smoothness and zero-phase distortion is finally obtained. According to the rapid filtering method, in differential protection of the photoelectric transformer, lower-order rapid filtering is achieved so that the maximum output smoothness and the zero phase can be obtained. The rapid filtering method is simple, practical and beneficial for rapid protection, can reduce errors caused by aliasing of the frequencies, and achieves the uniformization of the sampling frequencies.

Owner:SOUTHEAST UNIV

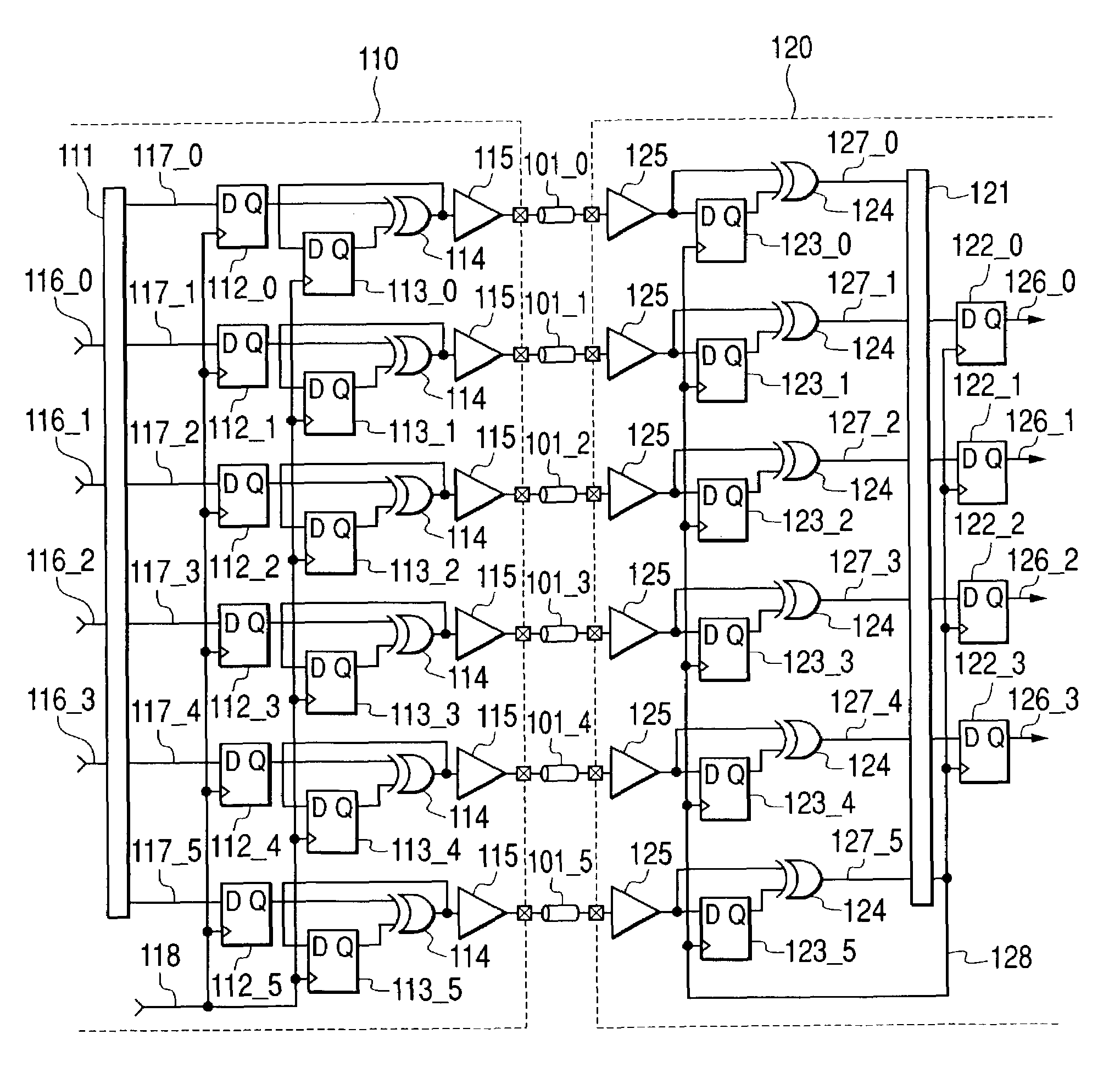

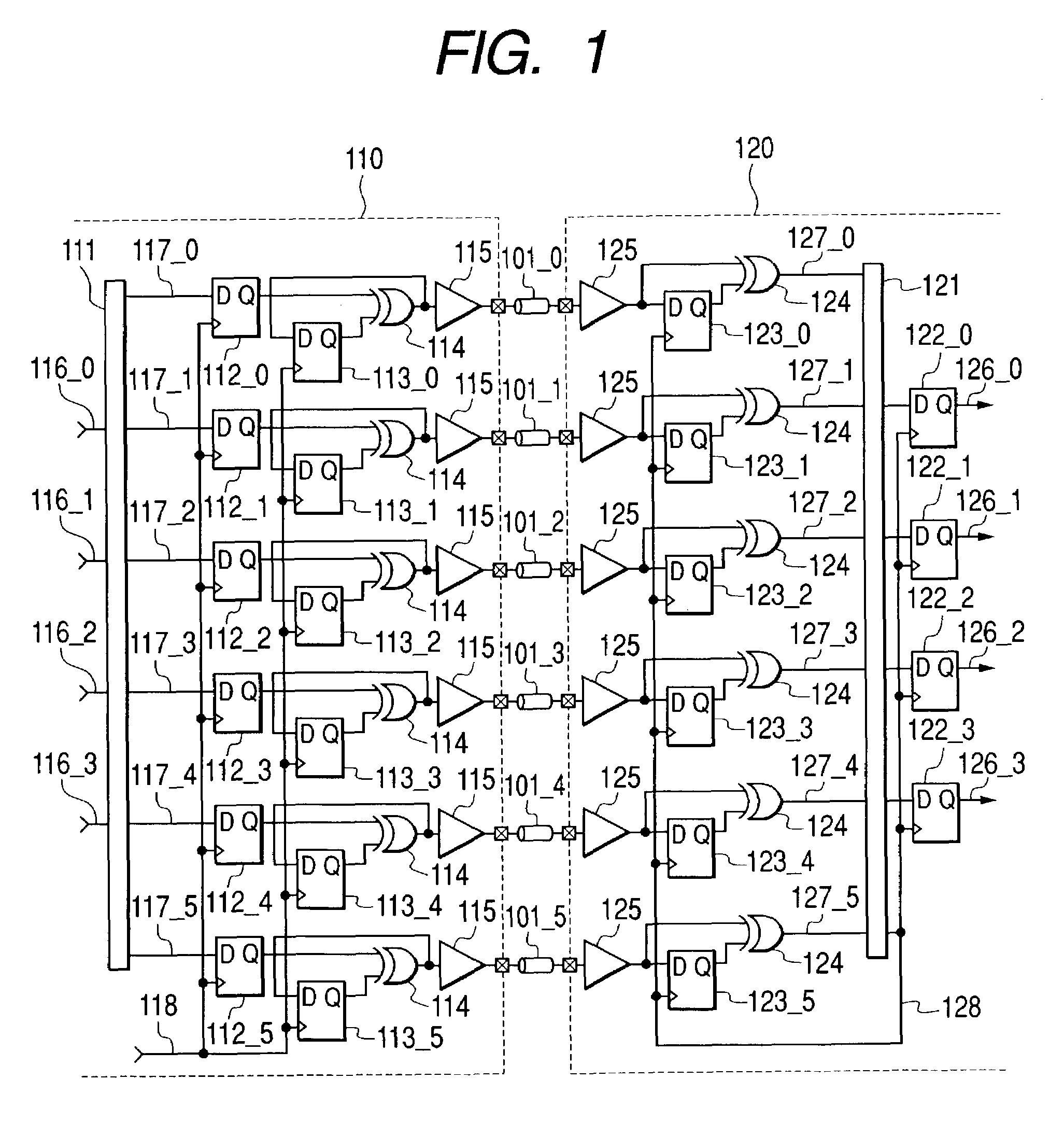

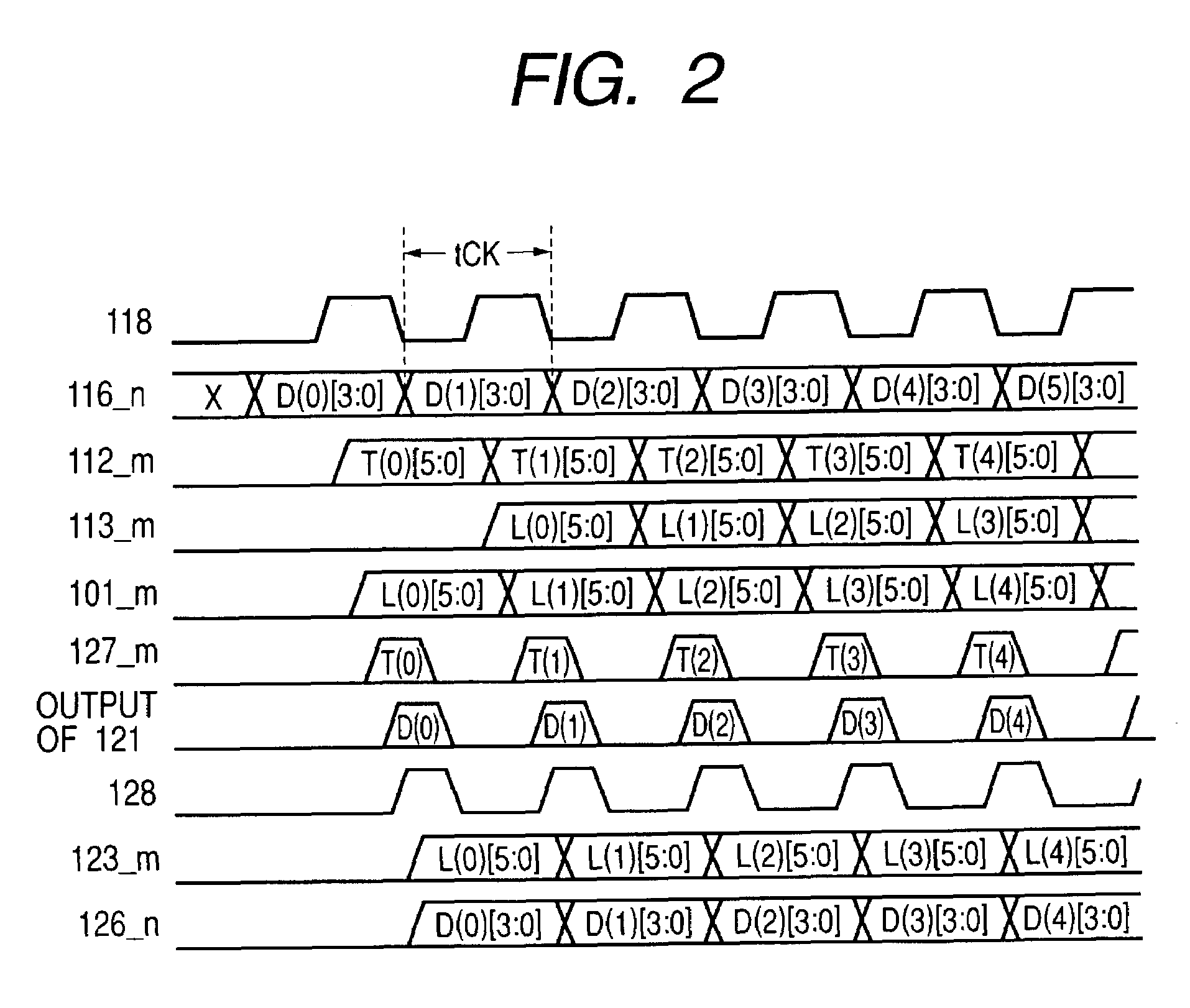

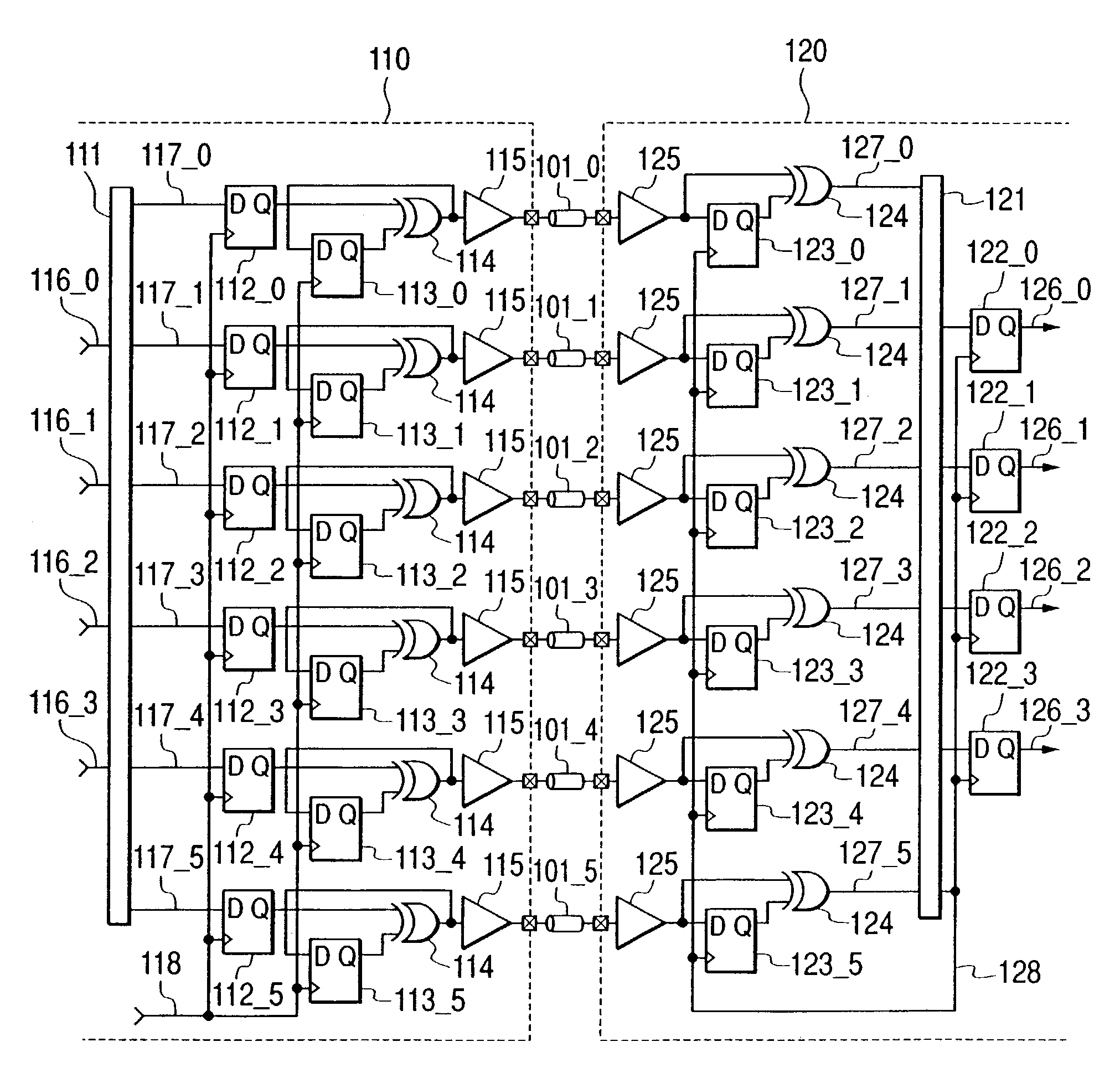

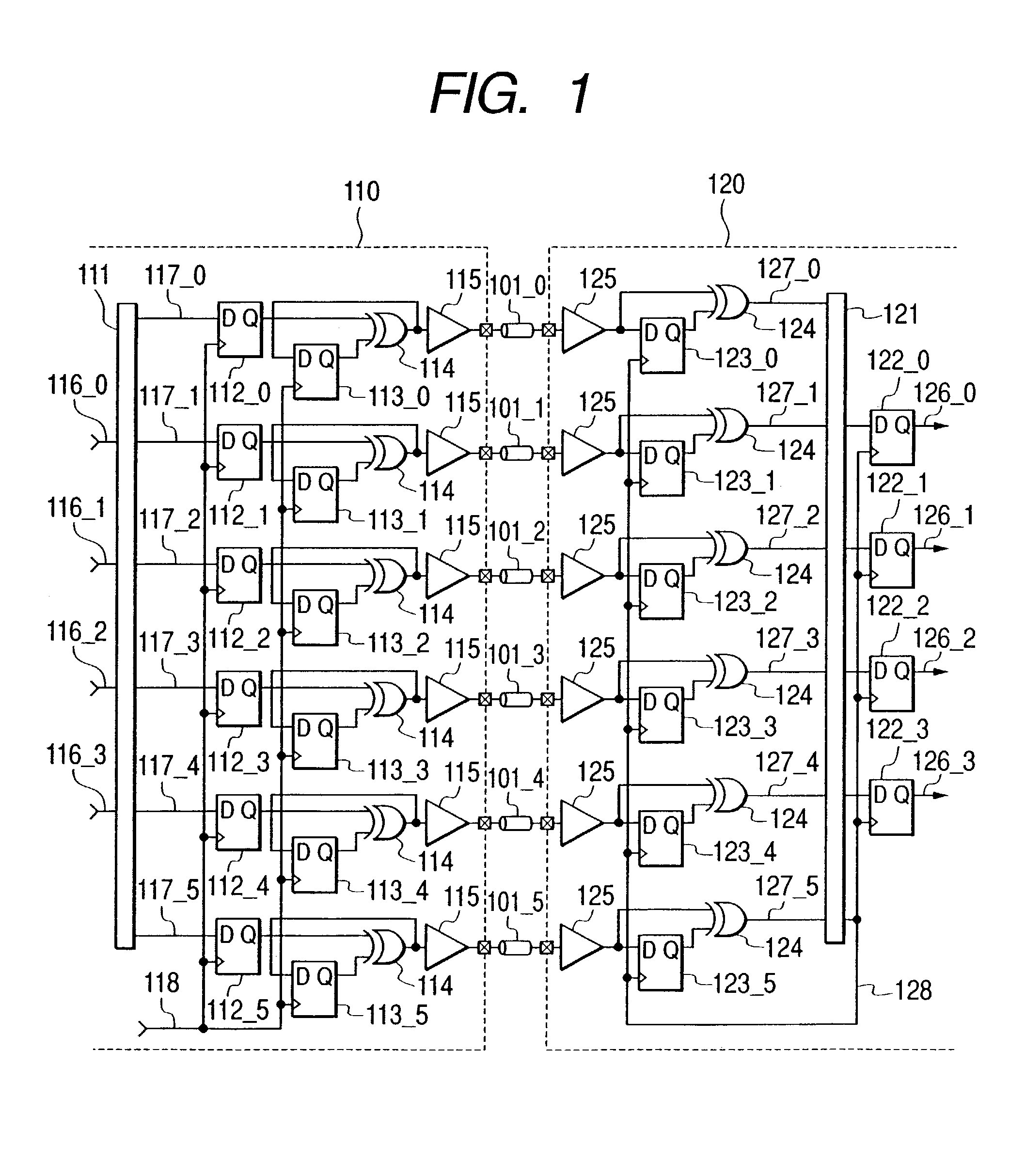

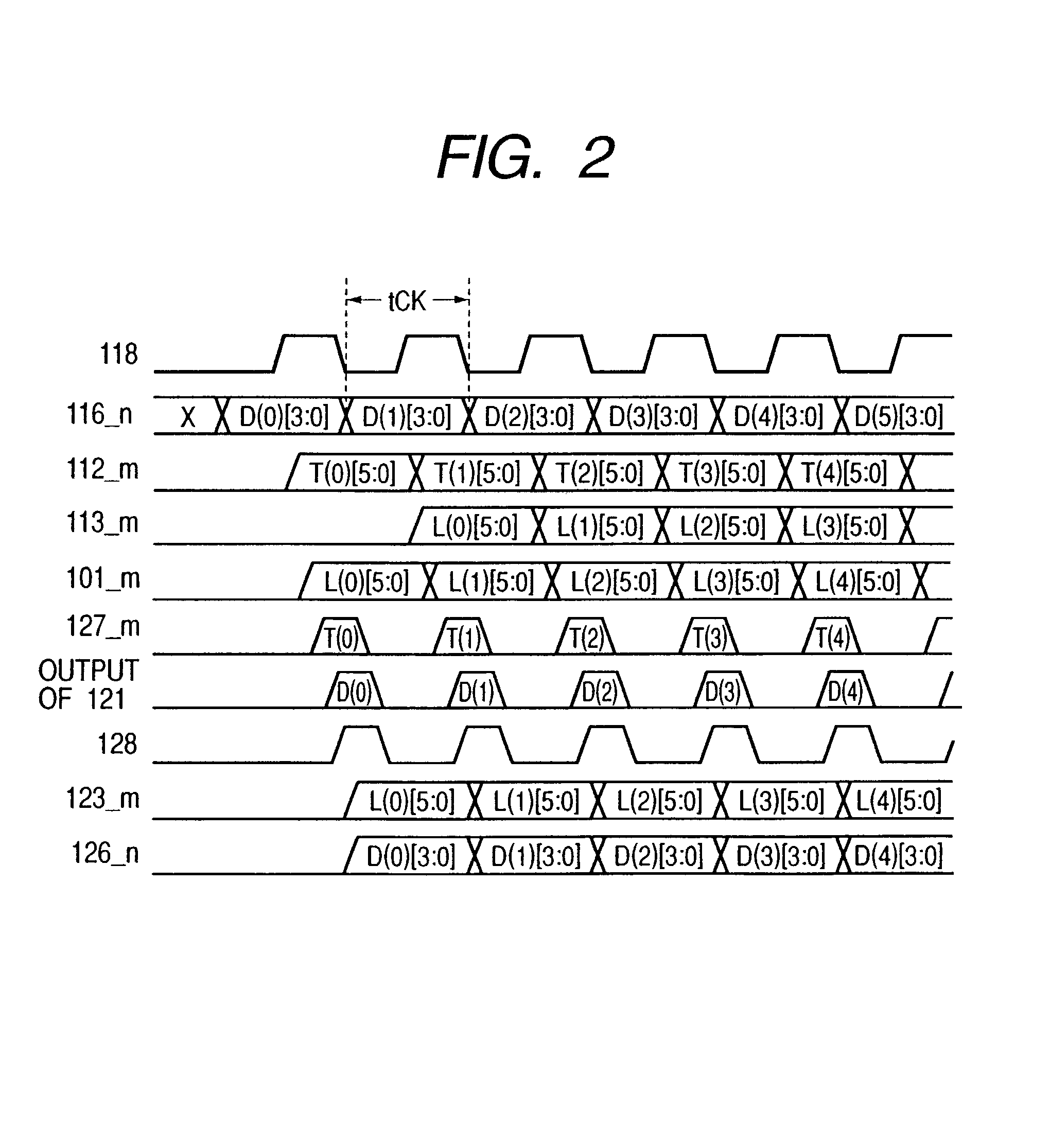

Data communication method and data communication device and semiconductor device

InactiveUS7319730B2Small amount of changeReduce output delayChannel dividing arrangementsPhase-modulated carrier systemsComputer hardwareData encoding

The present invention provides a data communication method and a data communication device capable of performing high-speed data communication by using a parallel link and higher-speed data communication by reducing a timing skew. A data communication method includes: a step of encoding data of N bits (N being 2 or larger) to transmission data of M bits (M being 3 or larger) on a transmission side; a step of generating a transmission signal in which transition takes place in at least one level of any of the transmission data synchronously with a transmission clock and transmitting the transmission signal to a transmission line on the transmission side; a step of recognizing transition in the signal of M bits received via the transmission line and detecting the reception data of M bits synchronized with the transmission clock on a reception side; and a step of decoding the reception data of M bits to the data of N bits.

Owner:RENESAS ELECTRONICS CORP

Single event transient pulse resisting CMOS circuit

The invention provides a single event transient pulse resisting CMOS circuit which comprises a first buffer and a second buffer. The input end of the first buffer is connected with the input signal of the first buffer, and the output signal of the first buffer is connected with the data input end of a first transmission door. The input end of the second buffer is connected with the input signal of the second buffer, and the output signal of the second buffer is connected with the data input end of a second transmission door. The data output signal of the first transmission door is connected with the data output end of the second transmission door and the input end of a first phase inverter. The output signal of the first phase inverter is connected with the input end of a second phase inverter, the grid electrode of an NMOS tube in the first transmission door and the grid electrode of a PMOS tube in the second transmission door. The output signal of the second phase inverter is connected with the grid electrode of a PMOS tube in the first transmission door and the grid electrode of an NMOS tube in the second transmission door and is used as the output signal of the single event transient pulse resisting CMOS circuit. According to the single event transient pulse resisting CMOS circuit, the buffers with different pull-up / pull-down capacities are used for filtering two classes of single particle pulses, the corresponding signals are output by controlling the transmission doors, and the single event transient pulse resisting CMOS circuit has the advantages of having few MOS tubes, being strong in single event transient pulse resisting capacity and good in filtering effect and the like.

Owner:北京中科微投资管理有限责任公司

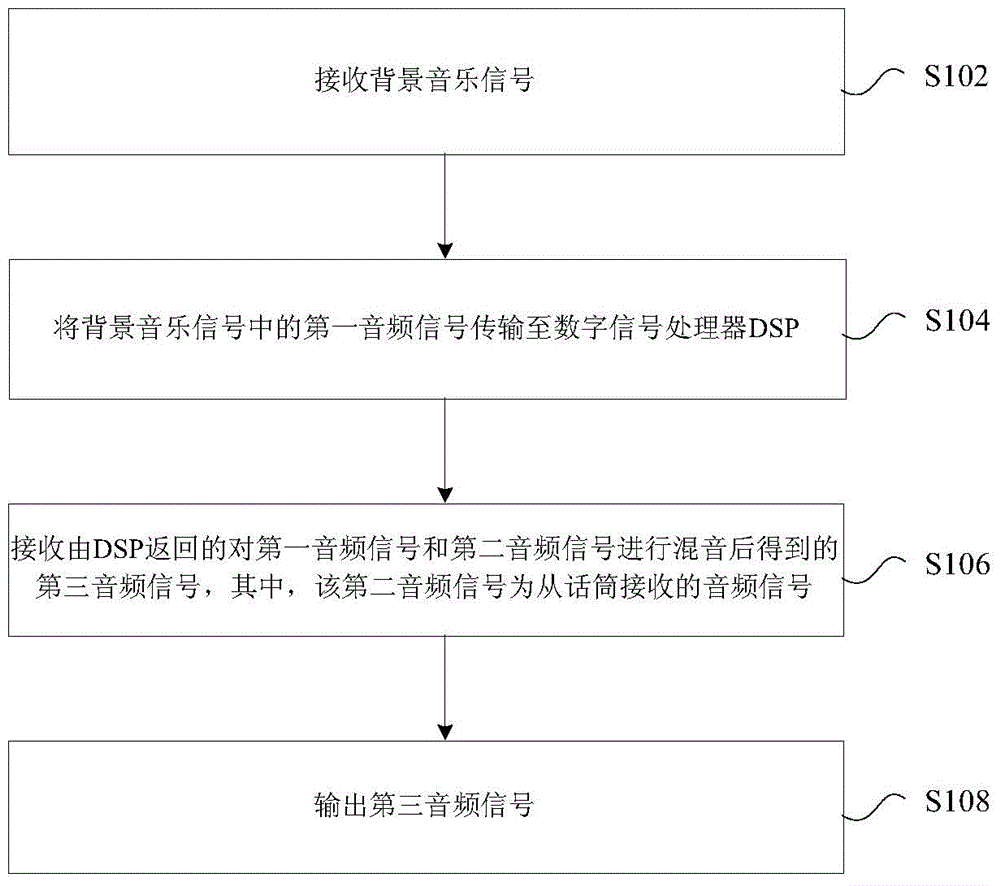

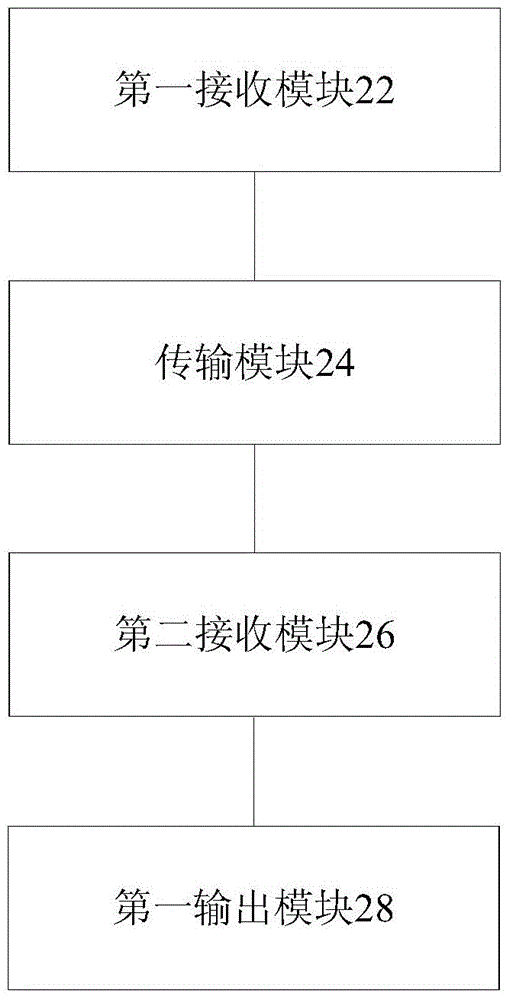

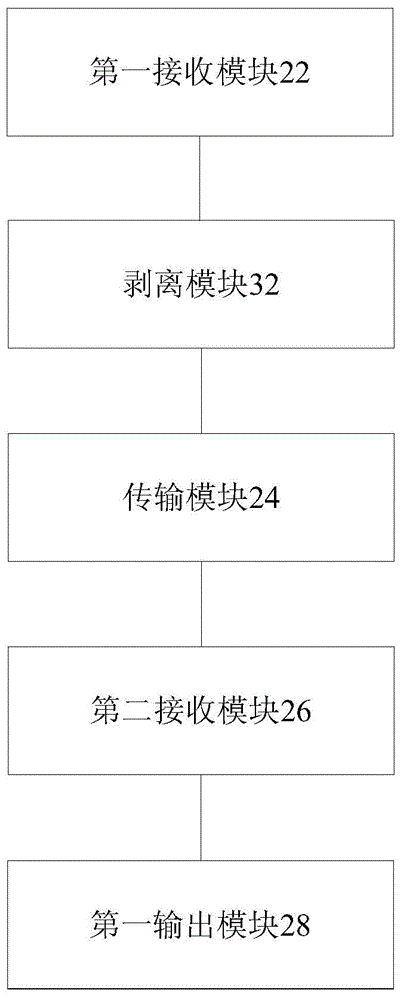

Audio signal output method and device, terminal, and system

InactiveCN105491302ASolve the problem of low experienceImprove experienceTelevision system detailsElectrophonic musical instrumentsDigital signal processingTime delays

The invention provides an audio signal output method and device, a terminal, and a system. The method comprises the steps: enabling a first audio signal of a background music signal to be transmitted to a DSP (digital signal processor); receiving a third audio signal formed by the mixing of the first audio signal, returned by the DSP, with a second audio signal, wherein the second audio signal is an audio signal received from a microphone; and outputting the third audio signal. According to the invention, the method solves problems in related technologies that the audio output is large in time delay and the user experience is poor, thereby reducing the time delay of audio output, and improving the user experience.

Owner:ZTE CORP

Communication apparatus and method

InactiveUS7733865B2Reduce output delayTime-division multiplexData switching by path configurationNetwork packetCommunication device

Owner:CANON KK

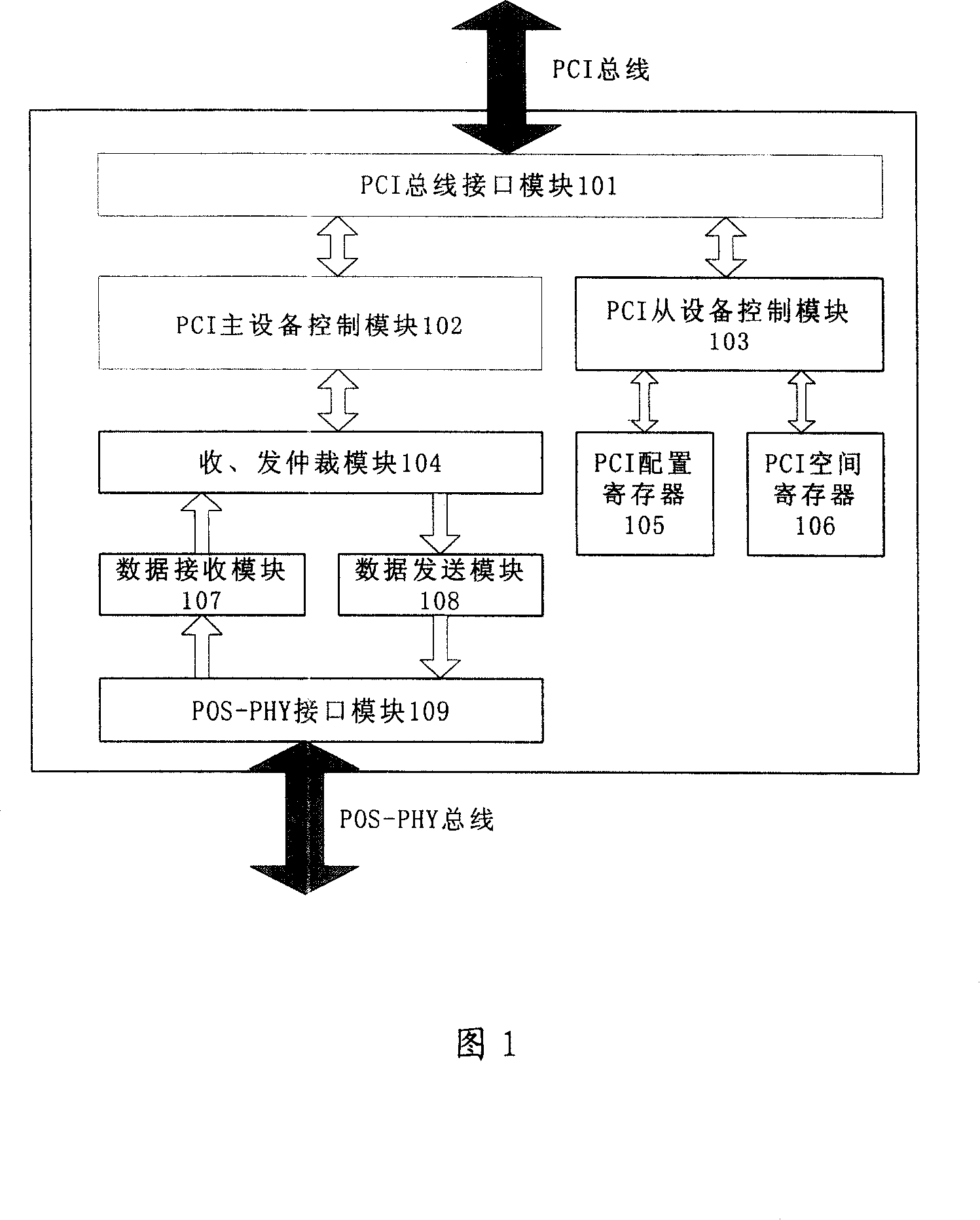

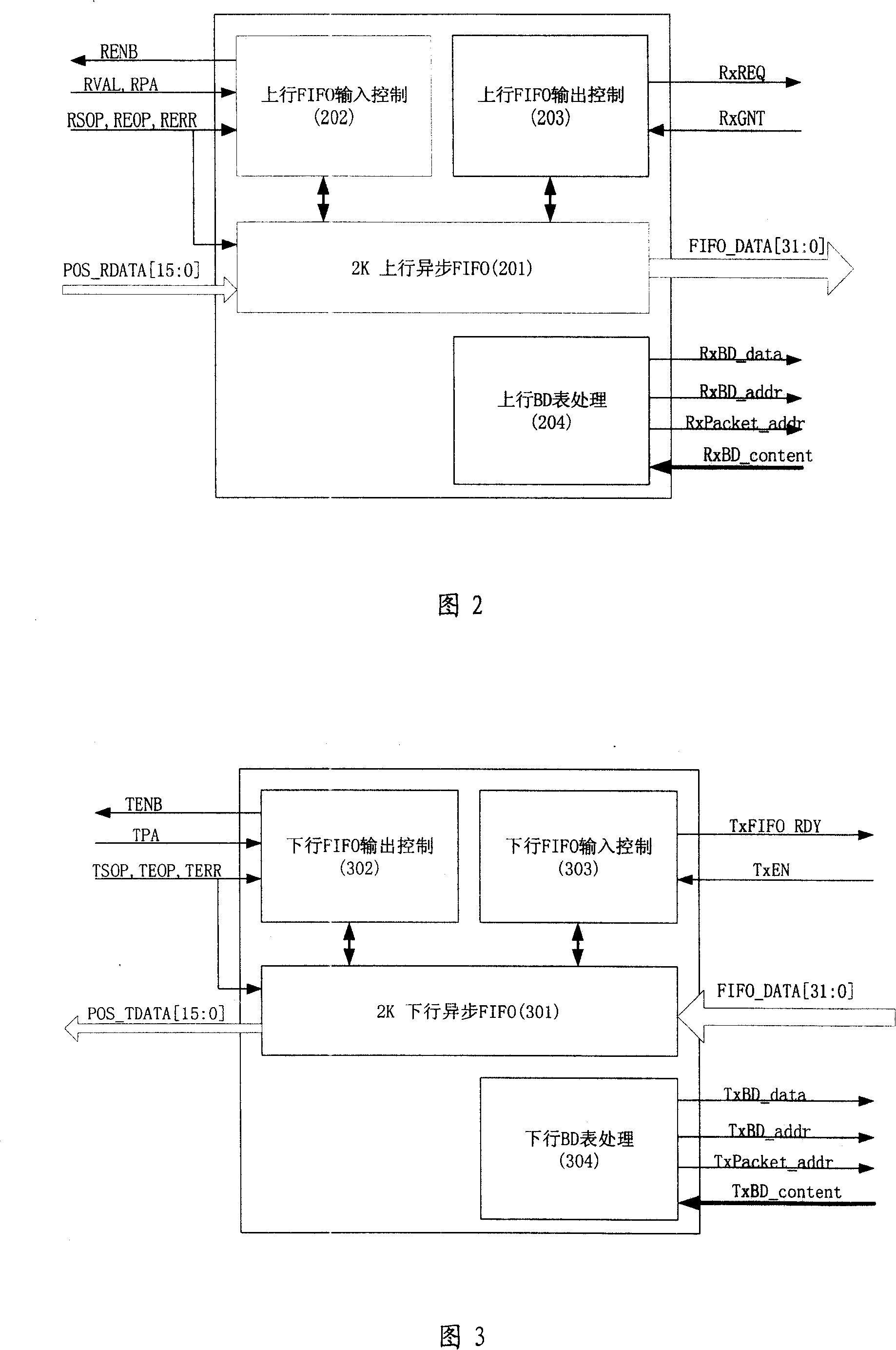

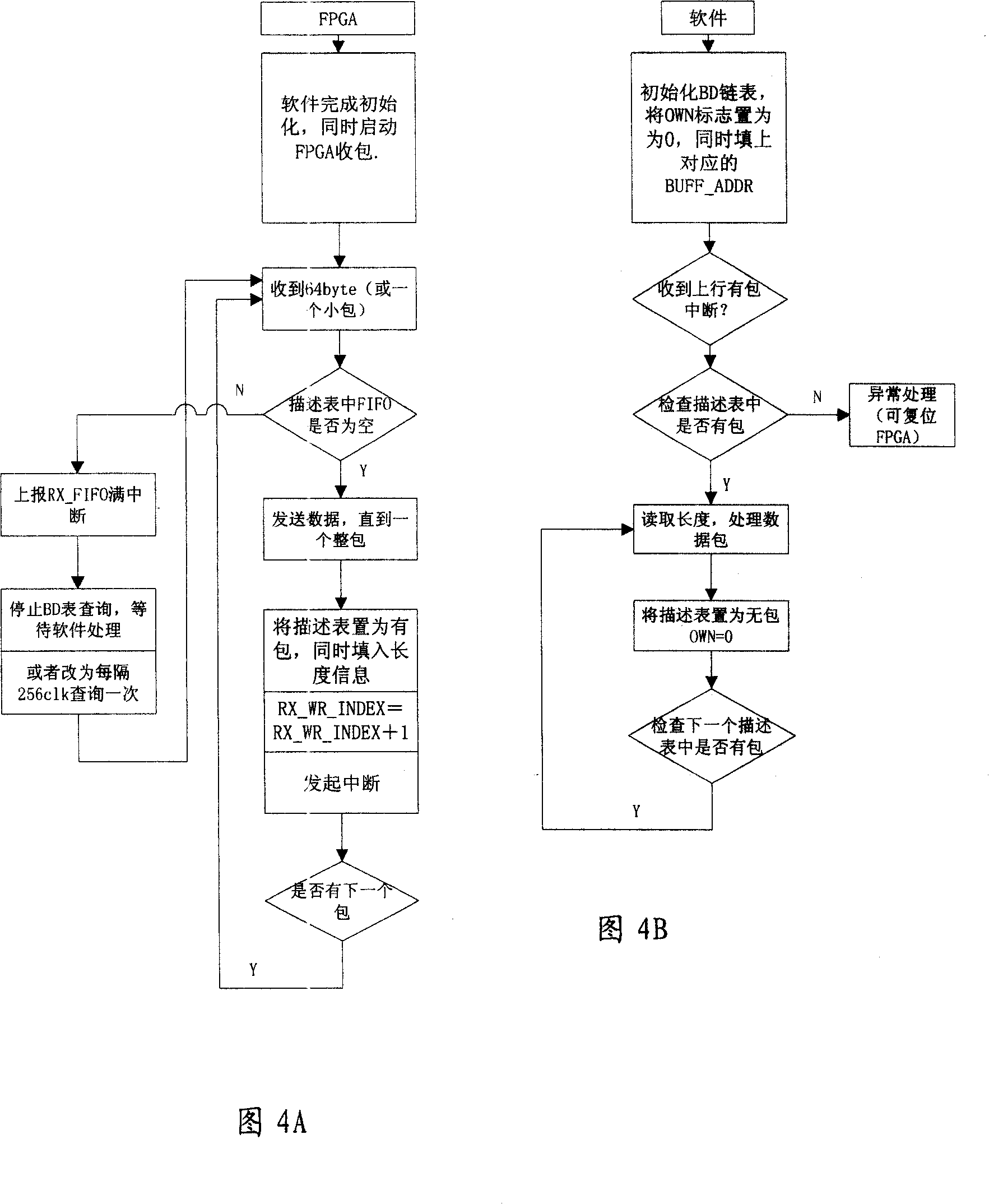

Device and method of data pocket retransmission between POS-PHY bus and PCI bus

InactiveCN100375484CReduce occupancyReduce the number of accesses to the PCI busData switching networksBus interfaceEmbedded system

The invention relates to a device and method for repeating data packet between the POS-PHY bus and the PCI bus, the device is a bridge transferring device, which includes following submodules: PCI bus interface model, PCI primary device control model, PCI slave device control model, transmission and receiving arbitrating model, PCI configuring register, PCI space register, data receiving model, data transmitting model, POS-PHY interface model; the PCI bus interface model is connected to the PCI bus, the POS-PHY interface model is connected to POS-PHY bus outer. The device and method complete the repeating of data packet between the POS-PHY bus and the PCI bus, it provides a method for transmitting data packet on the PCI bus with high efficiency, and the data packet is not easy to be lost.

Owner:ZTE CORP

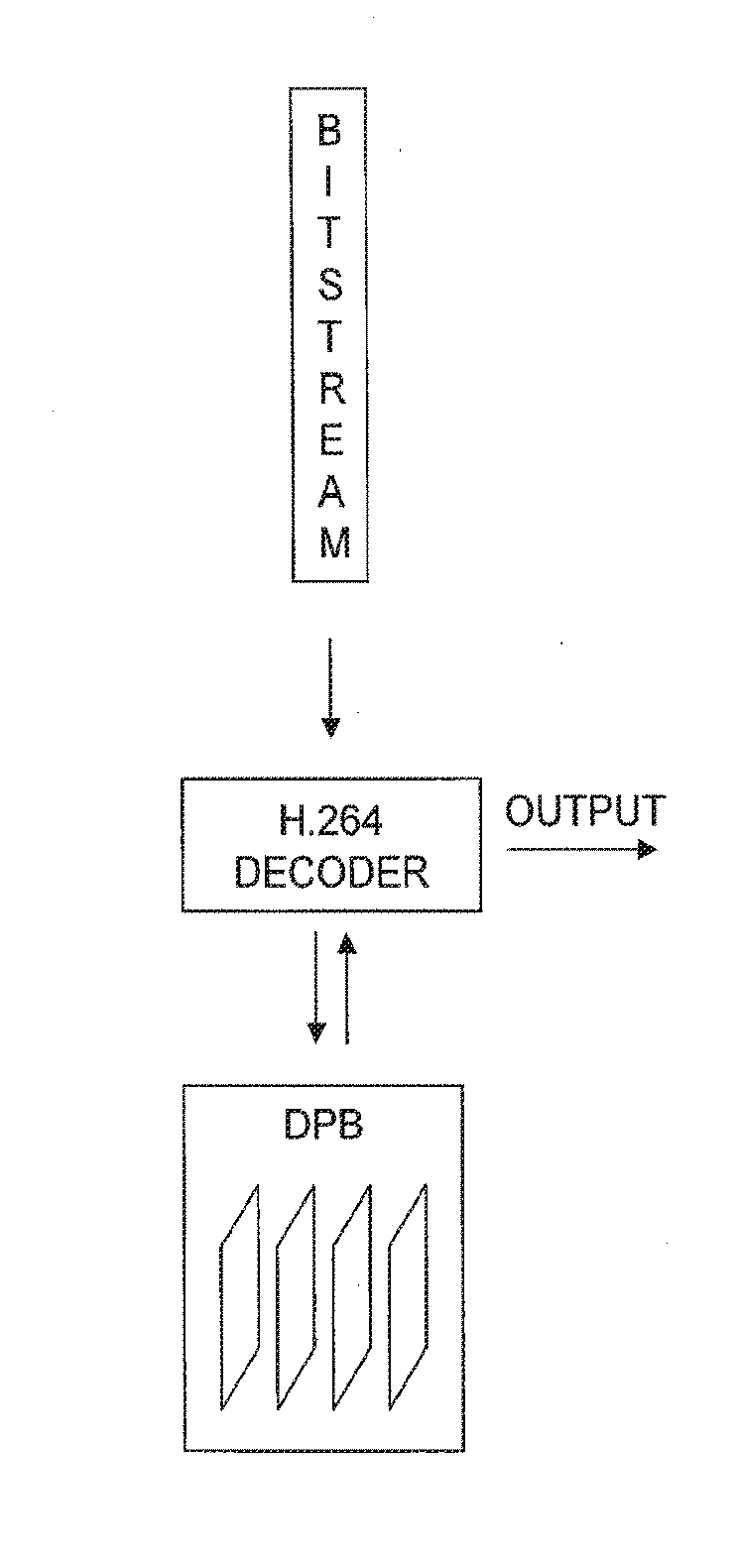

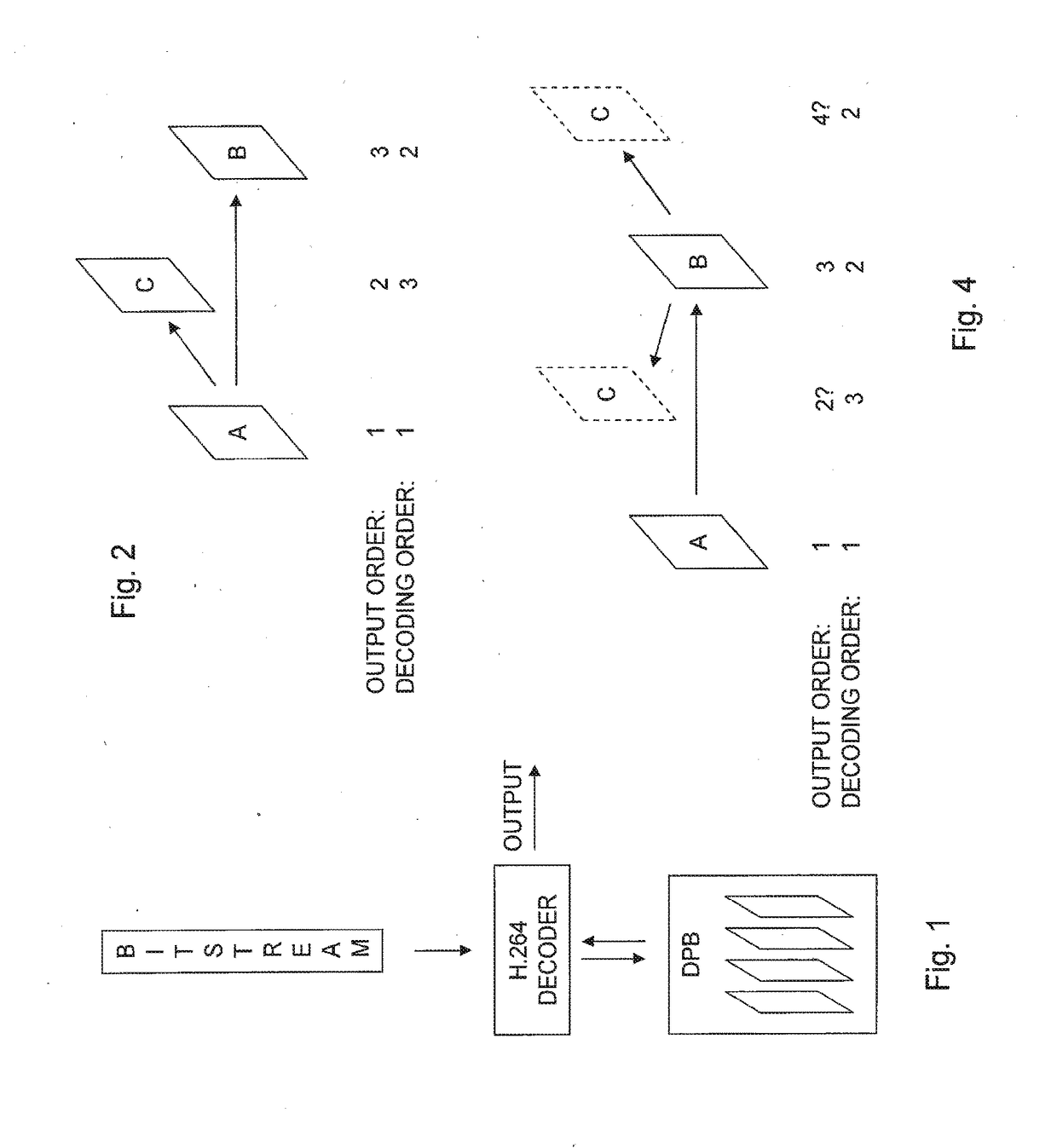

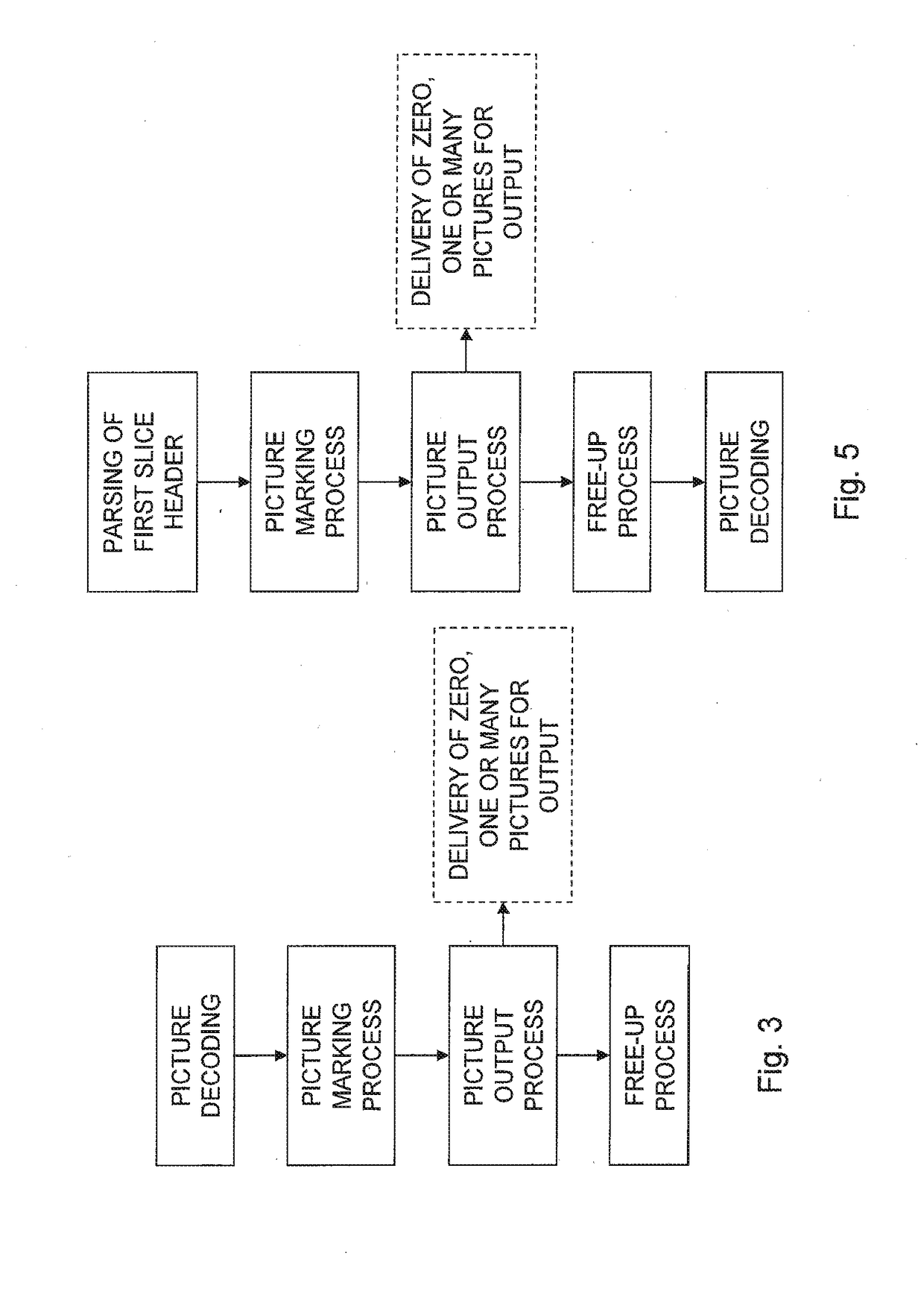

Decoding and encoding of pictures of a video sequence

ActiveUS20170264916A1Reduce output delayDigital video signal modificationComputer graphics (images)Video sequence

The embodiments reduce output delay for pictures by determining after a current picture has been decoded and stored in a decoded picture buffer, DPB, a number of pictures in the DPB that are marked as needed for output. This number is compared, after a current picture has been decoded and stored in the DPB, against a value derived form at least one syntax element present or to be present in a bitstream representing pictures of a video sequence. If this number is greater than the value a picture, which is the first picture in output order, of the pictures in the DPB that are marked as needed for output is preferably output and marked as not needed for output.

Owner:TELEFONABG L M ERICSSON PUBL

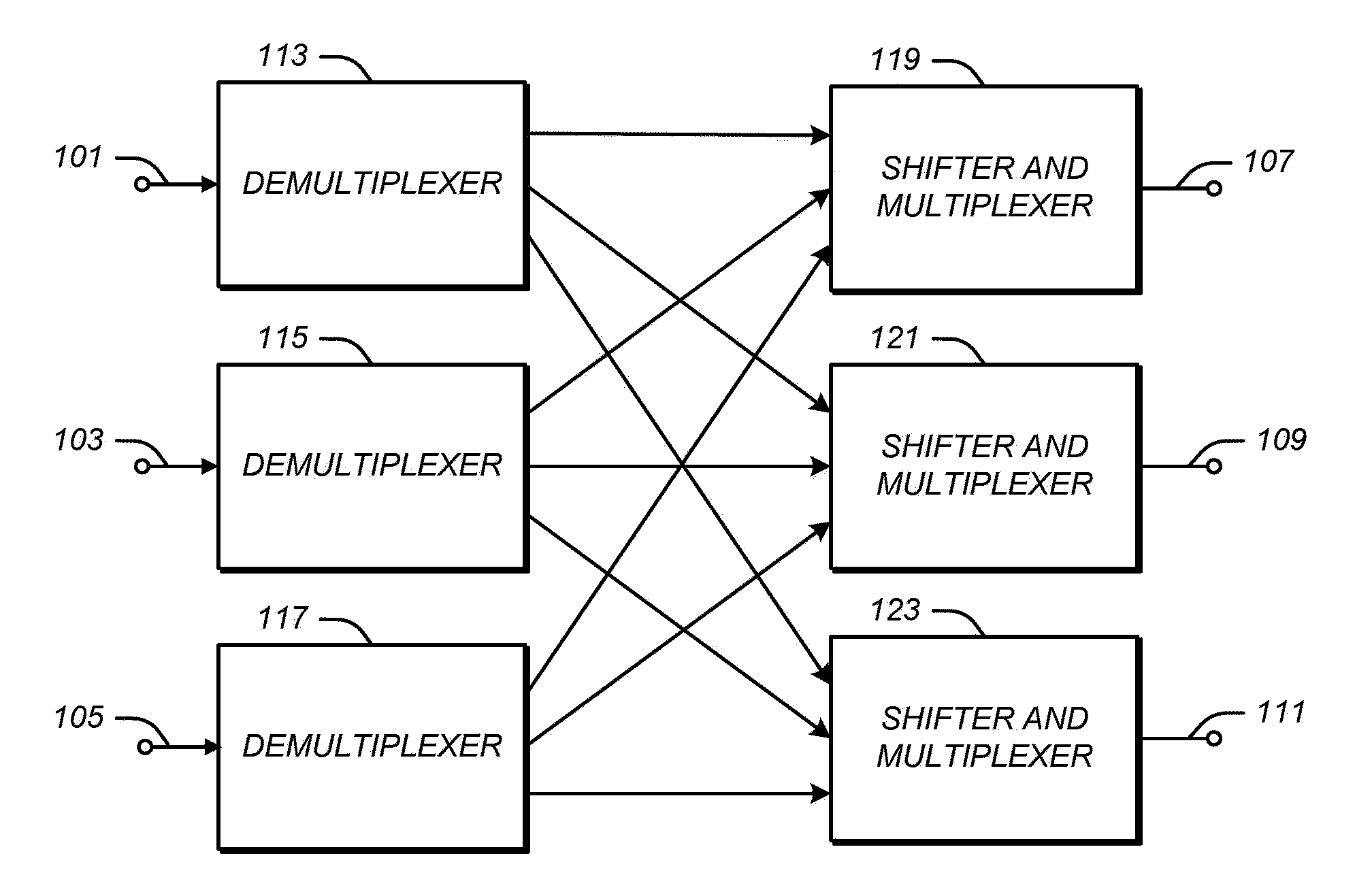

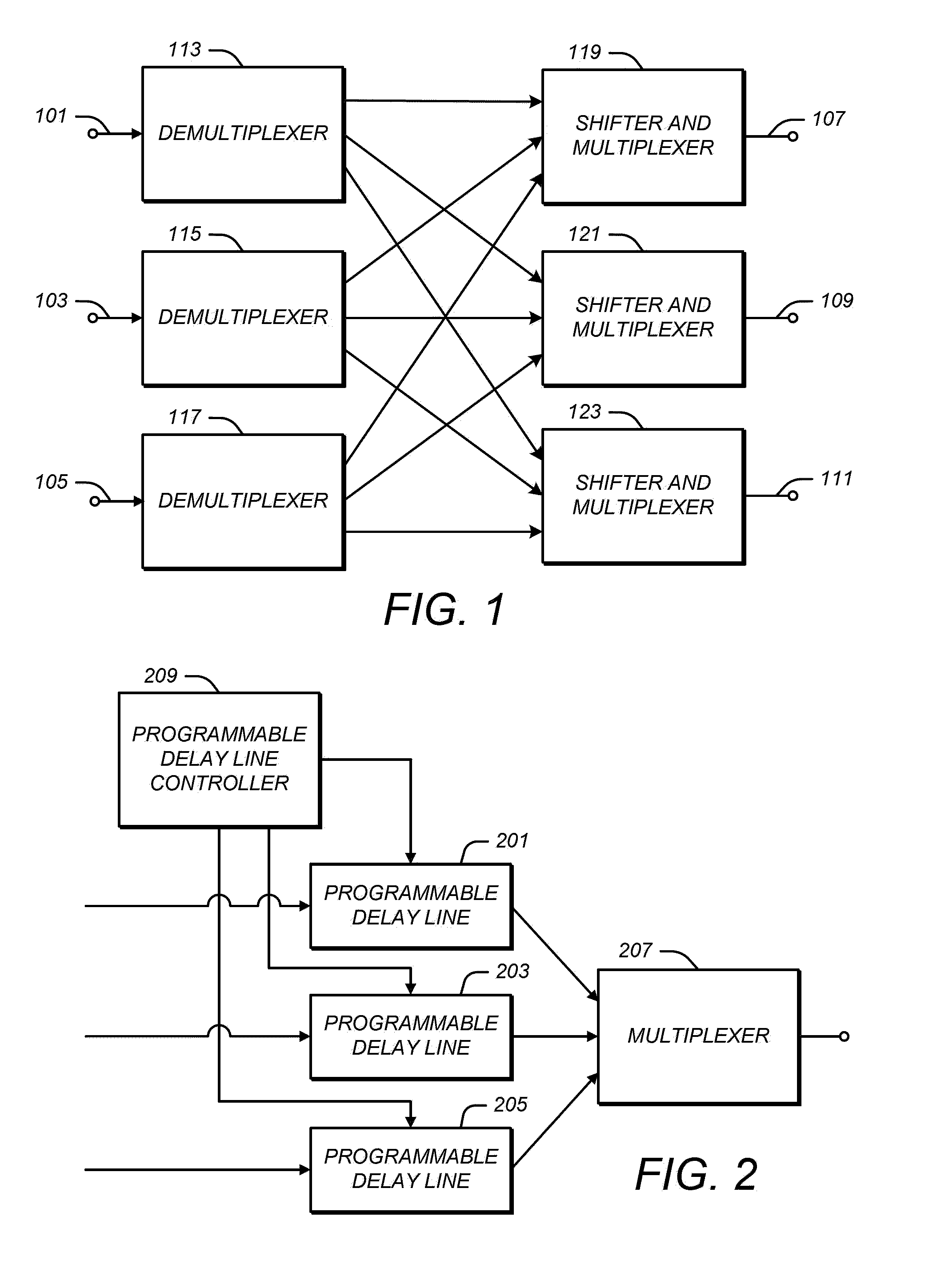

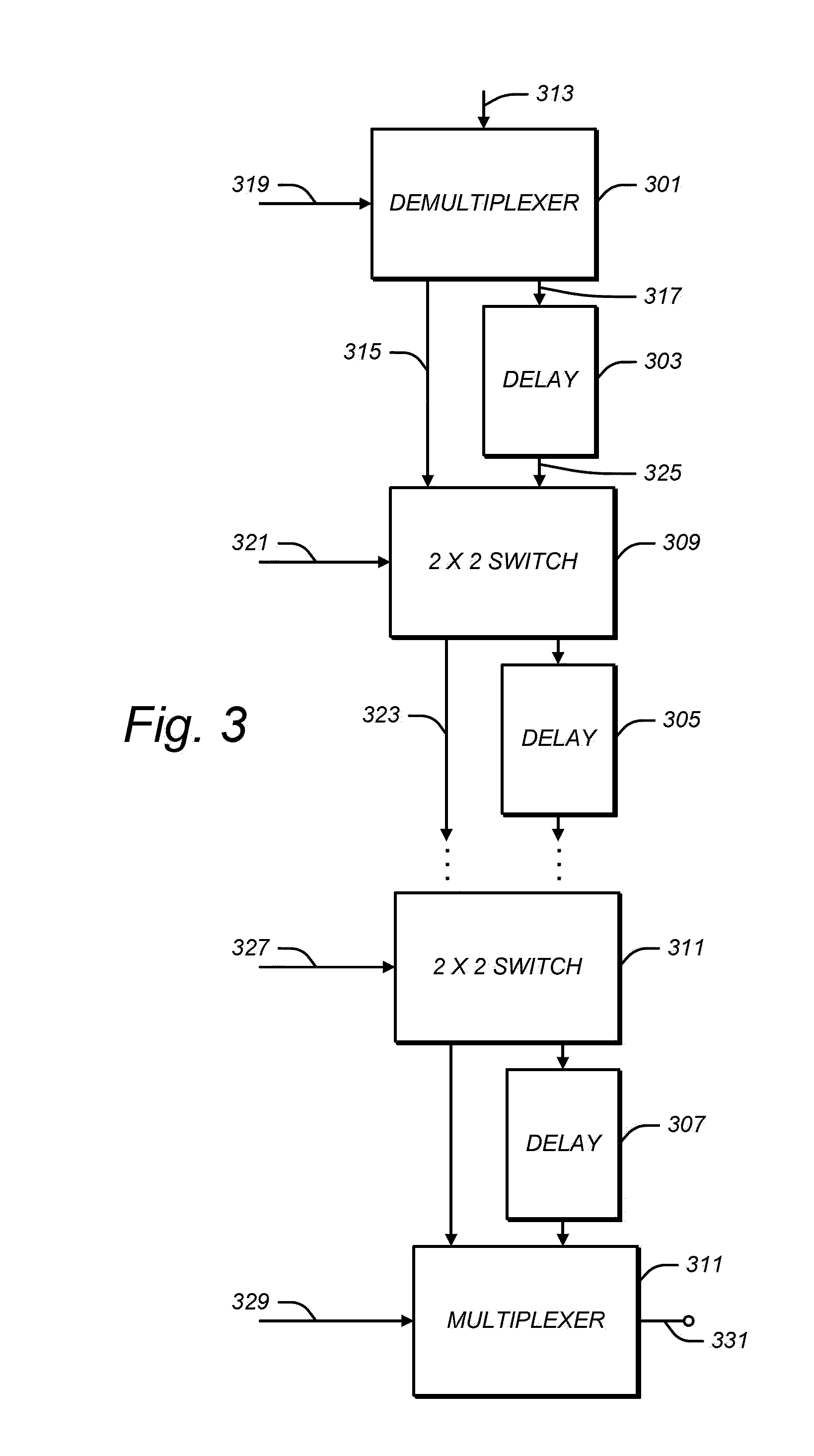

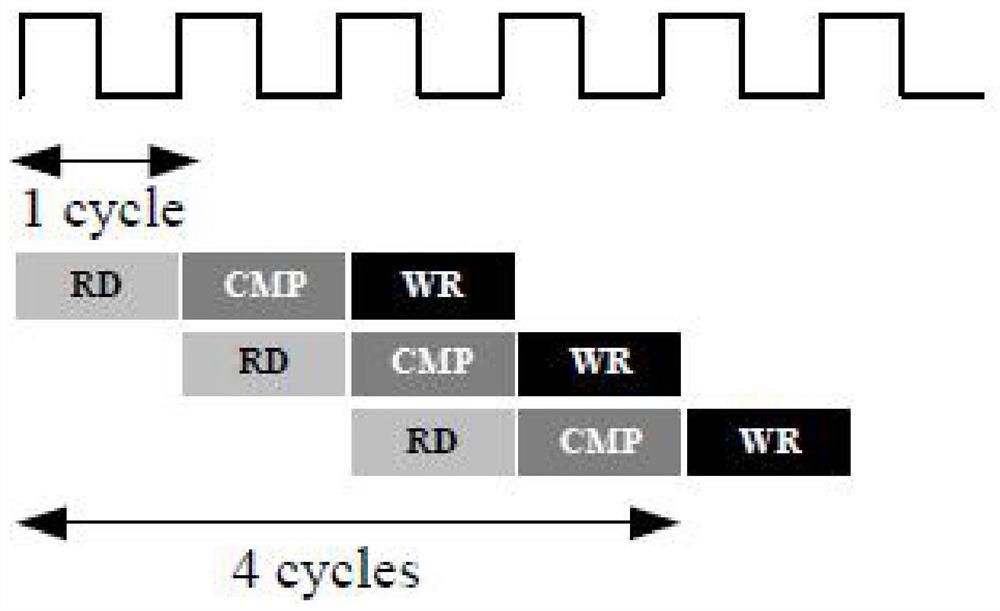

Packet Switch with Separate Look Ahead, Computation, and Shift Phases

InactiveUS20110026534A1Reduce output delayLowest possible loss of packetsMultiplex system selection arrangementsData switching by path configurationRandom access memoryOptical packet

A packet switch architecture that can switch optical packets at high throughputs without using any random access memory, without fragmenting variable length packets into fixed length fragments and reassembling them, and without converting the optical packets into electronic packets. Programmable delay lines are use which delay the output of each packet for a programmable amount which may be re-programmed while the packet is being delayed by the programmable delay line. Programmable delay line controllers manages the delays imposed by the programmable delay lines so as to have a look-ahead phase during which information about the packets is gathered and a shift phase during which the sequence of packets is shifted to match an output sequence.

Owner:UNIV OF SOUTHERN CALIFORNIA

Data communication method and data communication device and semiconductor device

InactiveUS7359471B2Small amount of changeReduce output delayChannel dividing arrangementsElectric digital data processingComputer hardwareData encoding

The present invention provides a data communication method and a data communication device capable of performing high-speed data communication by using a parallel link and higher-speed data communication by reducing a timing skew. A data communication method includes: a step of encoding data of N bits (N being 2 or larger) to transmission data of M bits (M being 3 or larger) on a transmission side; a step of generating a transmission signal in which transition takes place in at least one level of any of the transmission data synchronously with a transmission clock and transmitting the transmission signal to a transmission line on the transmission side; a step of recognizing transition in the signal of M bits received via the transmission line and detecting the reception data of M bits synchronized with the transmission clock on a reception side; and a step of decoding the reception data of M bits to the data of N bits.

Owner:RENESAS ELECTRONICS CORP

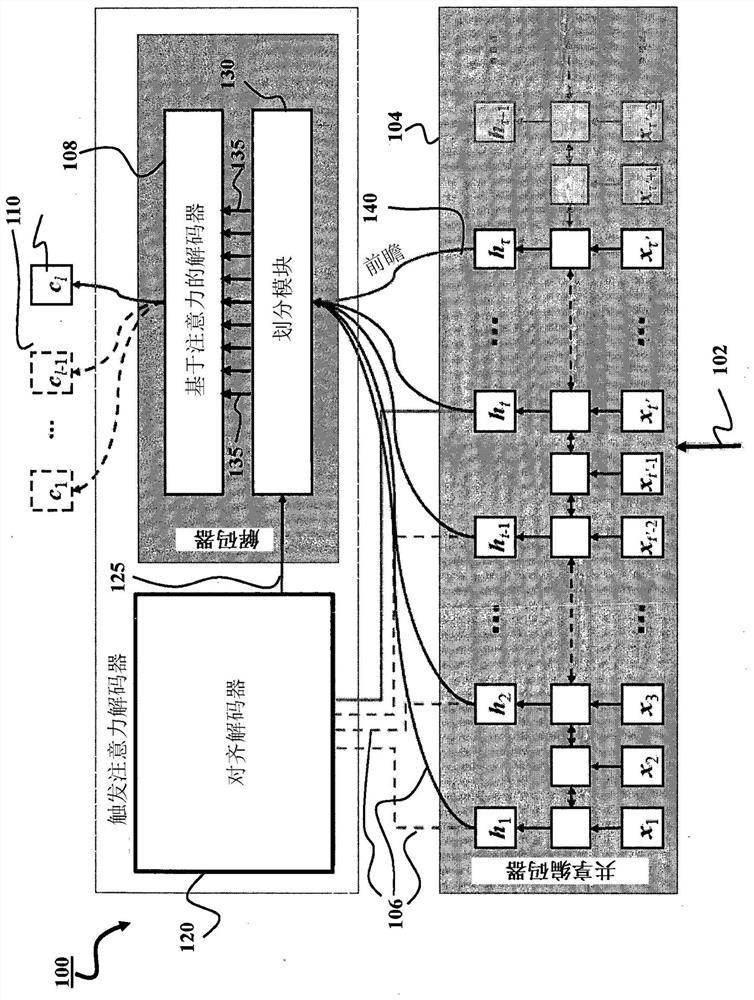

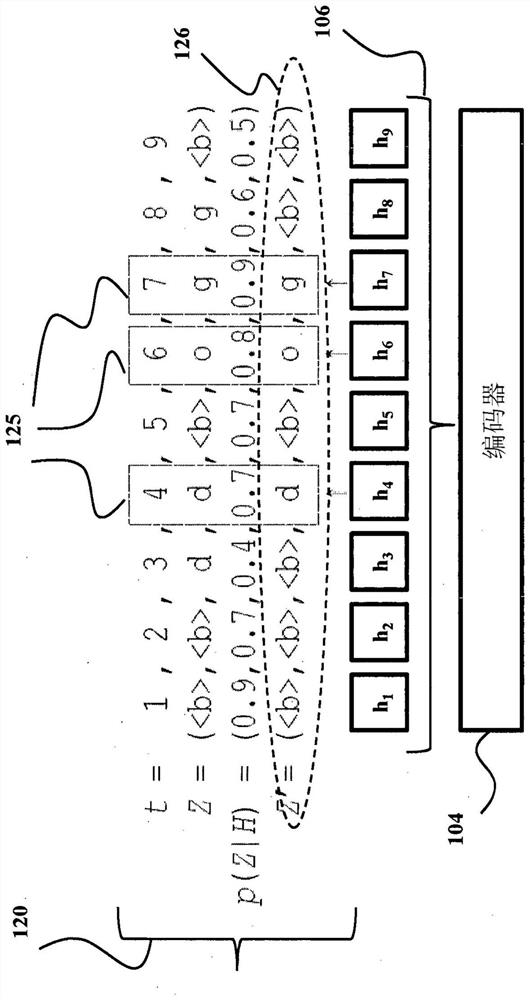

System and method for end-to-end speech recognition with triggered attention

PendingCN113574595ALess waitingReduce output delayMathematical modelsSpeech recognitionEngineeringSpeech sound

A speech recognition system includes an encoder to convert an input acoustic signal into a sequence of encoder states, an alignment decoder to identify locations of encoder states in the sequence of encoder states that encode transcription outputs, a partition module to partition the sequence of encoder states into a set of partitions based on the locations of the identified encoder states, and an attention-based decoder to determine the transcription outputs for each partition of encoder states submitted to the attention-based decoder as an input. Upon receiving the acoustic signal, the system uses the encoder to produce the sequence of encoder states, partitions the sequence of encoder states into the set of partitions based on the locations of the encoder states identified by the alignment decoder, and submits the set of partitions sequentially into the attention-based decoder to produce a transcription output for each of the submitted partitions.

Owner:MITSUBISHI ELECTRIC CORP

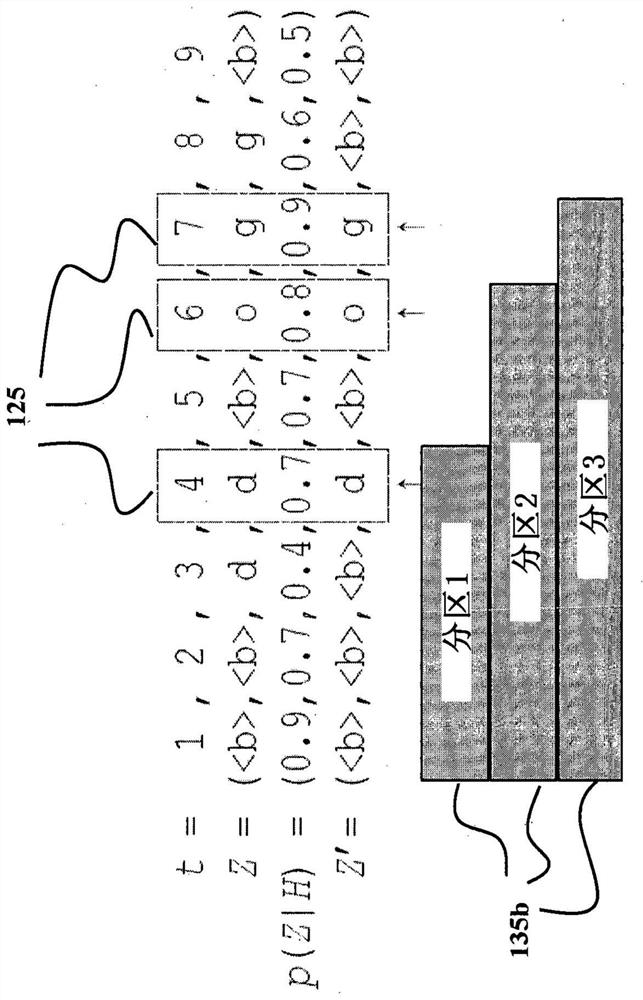

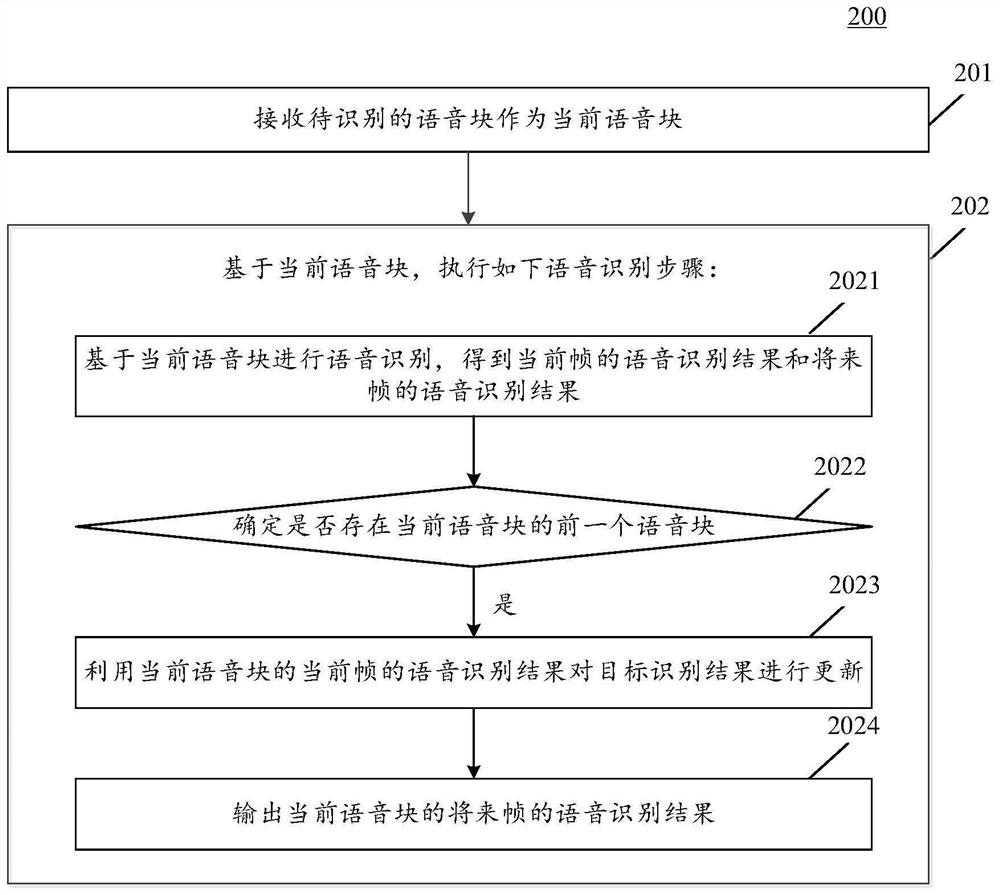

Voice processing method and device, and electronic equipment

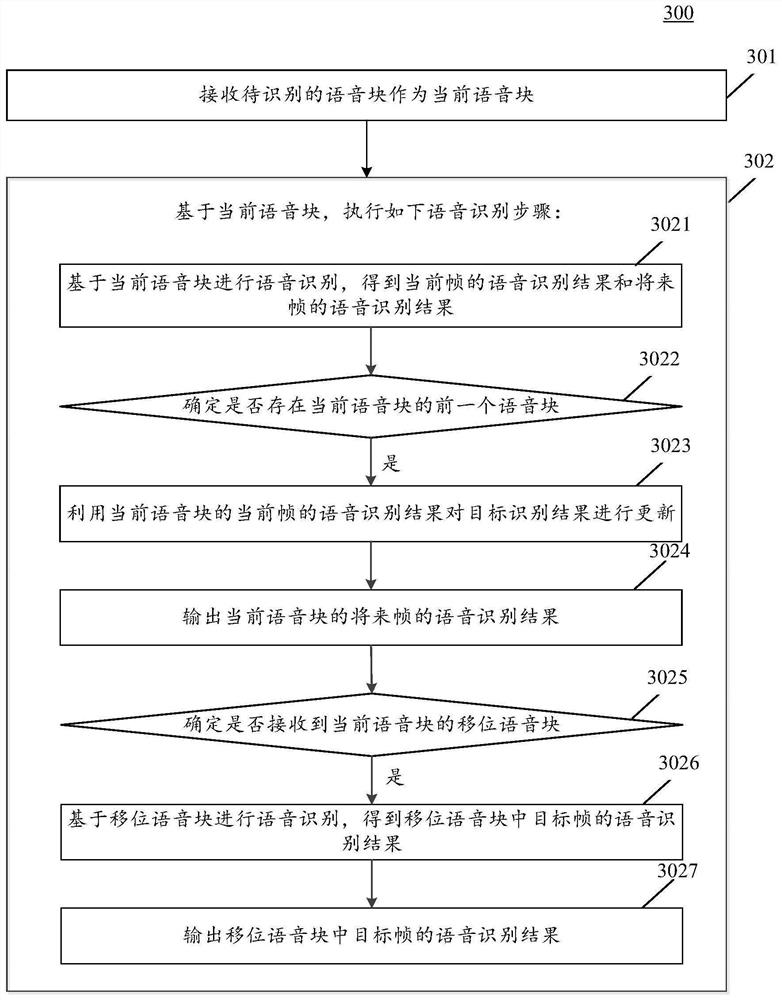

ActiveCN114038465AReduce output delayRecognition accuracy remains unchangedSpeech recognitionEngineeringSpeech sound

The embodiment of the invention discloses a voice processing method and device, and electronic equipment. According to a specific embodiment, the method comprises the following steps: receiving a to-be-recognized voice block as a current voice block, wherein the voice block comprises a past frame, a current frame and a future frame; and based on the current voice block, executing the following voice recognition steps: performing voice recognition based on the current voice block to obtain a voice recognition result of the current frame and a voice recognition result of the future frame; determining whether a previous voice block of the current voice block exists; if so, updating a target recognition result by using the voice recognition result of the current frame of the current voice block; and outputting the voice recognition result of the future frame of the current voice block. According to the embodiment, the output delay of the voiced recognition results can be reduced.

Owner:BEIJING YOUZHUJU NETWORK TECH CO LTD

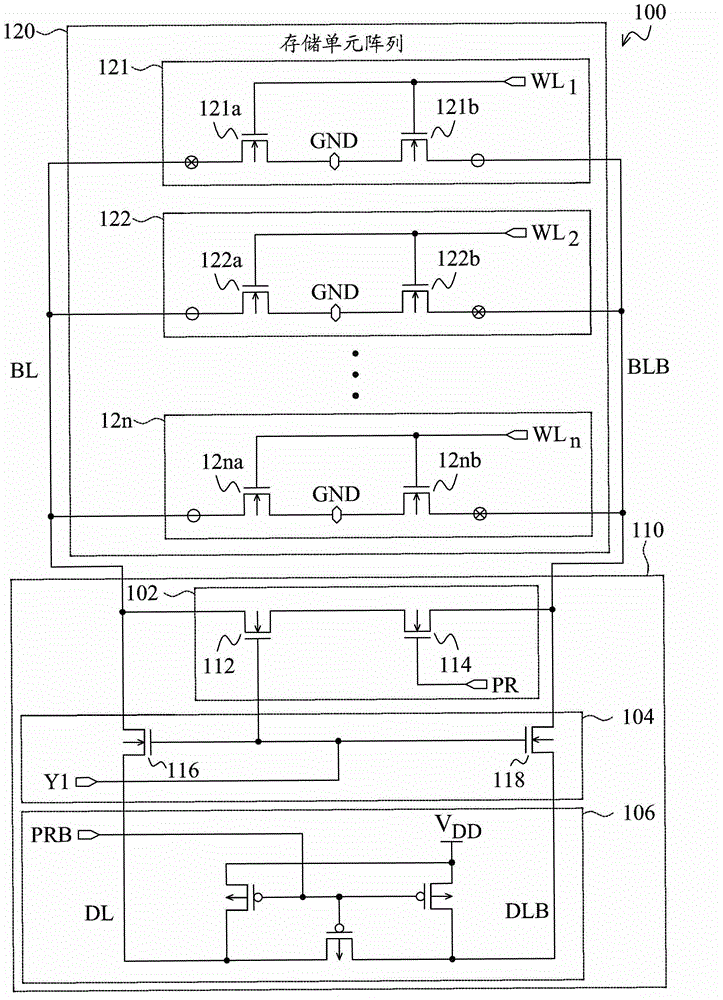

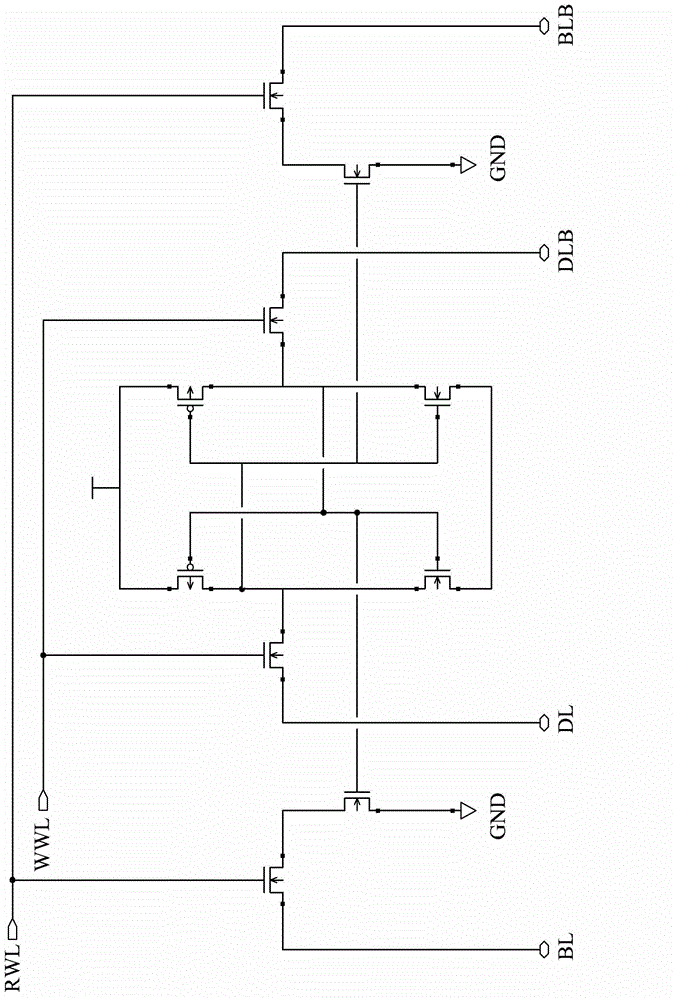

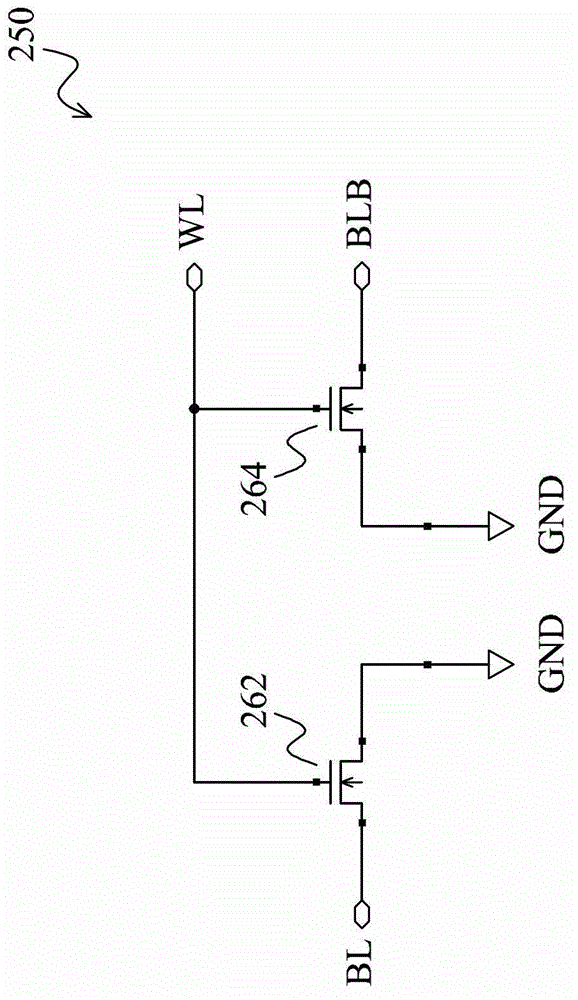

Memory output circuit

The invention provides a memory output circuit. The memory output circuit is capable of receiving bit line data and bit bar line data output by a memory cell array. In one embodiment, the memory output circuit comprises a pre-charge circuit, a pre-amplifier circuit, and a sense amplifier. The pre-charge circuit is capable of pre-charging a first node and a first inverse node wherein the bit line data and bit bar line data are respectively output to the first node and the first inverse node. The pre-amplifier circuit is capable of generating a second voltage on a second node and a second inverse voltage on a second inverse node according to a first voltage on the first node and a first inverse voltage on the first inverse node. The sense amplifier is capable of detecting the second voltage on the second node and the second inverse voltage on the second inverse node to generate a third voltage on a third node and a third inverse voltage on a third inverse node.

Owner:MEDIATEK INC

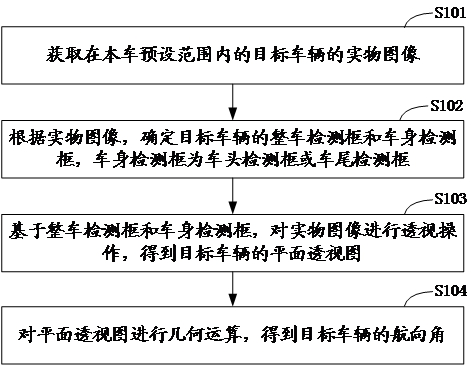

Vehicle course angle detection method and device, equipment and storage medium

ActiveCN114091521AReduce operational complexityReduce algorithm output delayCharacter and pattern recognitionNeural architecturesEngineeringSingle image

The invention discloses a vehicle course angle detection method, device and equipment and a storage medium, and the method comprises the steps: obtaining a real object image of a target vehicle in a preset range of a vehicle, determining a whole vehicle detection frame and a vehicle body detection frame of the target vehicle according to the real object image, and employing a single image to locate the position of the target vehicle in the image, and obtaining the vehicle head position or the vehicle tail position of the target vehicle; based on the whole vehicle detection frame and the vehicle body detection frame, carrying out the perspective operation on the real object image to obtain a plane perspective view of the target vehicle, and carrying out the geometric operation on the plane perspective view to obtain a course angle of the target vehicle, so that a three-dimensional space problem in the detection process is converted into a two-dimensional plane problem, the operation complexity and algorithm output delay are effectively reduced, and the purposes of reducing the computing amount and improving the precision are achieved; meanwhile, the method can be suitable for various scenes.

Owner:SHENZHEN MINIEYE INNOVATION TECH CO LTD

GOA circuit and liquid crystal display

ActiveUS9589523B2Reduce output delayHigh voltage levelCathode-ray tube indicatorsElectricityLiquid-crystal display

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD +1

Gate driving circuits and display devices

ActiveUS9972266B2Reduce leakageReduce output delayStatic indicating devicesDigital storageDisplay deviceEngineering

A gate driving circuit and a display device are disclosed. The gate driving circuit includes a control module for pulling down the level of the second control node to be at the low level before the gate strobe signals are outputted and during the output period of the gate cutoff signals. In this way, the second pull-down control end of the low level maintaining module is pulled down to be at the low levels, and the low level maintaining module is in the off state. In this way, the electrical leakage of the low level maintaining module may be reduced so as to decrease the output delay of the gate signals and to enhance the efficiency of the circuit.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

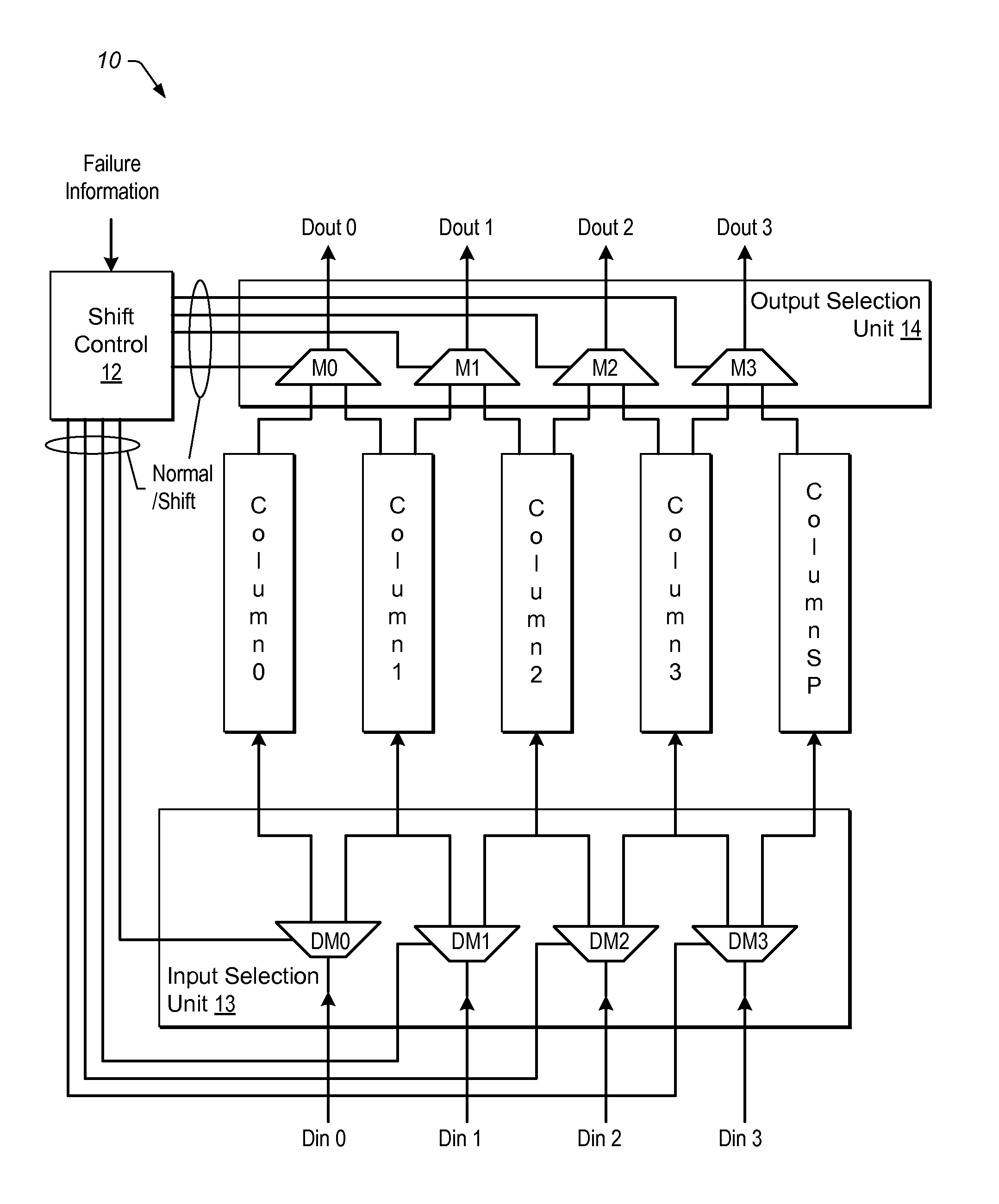

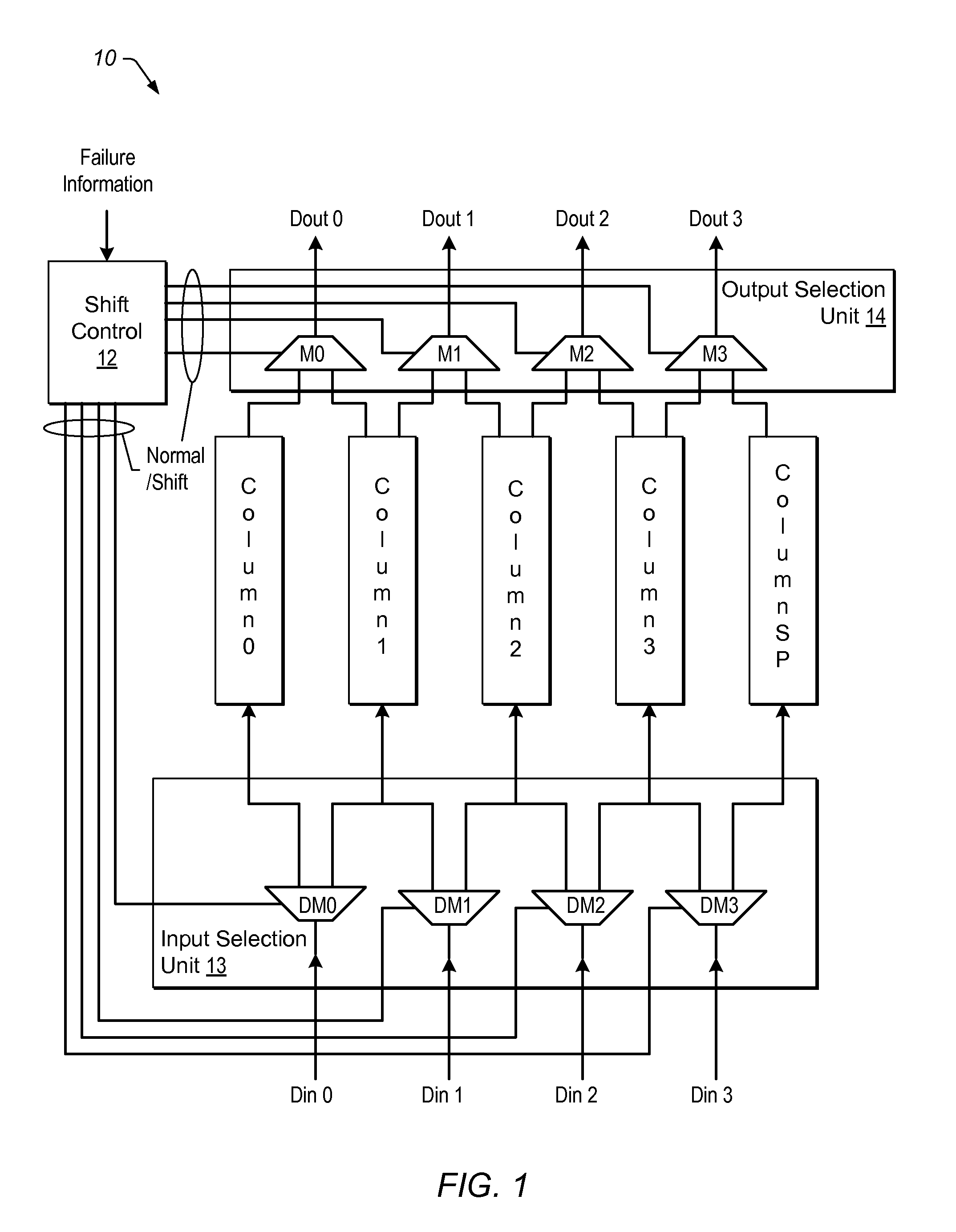

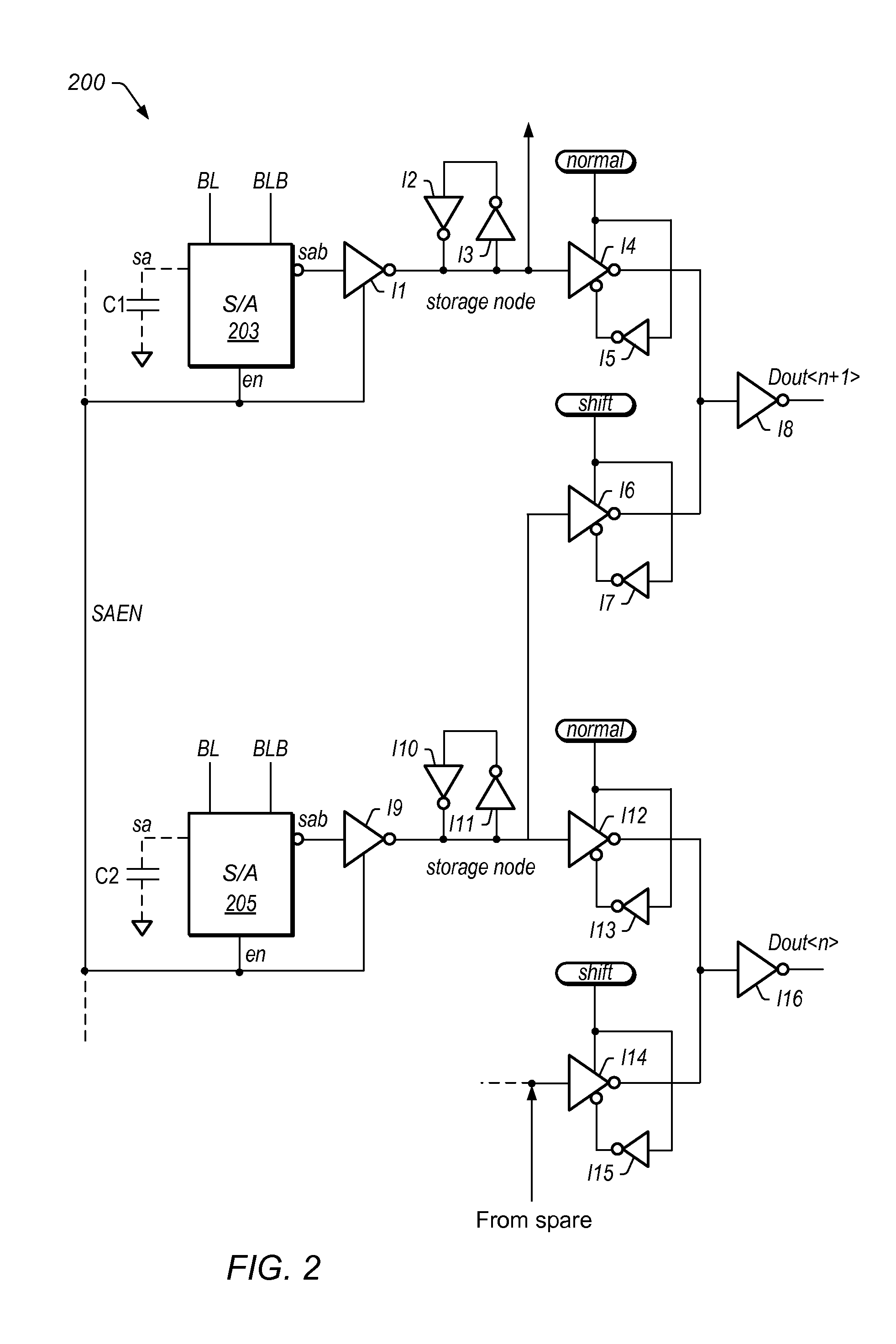

Reduced latency memory column redundancy repair

ActiveUS20130091329A1Reduce maintenanceReduce output delayMemory adressing/allocation/relocationDigital storageAudio power amplifierData port

A memory column redundancy mechanism includes a memory having a number of data output ports each configured to output one data bit of a data element. The memory also includes a number of memory columns each connected to a corresponding respective data port. Each memory column includes a plurality of bit cells that are coupled to a corresponding sense amplifier that may differentially output a respective data bit from the plurality of bit cells on an output signal and a complemented output signal. The memory further includes an output selection unit that may select as the output data bit for a given data output port, one of the output signal of the sense amplifier associated with the given data output port or the complemented output signal of the sense amplifier associated with an adjacent data output port dependent upon a respective shift signal for each memory column.

Owner:APPLE INC

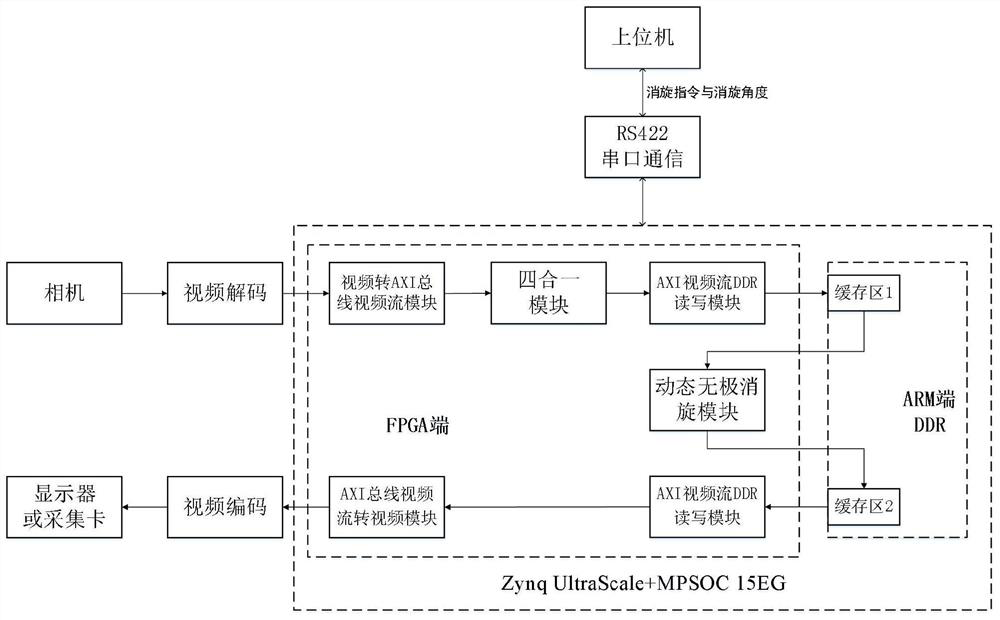

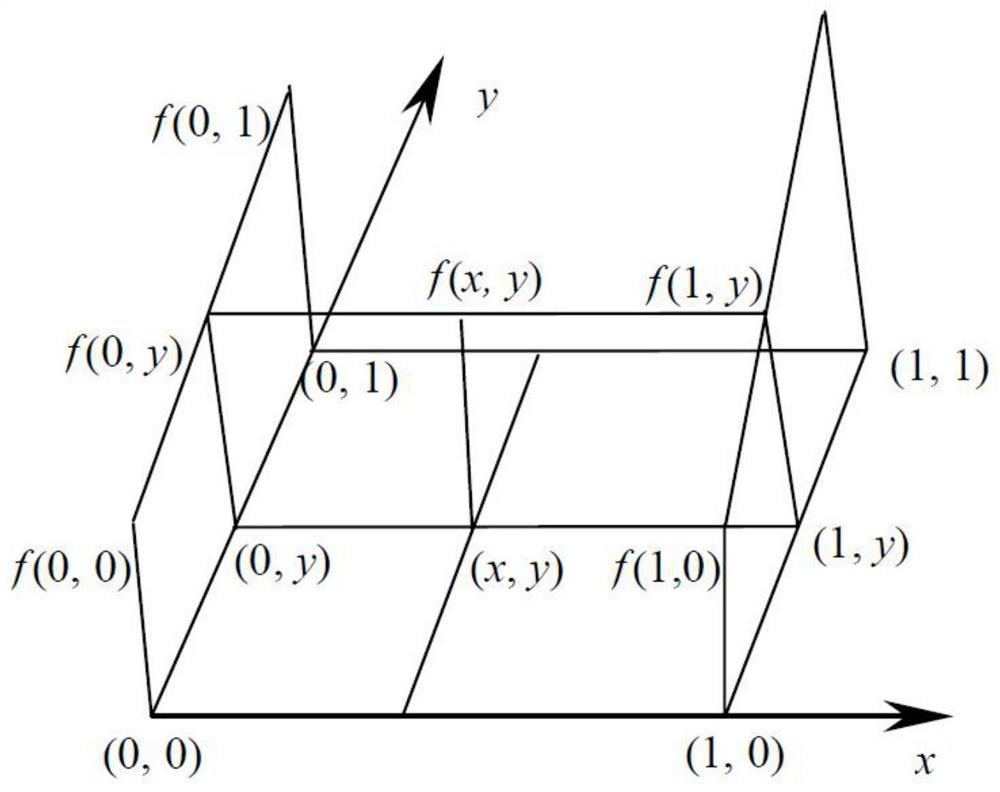

Dynamic stepless racemization system and method based on high-level integration of large-scale integrated circuit

ActiveCN113962842AEasy to handleAvoid cloggingImage enhancementDetails involving antialiasingVideo storageCode module

The invention relates to a dynamic stepless racemization system and method based on high-level integration of a large-scale integrated circuit. The system comprises a video acquisition module, a video decoding module, a video storage module, a data communication module, a video coding module, a dynamic stepless racemization module and a pixel merging module, namely a four-in-one module, which is innovatively designed for reducing algorithm delay and improving the utilization rate of bus bandwidth. According to the invention, the dynamic stepless racemization function is realized by adopting the high-level comprehensive technology, real-time racemization processing can be carried out on the acquired video image in a photoelectric platform, and compared with an existing racemization technology, the characteristics of FPGA parallel acceleration and assembly line optimization are fully utilized, the system and method have the excellent characteristics of high video resolution, large racemization range, high racemization precision, clear and sawtooth-free processed images, low output delay, high system stability, easiness in processing, low power consumption, small size and the like.

Owner:BEIHANG UNIV

A Fast Filtering Method for Sampling Rate Conversion of Multiple Digital Sources in Photoelectric Transformer

InactiveCN103607180BAchieve normalizationPromote normalizationDigital technique networkSample rate conversionAnti-aliasing

The invention discloses a fast filtering method for the sampling rate conversion of multiple digital sources in a photoelectric transformer. The conversion of any fractional sampling frequency is realized by cascading interpolation and extraction. The Butterworth analog filter is used as the Based on the calculation of the analog filter cut-off frequency according to different digital source sampling frequencies to achieve anti-aliasing and anti-image effects; then according to the principle of the largest flat passband and the narrowest transition band of the filter, and sampling bilinear transformation, we get Z-domain low-pass filter equation parameters; finally, the FRR method is used for filtering and phase inversion design, and finally the output signal sequence with maximum flatness and zero phase distortion is obtained. The method provided by the present invention can realize fast filtering with lower orders in differential protection of photoelectric transformers to obtain maximum output flatness and zero phase; it is simple and practical, is conducive to fast action of protection, and can reduce frequency aliasing The resulting error realizes the normalization of the sampling frequency.

Owner:SOUTHEAST UNIV

Array substrate, display panel and display device

The invention discloses an array substrate, a display panel, and a display device. Two adjacent shift register units of the first type and shift register units of the second type are used as a subgroup, and the two shift register units in each subgroup The signal ends of the shift register units used to connect to the same clock signal line are connected through the first lead, and the first lead is connected with the corresponding clock signal line through the second lead. In this way, by adjusting the arrangement sequence of the shift register units or reducing the number of clock signal lines, the overlap between the lead wires and the clock signal lines is reduced, thereby reducing the parasitic capacitance generated at the overlap between the lead wires and the clock signal lines. The number, thereby reducing the delay of the clock signal, and reducing the output delay of the shift register unit and the power consumption of the gate drive circuit.

Owner:BOE TECH GRP CO LTD +1