A method of manufacturing an interconnect structure containing an air gap

A technology of interconnection structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of small process window and poor sealing integrity, and achieve simplified process, ensure integrity, and large process window. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0033] Please refer to Figure 1A~1I , which is a schematic cross-sectional view of the manufacturing method of this embodiment.

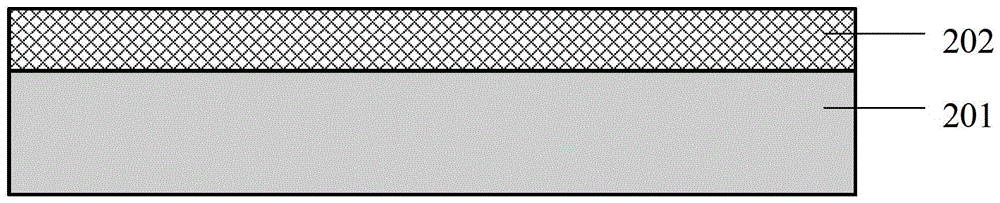

[0034] Please refer to Figure 1A , firstly, a substrate 201 is provided, and the material of the substrate 201 may be silicon, germanium or silicon germanium. In this embodiment, the substrate 201 is a silicon substrate, and the previous process of the substrate 201 has been completed. Then form the first sacrificial layer 202 on the substrate 201, the sacrificial medium of the first sacrificial layer 202 can be SiO2, Si3N4, amorphous silicon material, volatile organic material or polyimide (Polyimide) material with photosensitive properties etc. Preferably, in this embodiment, an amorphous silicon material deposited by plasma enhanced chemical vapor deposition (PECVD) is used as the first sacrificial layer 202 .

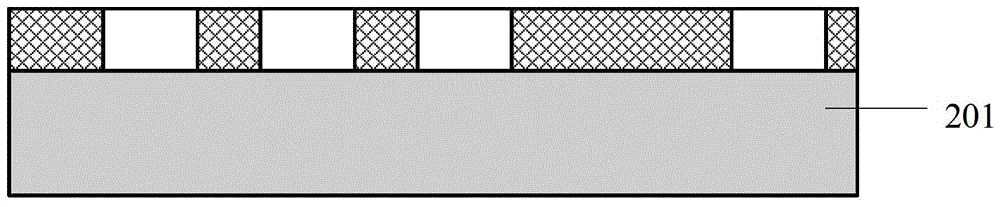

[0035] Please refer to Figure 1B with Figure 1C , which shows a step of performing a single damascene process using the first s...

Embodiment 2

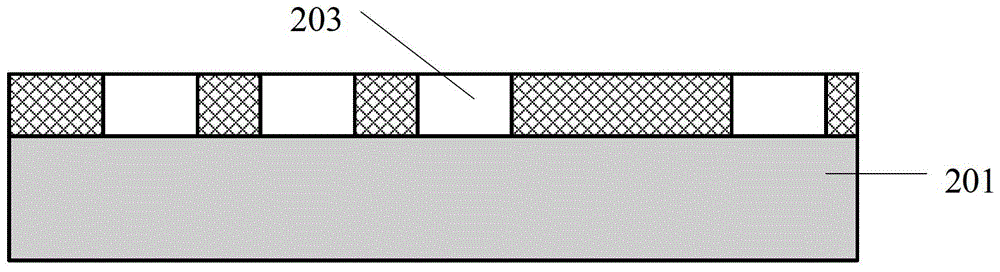

[0044] Please refer to Figure 2A~2J , which is a schematic cross-sectional view of the manufacturing method of this embodiment. The difference from the first embodiment is that the air gap is formed between the metal interconnection structures formed by the double damascene process in this embodiment, which can be used in the first embodiment Completed on the basis of, also can carry out independently, the present invention is not limited to this. Combine below Figure 2A~2J The present embodiment will be described in detail.

[0045] Please refer to Figure 2A , firstly, a substrate 201 is provided, in which a metal interconnection layer 203 is formed, and a dielectric layer 205 is filled between the metal interconnection lines of the metal interconnection layer 203, and the space between the metal interconnection lines and the filling medium can be Air gap 207 is included. The filling medium layer 205 on the surface of the substrate 201 is planarized; preferably, the pl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More