Method for generating gate-level netlist and standard delay file and checking and correcting false routes

A gate-level netlist and path technology, applied in the field of back-end design of system-on-chip, can solve problems such as increasing the layout and wiring production cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The specific implementation manner of the present invention will be further described below in conjunction with the accompanying drawings.

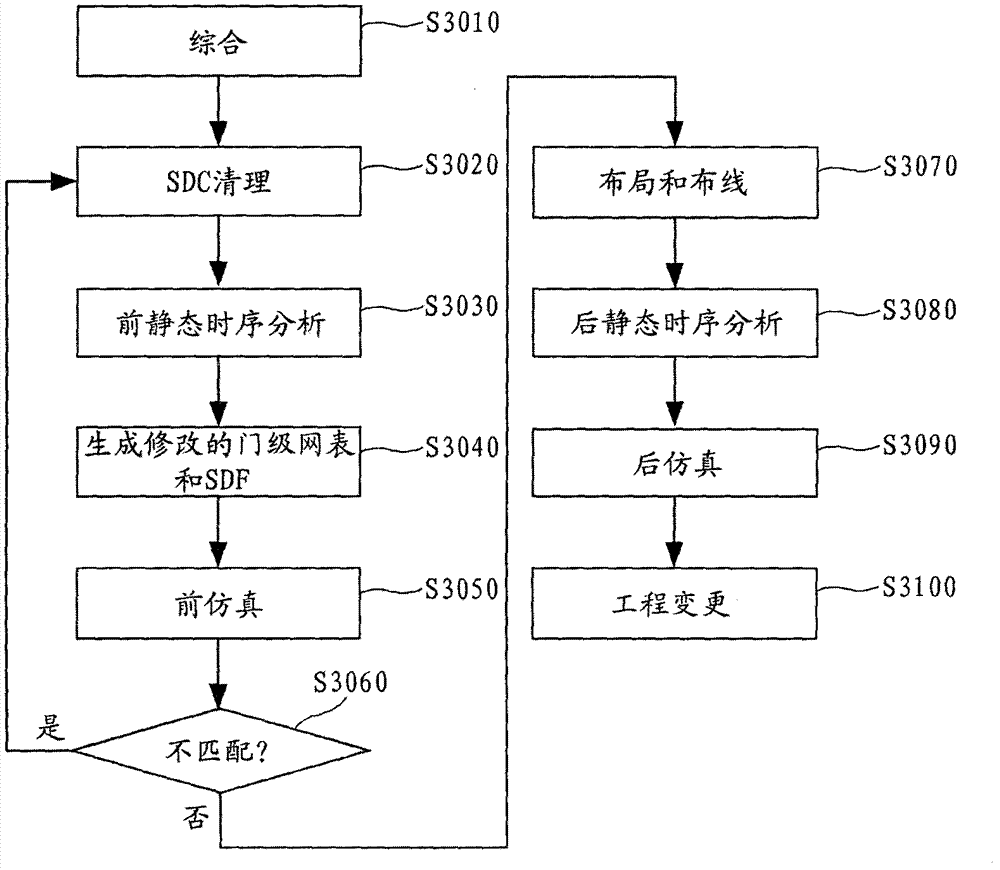

[0047] image 3 is a flow chart of SOC backend design according to an exemplary embodiment of the present invention. Such as image 3 As shown, the flow process of the SOC back-end design according to an exemplary embodiment of the present invention includes the following steps: synthesis (S3010), SDC cleaning (S3020), pre-static timing analysis (S3030), generation of SDF and revised gate-level netlist (3040), use the SDF and the modified gate-level netlist to perform pre-simulation (S3050), determine whether the pre-simulation results do not match the expected results (S3060), place and route (S3070), post static timing simulation (S3080), post Simulation (S3090) and engineering change (S3100). In step S3060, if it is judged that the previous simulation result does not match the expected result, that is, if the previous simulat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More