Semiconductor package structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of inability to stack chips, pollute the active surface of chips, and fail to apply CMOS chips, etc. The effect of reducing production cost and increasing structural reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

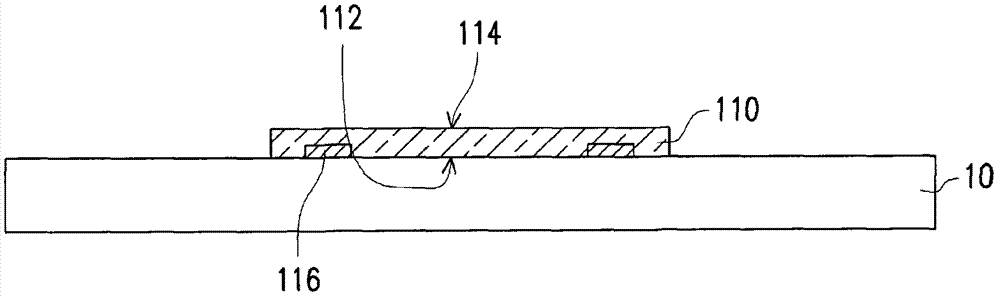

[0050] Figure 1A to Figure 1G It is a schematic cross-sectional view of a manufacturing method of a semiconductor package structure according to an embodiment of the present invention. Please refer to Figure 1A , The manufacturing method of the semiconductor package structure of this embodiment includes the following steps. First, a chip 110 is provided, wherein the chip 110 has an active surface 112 and a back surface 114 opposite to each other and a plurality of bonding pads 116 on the active surface 112 . Next, the chip 110 is disposed on a carrier board 10 , wherein the active surface 112 of the chip 110 faces the carrier board 10 .

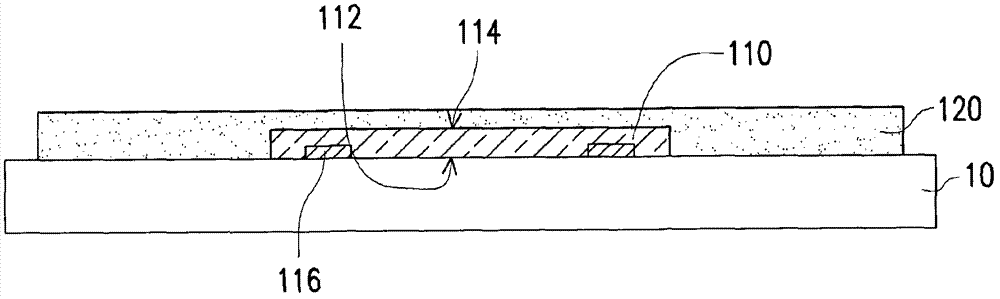

[0051] Next, please refer to Figure 1B , forming a first encapsulant 120 on the carrier board 10 to cover the chip 110 and part of the carrier board 10 .

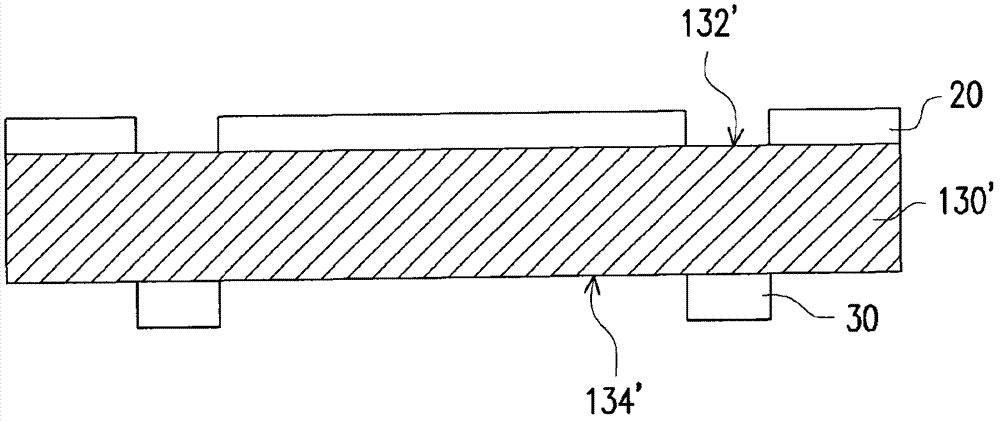

[0052] Afterwards, please also refer to Figure 1C and Figure 1D, provide a metal material layer 130', and coat a layer of photoresist (not shown) on a first surface 132' and a se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More