Patents

Literature

69results about How to "Prevent warpage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

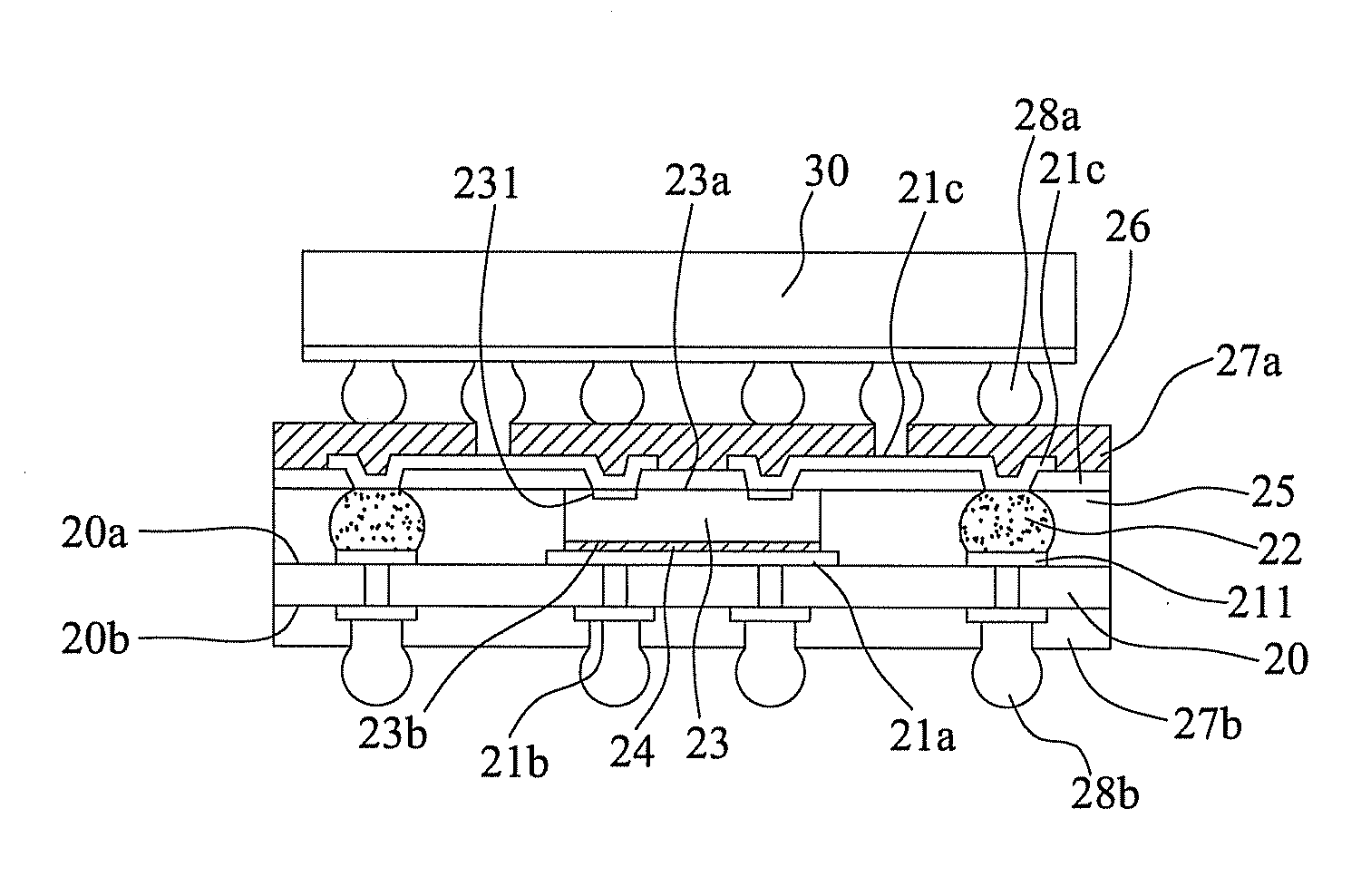

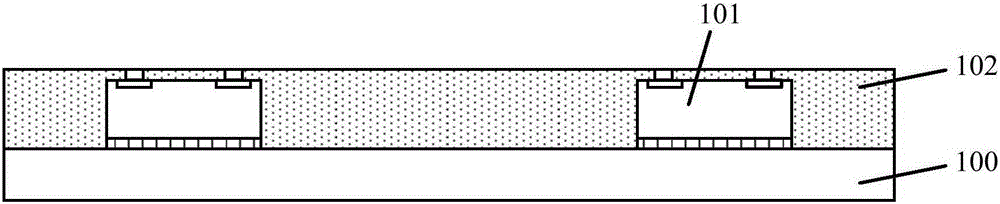

Chip scale package and fabrication method thereof

ActiveUS20120038044A1Eliminate needPrevent warpageSemiconductor/solid-state device detailsSolid-state devicesEngineeringChip-scale package

A CSP includes: a hard board having a first wiring layer with conductive pads; a plurality of conductive elements disposed on at least a portion of the conductive pads; an electronic component having opposite active and inactive surfaces and being mounted on the hard board via the inactive surface; an encapsulating layer disposed on the hard board for encapsulating the conductive elements and electronic component, the active surface of the electronic component and the surfaces of the conductive elements being exposed through the encapsulating layer; a first dielectric layer and a third wiring layer disposed on the encapsulating layer, the third wiring layer being electrically connected to the conductive elements and the electronic component and further electrically connected to the first wiring layer through the conductive elements, thereby obtaining a stacked connection structure without the need of PTHs and using the hard board as a main structure to avoid warpage.

Owner:SILICONWARE PRECISION IND CO LTD

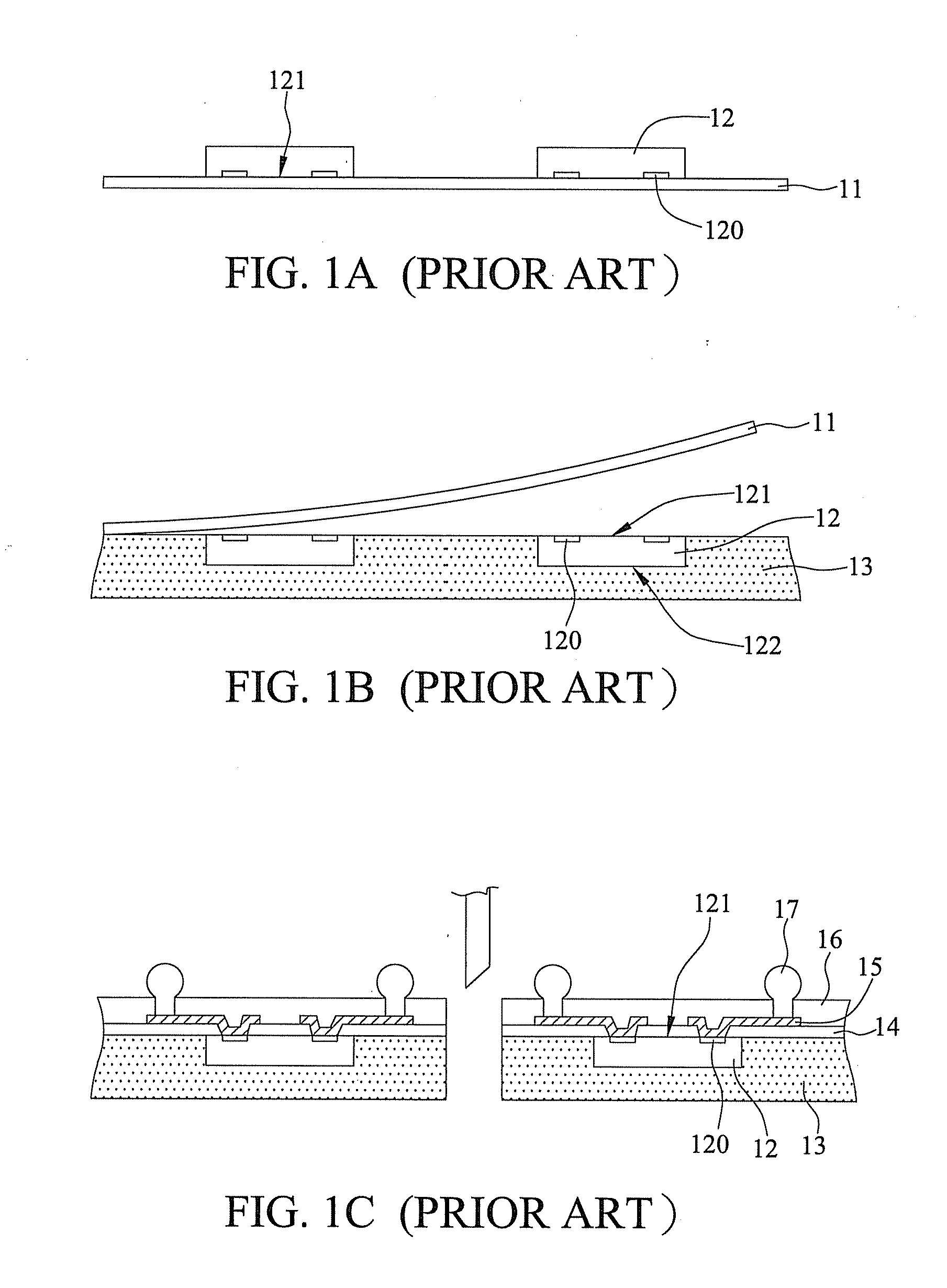

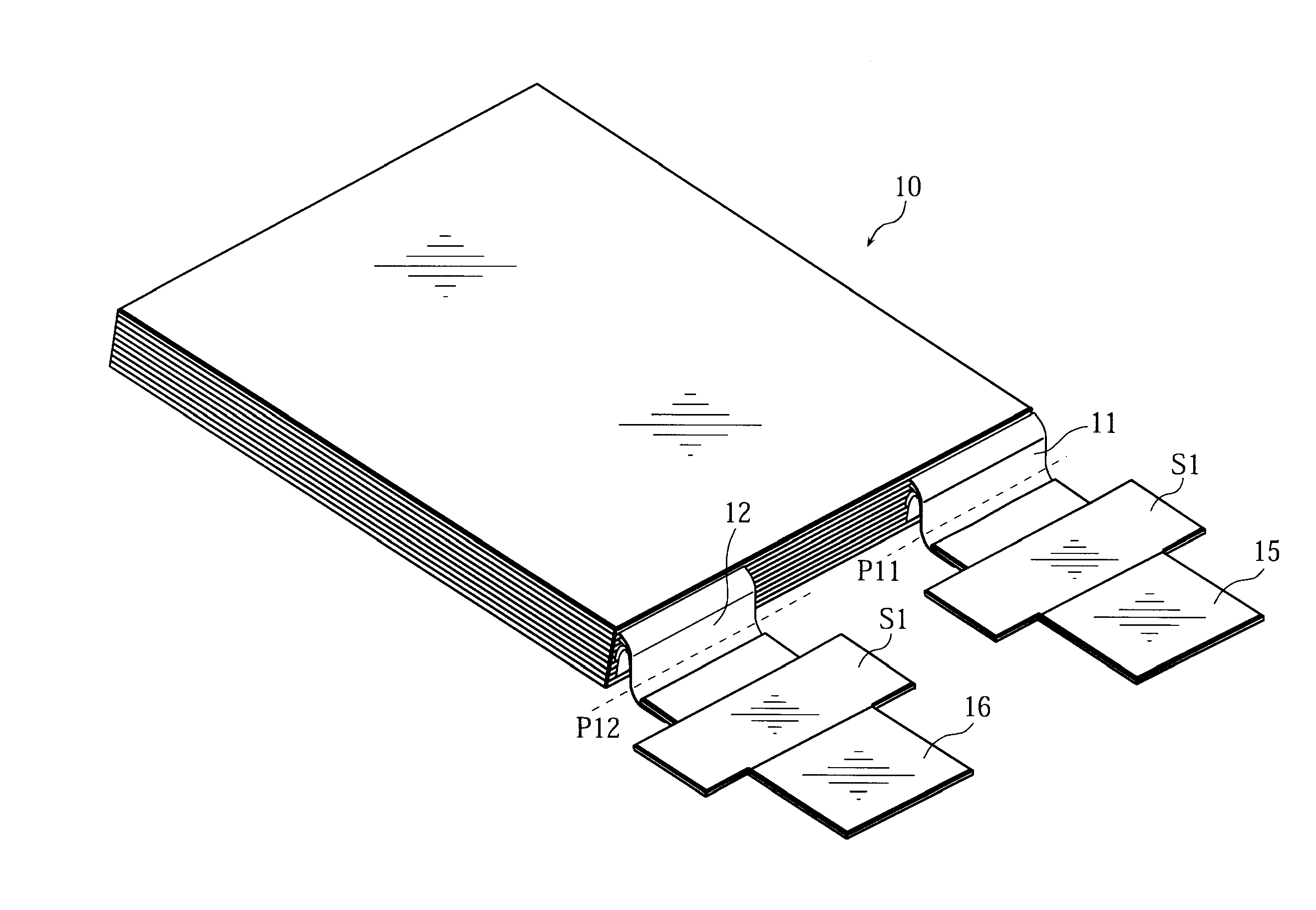

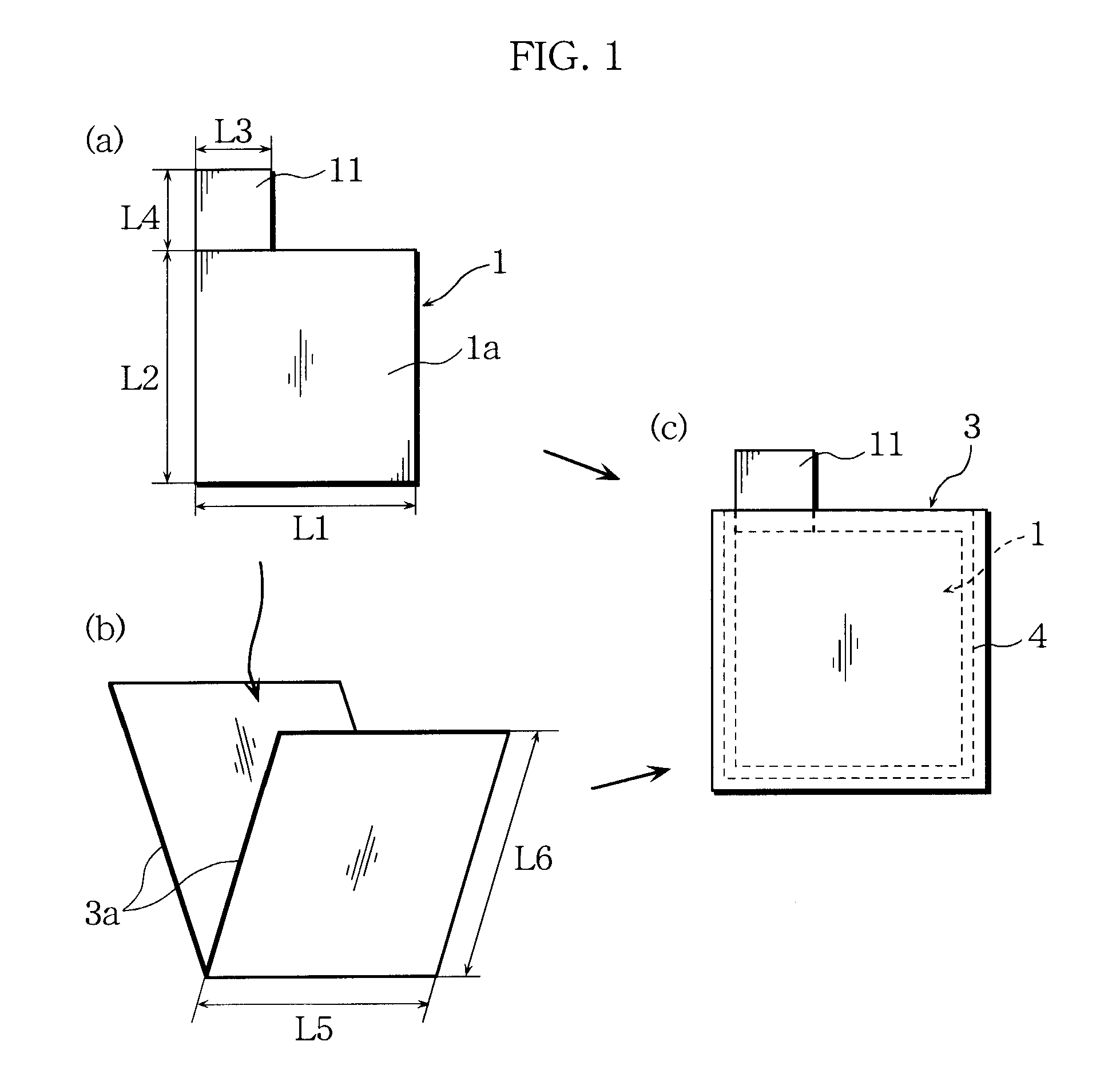

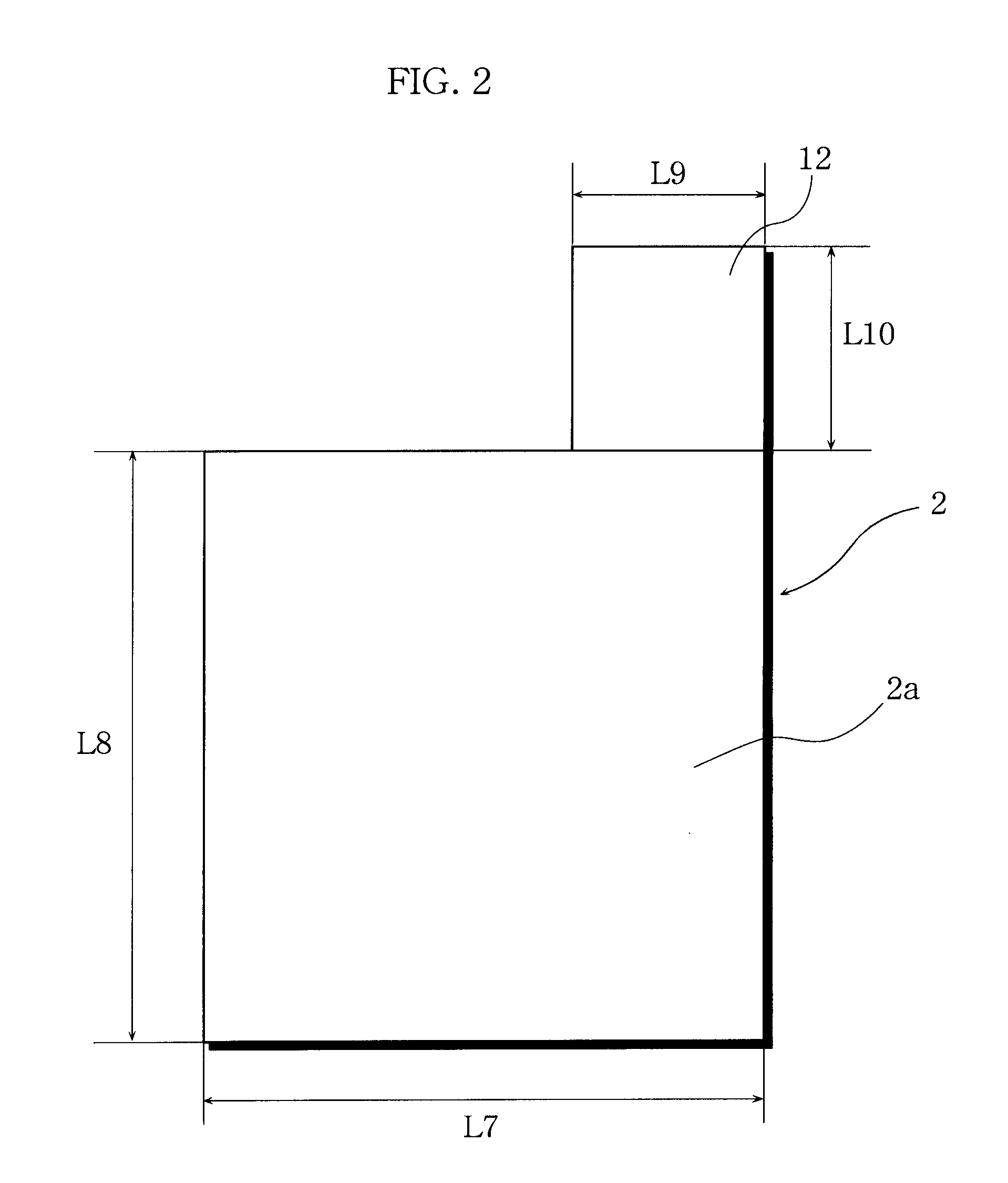

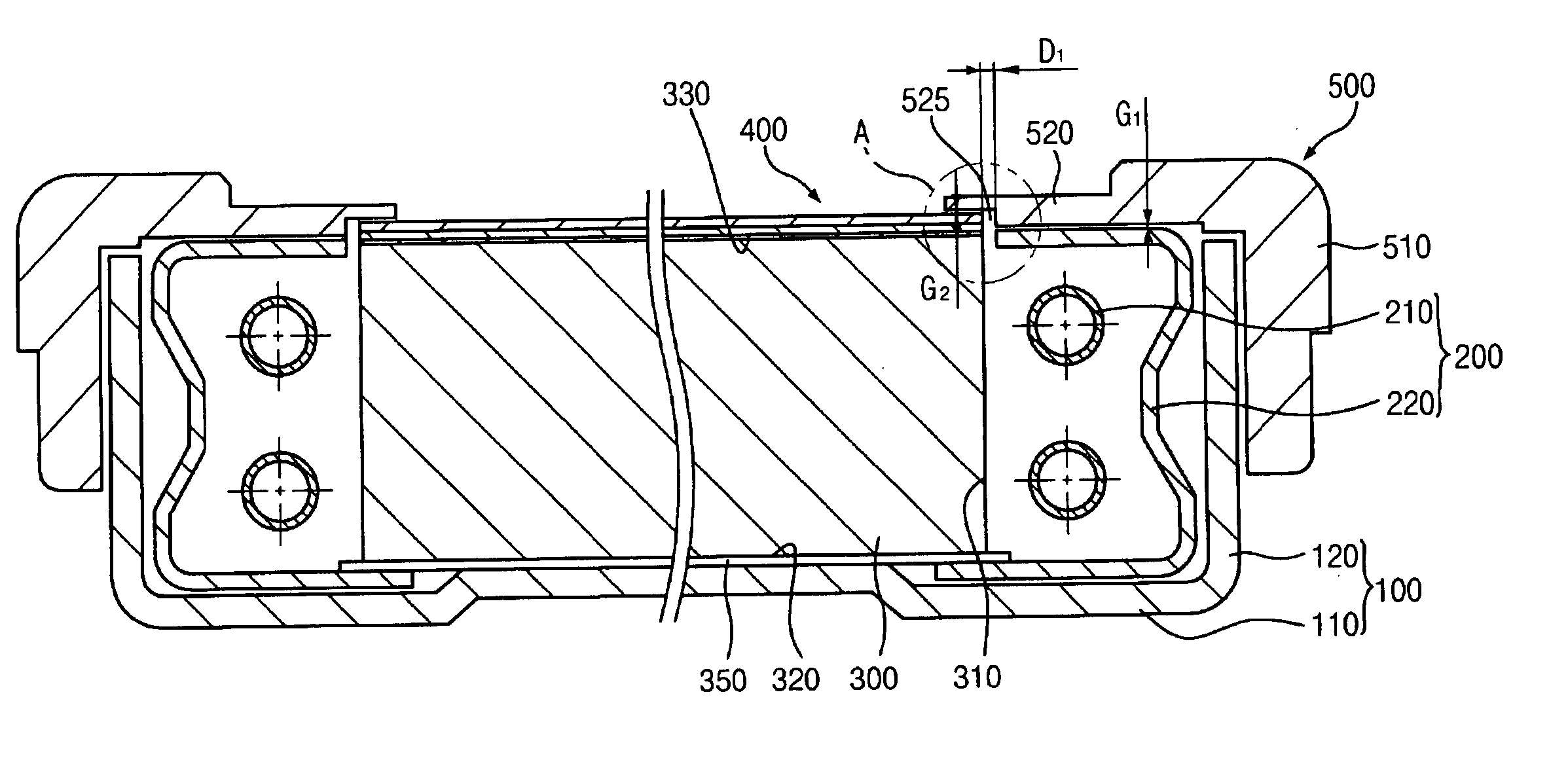

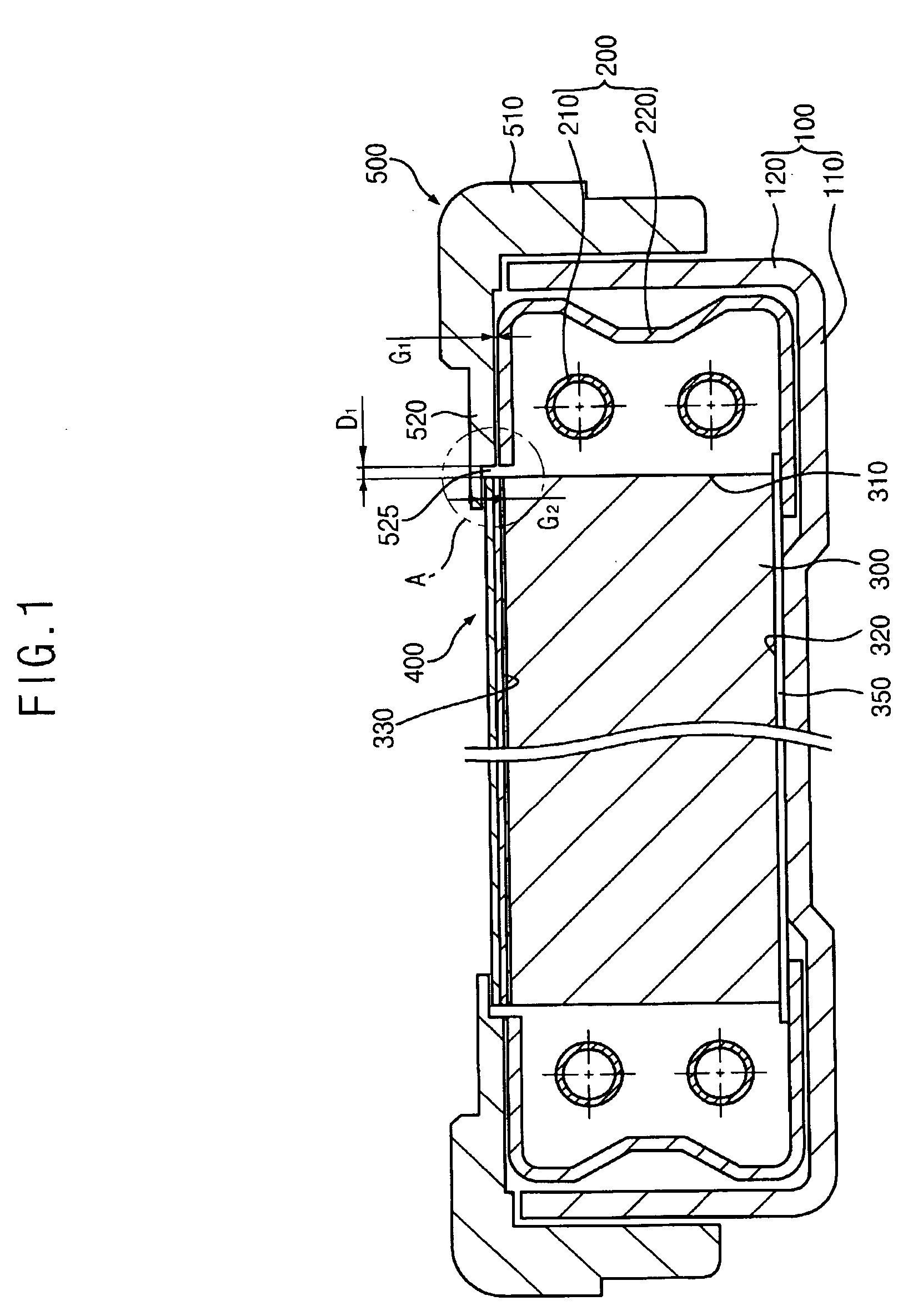

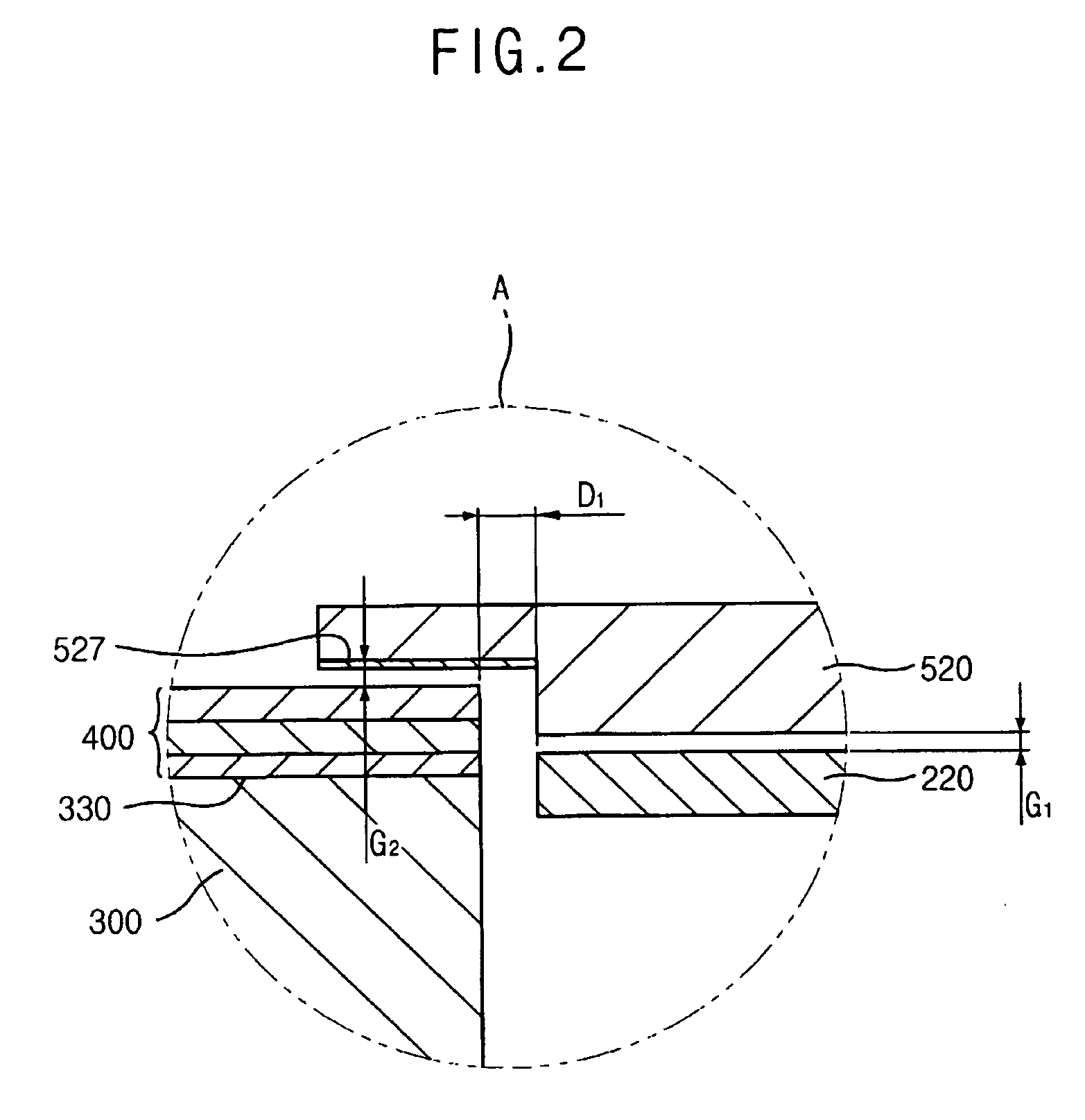

Stack type battery

InactiveUS20110244312A1Avoid constructionAvoid creasesLarge-sized flat cells/batteriesFinal product manufactureEngineeringBattery cell

In a stack type battery, stacked positive and negative electrode lead tabs (11, 12) are joined to one another at a location between the current collector terminals and the electrode plates, the positive and negative electrode lead tabs (11, 12) being folded at an intermediate location between positive and negative electrode current collector terminals (15, 16) and positive and negative electrode plates and protruding from the positive and negative electrode plates. A stacked electrode assembly (10) is accommodated in a battery case (18) having flexibility. A first spacer (a first cover portion (52) of an integral-type spacer (5)) is disposed between the battery case (18) and an open side end of the positive and negative electrode lead tabs (11, 12) formed by folding the positive and negative electrode lead tabs (11, 12).

Owner:SANYO ELECTRIC CO LTD

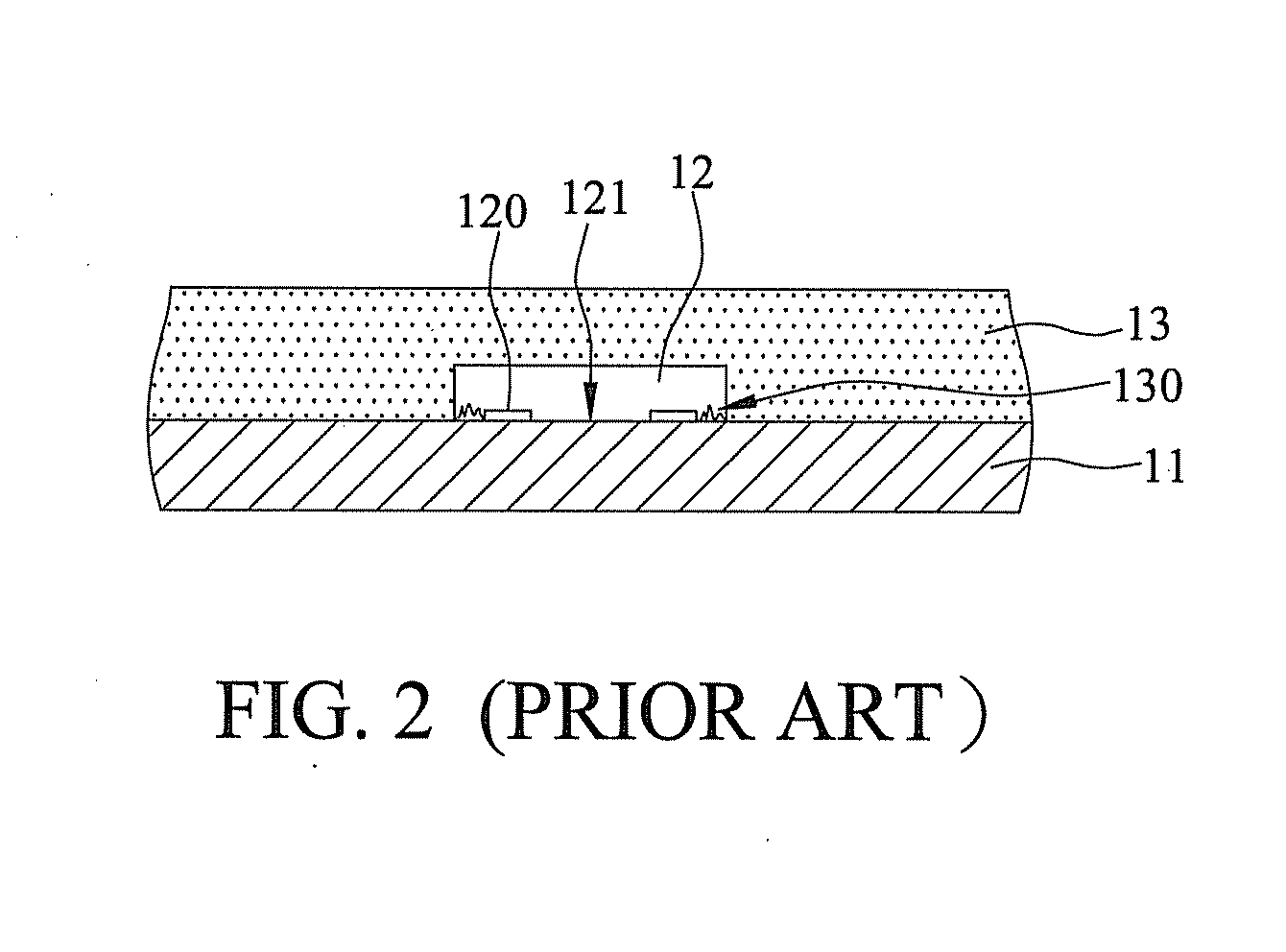

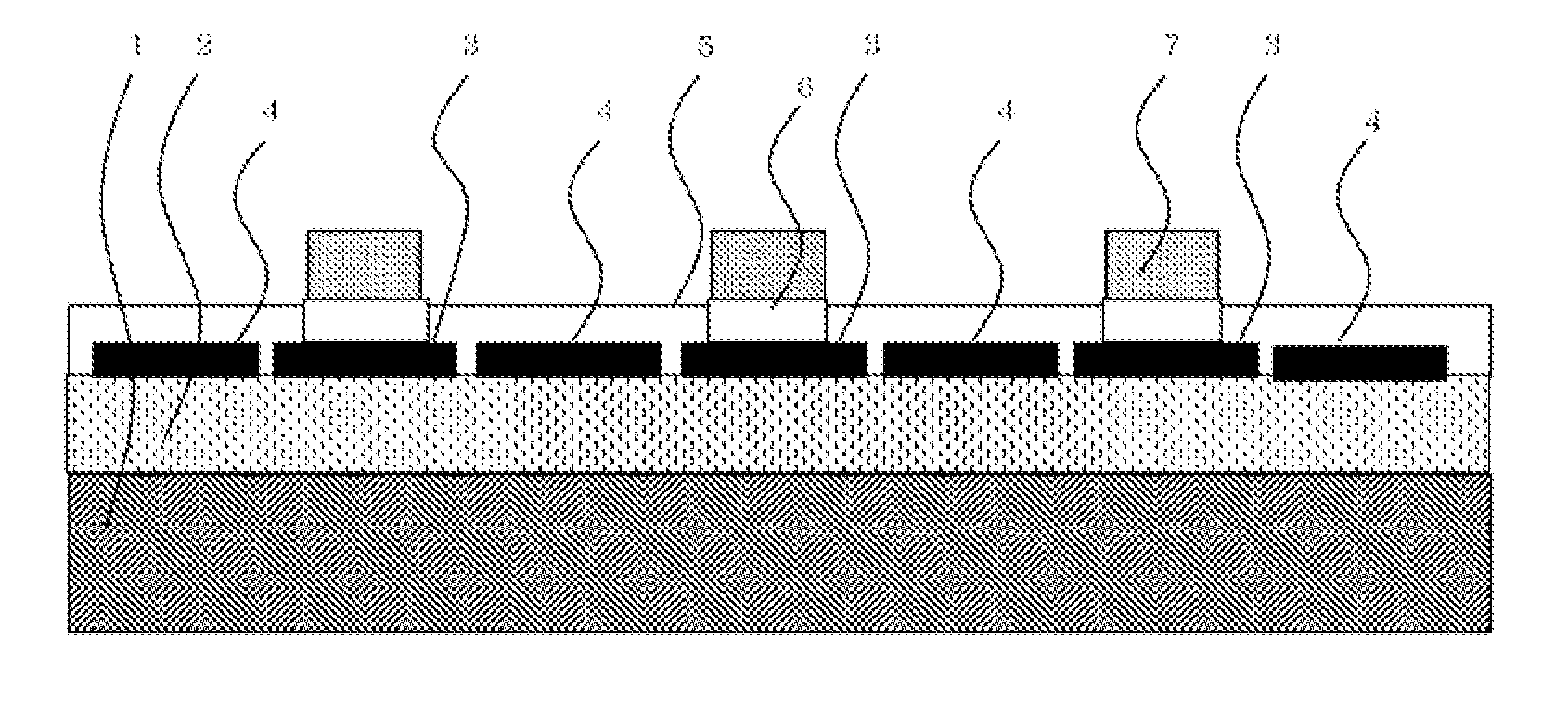

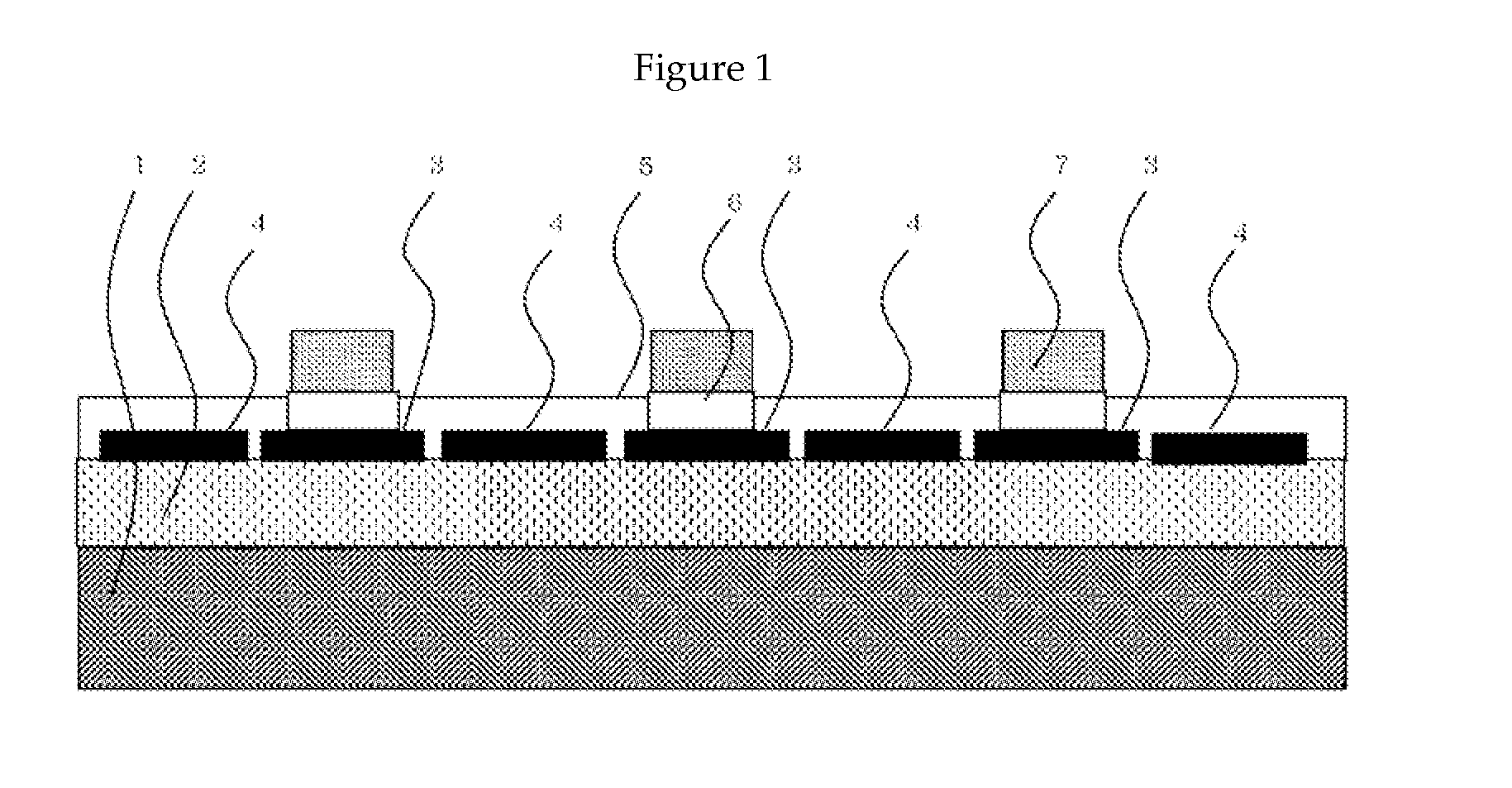

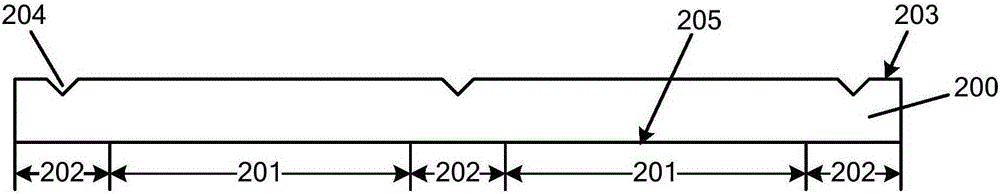

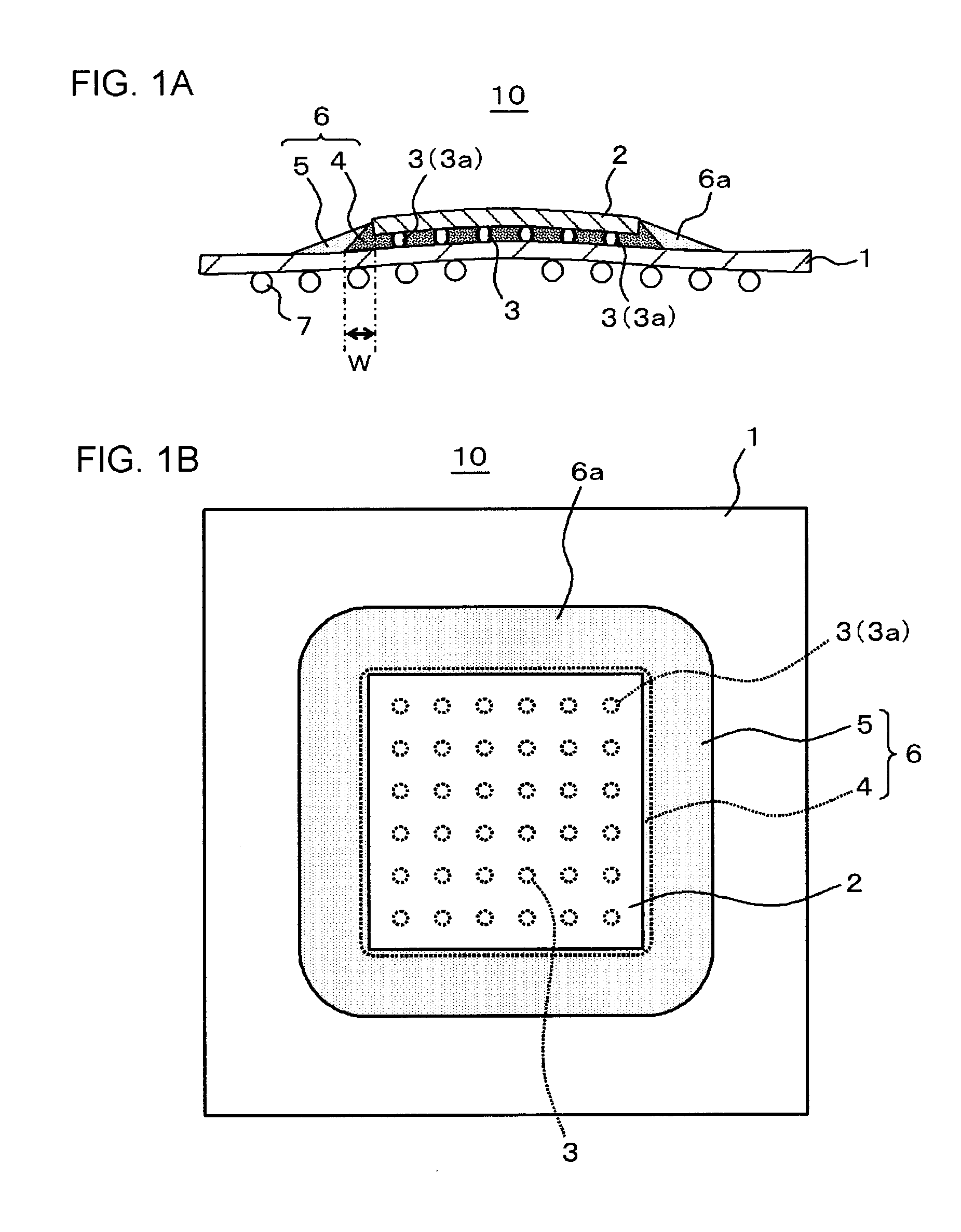

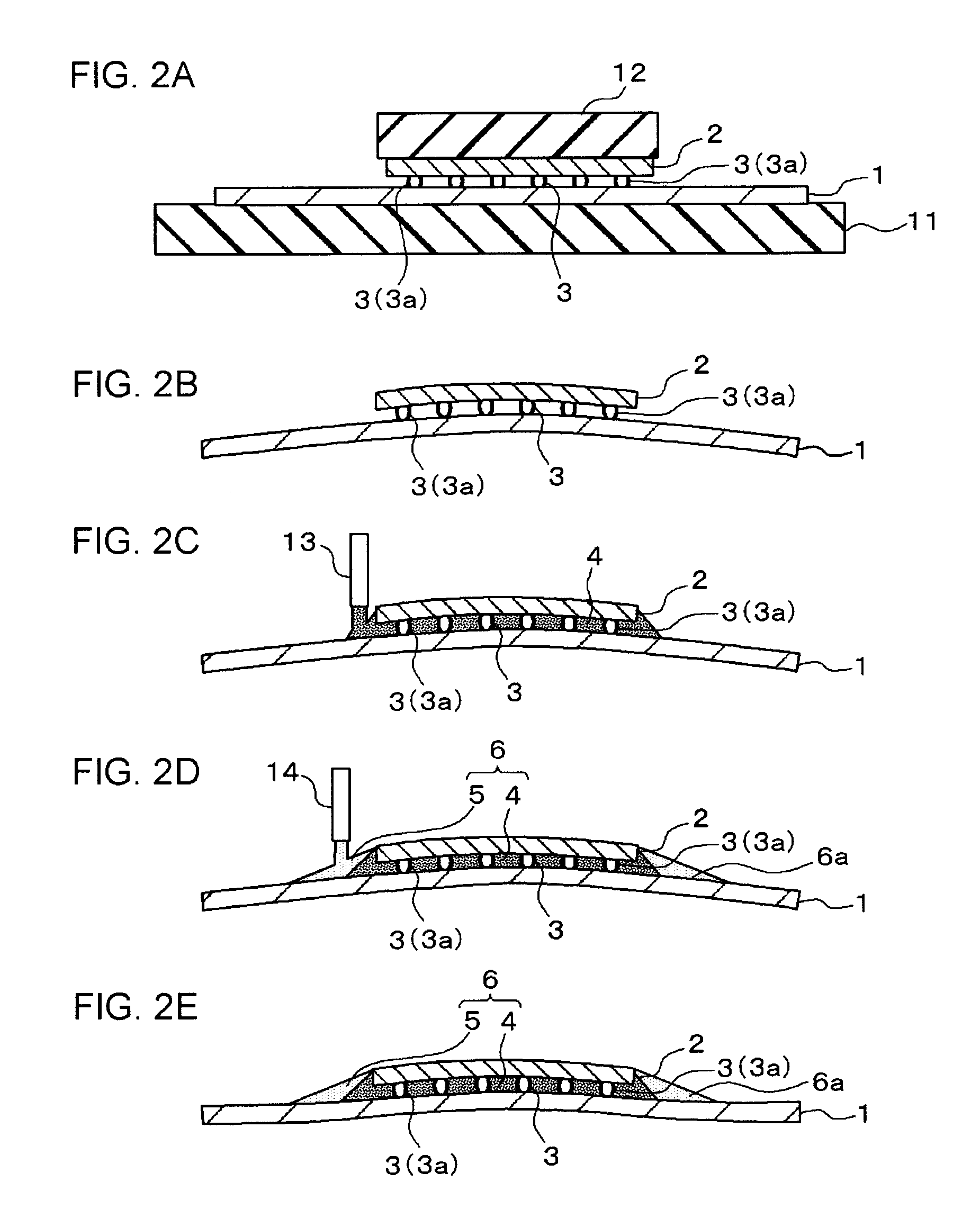

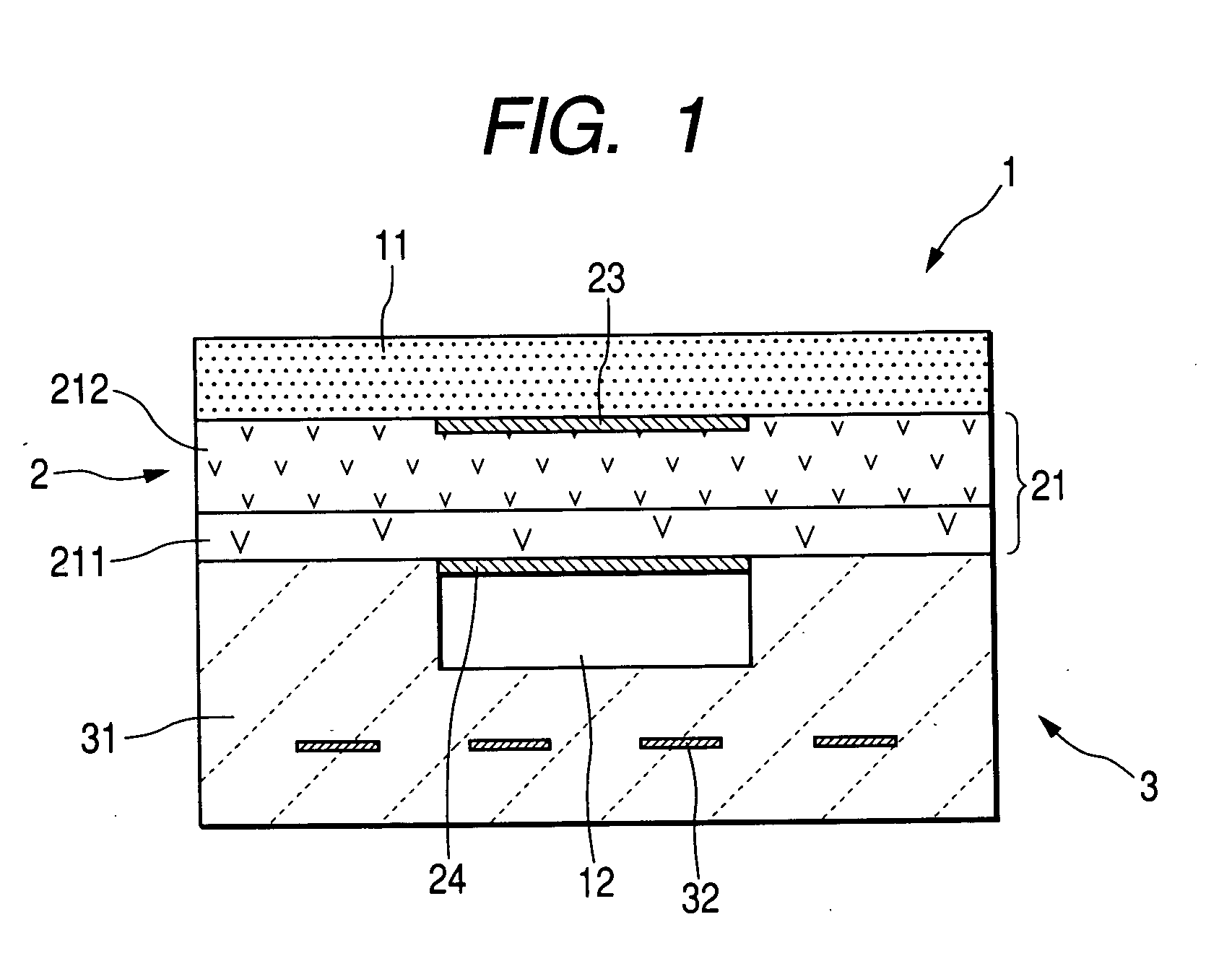

Metal base circuit board

ActiveUS20110132644A1Improve workabilityGood heat dissipationCircuit optical detailsPrinted circuit aspectsMetal foilPrinted circuit board

Lifespan of LEDs can be lengthened, and the workability of the printed circuit board during circuit formation and during LED mounting can be improved.A metal base circuit board, having an insulating layer with a linear expansion coefficient of 60 ppm per degree C. or higher and 120 ppm per degree C. or lower, a metal foil provided on one side of the insulating layer, comprising a metal material with a linear expansion coefficient of 10 ppm per degree C. or higher and 35 ppm per degree C. or lower, a circuit portion and a non-circuit potion having a linear expansion coefficient of 10 ppm per degree C. or higher and 35 ppm per degree C. or lower, and a white film formed on top of the insulating layer, circuit portion, and non-circuit portion, the total sum of the areas of the non-circuit portion and the circuit portion on top of the insulating layer being 50% or higher and 95% or lower relative to the area of the metal foil, and the relation between the linear expansion coefficients of each of the materials being: linear expansion coefficient of insulating layer>linear expansion coefficient of metal foil>linear expansion coefficient of circuit portion and non-circuit portion.

Owner:DENKA CO LTD

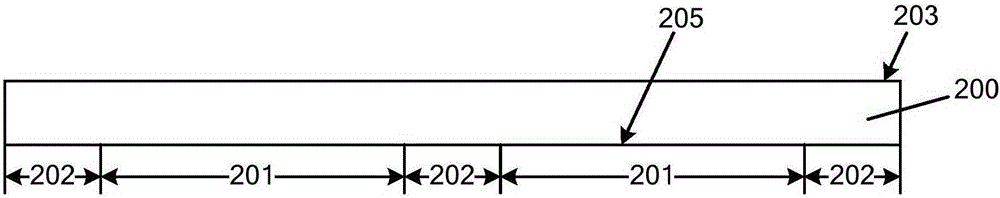

Packaging method

InactiveCN105355569AEliminate driftDrift suppressionSolid-state devicesSemiconductor/solid-state device manufacturingPlastic packagingNon functional

A packaging method comprises the steps of: providing a carrier plate, wherein the carrier plate comprises a plurality of chip regions and cutting regions arranged between the adjacent chip regions, the carrier plate further comprises a first surface, and a plurality of grooves are formed in the cutting regions in the first surface of the carrier plate; providing chips, wherein each chip comprises a functional surface and a non-functional side surface which are opposite to each other, the surface of each functional surface is provided with bumps, and the bumps protrude out of the functional surfaces; fixing the non-functional side surfaces of the chips with the first surface of the carrier plate in the chip regions; forming a plastic packaging layer on the first surface of the carrier plate and the surfaces of the chips, wherein the plastic packaging layer exposes top part surfaces of the bumps; removing the carrier plate after forming the plastic packaging layer; forming a rewiring structure on the surface of the plastic packaging layer and the functional surfaces of the chips; and cutting the plastic packaging layer and the rewiring structure, so that the plurality of chips are separated from one another, thereby forming an independent packaging structure. The yield and reliability of the formed packaging products are improved.

Owner:NANTONG FUJITSU MICROELECTRONICS

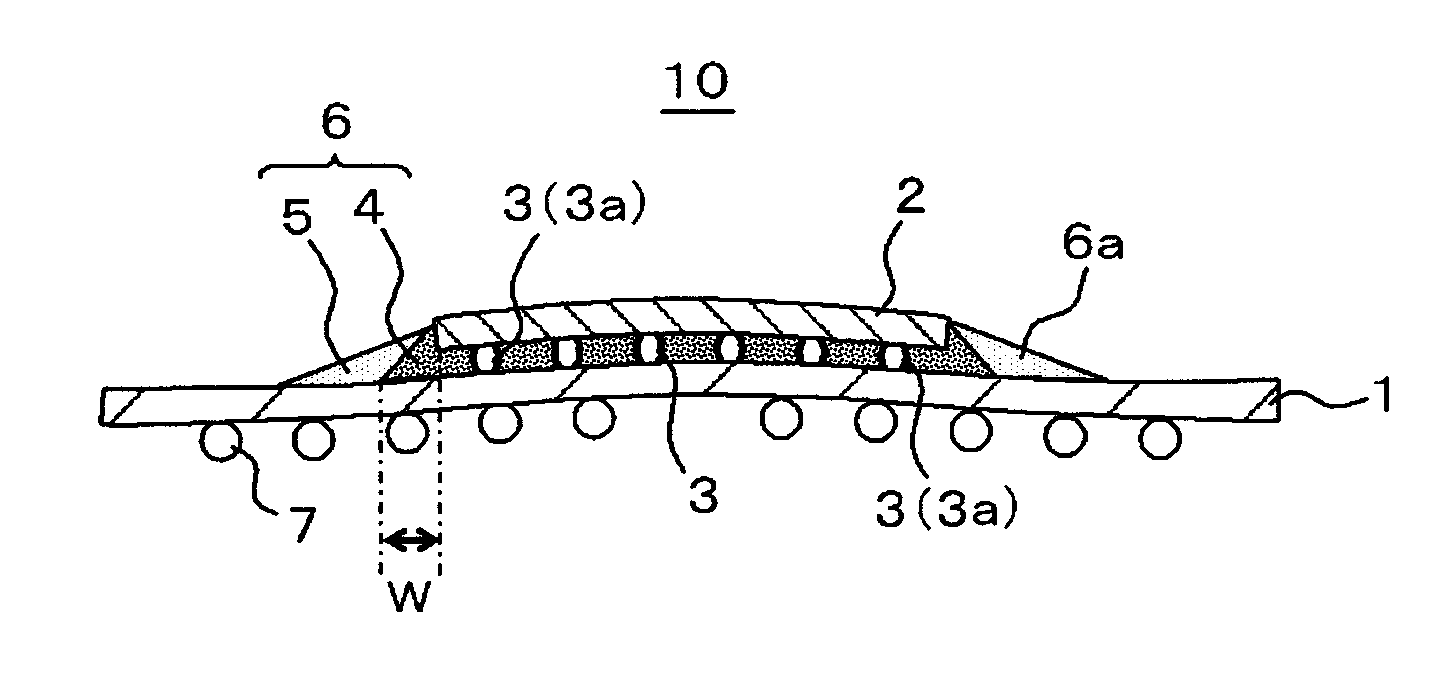

Semiconductor device and method for manufacturing the same

ActiveUS20110084384A1Improve flatnessStress is appliedSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipEngineering

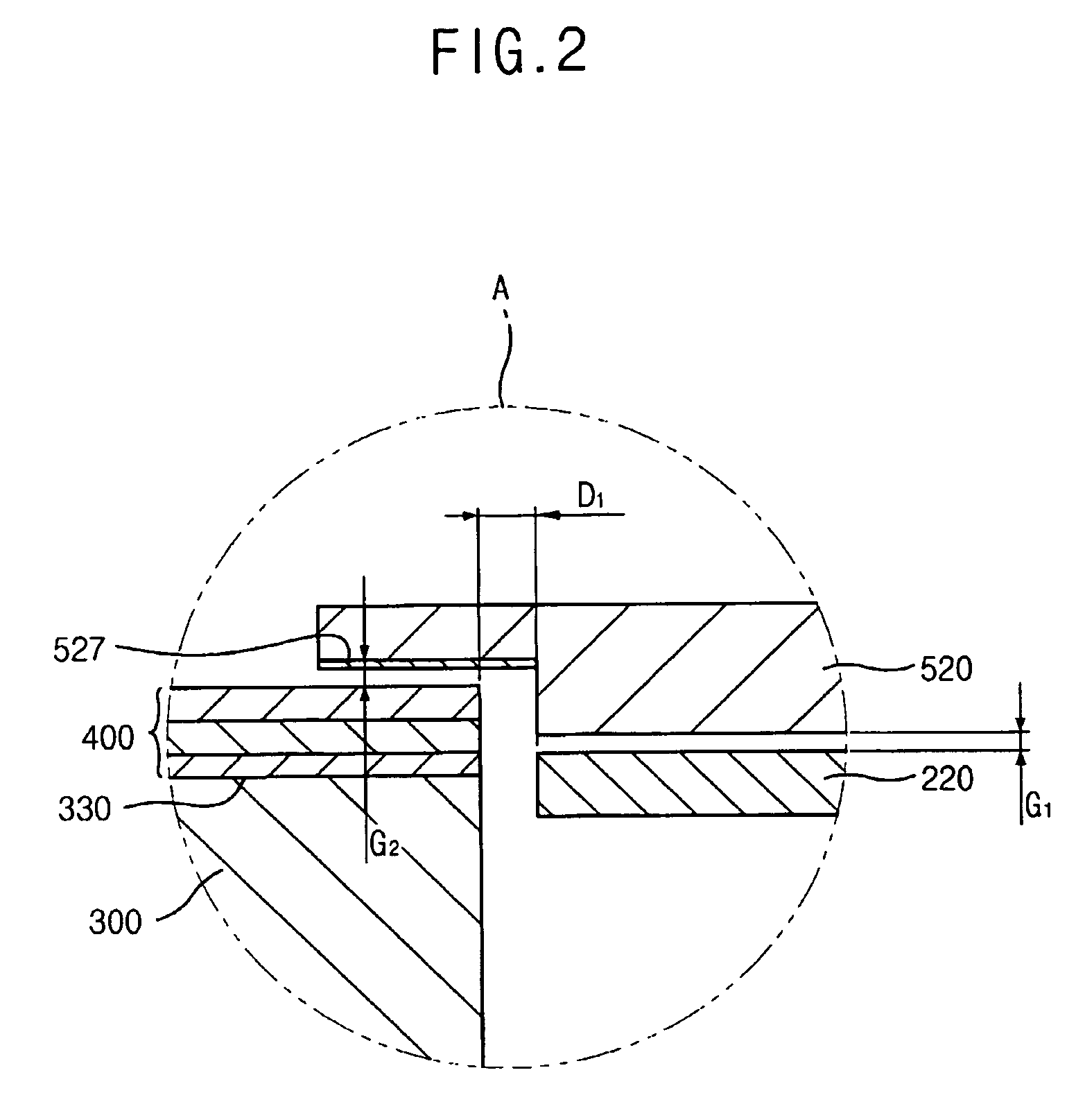

A semiconductor device includes a substrate, a semiconductor chip that is bonded to one of the faces of the substrate via bumps, and has a device formation face facing the one of the faces, and a resin that fills the space between the device formation face of the semiconductor chip and the one of the faces of the substrate. The resin includes: a first resin that is formed in a formation region of bumps placed on the outermost circumference of the bumps, and is formed inside the formation region, and a second resin that is formed outside the first resin. The thermal expansion coefficient of the substrate is higher than the thermal expansion coefficient of the first resin. The thermal expansion coefficient of the second resin is higher than the thermal expansion coefficient of the first resin.

Owner:RENESAS ELECTRONICS CORP

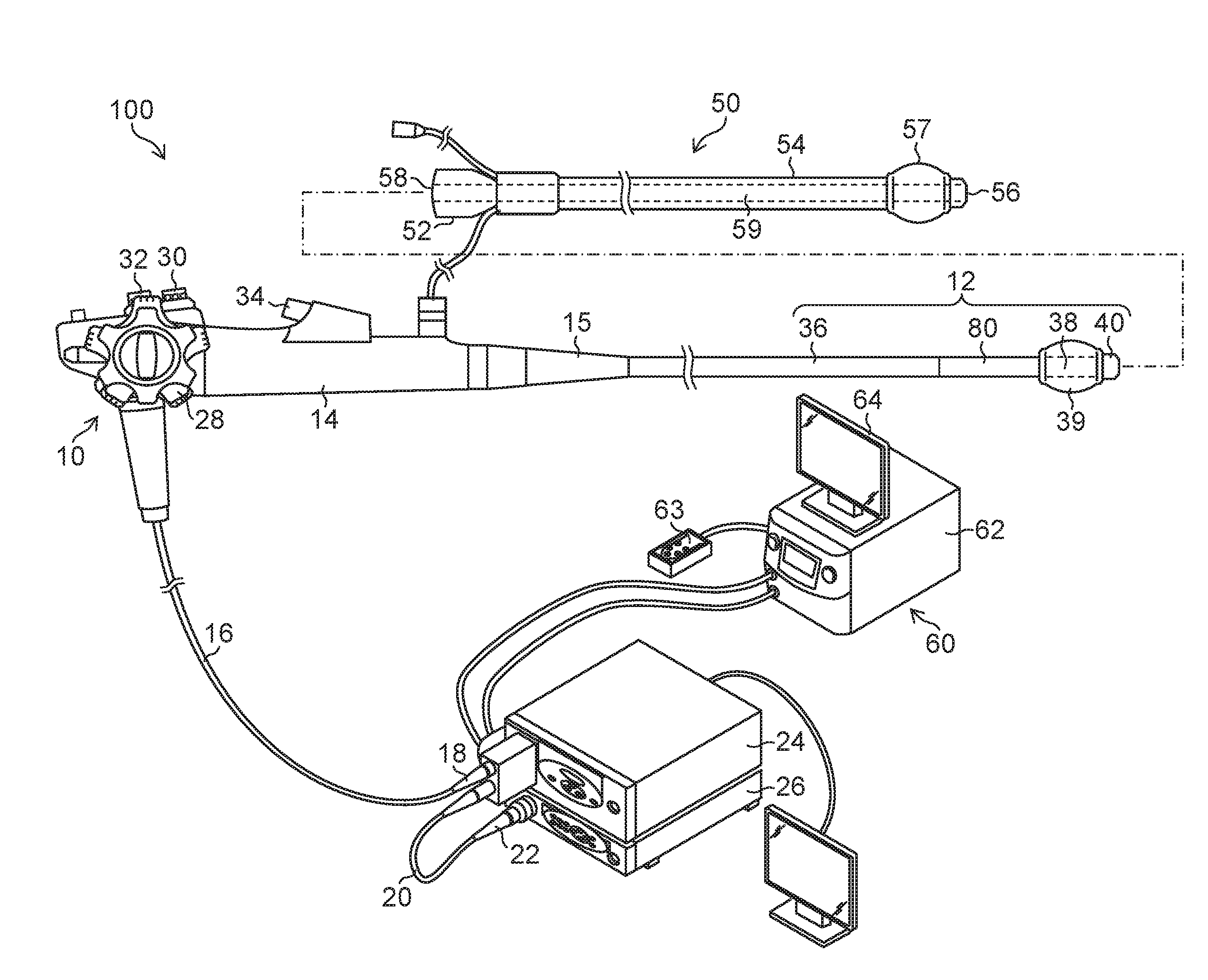

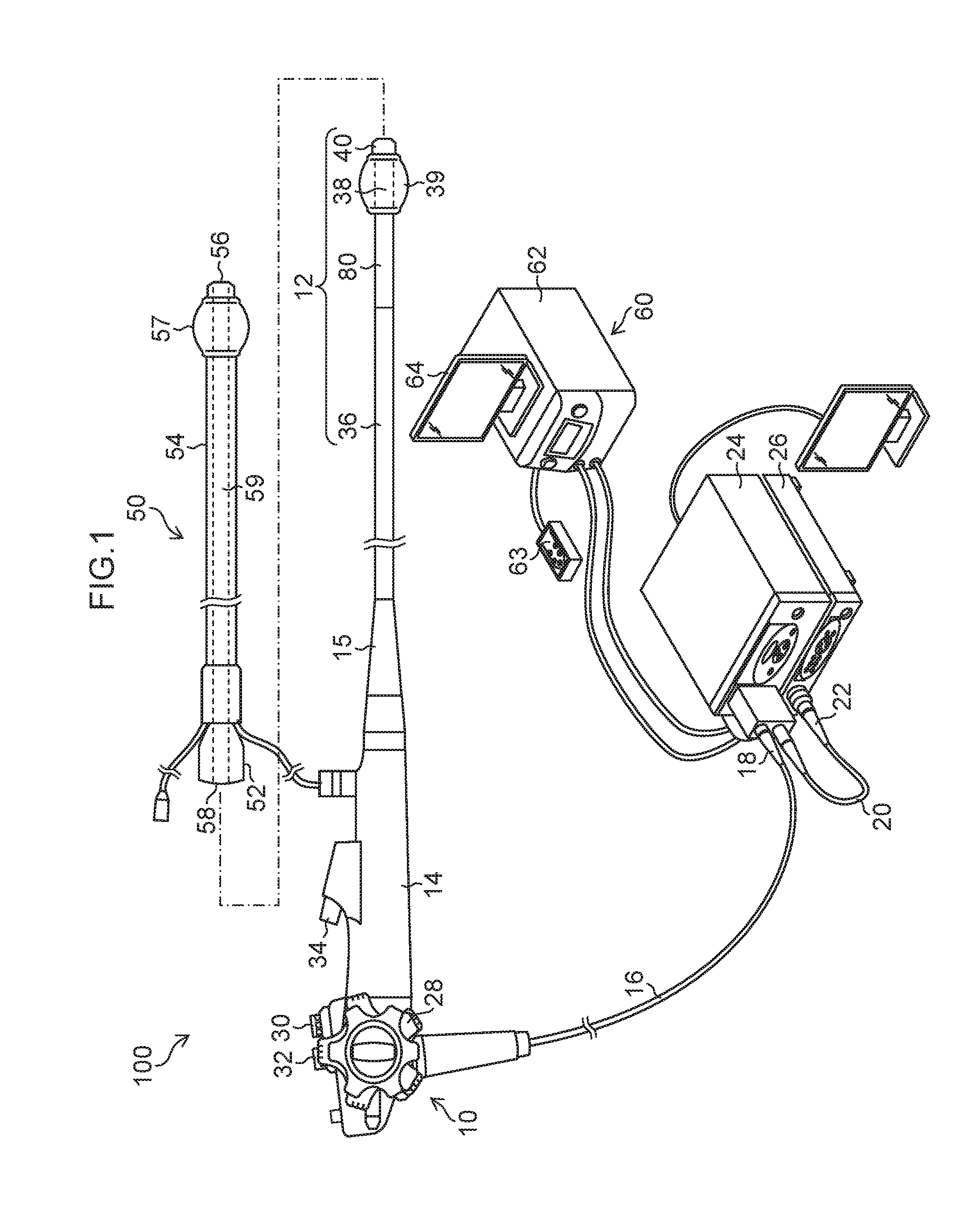

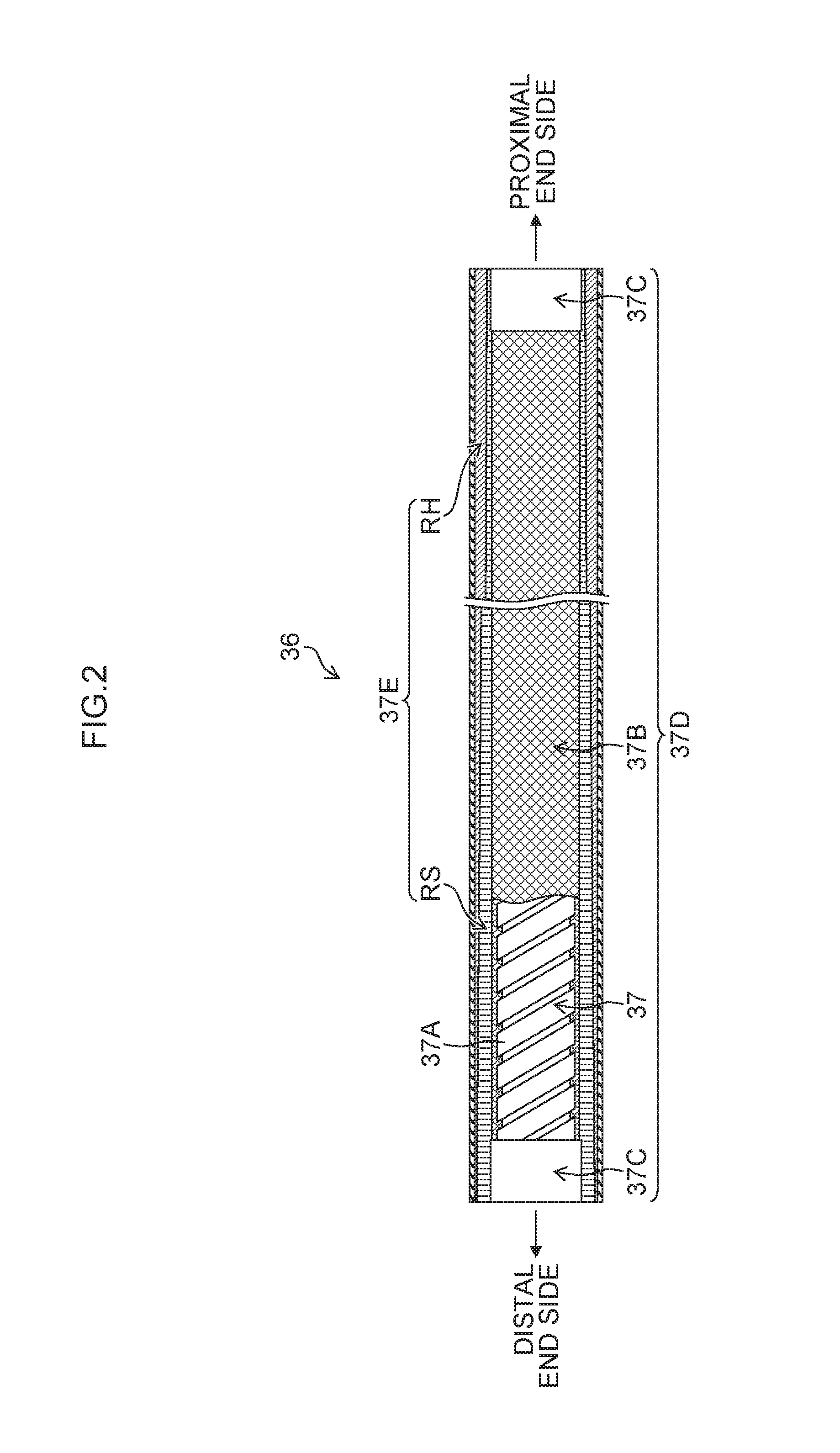

Endoscope system

ActiveUS20160227982A1Prevent warpageFacilitate insertionGastroscopesOesophagoscopesBiomedical engineeringEndoscope

There is provided an endoscope system which can secure appropriate bending stiffness of an insertion portion while maintaining the slide length of an endoscope insertion portion. According to one aspect of one of the present invention, in an endoscope system including an endoscope and an insertion assisting tool in which the endoscope is inserted and which assists the insertion of an endoscope insertion portion into a body, a flexible portion of the endoscope insertion portion includes a projection region which projects from the distal end opening of a tube body when the endoscope insertion portion is located in the distal end position in a movable range with respect to the tube body of the insertion assisting tool, and the projection region includes a bending stiffness change portion in which bending stiffness increases from a first position on the distal end side to a second position on the proximal end side.

Owner:FUJIFILM CORP

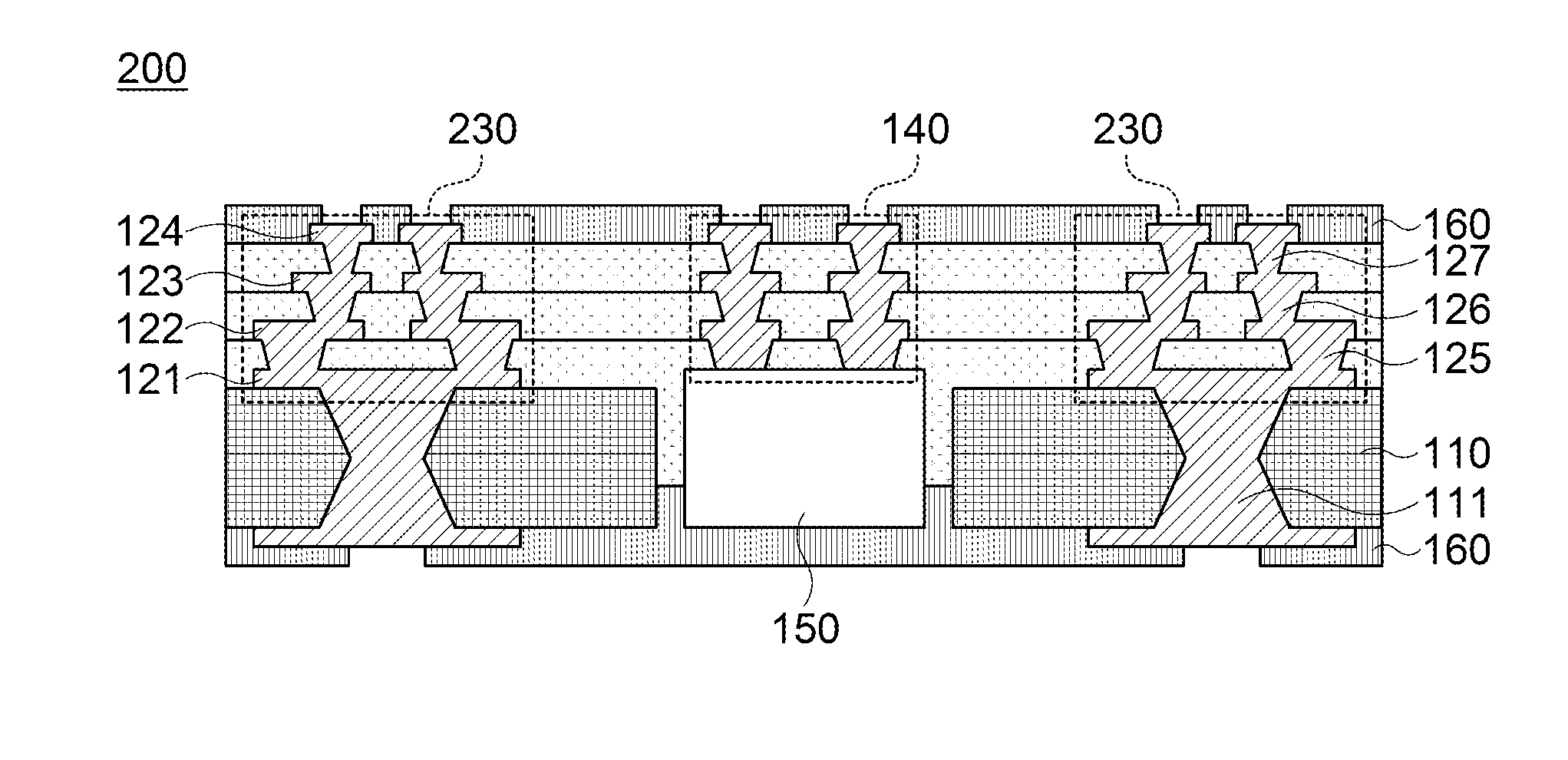

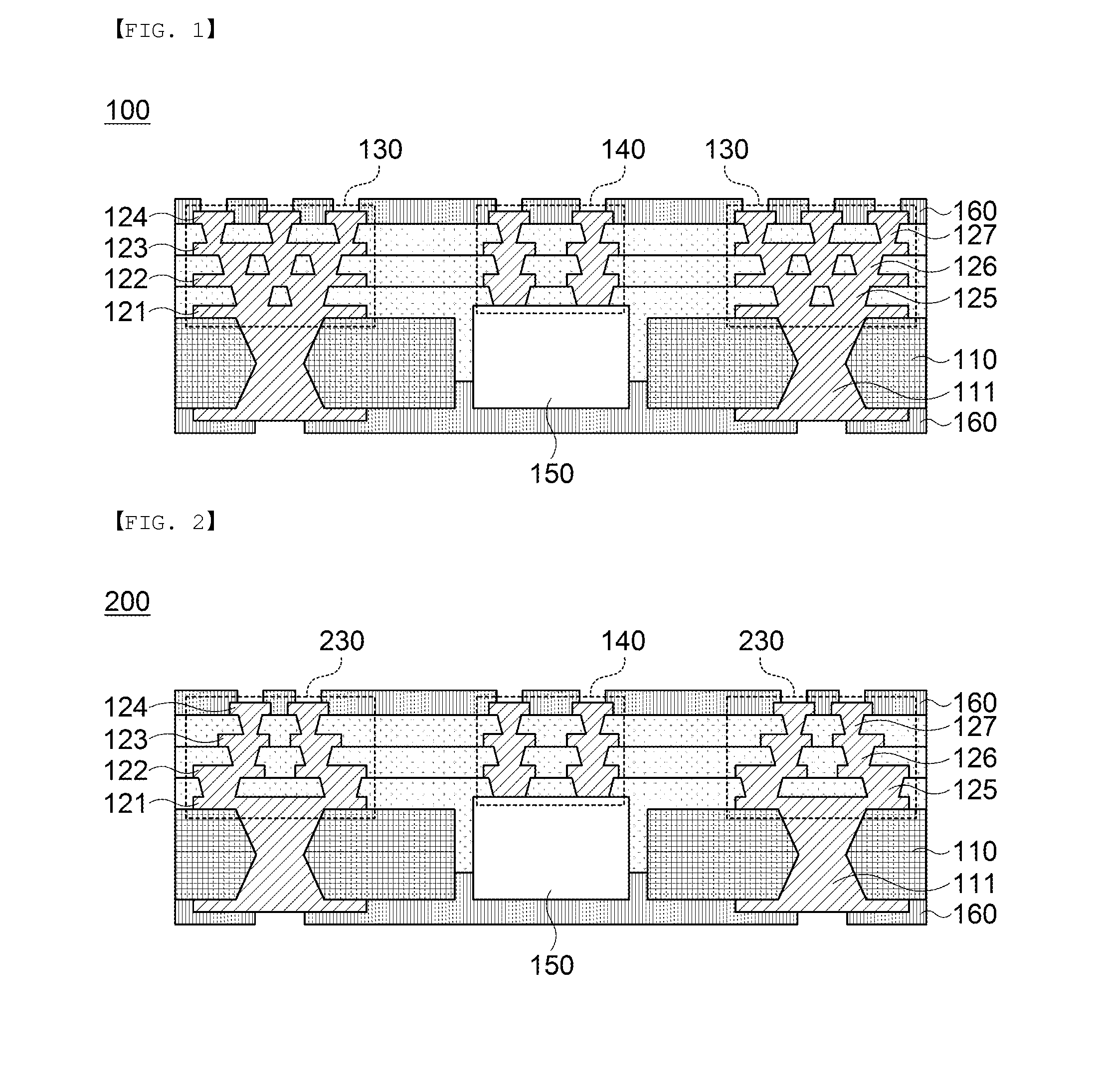

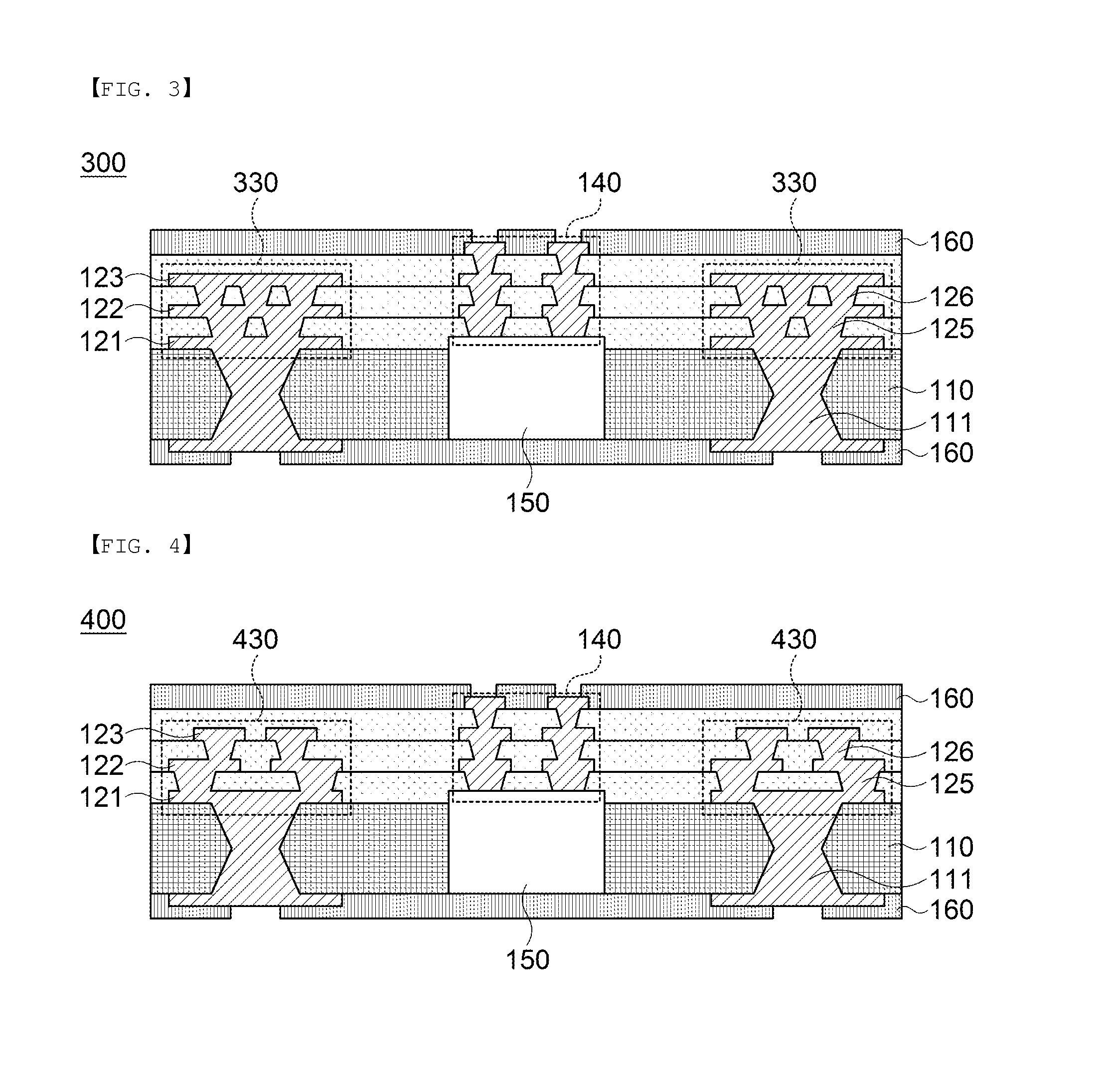

Multilayer printed circuit board

InactiveUS20150107880A1Prevent warpagePrevent warpage from being generatedPrinted circuit aspectsSolid-state devicesResistPrinted circuit board

Disclosed herein is a multilayer printed circuit board. The multilayer printed circuit board according to the present invention includes: a stack via stacked in an upper portion of a core layer; staggered vias formed at both sides of the stack via and stacked on the core layer; and a solder resist layer stacked in a lower portion of the core layer and stacked on an insulating film except for open regions of the stack via and the staggered vias, such that the plurality of vias formed in the staggered via may increase rigidity to prevent warpage of the multilayer printed circuit board from being generated.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

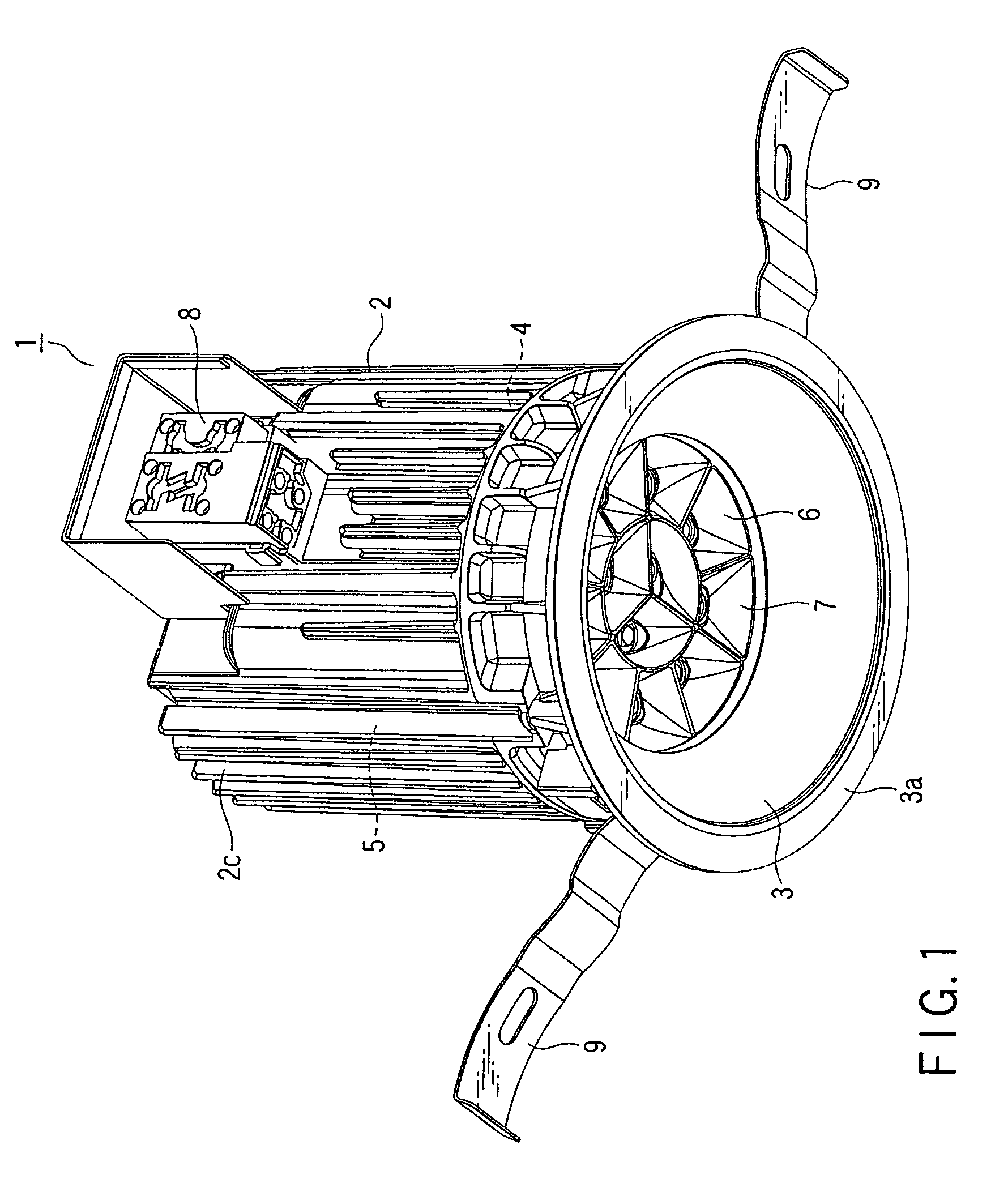

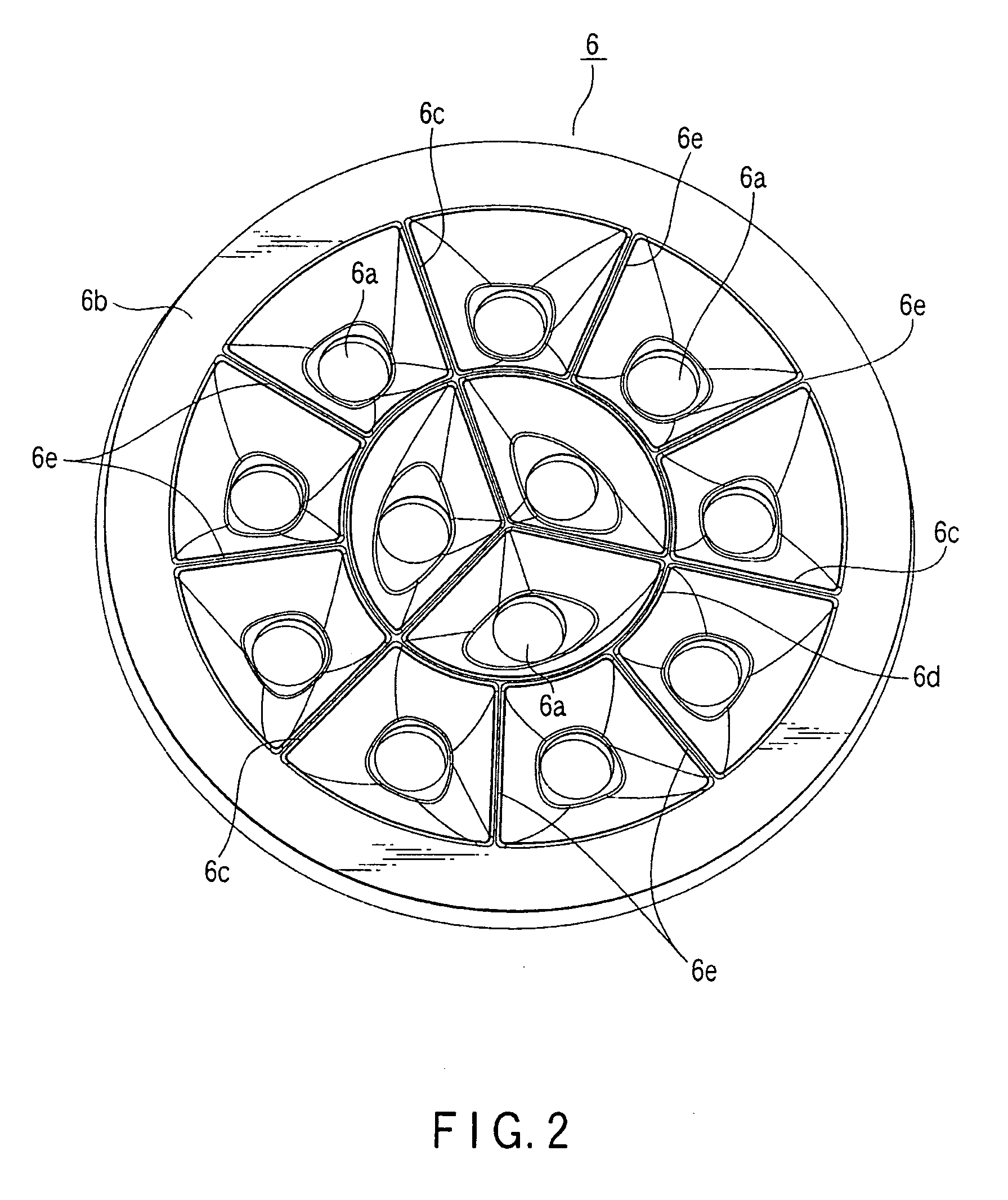

Reflector and lighting apparatus comprising reflector

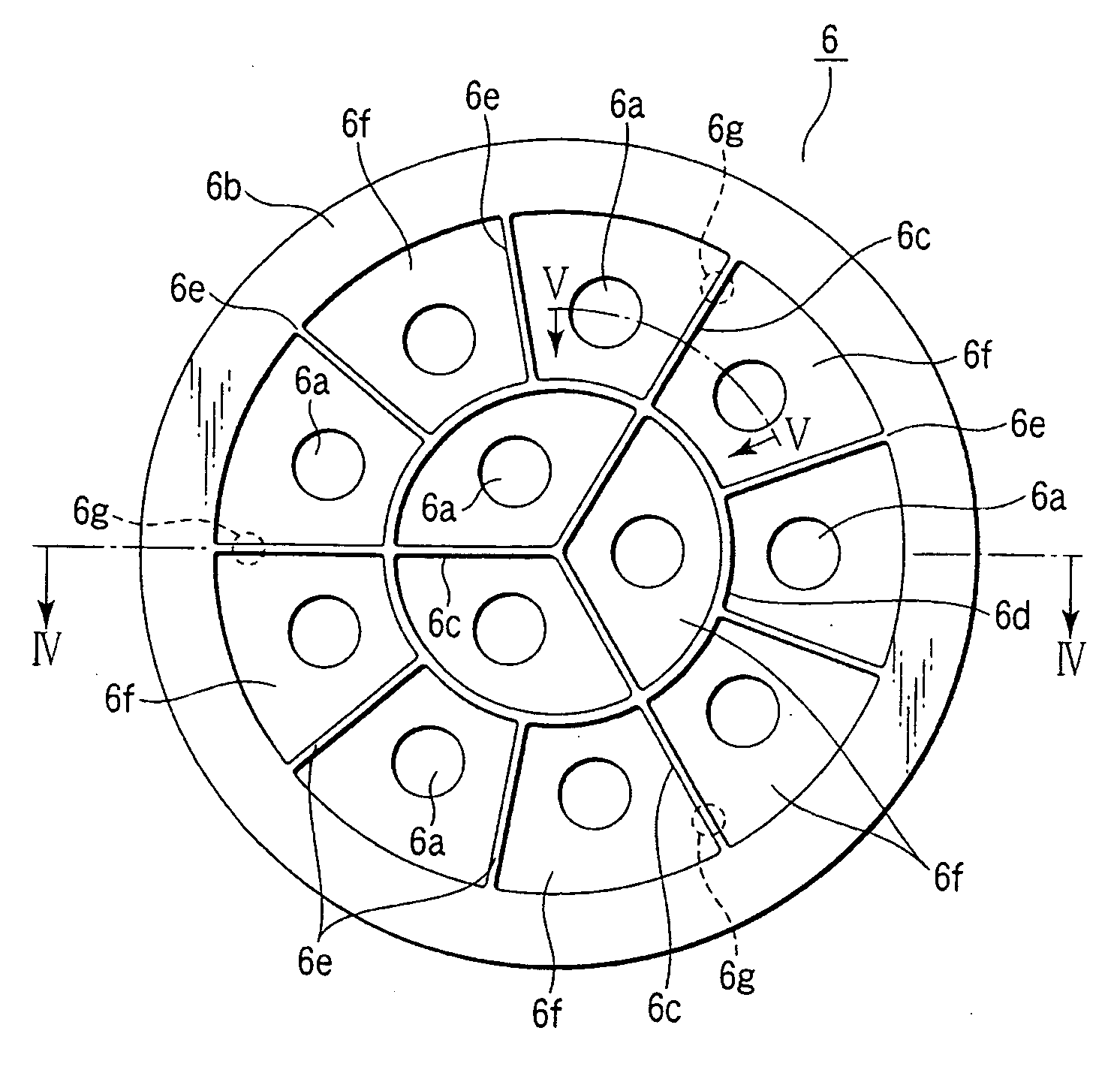

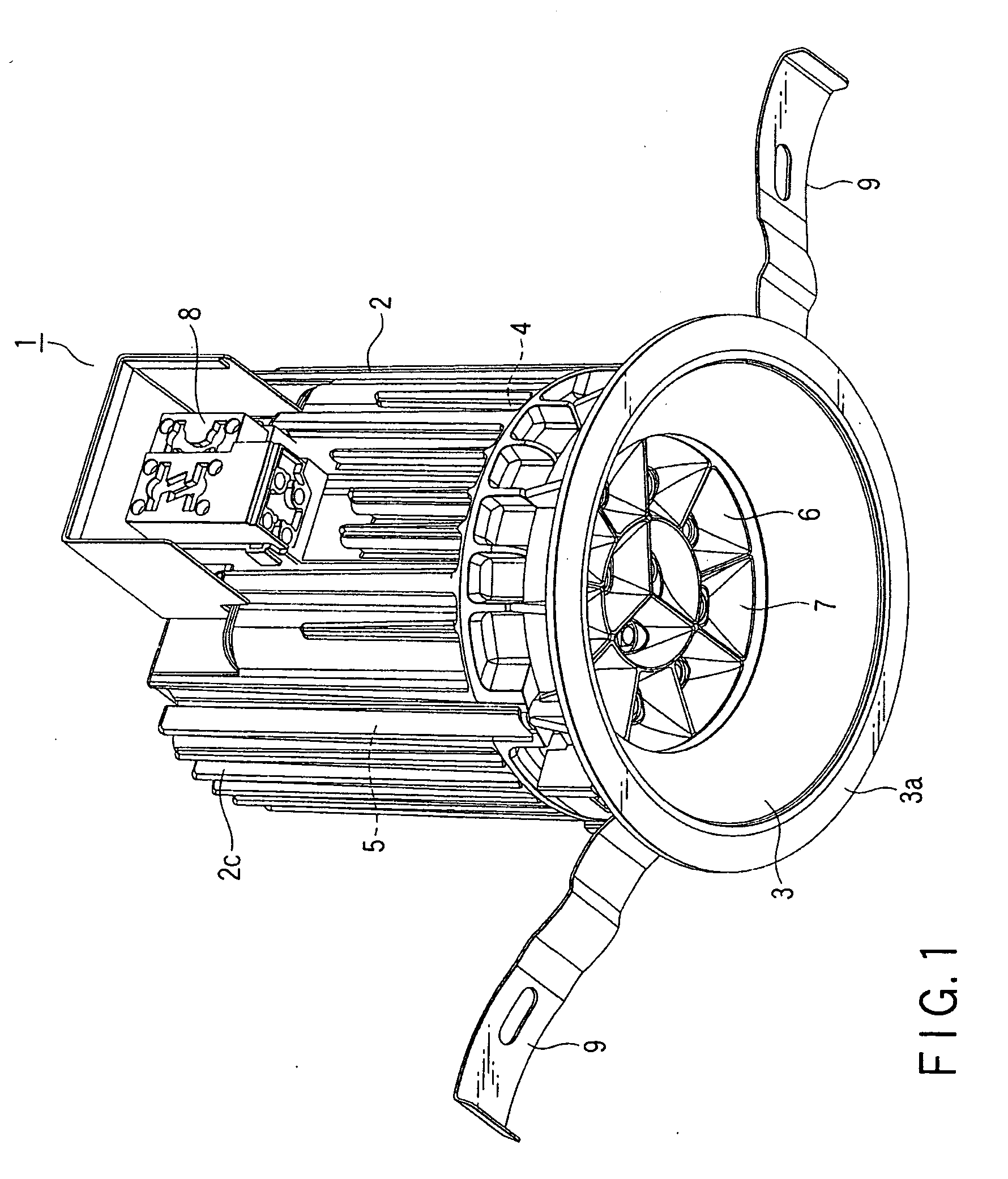

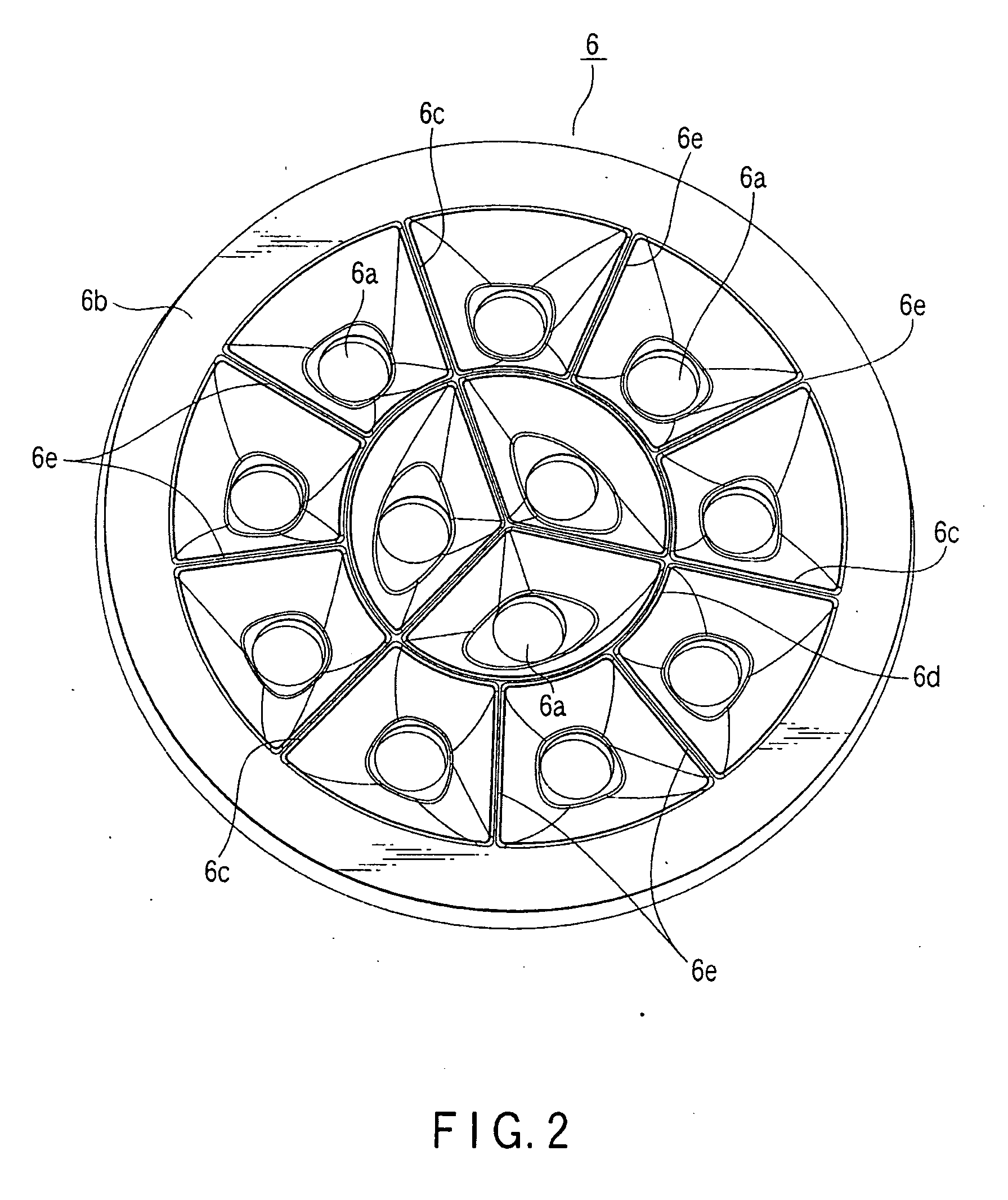

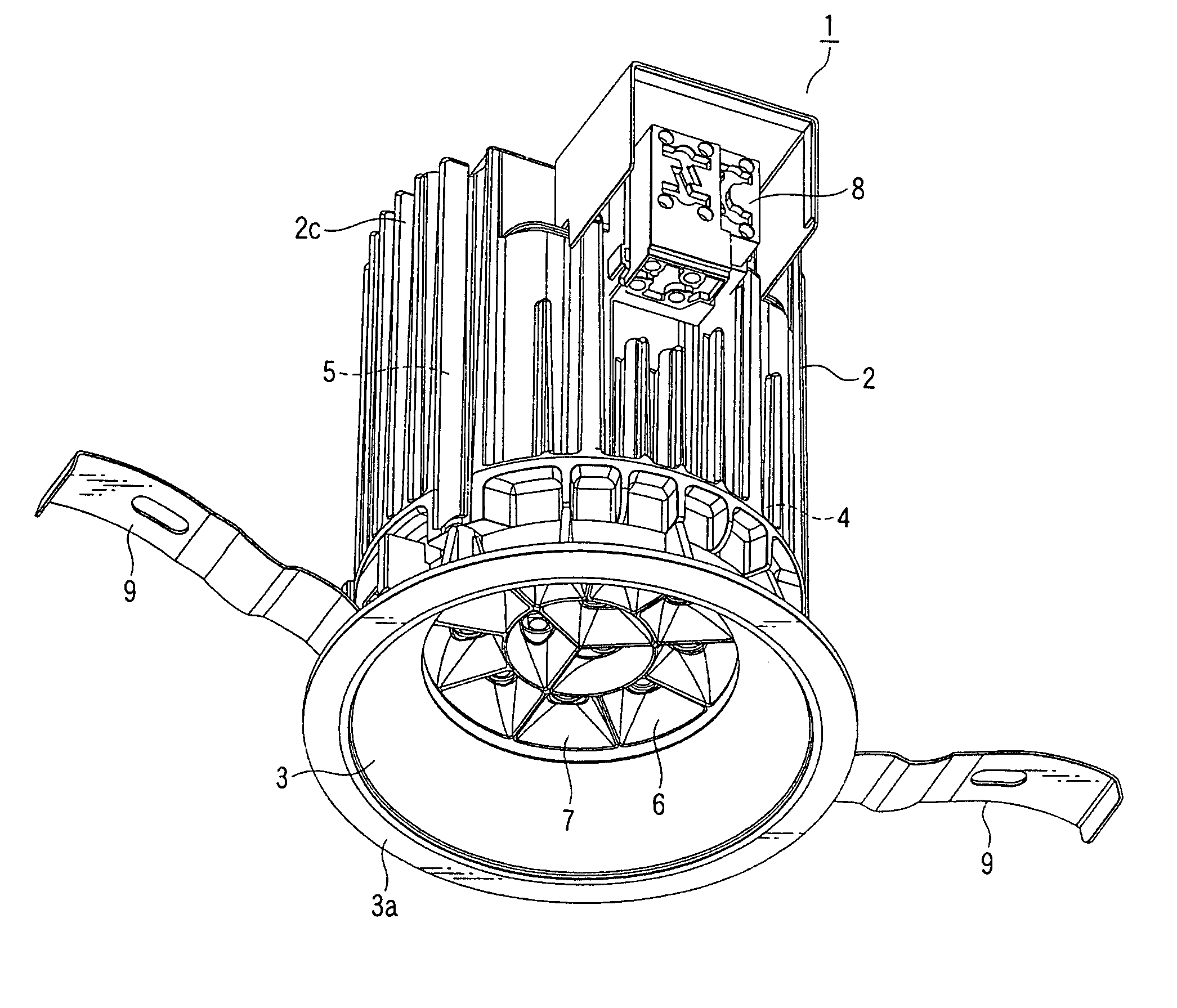

InactiveUS20090290354A1Prevent warpageAvoid deformationNon-electric lightingPlanar light sourcesLight equipmentStructural engineering

A reflector built in a down light includes a plurality of floodlight openings respectively exposing a plurality of light-emitting elements to a front surface side, a plurality of radial partition walls which respectively partition and surround these floodlight openings, and an inner circumferential partition wall. Each of the partition walls has a ridge line, and the reflector includes a plurality of reflection concave surfaces each which open and widen from a respective one of the plurality of floodlight openings towards ridge lines of the plurality of partition walls which respectively surround the plurality of floodlight openings. The plurality of radial partition walls extend from the center of the reflector towards the outer circumference, and the inner circumferential partition wall is located between the center and the outer circumference.

Owner:TOSHIBA LIGHTING & TECH CORP +1

Reflector and lighting apparatus comprising reflector

InactiveUS7993033B2Prevent warpageAvoid deformationPlanar light sourcesNon-electric lightingStructural engineeringFloodlight

A reflector built in a down light includes a plurality of floodlight openings respectively exposing a plurality of light-emitting elements to a front surface side, a plurality of radial partition walls which respectively partition and surround these floodlight openings, and an inner circumferential partition wall. Each of the partition walls has a ridge line, and the reflector includes a plurality of reflection concave surfaces each which open and widen from a respective one of the plurality of floodlight openings towards ridge lines of the plurality of partition walls which respectively surround the plurality of floodlight openings. The plurality of radial partition walls extend from the center of the reflector towards the outer circumference, and the inner circumferential partition wall is located between the center and the outer circumference.

Owner:TOSHIBA LIGHTING & TECH CORP +1

Semiconductor device and method for manufacturing the same

ActiveUS8710651B2Prevent warpageImprove flatnessSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipThermal expansion

A semiconductor device includes a substrate, a semiconductor chip that is bonded to one of the faces of the substrate via bumps, and has a device formation face facing the one of the faces, and a resin that fills the space between the device formation face of the semiconductor chip and the one of the faces of the substrate. The resin includes: a first resin that is formed in a formation region of bumps placed on the outermost circumference of the bumps, and is formed inside the formation region, and a second resin that is formed outside the first resin. The thermal expansion coefficient of the substrate is higher than the thermal expansion coefficient of the first resin. The thermal expansion coefficient of the second resin is higher than the thermal expansion coefficient of the first resin.

Owner:RENESAS ELECTRONICS CORP

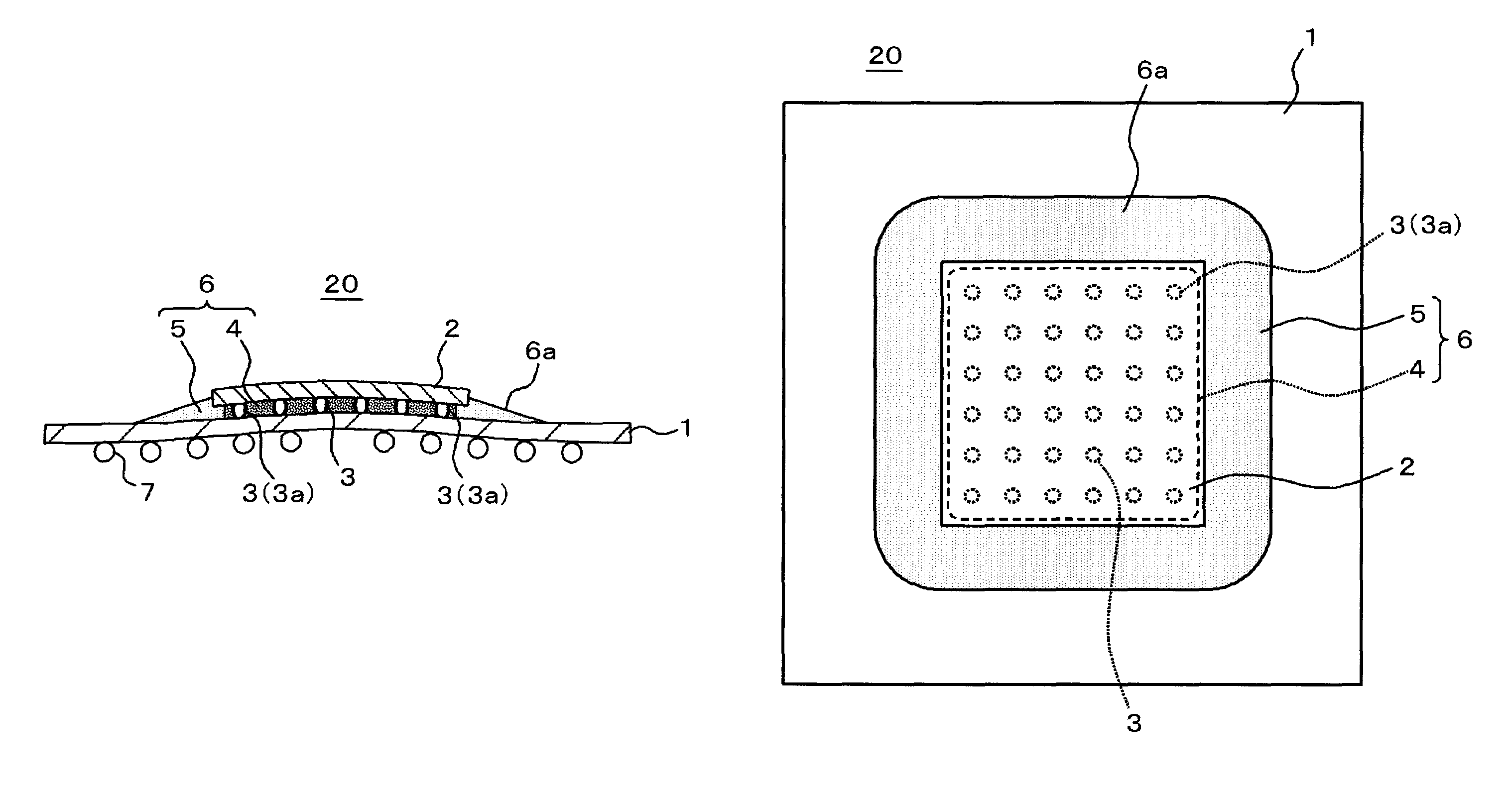

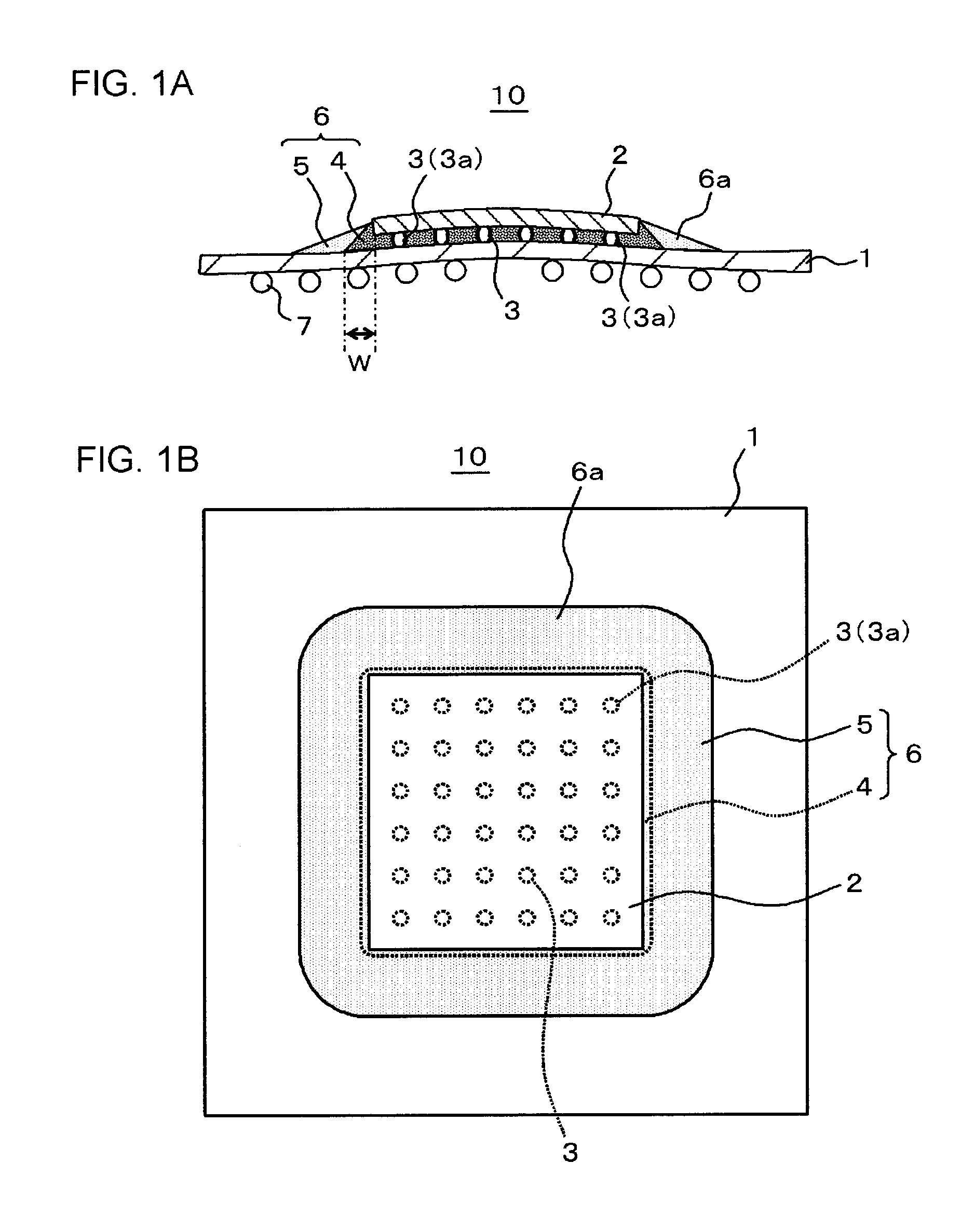

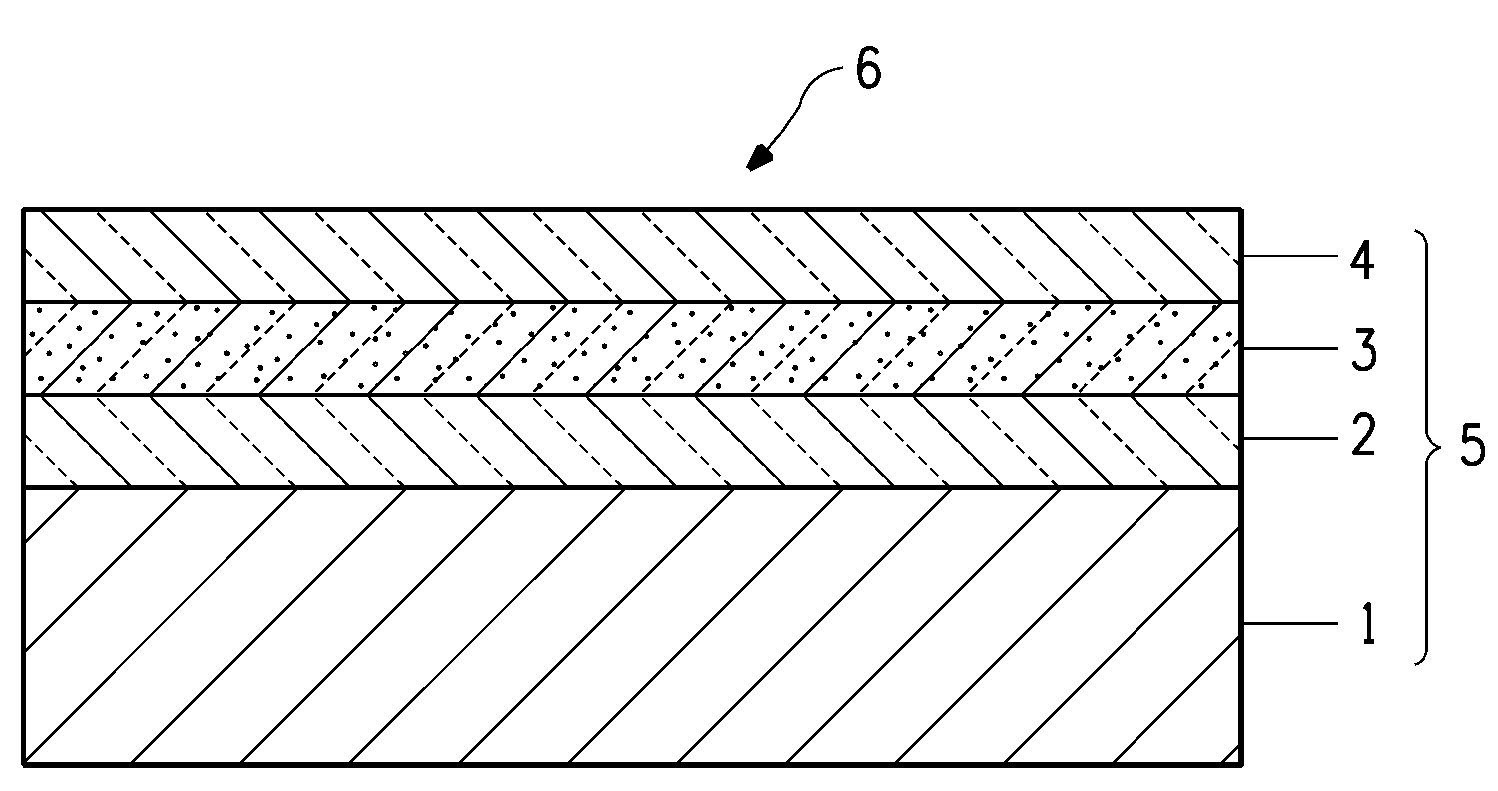

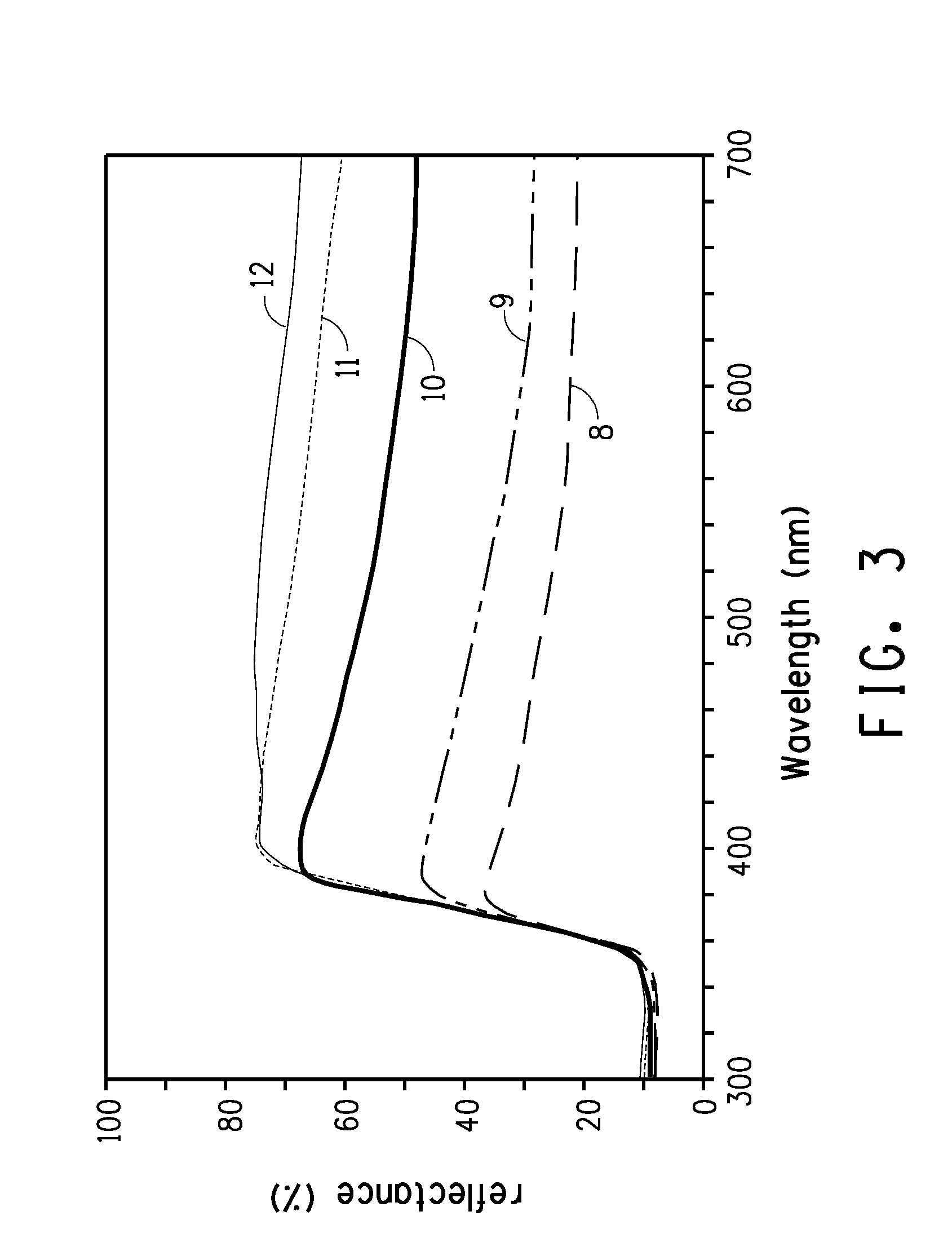

Substrate for Lighting Device and Production Thereof

InactiveUS20100086771A1High optical reflectancePrevent warpageCircuit optical detailsPrinted circuit aspectsMagnesium AluminateTitanium oxide

Disclosed is a substrate for a lighting device that includes an inorganic substrate with a coefficient of thermal expansion (TCE) of 7 to 13 ppm / K and an insulating layer. The insulating layer includes; a first transparent glass insulating layer having a TCE of 8.2 to 9.4 ppm / K; a white glass insulating layer which is on the first transparent glass insulating layer, and which contains, as white pigment, one or two or more of titanium oxide (TiO2), aluminum oxide (Al2O3), silicon dioxide (SiO2), strontium titanate (SrTiO2), barium titanate (BaTiO3), zinc oxide (ZnO), or magnesium aluminate (MgAl2O4), and has a TCE of 5.0 to 9.0 ppm / K; and a second transparent glass insulating layer which is on the white glass insulating layer, and which has a TCE of 8.2 to 9.4 ppm / K.

Owner:EI DU PONT DE NEMOURS & CO

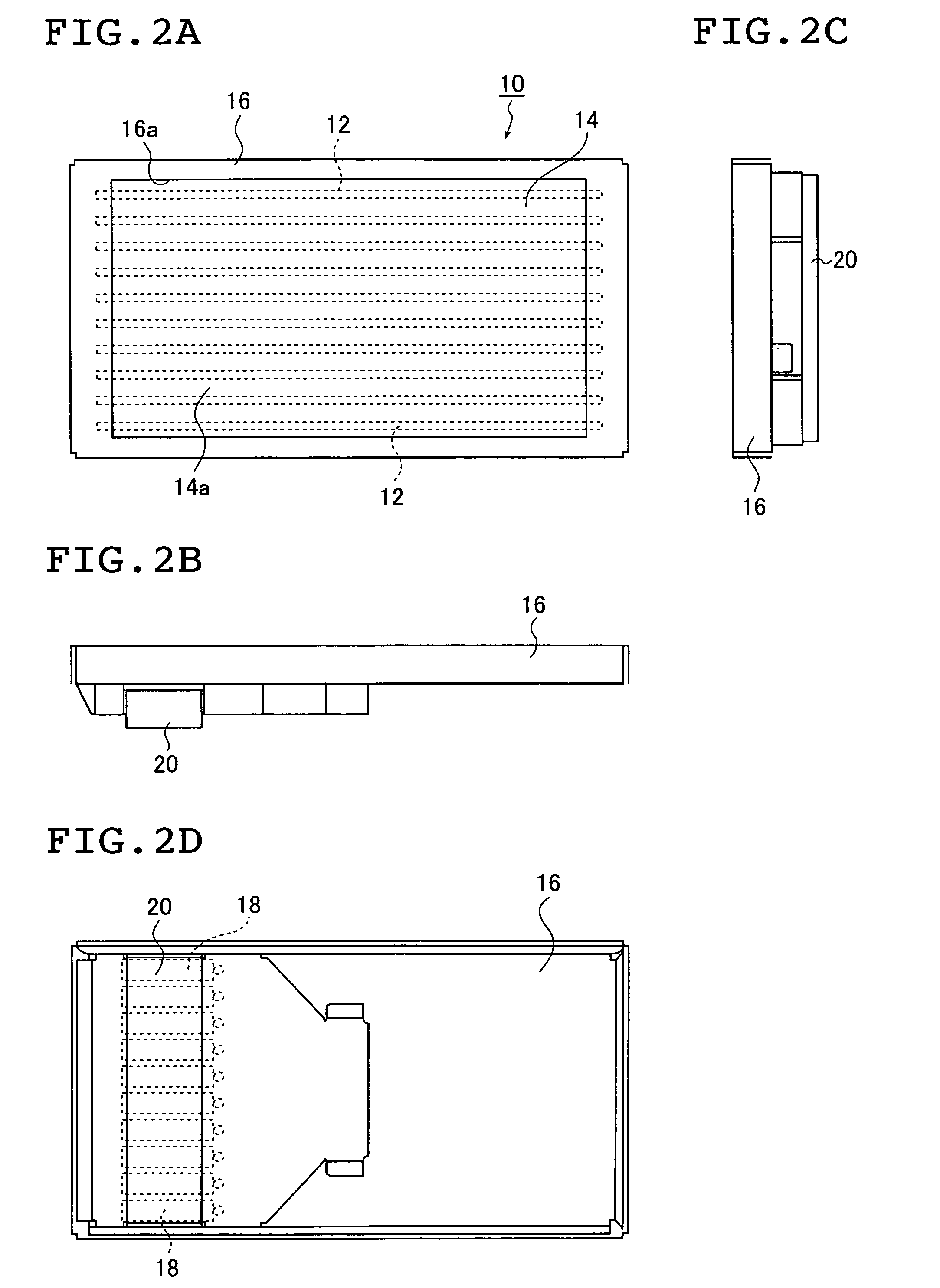

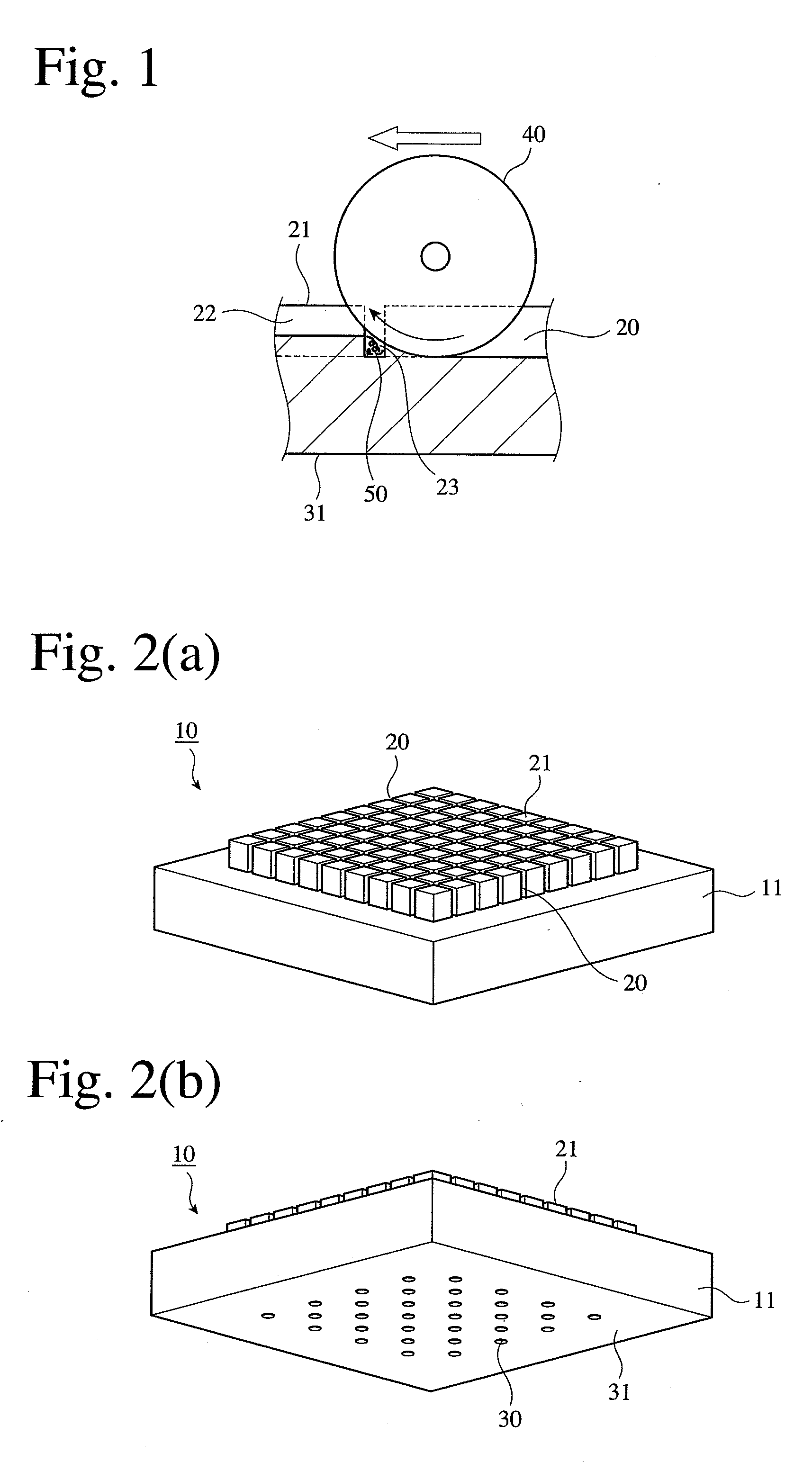

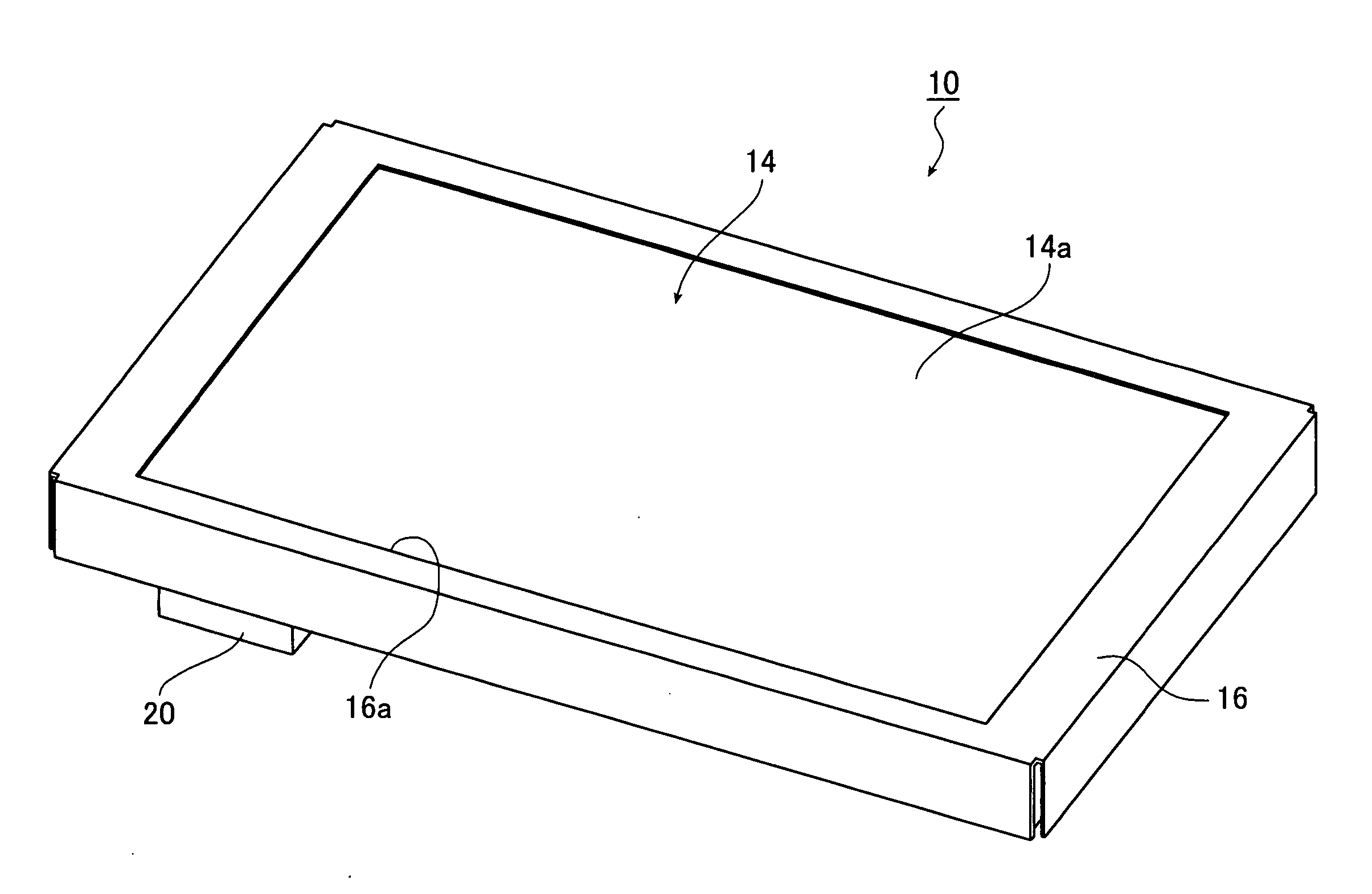

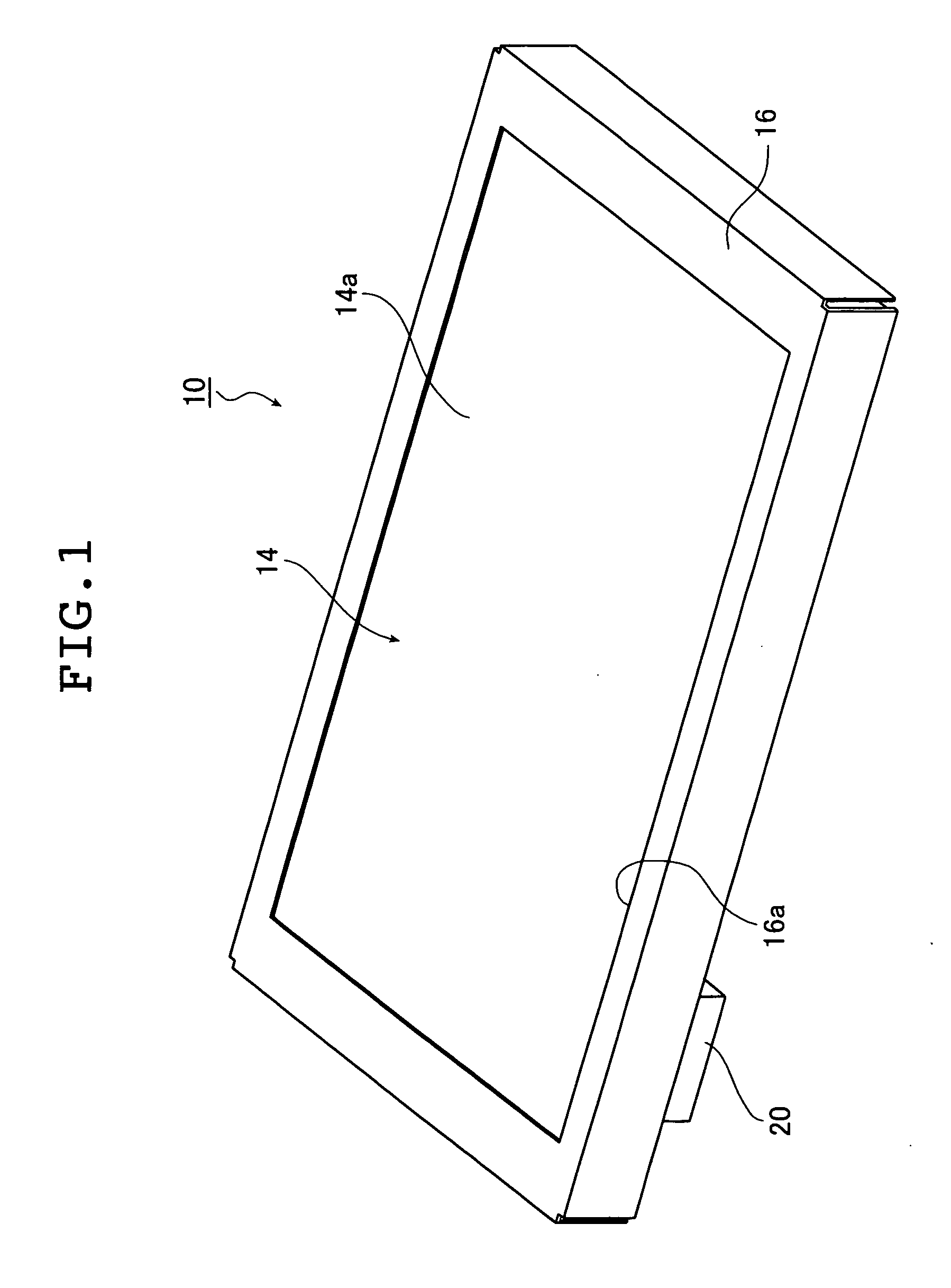

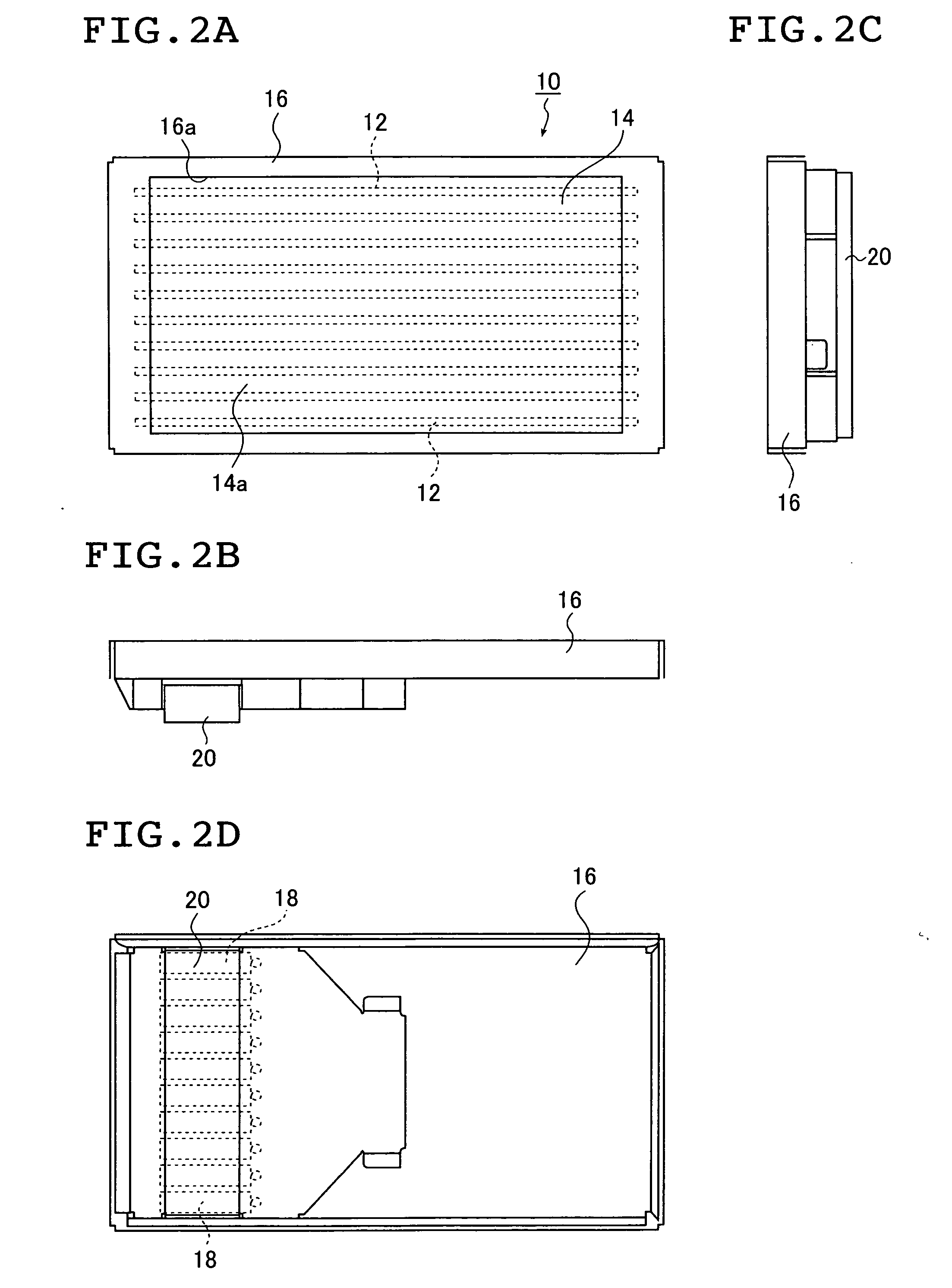

Light guide plate and a planar lighting device using the same

InactiveUS7445358B2Prevent warpagePrevent and suppress occurrenceElectric lightingOptical waveguide light guideLight guideOptoelectronics

A light guide plate of the invention has a plurality of unit light guide plates that are formed of a transparent resin material and which are joined together. Each of the unit light guide plates has a flat rectangular light exit surface and a back surface that is opposite the light exit surface and which has a parallel groove formed in generally a center and parallel to a side of the rectangular light exit surface. The light guide plate is used with a linear light source fitted in the parallel groove, satisfying the inequality (L0 / 280)2·k(14T2+710T)·(−0.65 log S+1.9)≦10, where L0 is the length (mm) of the light guide plate, k is the linear expansion coefficient [ / ° C.] of the resin material, Ts is the surface temperature [° C.] of the linear light source that has become stable, S is half of the cross-sectional area [mm2] of the unit light guide plate as it is cut through a plane perpendicular to the parallel groove, and T=Ts −25.

Owner:FUJIFILM CORP

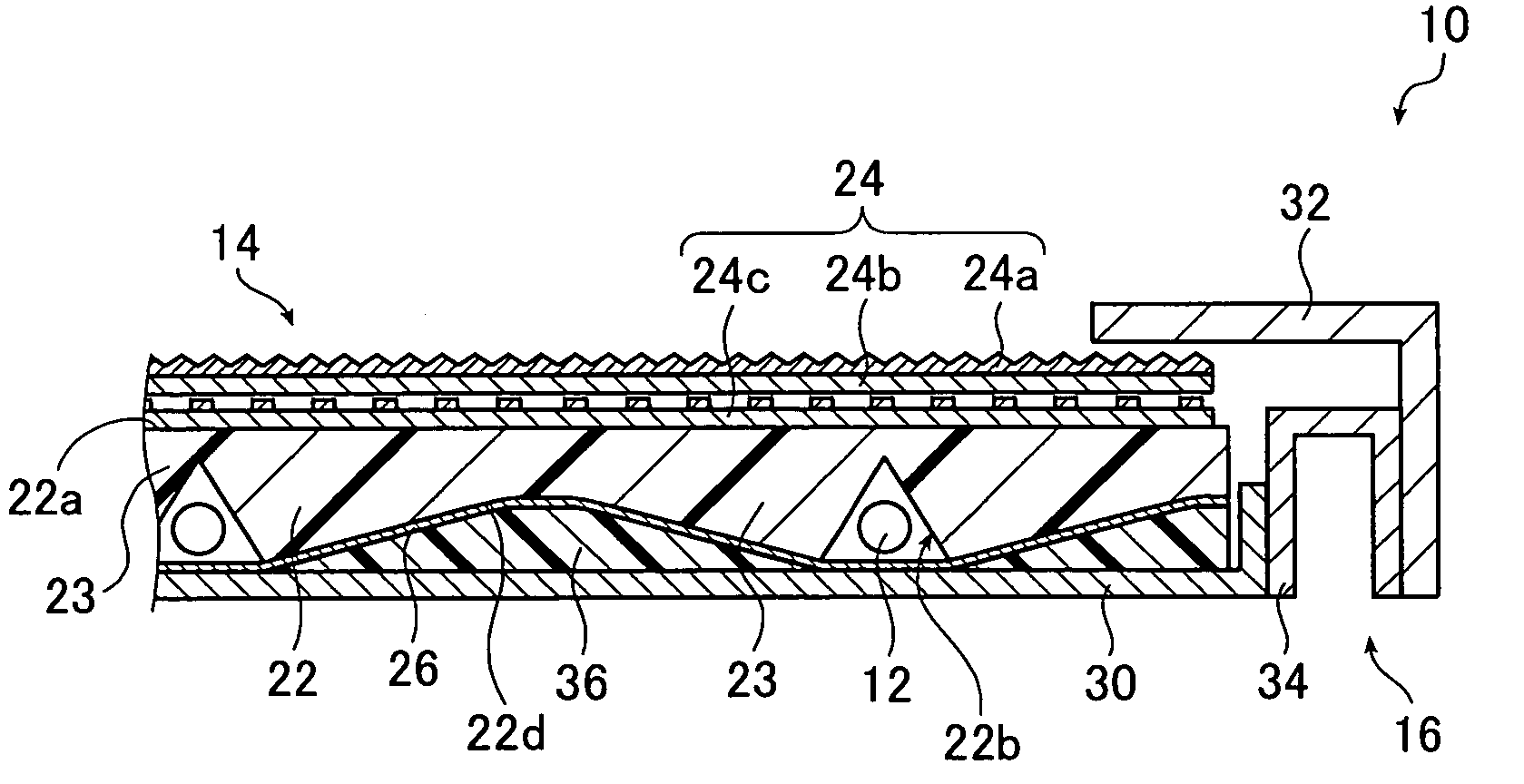

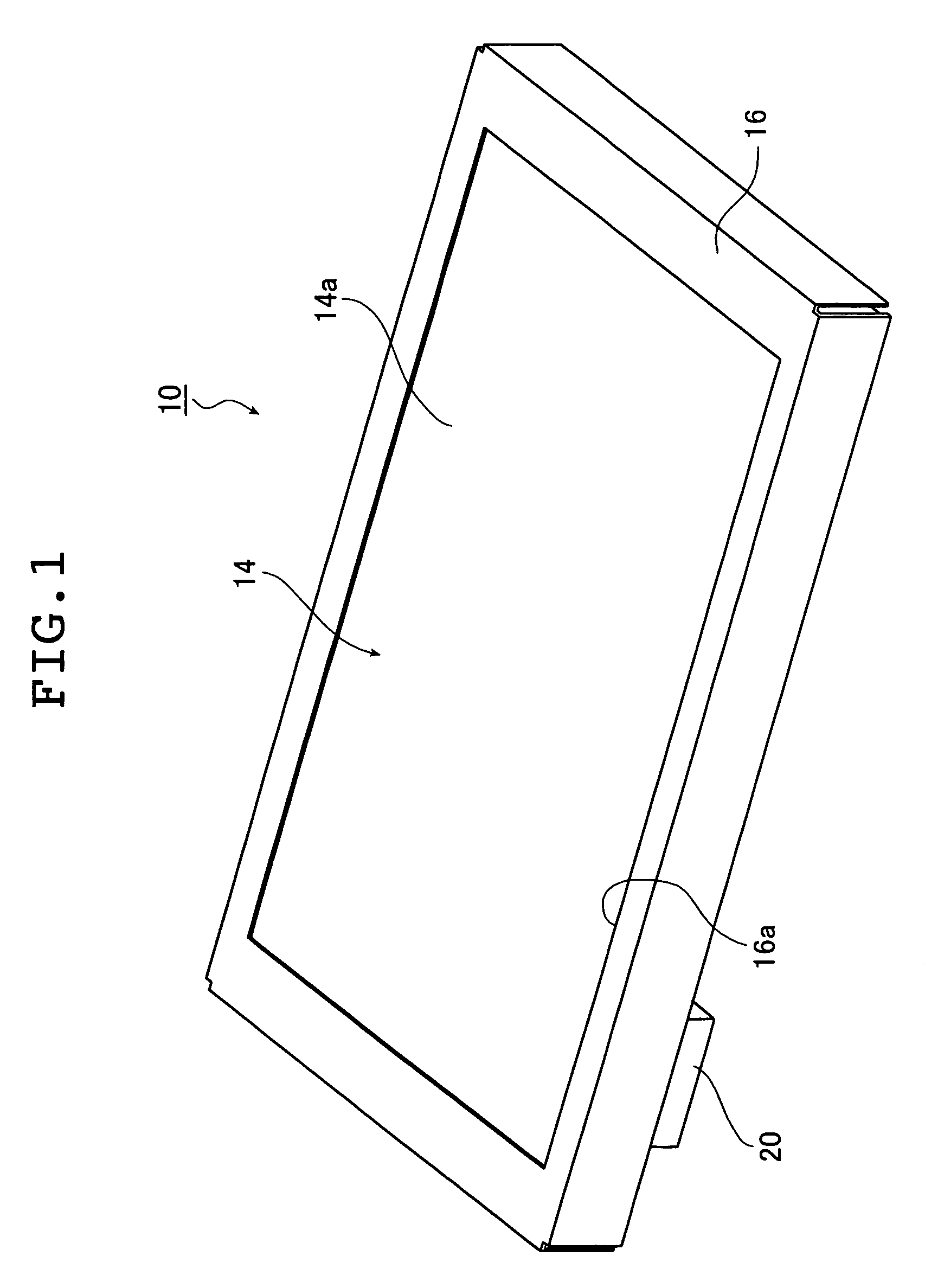

Backlight assembly and display apparatus having the same

ActiveUS20060028839A1Prevent warpagePreventing cleavageElectric lightingIlluminated signsLight guideLight reflection

A backlight assembly includes a receiving container, a light guide plate, a light source unit, an optical member and a panel-guiding member. The receiving container includes a bottom plate and a sidewall extended from an edge portion of the bottom plate. The light source unit includes a light source generating light and disposed at side face of the light guide plate, and a light reflecting cover that covers the light source to reflect the light generated from the light source toward the side face. The optical member is disposed over the light guide plate. The panel-guiding member has a first plate combined with the sidewall of the receiving container, and a second plate extended from the first plate such that the second plate covers a portion of the optical member and is spaced apart from an upper face of the optical member. Therefore, warpage and cleavage of the optical member are prevented.

Owner:SAMSUNG DISPLAY CO LTD

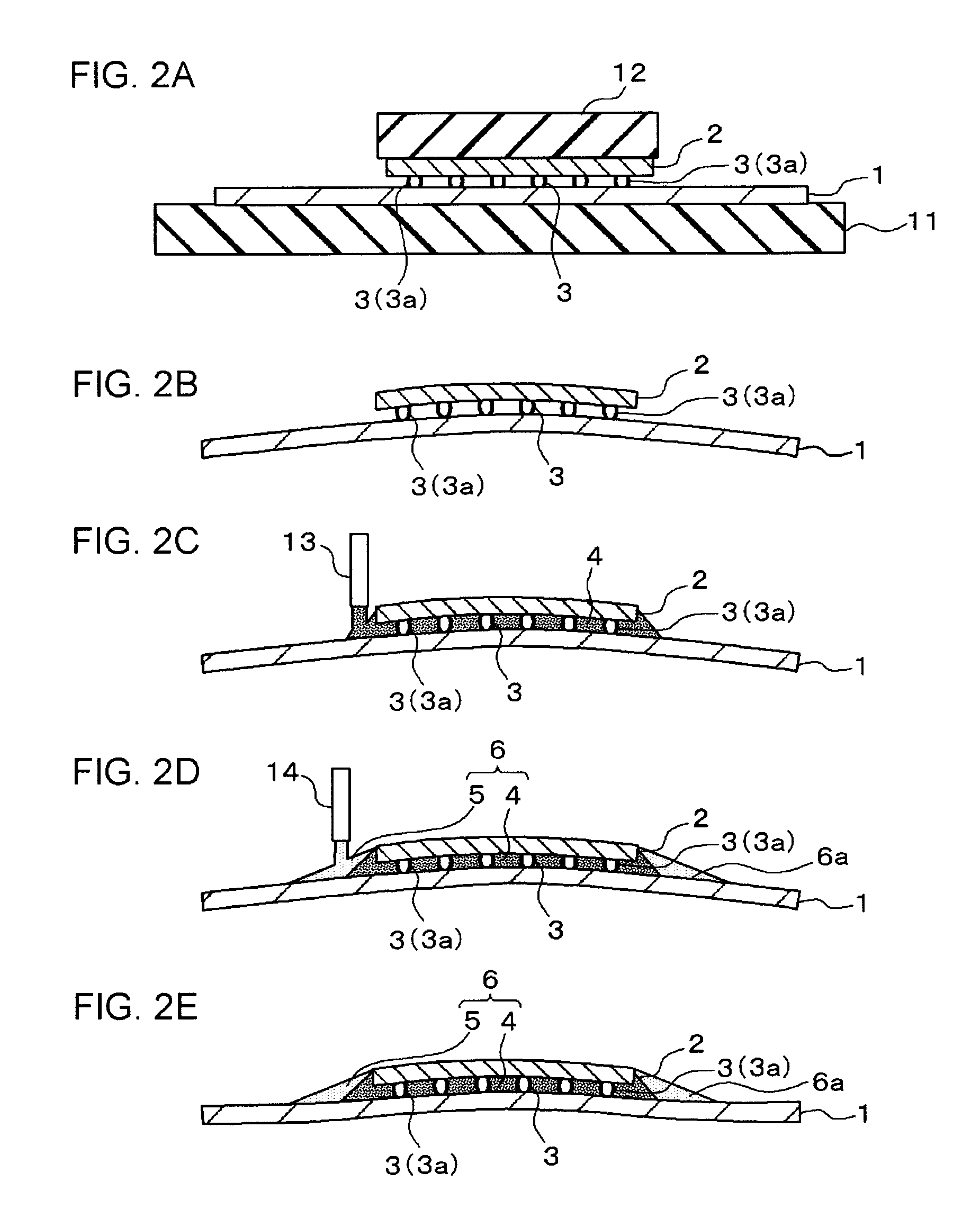

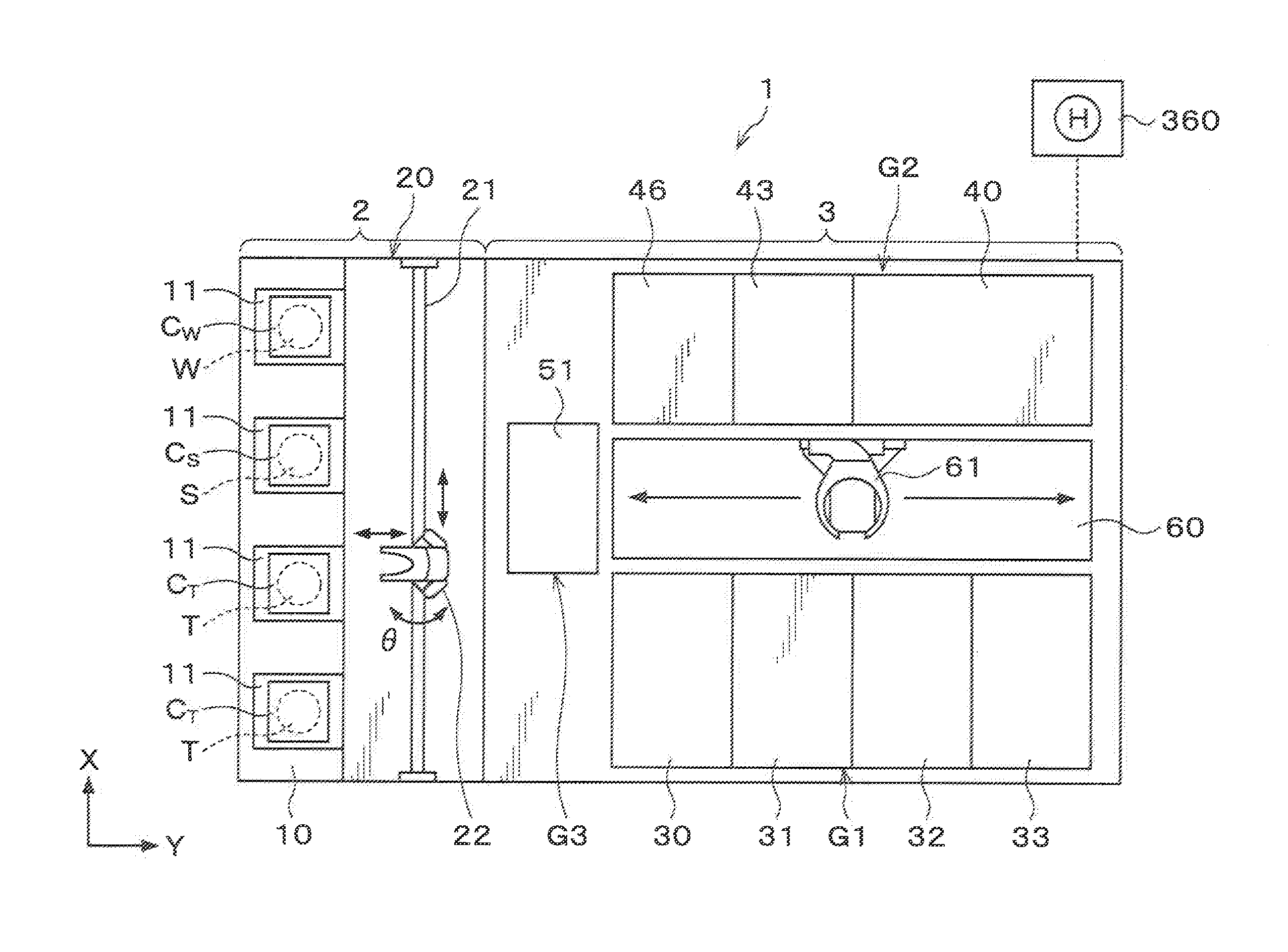

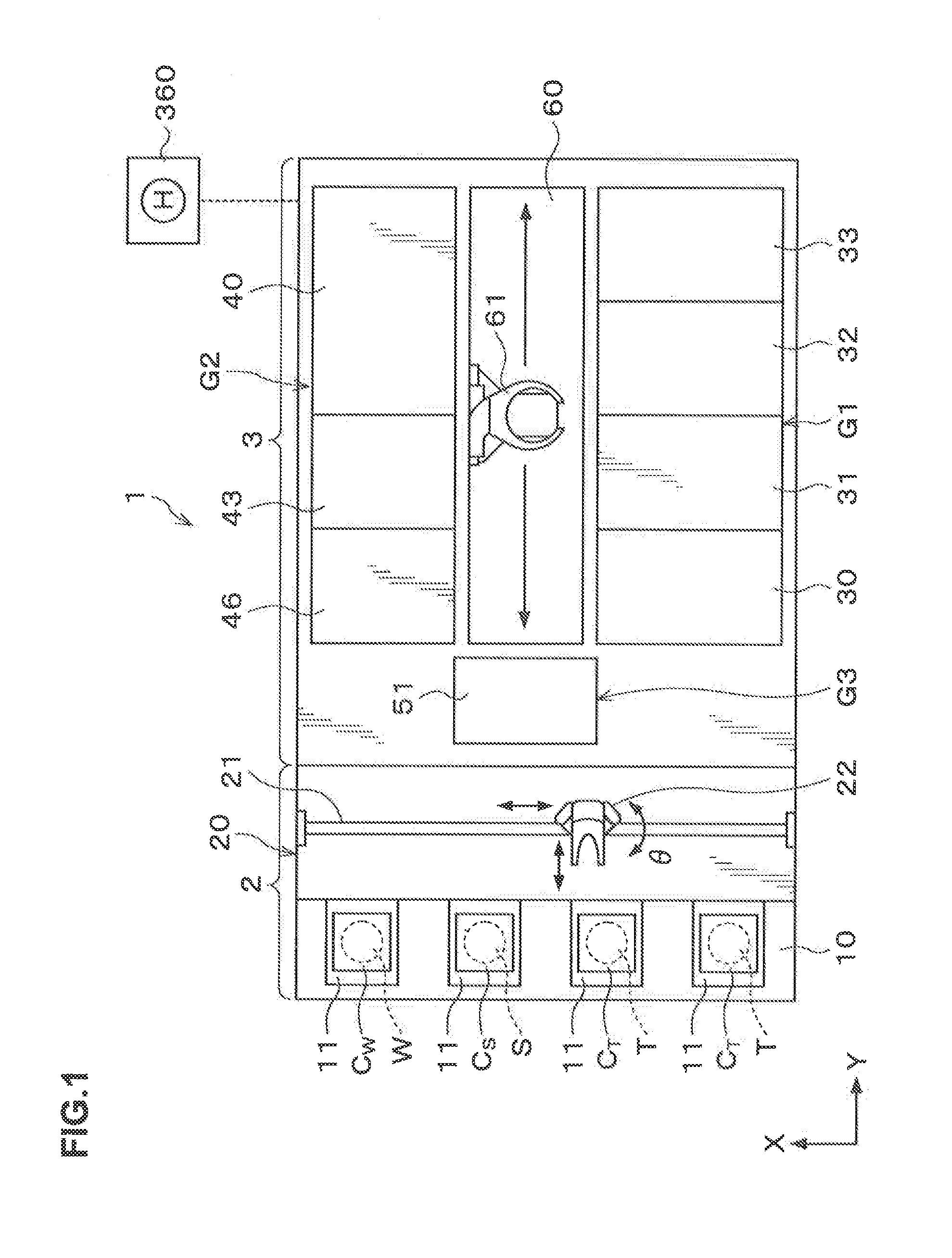

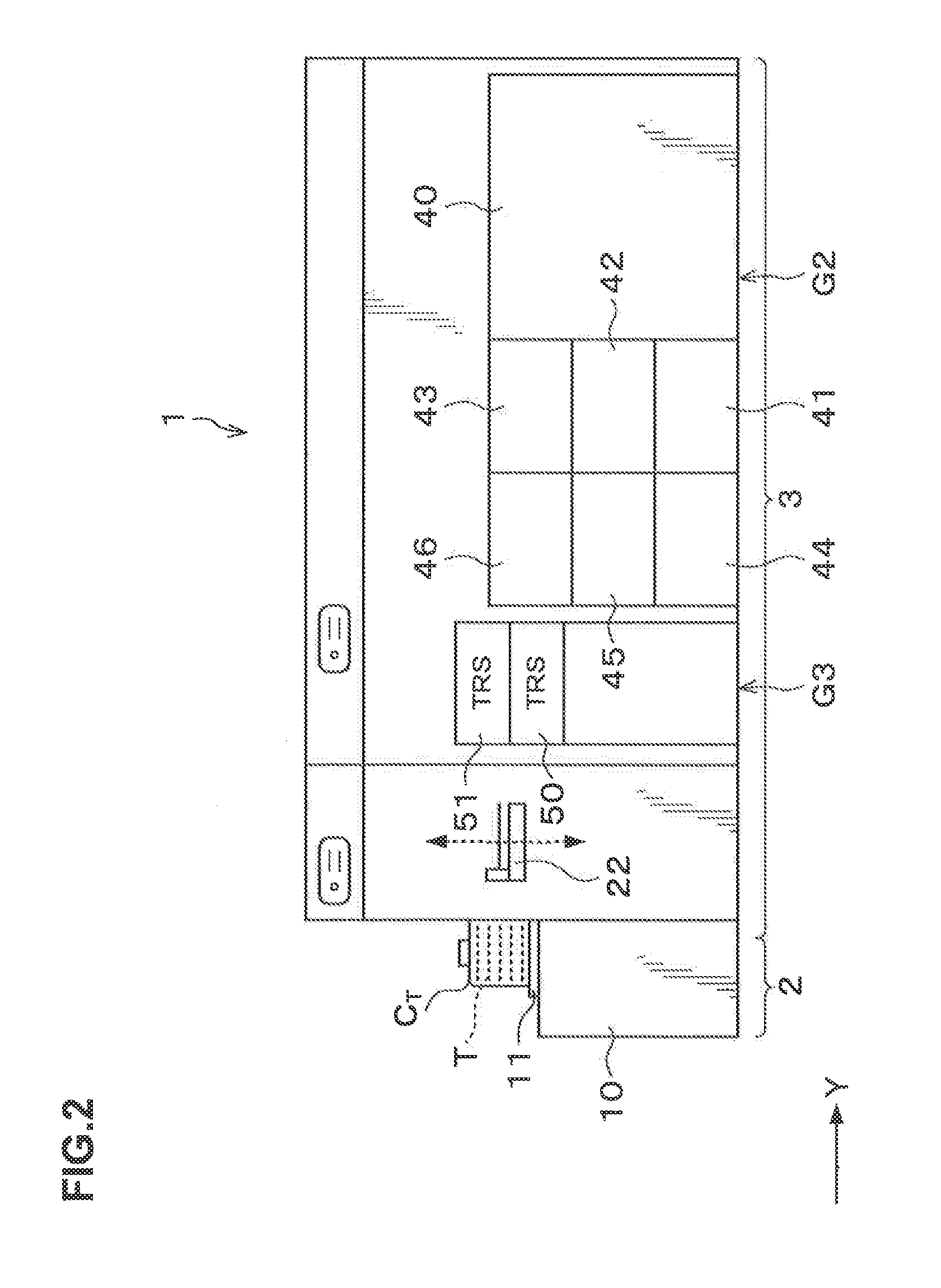

Joint apparatus, joint system, and joint method

InactiveUS20130062013A1Suppression of distortionSuppress occurrenceLaminationAdhesive processes with adhesive heatingAdhesiveEngineering

A joint apparatus that joins a processing target substrate and a supporting substrate together, includes: a processing container that is capable of hermetically closing an inside thereof; a joint unit that joins the processing target substrate and the supporting substrate together by pressing the processing target substrate and the supporting substrate via an adhesive; and a superposed substrate temperature regulation unit that temperature-regulates a superposed substrate joined in the joint unit, wherein the joint unit and the superposed substrate temperature regulation unit are arranged in the processing container, A delivery unit for delivering the processing target substrate, the supporting substrate, or the superposed substrate to / from an outside of the processing container is provided in the processing container, and the superposed substrate temperature regulation unit is provided in the delivery unit.

Owner:TOKYO ELECTRON LTD

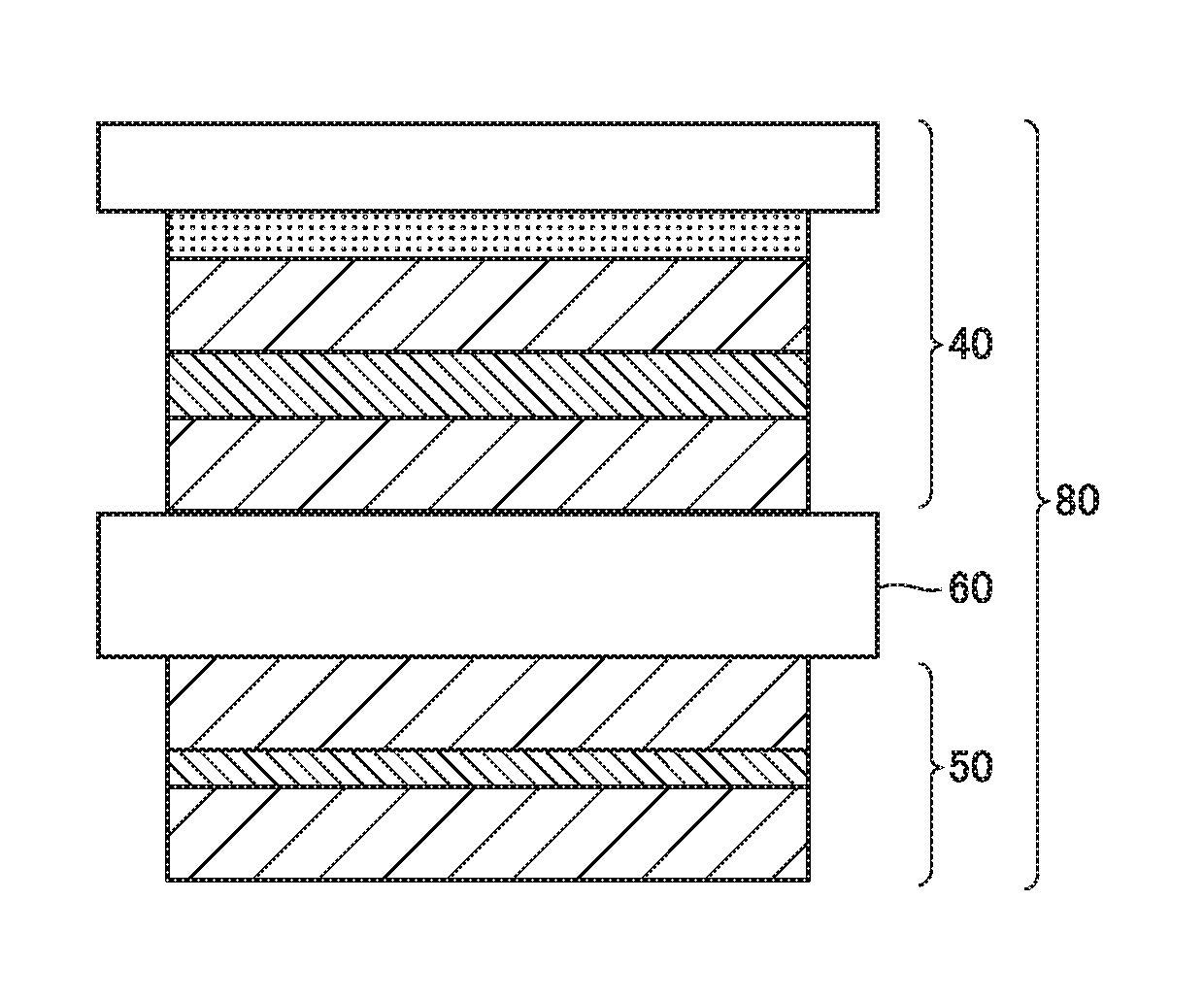

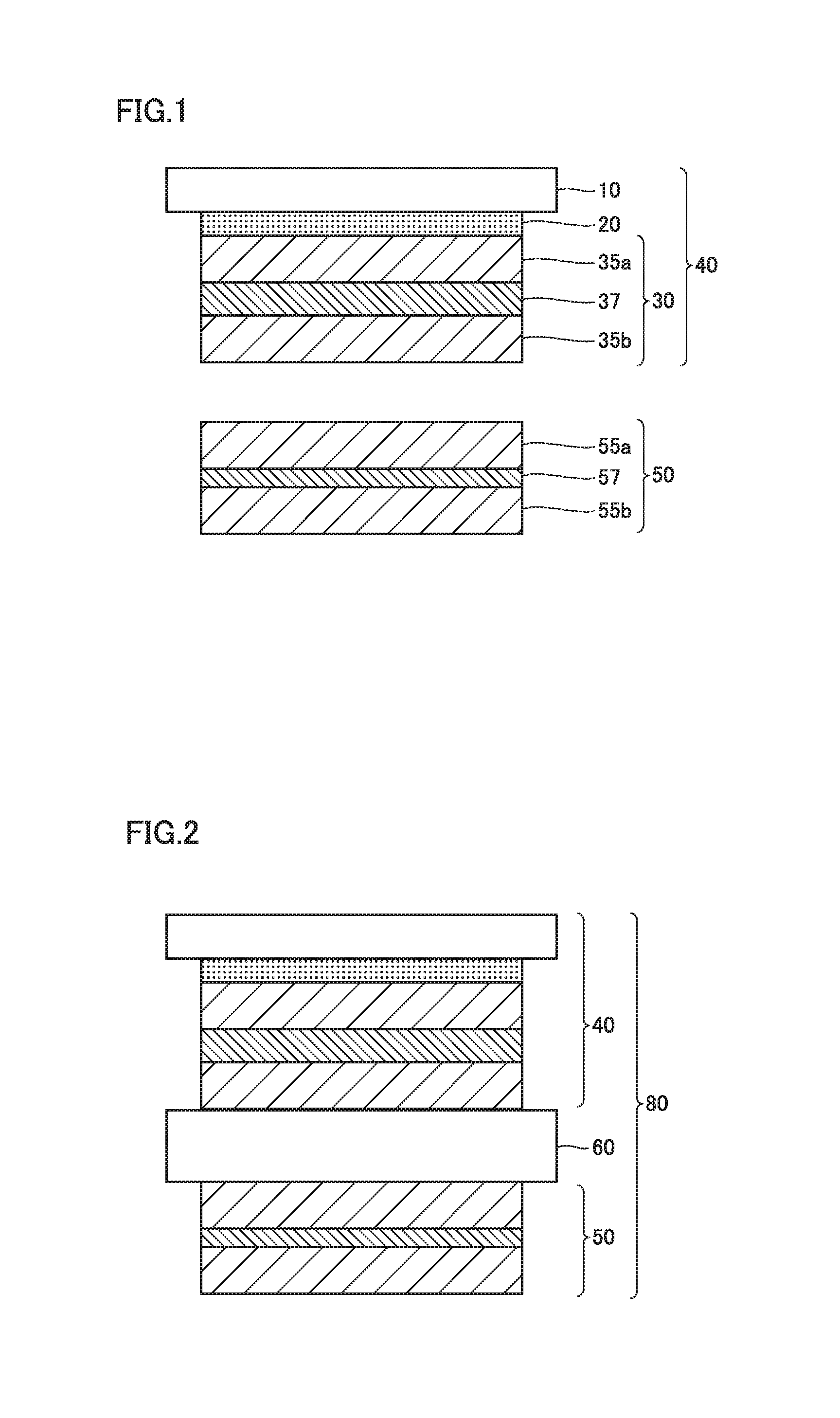

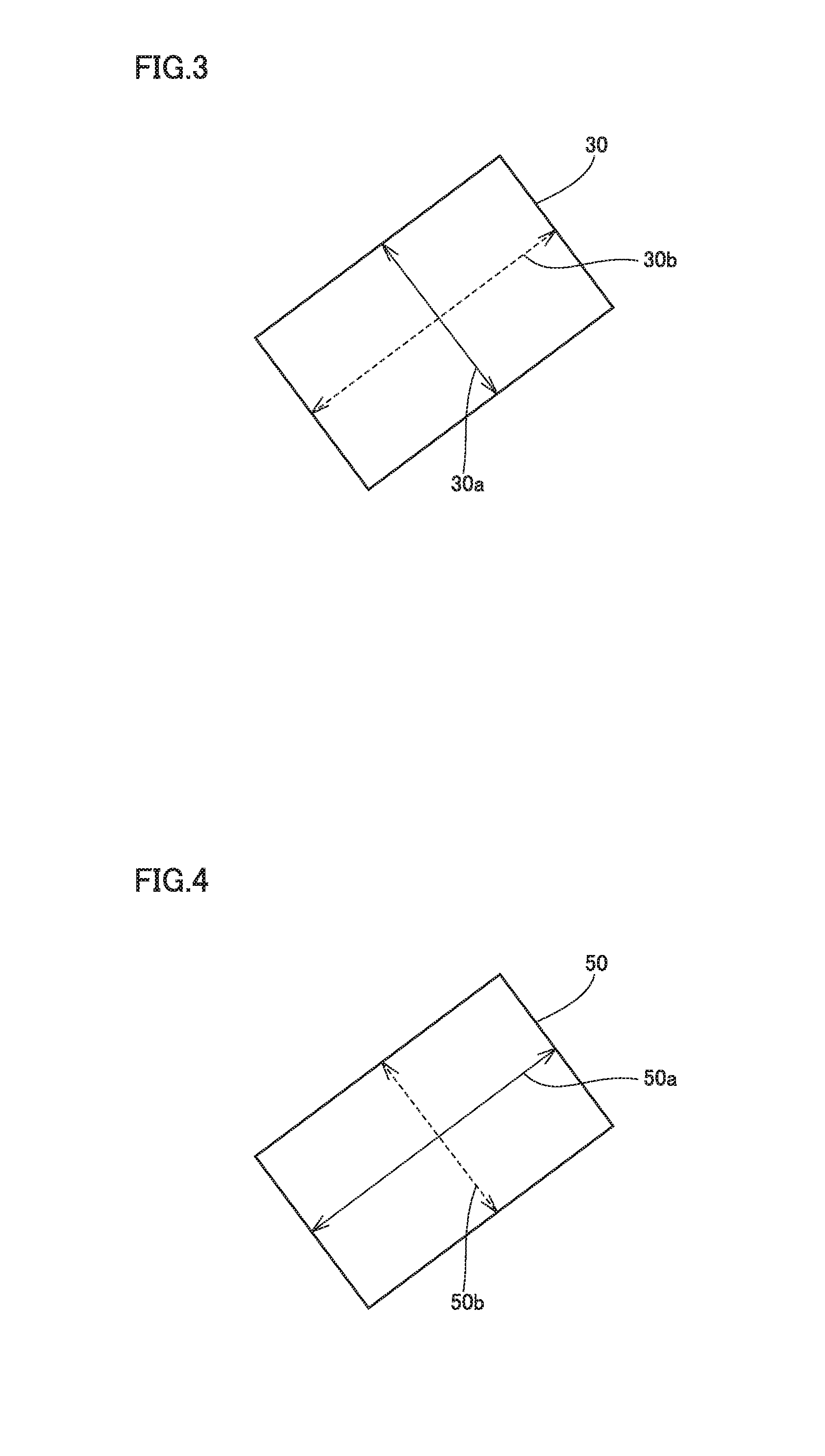

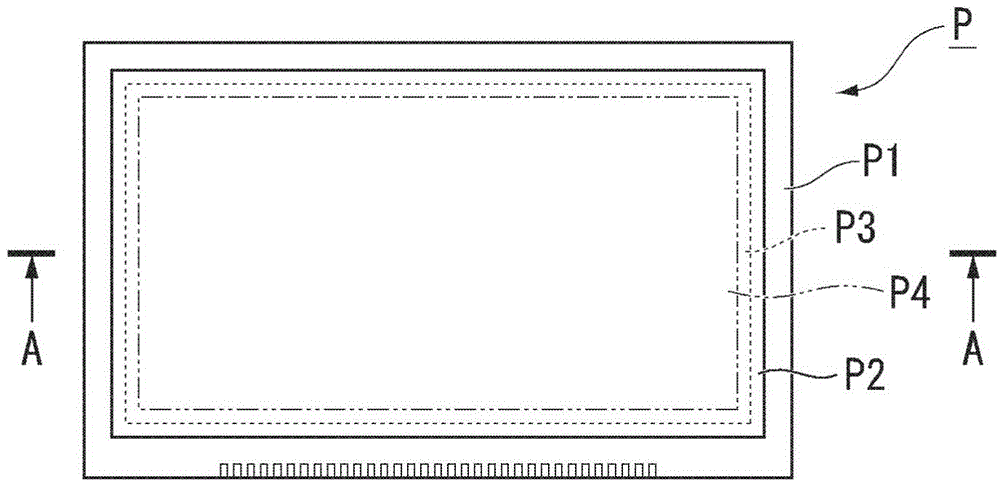

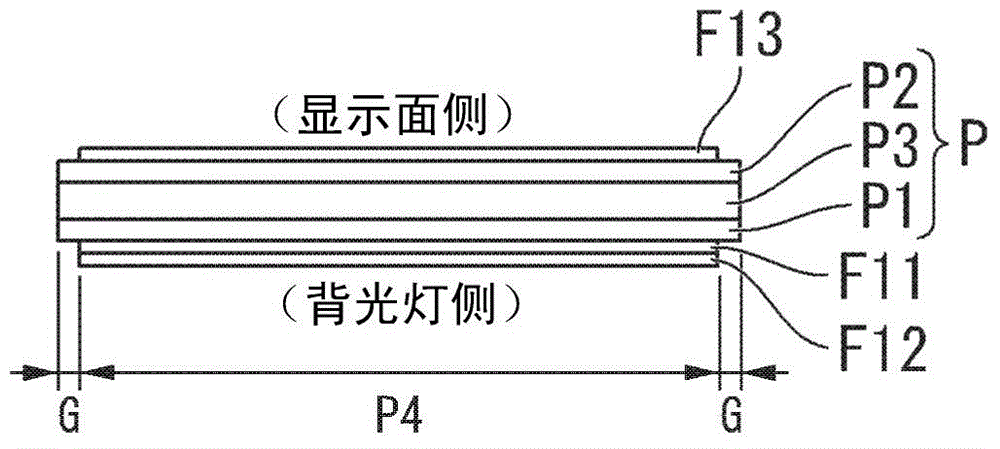

Set of polarizing plates and front-plate-integrated liquid crystal display panel

ActiveUS20160252774A1Prevent warpageConvenient to accommodatePolarising elementsNon-linear opticsYoung's modulusPolarizer

Provided is a set of polarizing plates comprising a front-plate-integrated polarizing plate to be disposed at a viewing side of a liquid crystal cell and a back-side polarizing plate to be disposed at a back side of the cell. The front-plate-integrated polarizing plate includes a front-side polarizing plate and a front plate having a Young's modulus of 2 GPa or more. The set of polarizing plates satisfies the formula: (Ra−Ft)<(Fa−Rt), where Fa and Ft represent ratios of dimensional change observed in the front-side polarizing plate in absorption and transmission axis directions, respectively, after the front-side polarizing plate is heated at 85° C. for 100 hours, and Ra and Rt represent ratios of dimensional change observed in the back-side polarizing plate in absorption and transmission axis directions, respectively, after the back-side polarizing plate is heated at 85° C. for 100 hours.

Owner:SUMITOMO CHEM CO LTD

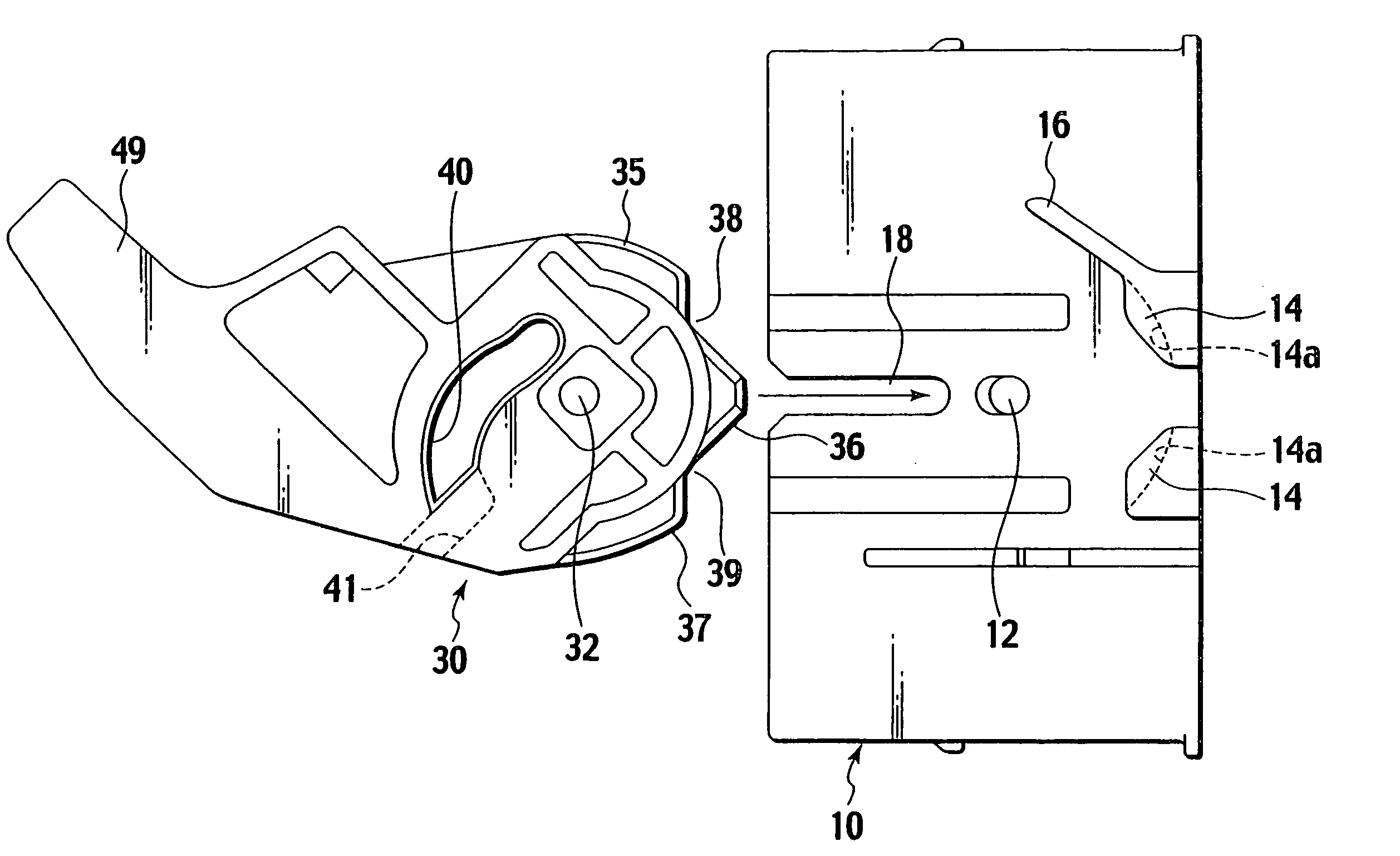

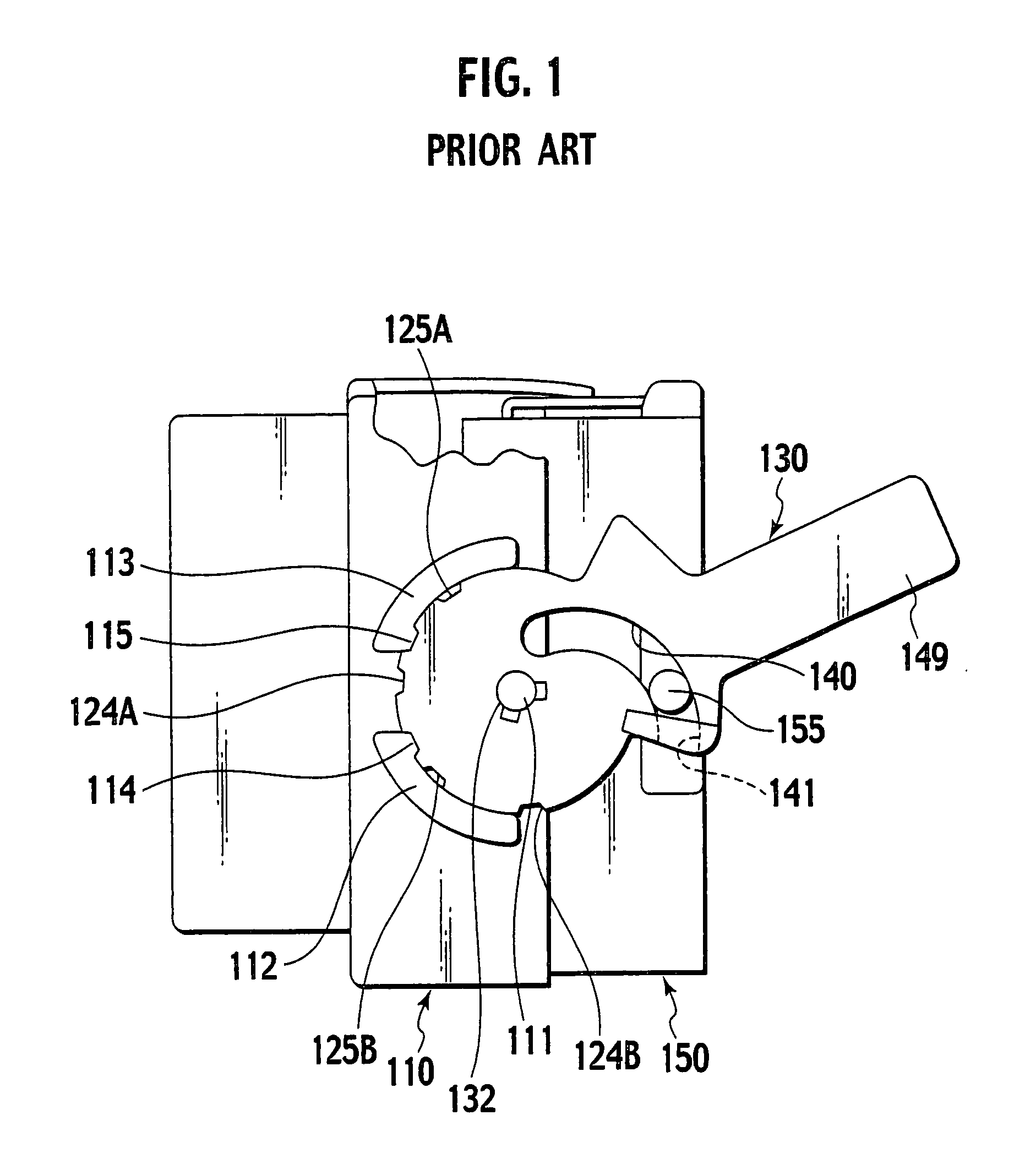

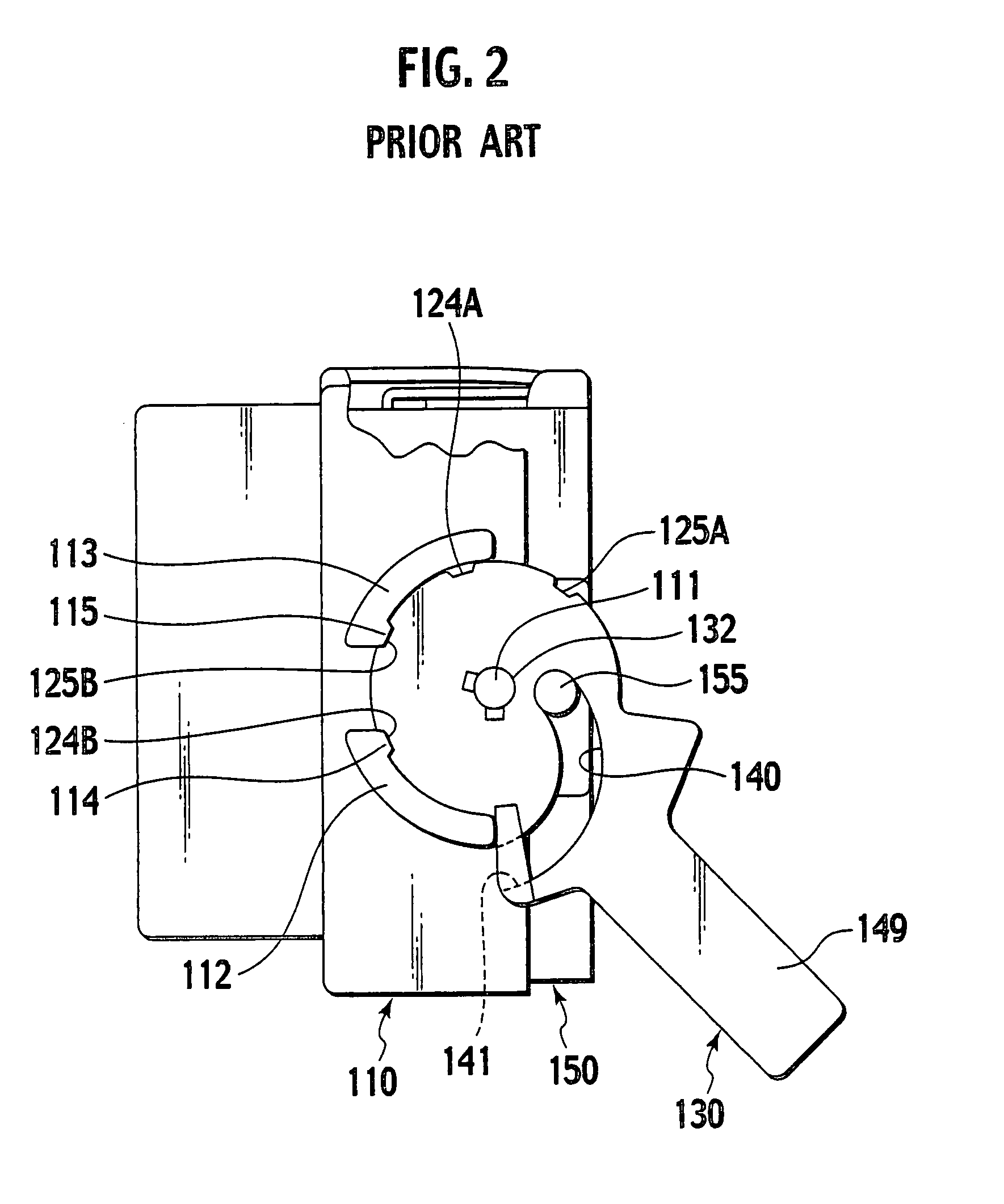

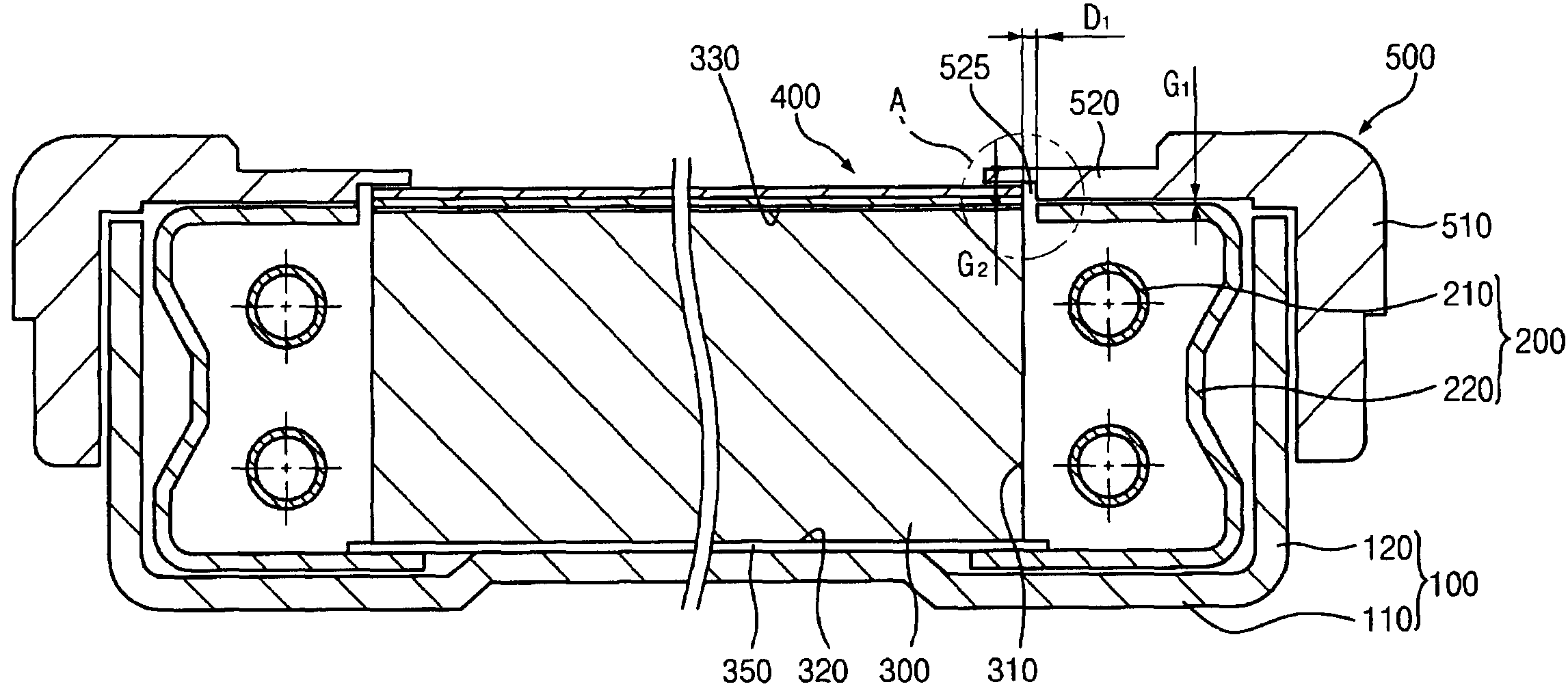

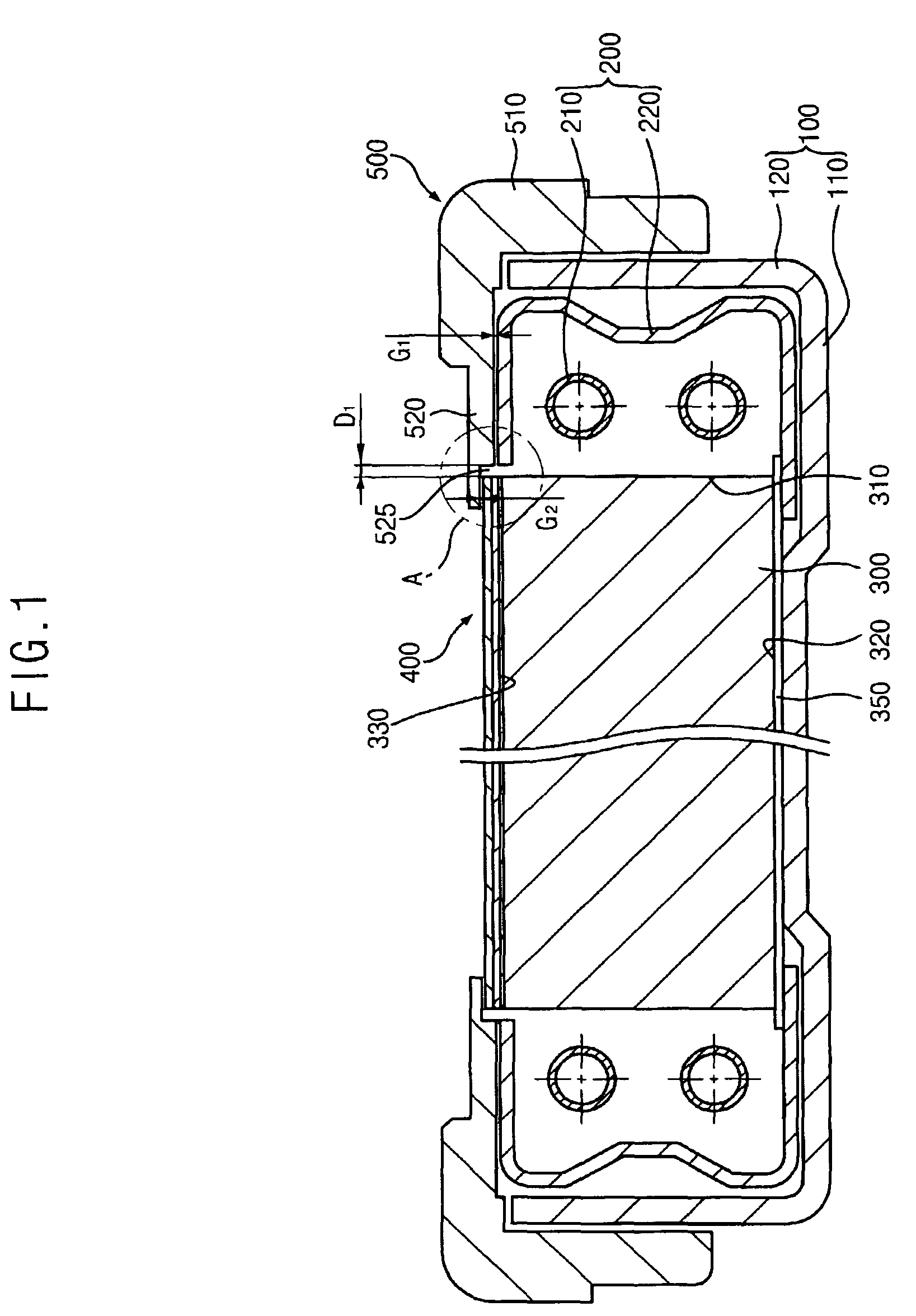

Lever type connector

ActiveUS20070202722A1Avoid deformationPrevent warpageEngagement/disengagement of coupling partsIncorrect coupling preventionMechanical engineeringEngineering

Owner:YAZAKI CORP +1

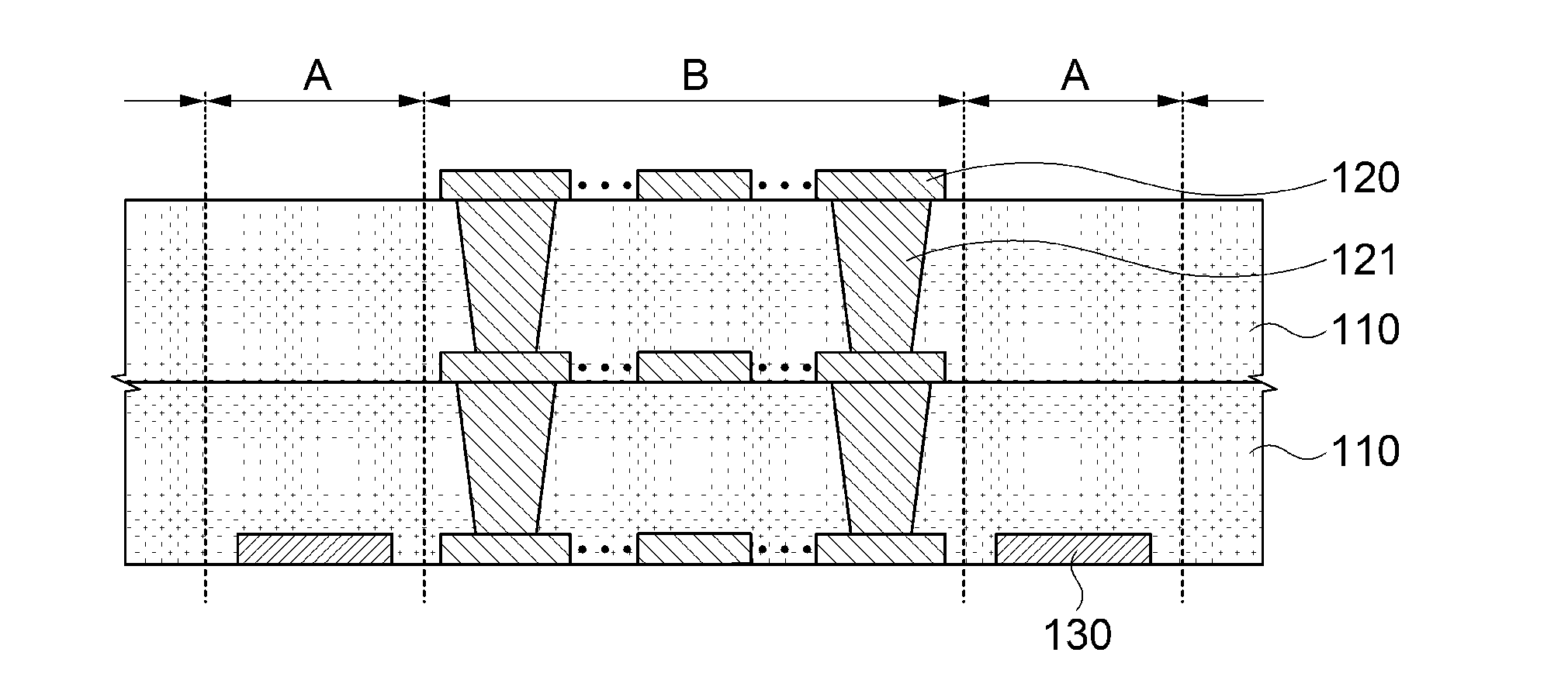

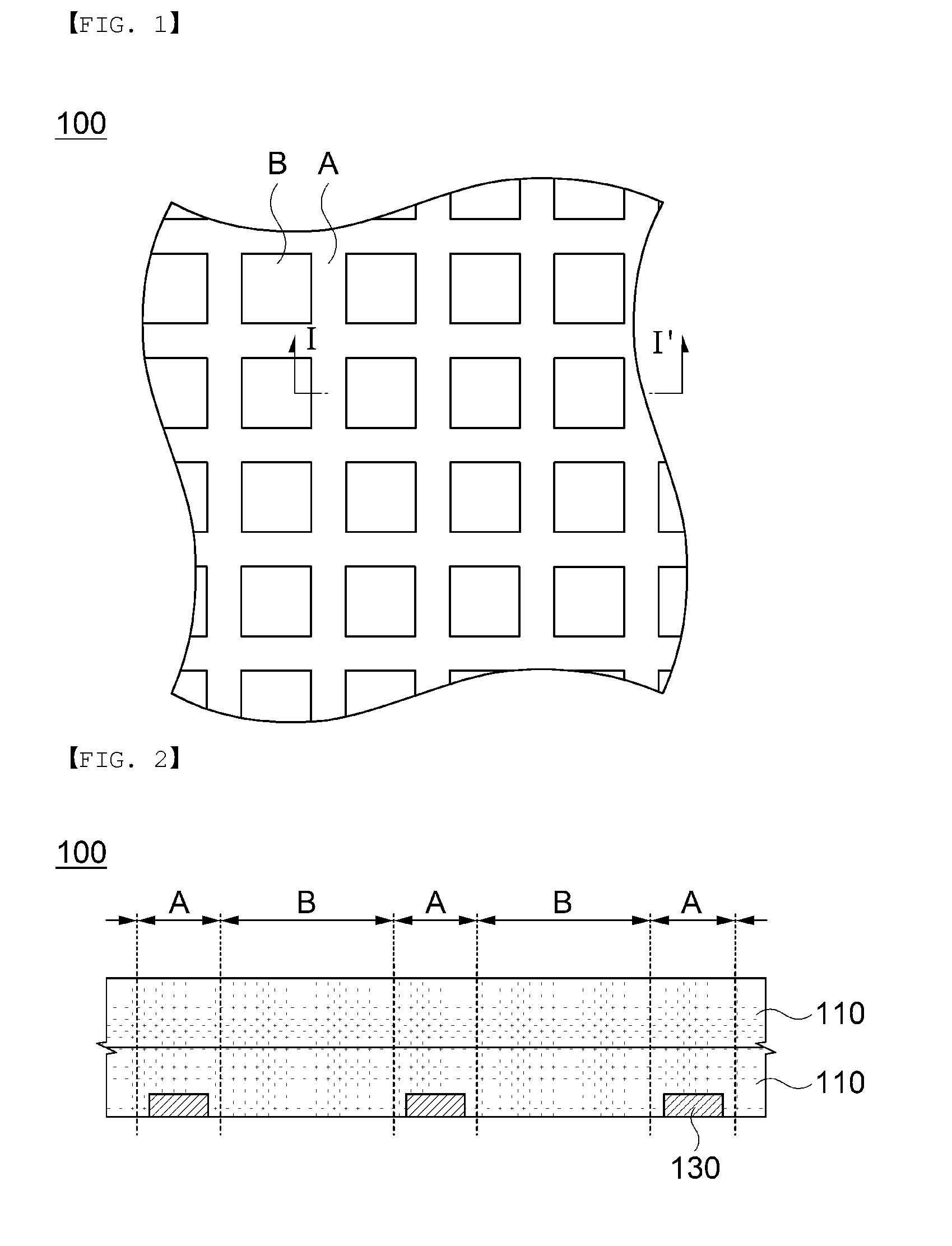

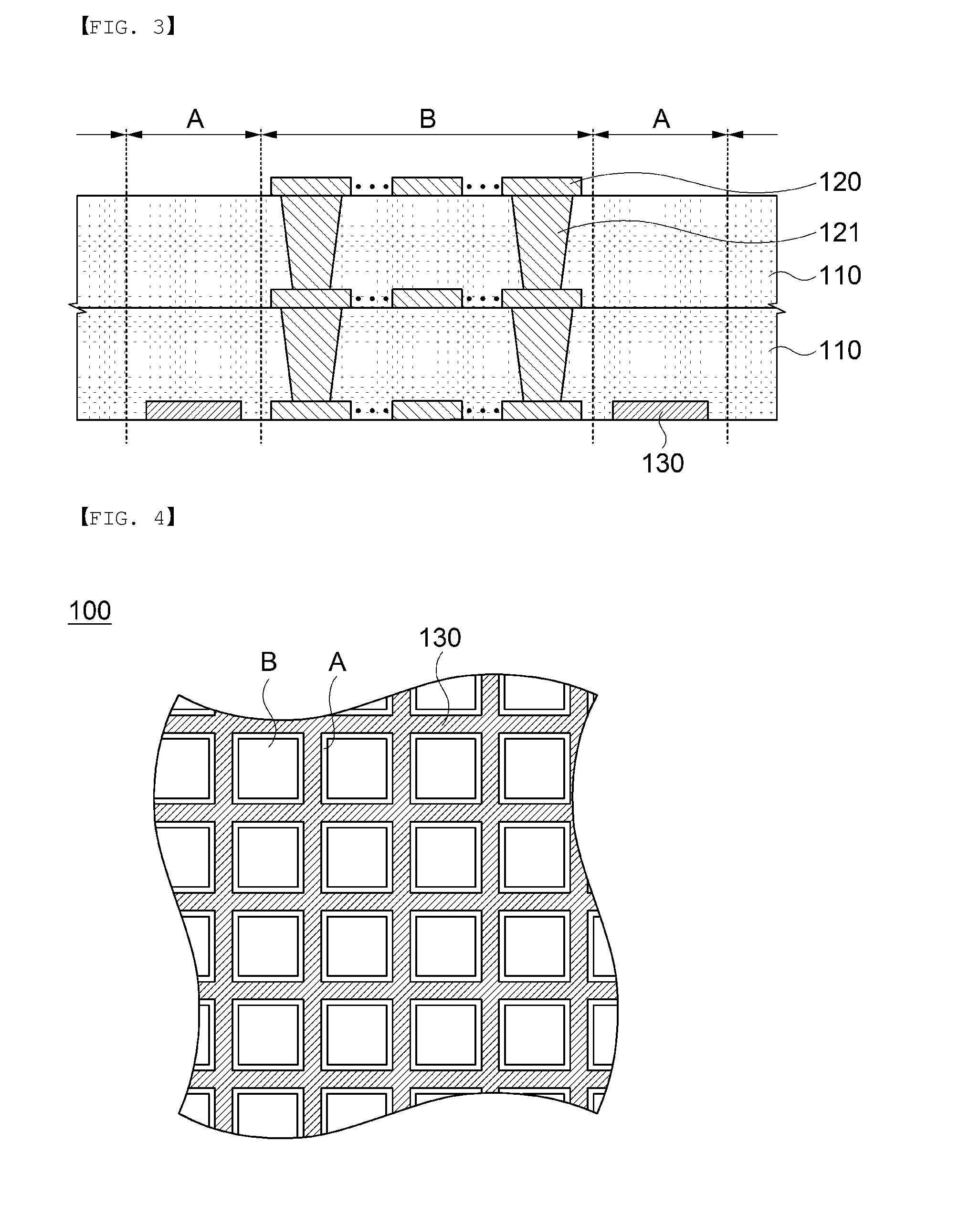

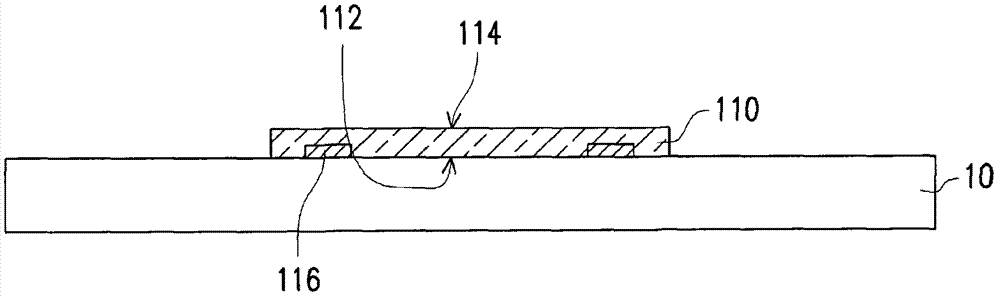

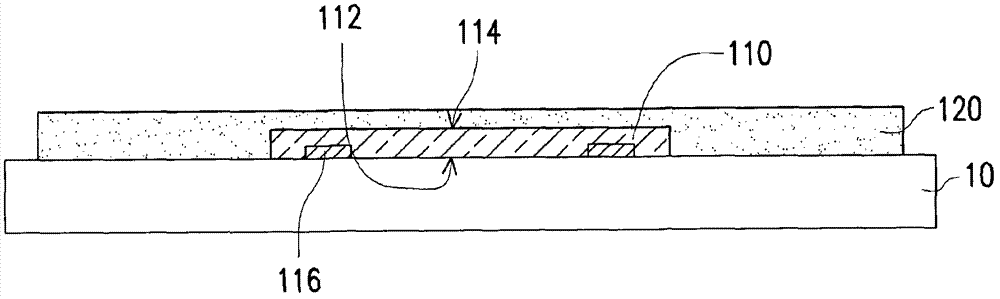

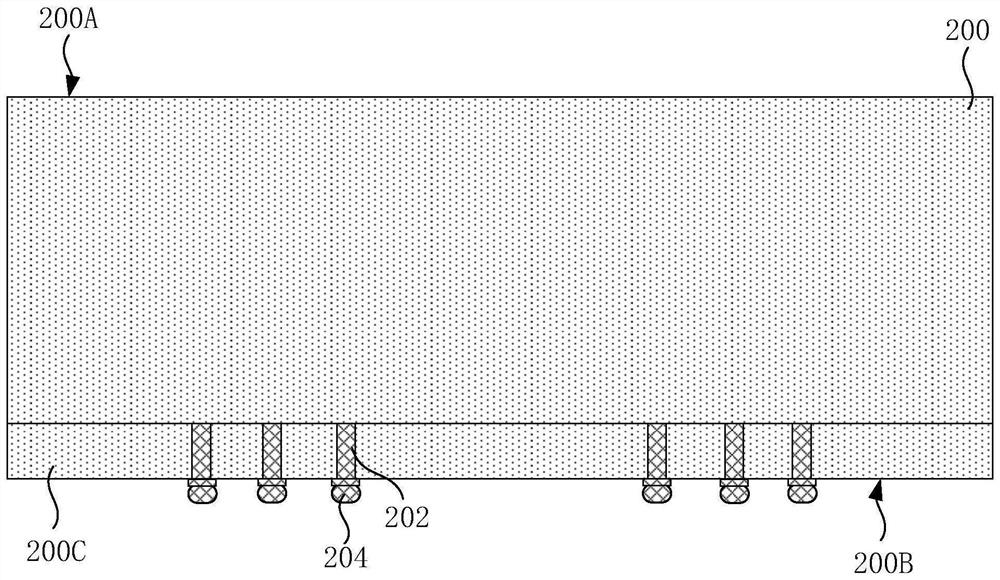

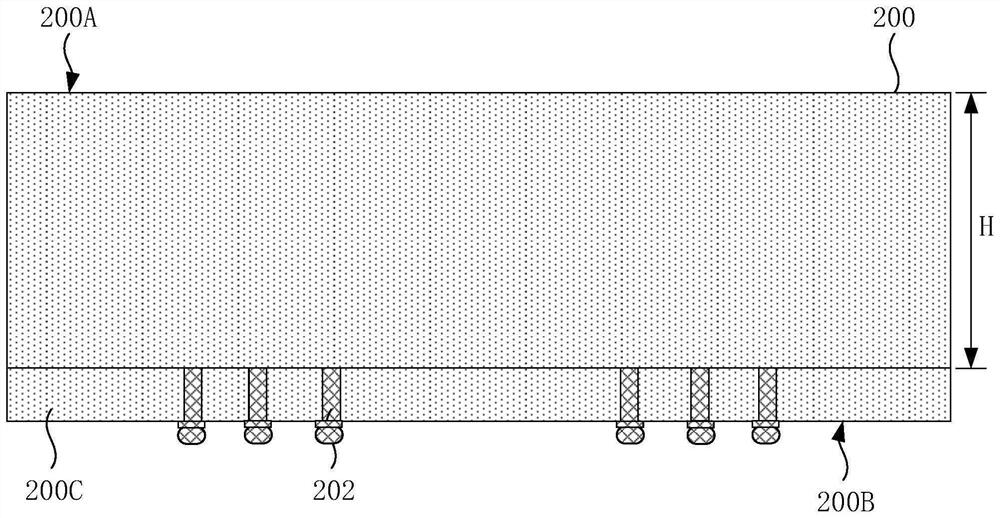

Strip level substrate including warpage preventing member and method of manufacturing the same

InactiveUS20150156877A1Prevent warpageAvoid warpingDielectric materialsPrinted circuits stress/warp reductionEngineeringElectrical and Electronics engineering

Disclosed herein is a strip level substrate having a plurality of unit level substrate regions partitioned by unit saw lines, including: a plurality of wiring layers and a plurality of insulating layers that are alternately stacked; and warpage preventing members disposed in unit saw line regions of an insulating layer bonded to a carrier member among the plurality of insulating layers, in order to improve warpage characteristics of the strip level substrate.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Backlight assembly and display apparatus having the same

ActiveUS7758231B2Prevent warpagePreventing cleavageElectric lightingOptical light guidesLight guideOptoelectronics

A backlight assembly includes a receiving container, a light guide plate, a light source unit, an optical member and a panel-guiding member. The receiving container includes a bottom plate and a sidewall extended from an edge portion of the bottom plate. The light source unit includes a light source generating light and disposed at side face of the light guide plate, and a light reflecting cover that covers the light source to reflect the light generated from the light source toward the side face. The optical member is disposed over the light guide plate. The panel-guiding member has a first plate combined with the sidewall of the receiving container, and a second plate extended from the first plate such that the second plate covers a portion of the optical member and is spaced apart from an upper face of the optical member. Therefore, warpage and cleavage of the optical member are prevented.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor package structure and manufacturing method thereof

ActiveCN102956511ASimple processImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSolder ball

A method of manufacturing a semiconductor package structure is provided, comprising the steps that a chip is provided; an active surface of the chip is disposed on a carrier; a molding compound is formed on the carrier with a metal layer disposed thereon, the metal layer has an upper and lower surface, multiple cavities formed on the upper surface and multiple protrusions formed on the lower surface and corresponding to the cavities, the protrusions are embedded in the molding compound, the metal layer is patterned to form multiple pads on a portion of the molding compound, the carrier and the molding compound are separated, multiple through holes are formed on the molding compound exposing the protrusions; a redistribution layer is formed on the molding compound and the active surface of the chip; multiple solder balls are formed on the redistribution layer, and a portion of the solder balls are correspondingly disposed to the pads.

Owner:CHIPMOS TECH INC

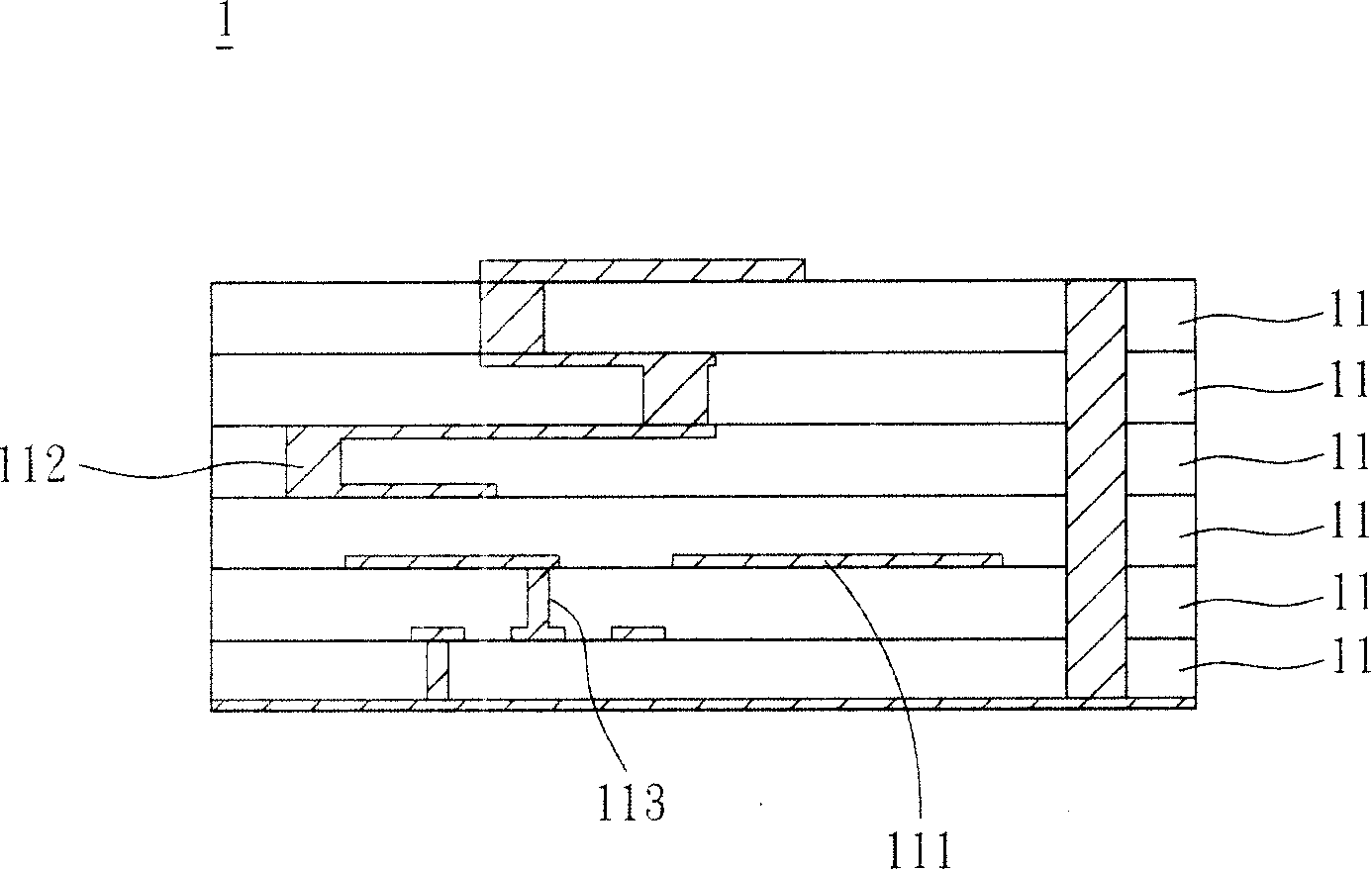

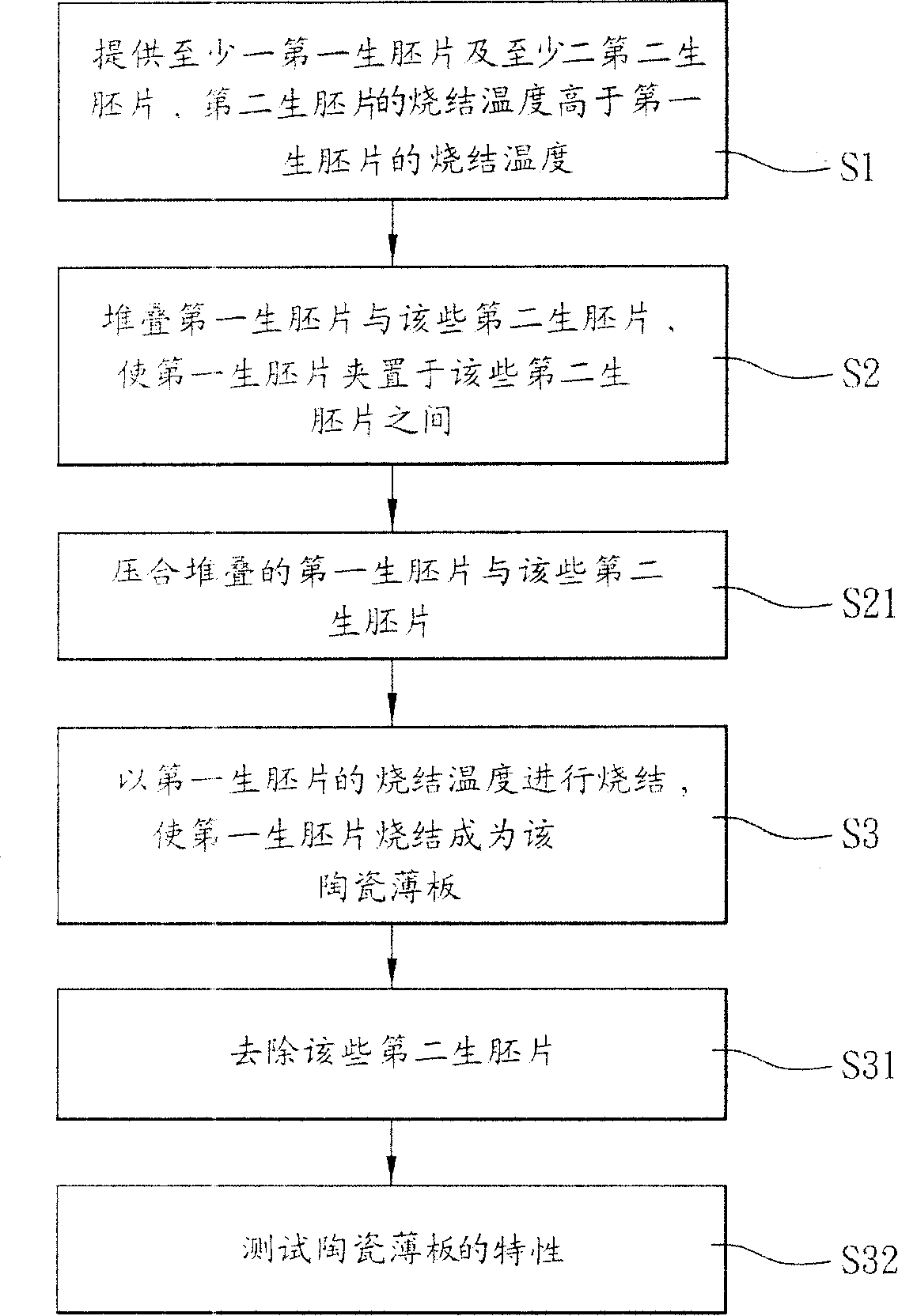

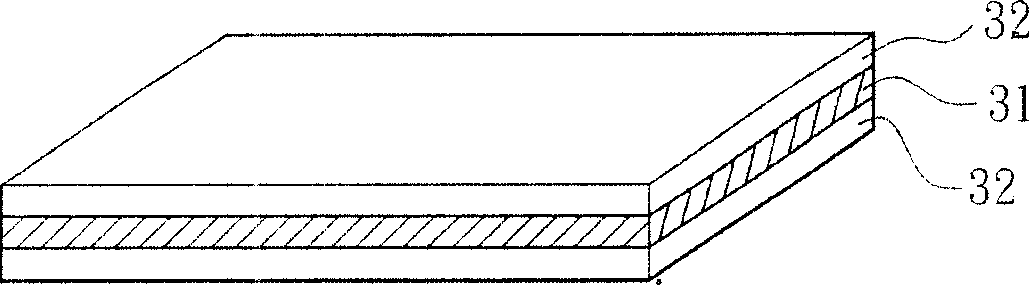

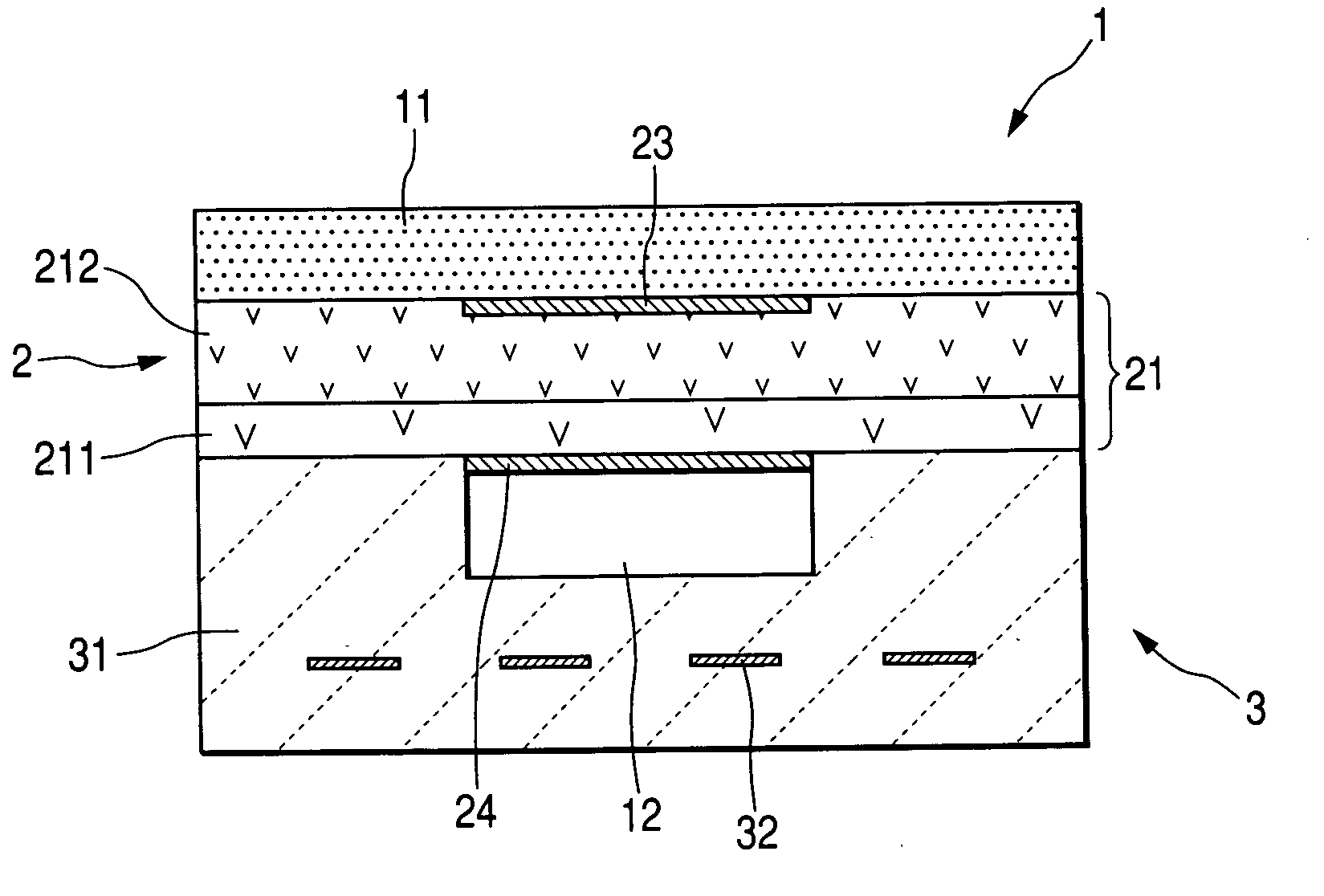

Method for preparing ceramic sheet

InactiveCN101161606AInhibition affects flatnessPrevent warpageCeramic shaping apparatusCeramic layered productsMetallurgyThin sheet

The invention discloses a method for manufacturing ceramic sheets. The method comprises the following steps that: at least one first blank sheet and at least two second blank sheets are provided, and the sintering temperature of the second blank sheets is higher than that of the first blank sheet; the first blank sheet and the second blank sheets are stacked to allow the first blank sheet to be placed among the second blank sheets; the first blank sheet is sintered into a ceramic sheet by the sintering temperature of the first blank sheet.

Owner:DELTA ELECTRONICS INC

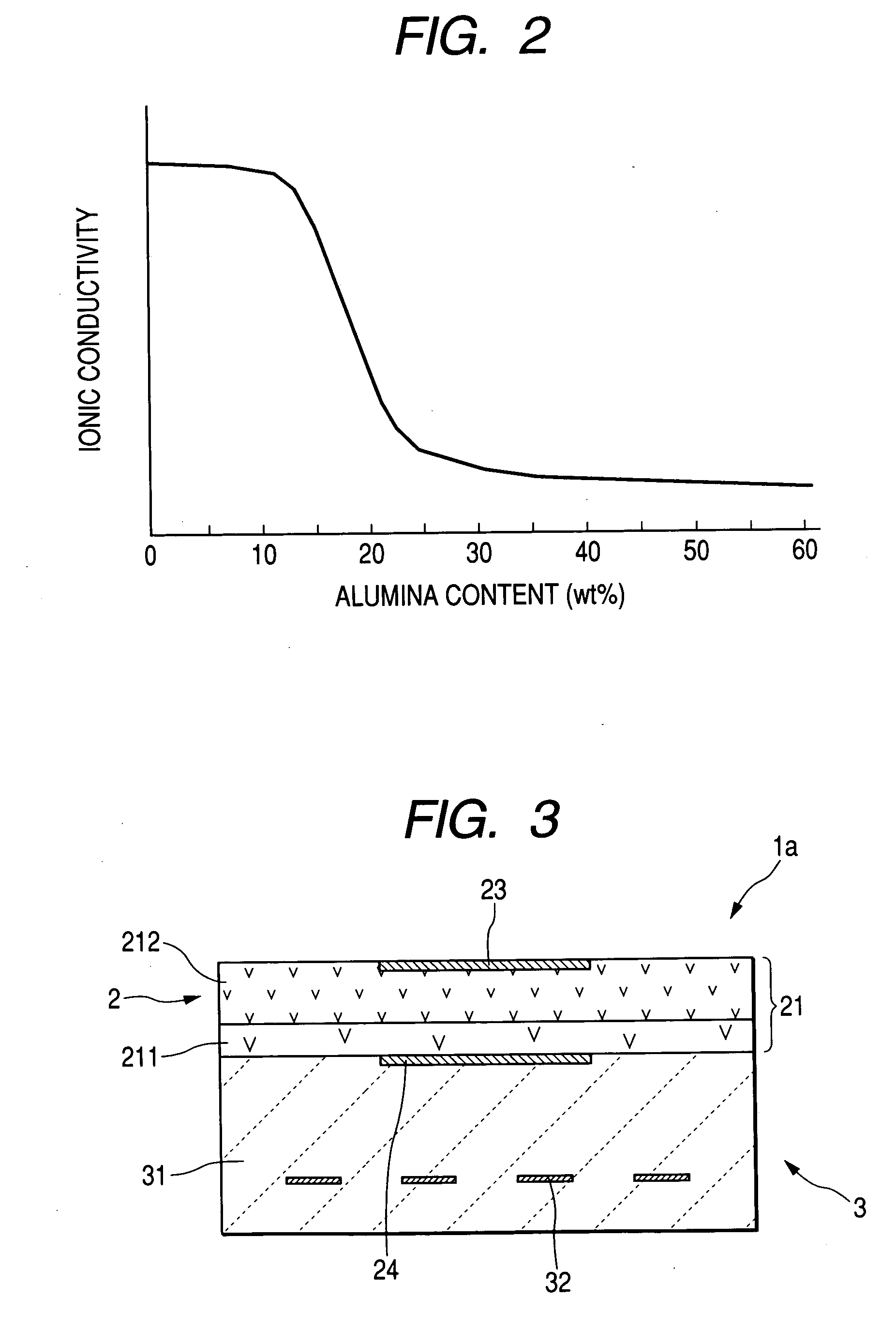

Multilayered gas sensing element

InactiveUS20050230250A1Warpage suppressionReduce the differenceMaterial electrochemical variablesMetallurgyMaterials science

A multilayered gas sensing element includes a sensor cell and a ceramic heater which are integrally laminated. The sensor cell has a solid electrolytic substrate containing an electrolytic component serving as a main component of the ionic conductive solid electrolyte. The ceramic heater has a heater substrate containing the insulating ceramic as a main component. The solid electrolytic substrate includes a first electrolytic layer containing the insulating ceramic at a position closest to the ceramic heater, and a second electrolytic layer whose insulating ceramic content is smaller than that of the first electrolytic layer.

Owner:DENSO CORP

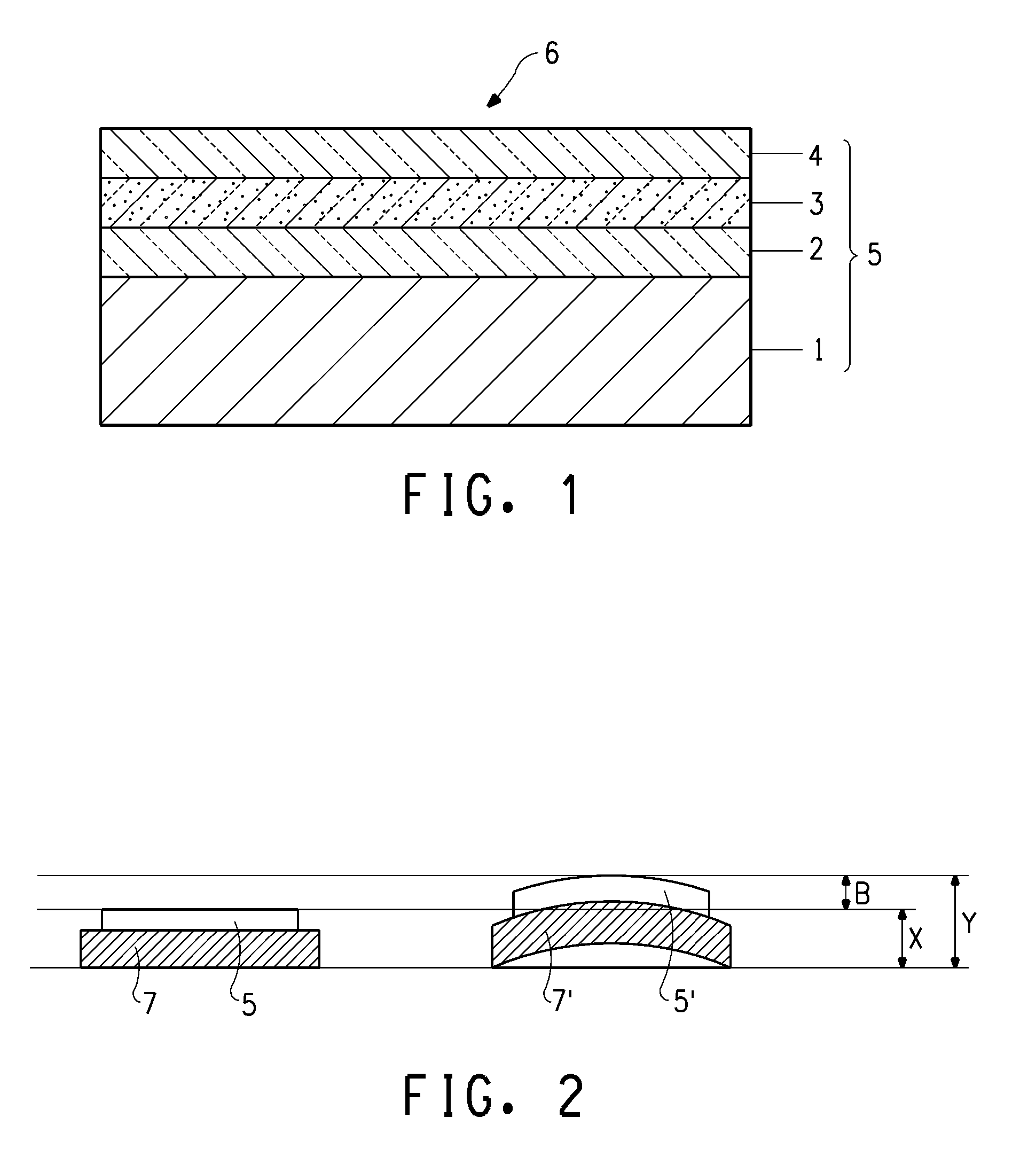

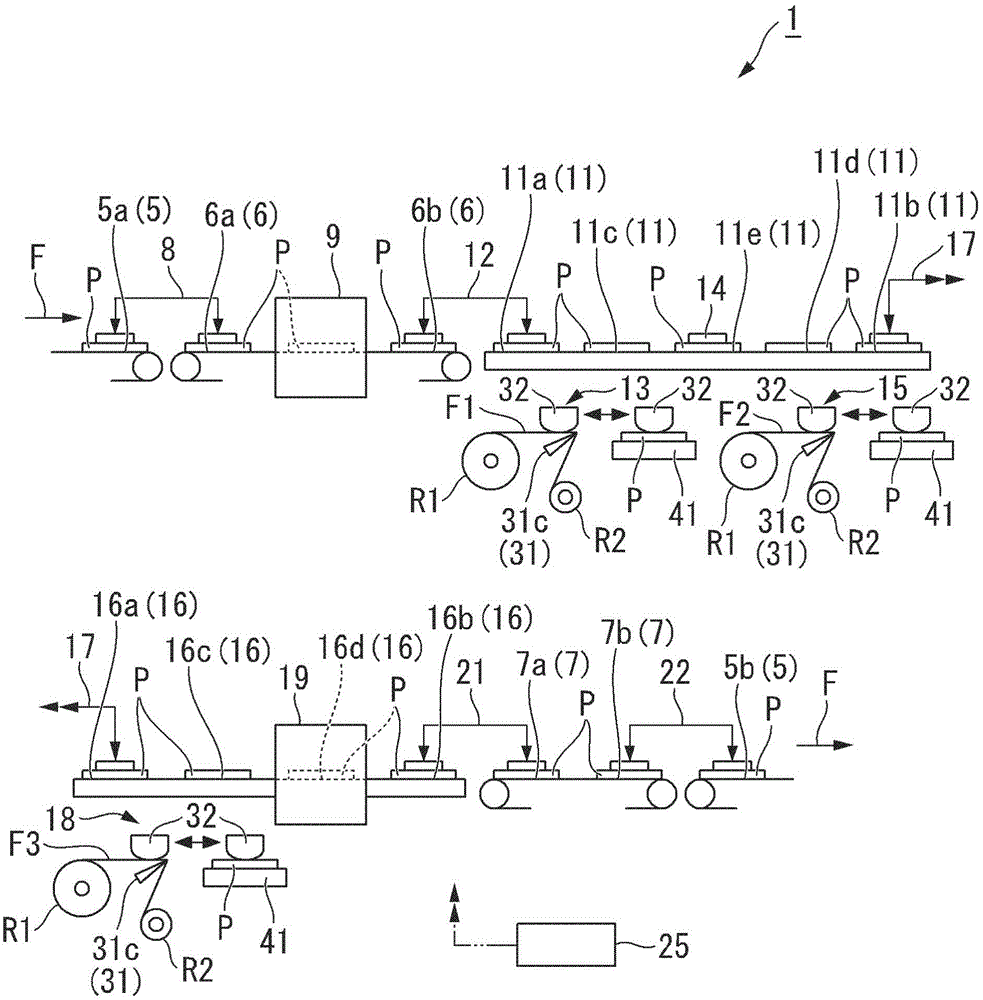

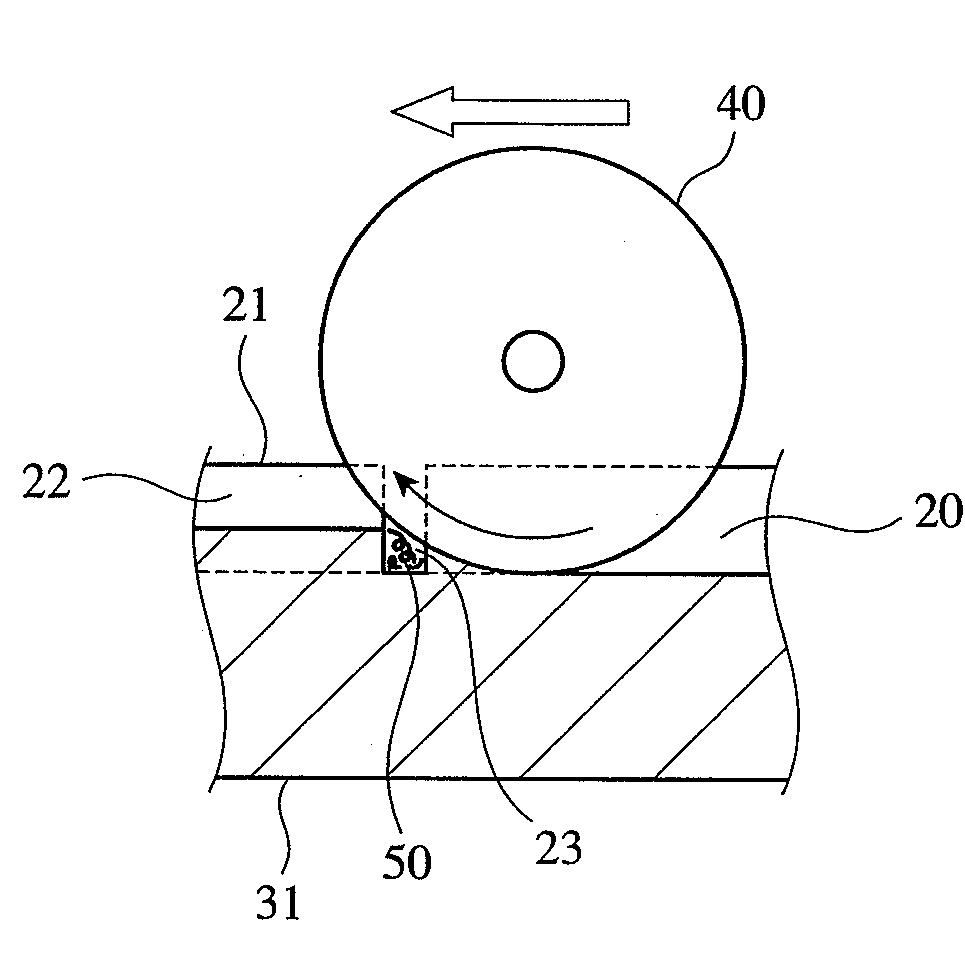

System and method for producing optical display devices

ActiveCN104969281ASuppress size deviationSuppress fit deviationLayered productsElectrical equipmentEngineeringMethods of production

This system for producing optical display devices is provided with a laminating device which, for a plurality of optical display components (P) transported on a line, unwinds a belt-shaped optical member sheet (F1) having a width corresponding to the display area of the optical display components from a whole-sheet roll (R1), and, while so doing, cuts the optical member sheet to a length corresponding to the display region to obtain an optical member (F11), and then laminates the optical member onto the optical display component. The laminating device has: a laminating head (32) whereby the optical member held in place by being pasted to an arc-shaped holding surface (32a) is laminated onto the optical display component; a movement device (44) for moving the laminating head and the optical display component relative to each other during lamination of the optical member; and a drive device (42) for driving the laminating head so that the laminating head is tilted along the curve of the holding surface during lamination of the optical member, the laminating head pressing the optical member against the optical display component.

Owner:SUMITOMO CHEM CO LTD

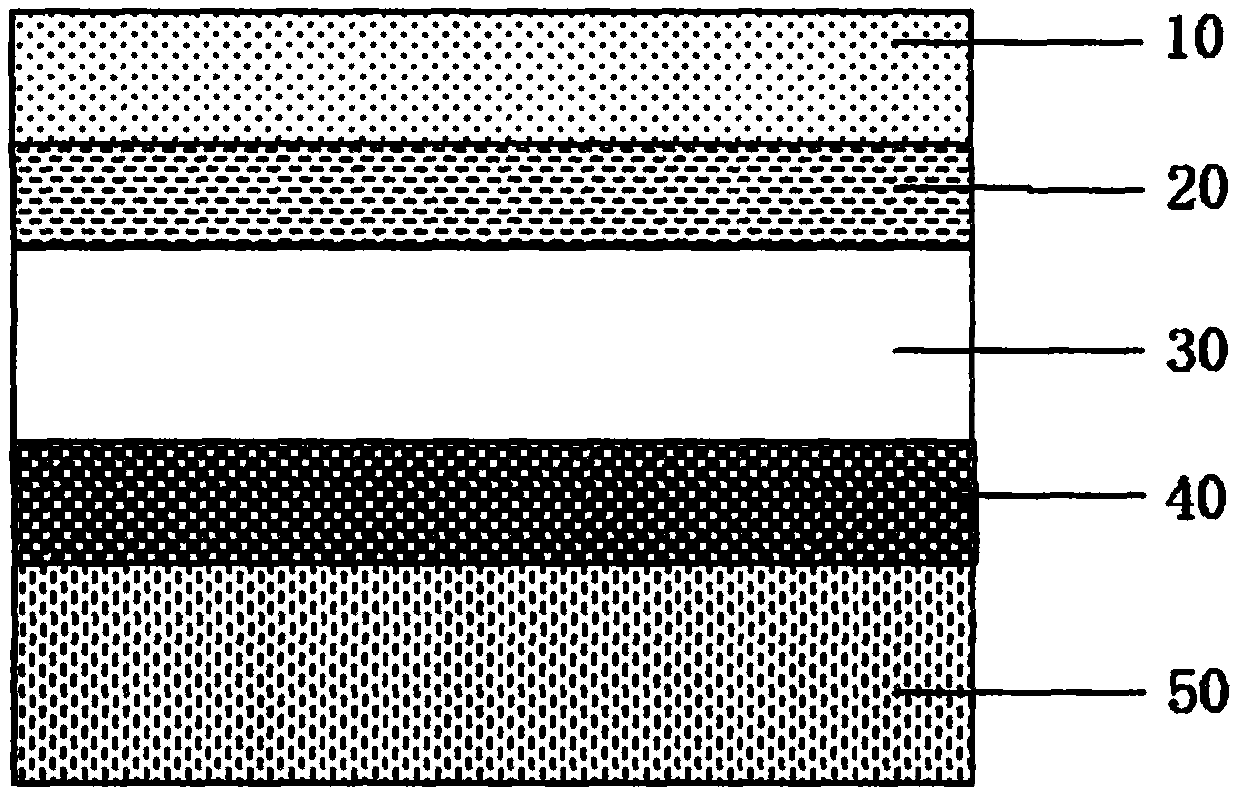

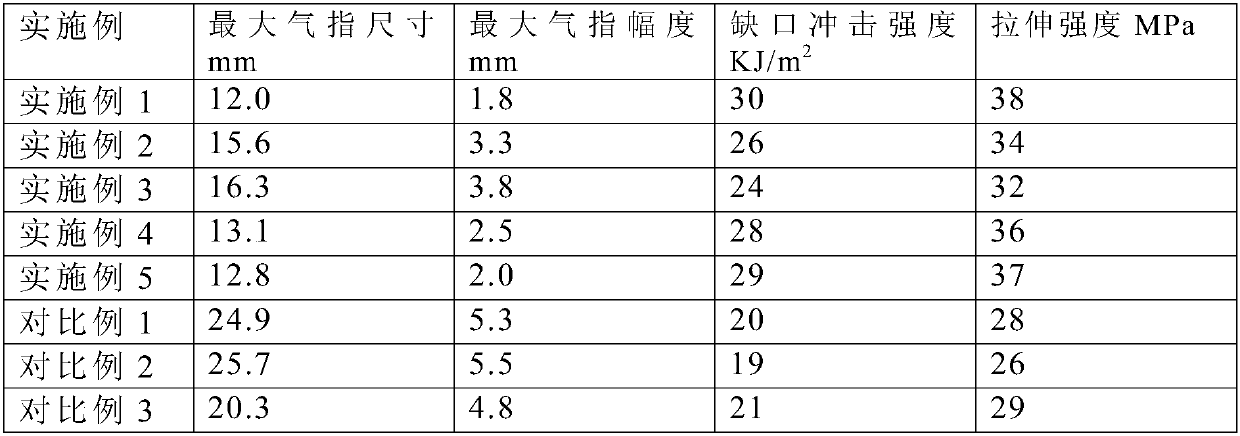

Aluminum plastic film with low warping degree after deep punching and high heat sealing strength as well as preparation method thereof

InactiveCN110328952ASimple processing technologyReduce weightSynthetic resin layered productsCell component detailsPunchingWhole body

The invention provides an aluminum plastic film with low warping degree after deep punching and high heat sealing strength as well as a preparation method thereof. The aluminum plastic film is prepared by pressing a polyamide film layer, a first adhesion layer, an aluminum foil layer, a second adhesion layer and a polypropylene film layer into a whole body. According to the aluminum plastic film with low warping degree after deep punching, which is provided by the invention, the tensile strength of the polypropylene film is more than 40 MPa, the breaking elongation is more than 200 percent, and the stress generated by the polyamide film is counteracted by the stress generated by the high-strength casting polypropylene film layer in the deep punching process, so that the deep punching warping is avoided. The aluminum plastic film provided by the invention is simple in processing process, lightweight, high in deep punching depth, low in warping degree and high in heat sealing strength, and the product is safe and practical.

Owner:惠州市广麟材耀科技有限公司

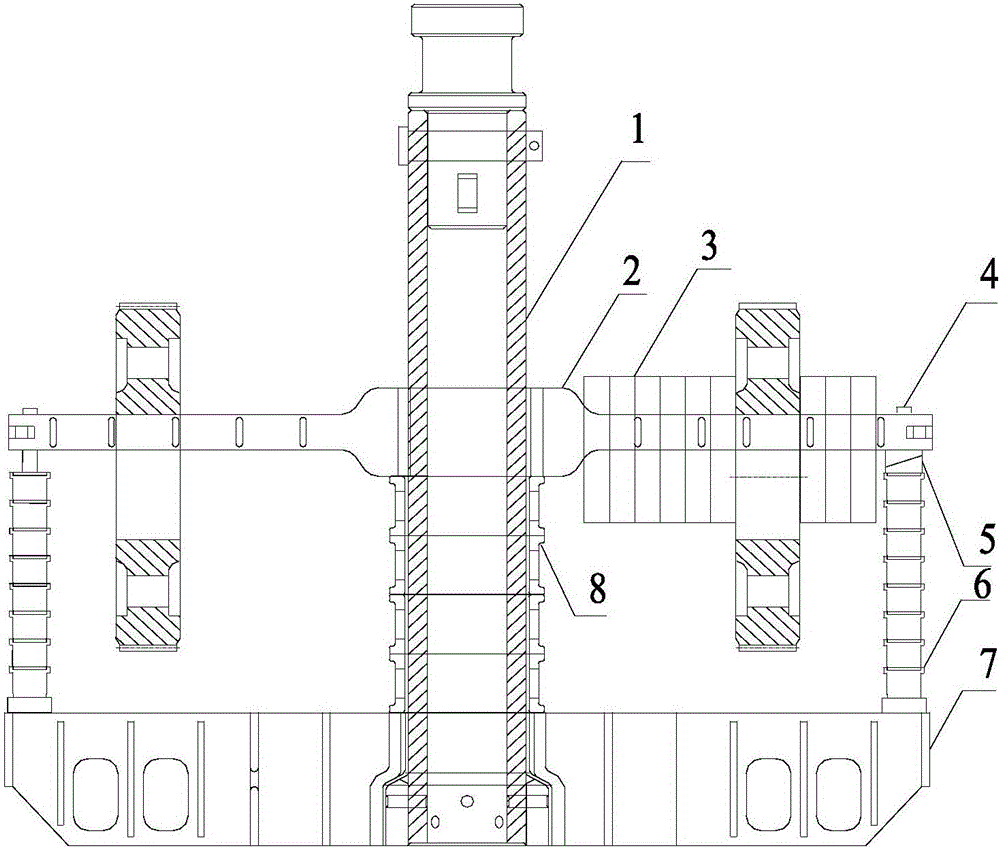

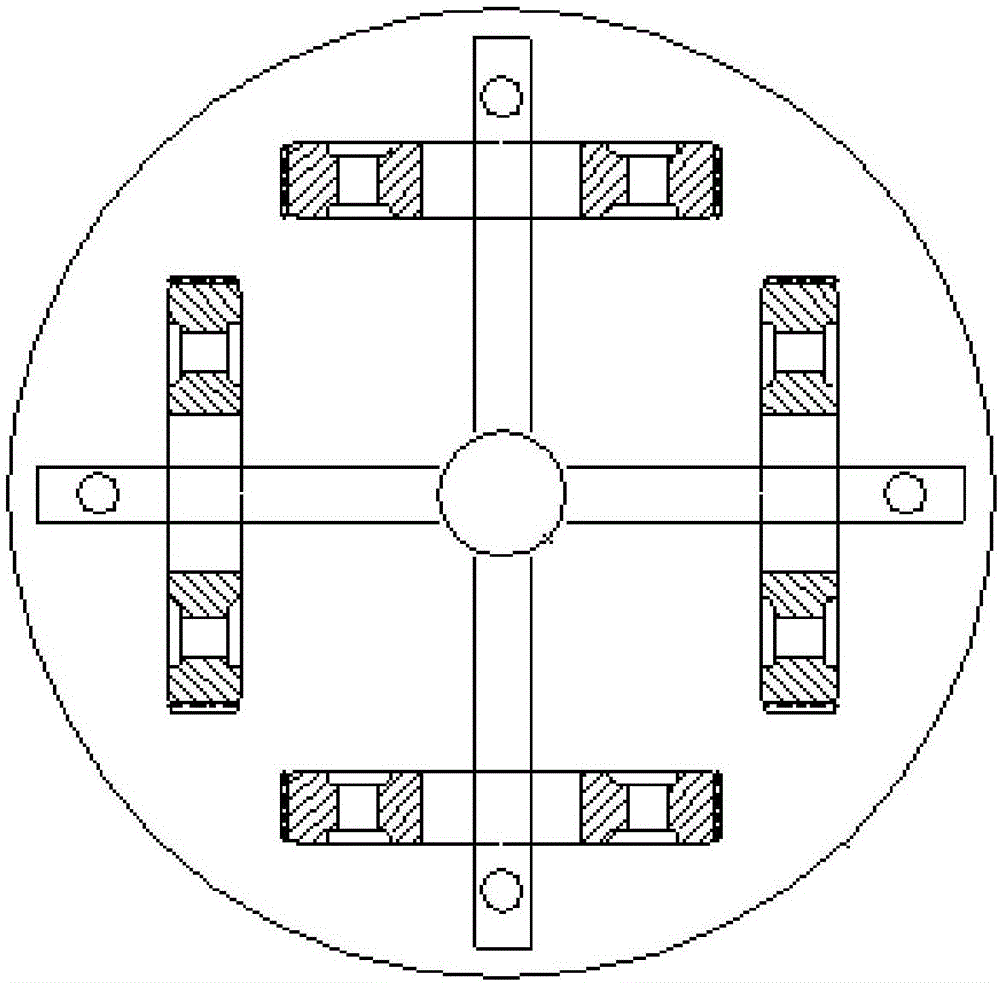

Gear quenching device

InactiveCN106544492AEvenly heatedPrevent ellipseFurnace typesHeat treatment furnacesEngineeringCantilever

The invention relates to a gear quenching device. The gear quenching device comprises a chassis, a hanger rod perpendicularly mounted on the center of the chassis and a cantilever wing beam, wherein a plurality of spacer bushes are stacked at the outer side of the hanger rod between the cantilever wing beam and the chassis in a sleeving mode; peripheral holes are formed in four outer end parts of the cantilever wing beam; vertical brackets, lower ends of which are connected to the upper surface of the chassis, are formed in the peripheral holes in a penetrating mode; a plurality of sleeves are stacked at the outer side of the vertical brackets between the cantilever wing beam and the chassis in the sleeving mode; and a pair of wedge-shaped cushion blocks is blocked between the sleeves and the vertical brackets. The gear quenching device has the beneficial effects: a cross cantilever wing beam is adopted for suspending a gear, so that the advantages of high efficiency, stability, safety and the like are achieved; suspending, quenching and racking can be efficiently completed by regulating height of the space bushes and height of the cushion blocks, so that parts in the device are fixed and do not shift. Number of loaded gears is increased, so that production efficiency is greatly improved, and production cost is greatly reduced; and the left end and the right end of the gear are uniformly heated, so that the dimension precision of the gear is improved.

Owner:CHANGZHOU UNIV

Infrared detection device

InactiveUS20150168222A1High infrared detectabilityPrevent warpageMaterial analysis by optical meansPyrometry using electric radation detectorsInter layerLight sensing

An infrared detection device includes a substrate and a heat-type light sensing element. The substrate has a recess, and a frame positioned around the recess. The heat-type light sensing element has a leg and a sensing unit, and the leg is connected onto the frame so that the sensing unit is positioned over the recess. The heat-type light sensing element includes an intermediate layer provided on the substrate, a first electrode layer provided on the intermediate layer, a sensing layer provided on the first electrode layer, and a second electrode layer provided on the sensing layer. The substrate has a linear thermal expansion coefficient larger than that of the sensing layer. The intermediate layer has a linear thermal expansion coefficient decreasing toward the first electrode layer from the substrate.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

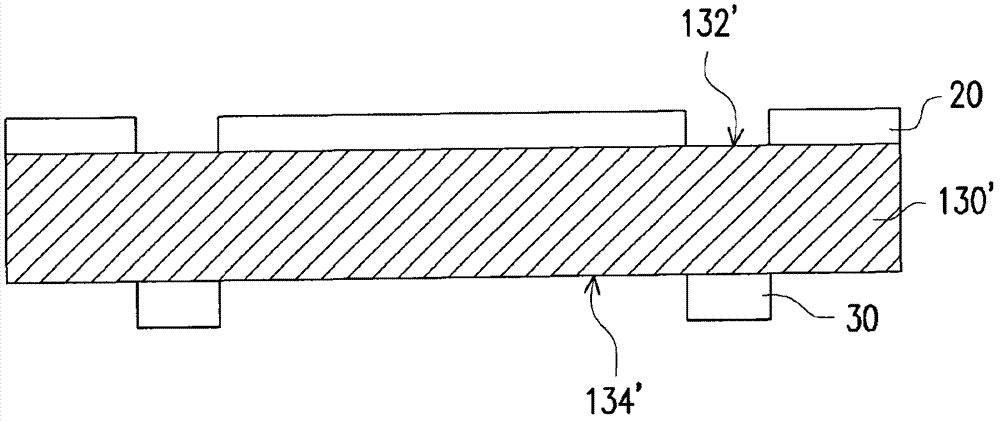

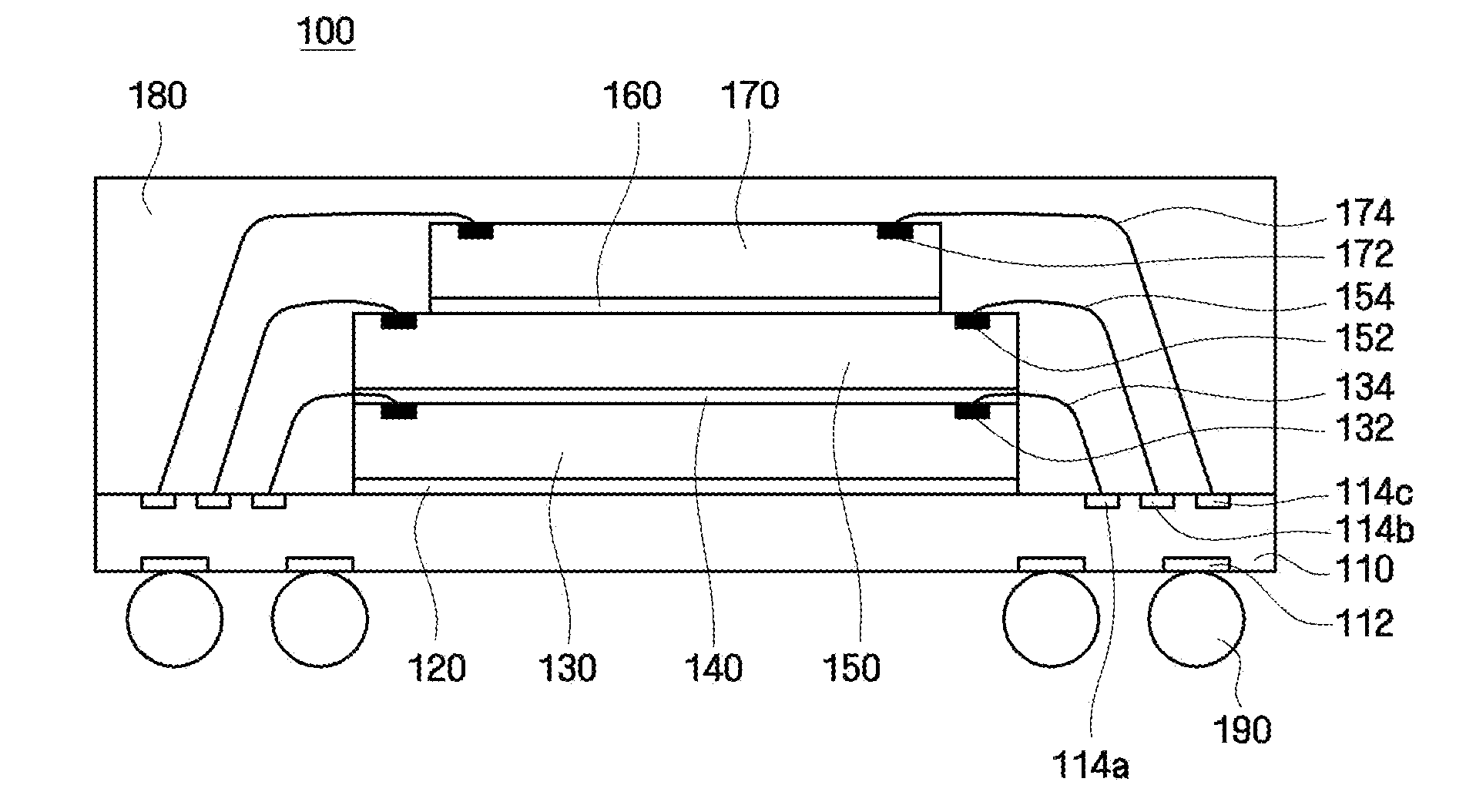

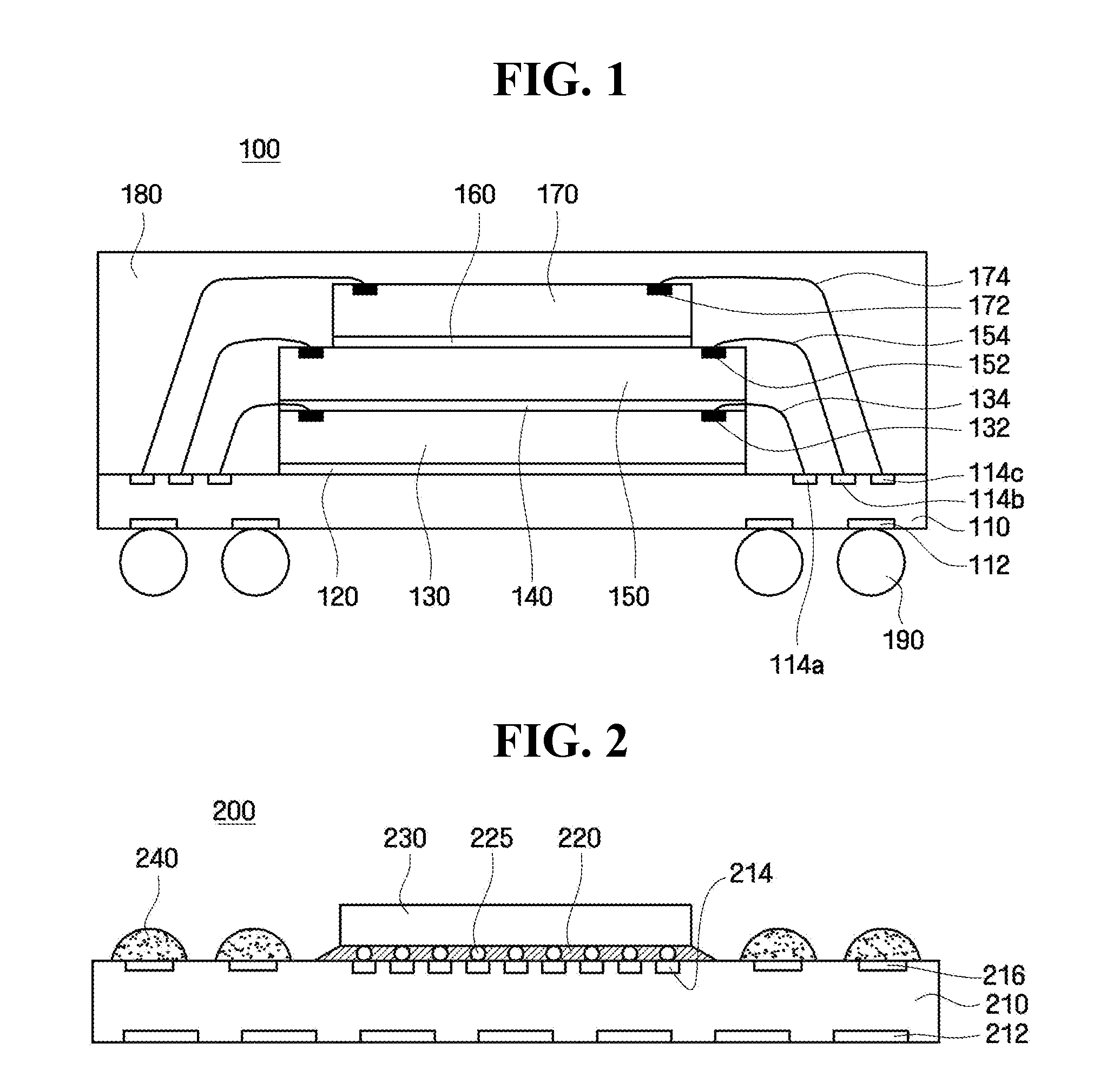

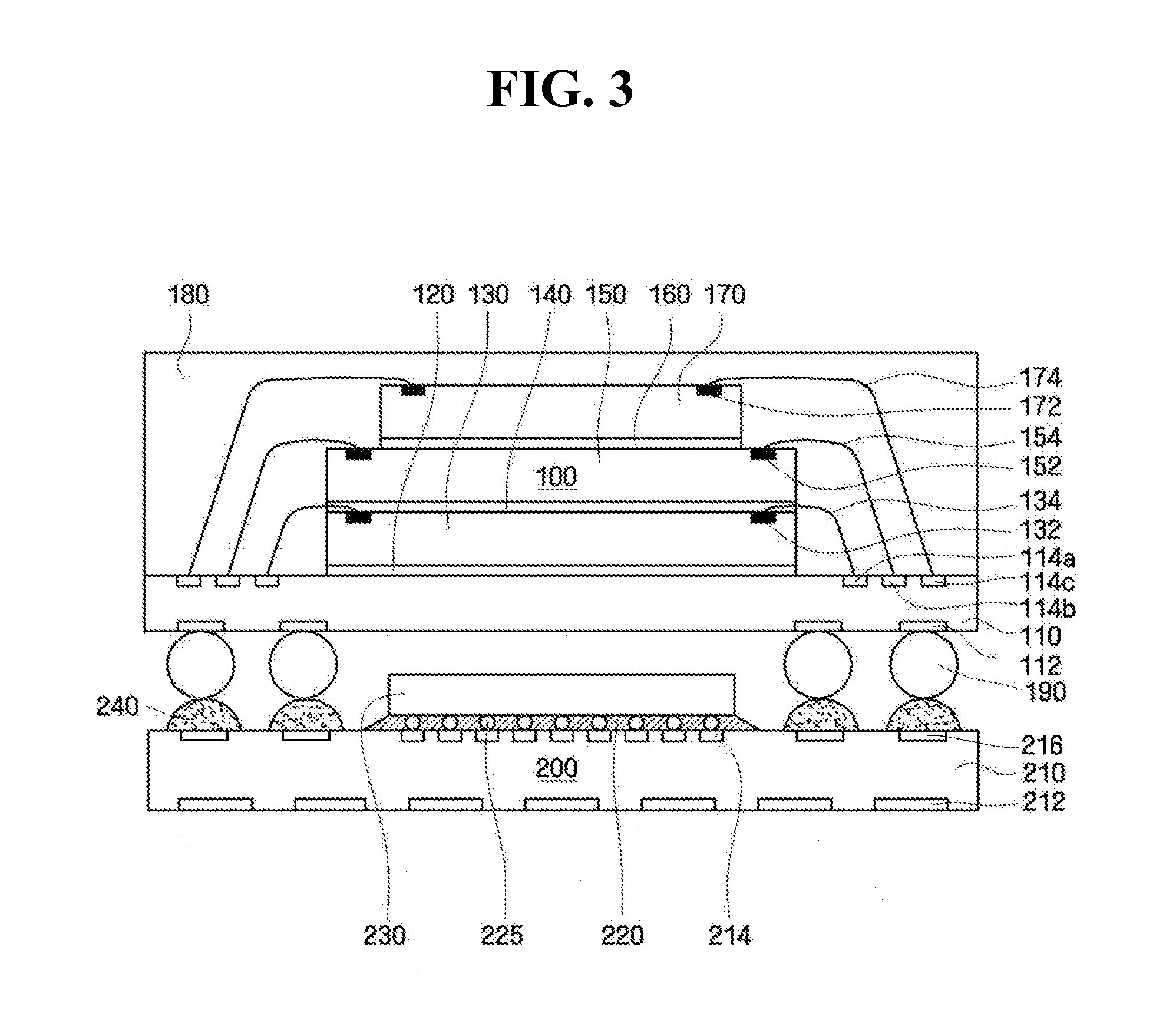

Stacked package, method of fabricating stacked package, and method of mounting stacked package fabricated by the method

ActiveUS20120252163A1Easy to makeMinimizing load appliedSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Provided are a stacked package, method of fabricating a stacked package, and method of mounting a stacked package. A method includes providing an upper semiconductor package including an upper package substrate, upper semiconductor chips formed on a top surface of the upper package substrate, and first solders formed on a bottom surface of the upper package substrate and having a first melting temperature, providing a lower semiconductor package including a lower package substrate, lower semiconductor chips formed on a top surface of the lower package substrate, and solder paste nodes formed on the top surface of the lower package substrate and having a second melting temperature lower than the first melting temperature, and forming inter-package bonding units by attaching respective first solders and solder paste nodes to each other by performing annealing at a temperature higher than the second melting temperature and lower than the first melting temperature.

Owner:SAMSUNG ELECTRONICS CO LTD

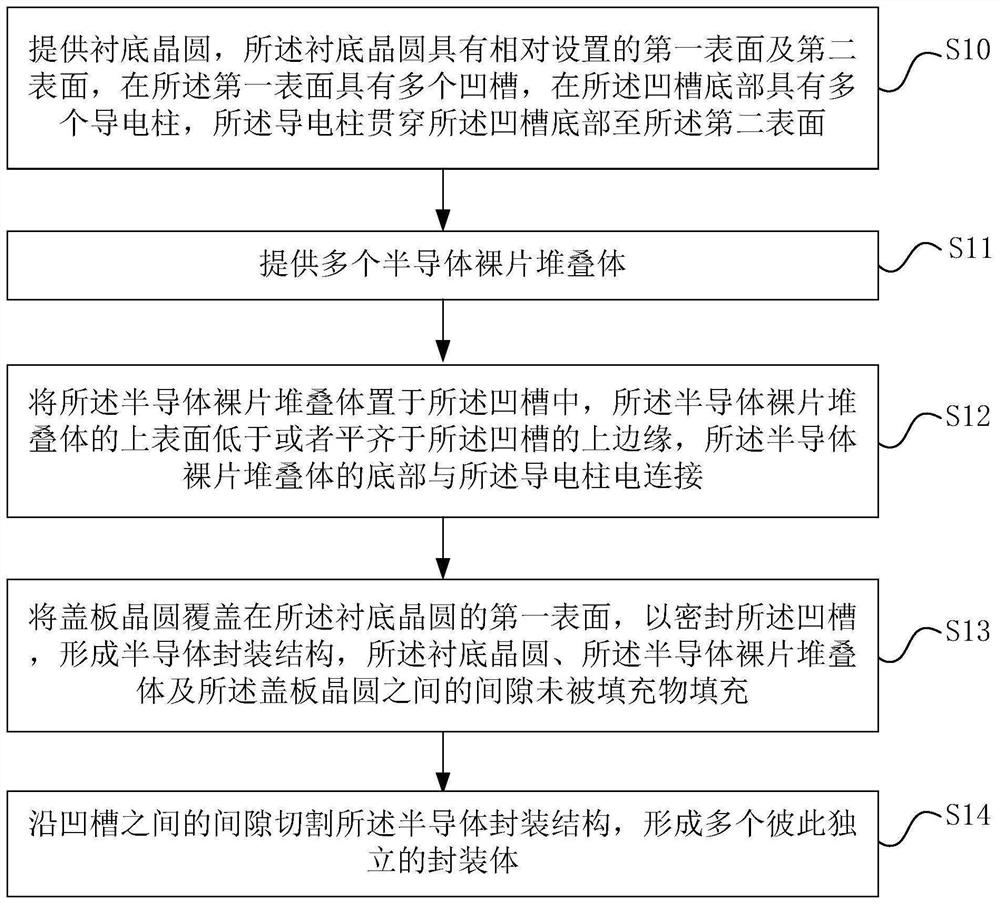

Semiconductor packaging method, semiconductor packaging structure and packaging body

PendingCN112670191ALower the altitudeAchieve ultra-thin packagingSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureWafer

The invention provides a semiconductor packaging method, a semiconductor packaging structure and a packaging body. The method comprises the following steps: providing a substrate wafer provided with a first surface and a second surface, wherein the first surface and the second surface are oppositely arranged, the first surface is provided with a plurality of grooves, the bottom of each groove is provided with a plurality of conductive columns, and the conductive columns penetrate through the substrate wafer; providing a plurality of semiconductor bare chip stacks; placing the semiconductor bare chip stacks in the groove, wherein the upper surface of the semiconductor bare chip stack is lower than or flush with the upper edge of the groove, and the bottom of the semiconductor bare chip stack is electrically connected with the conductive columns; and covering the first surface of the substrate wafer with the cover plate wafer to seal the groove to form a semiconductor packaging structure, wherein it is ensured that gaps among the substrate wafer, the semiconductor bare chip stack body and the cover plate wafer are not filled with the filler. The method of the invention has the advantages that the formed semiconductor structure has the characteristics of low packaging height, high reliability and low warping degree.

Owner:CHANGXIN MEMORY TECH INC

Method for producing ceramic-honeycomb-structure-molding die and method for producing ceramic honeycomb structure

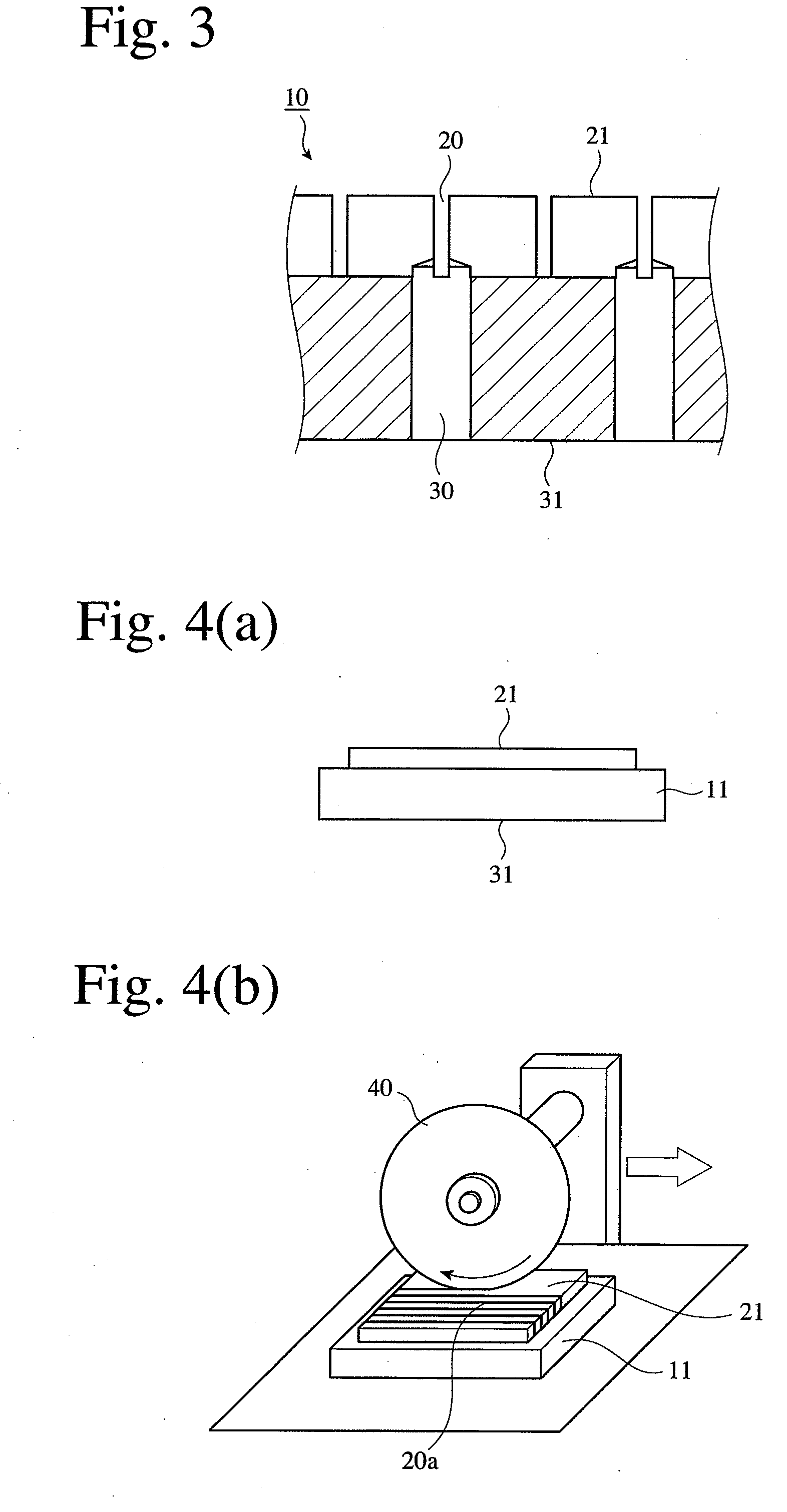

ActiveUS20100044910A1Avoid breakingPrevent warpageEdge grinding machinesMetal working apparatusEngineeringHoneycomb structure

A method for producing a die for molding a ceramic honeycomb structure, which has molding grooves arranged in a lattice pattern and apertures communicating with the molding grooves for supplying a moldable material, wherein the formation of the lattice-patterned grooves by machining is conducted by a first machining operation for forming pluralities of first parallel grooves, and a second machining operation for forming second grooves crossing the first grooves; wherein the first and second machining operations are conducted by at least 2 passes of grinding or cutting using a rotating tool; and wherein the second machining operation is conducted by up-cutting in the second pass or later, and a method for producing a ceramic honeycomb structure using such a die.

Owner:HITACHI METALS LTD

Light guide plate and a planar lighting device using the same

InactiveUS20070147759A1Suppress warpageUneven brightness be reduceElectric lightingOptical waveguide light guideExit surfaceOptoelectronics

A light guide plate of the invention has a plurality of unit light guide plates that are formed of a transparent resin material and which are joined together. Each of the unit light guide plates has a flat rectangular light exit surface and a back surface that is opposite the light exit surface and which has a parallel groove formed in generally a center and parallel to a side of the rectangular light exit surface. The light guide plate is used with a linear light source fitted in the parallel groove, satisfying the inequality (L0 / 280)2·k(14T2+710T)·(−0.65 log S+1.9)≦10, where L0 is the length (mm) of the light guide plate, k is the linear expansion coefficient [ / ° C.] of the resin material, Ts is the surface temperature [° C.] of the linear light source that has become stable, S is half of the cross-sectional area [mm2] of the unit light guide plate as it is cut through a plane perpendicular to the parallel groove, and T=Ts−25.

Owner:FUJIFILM CORP

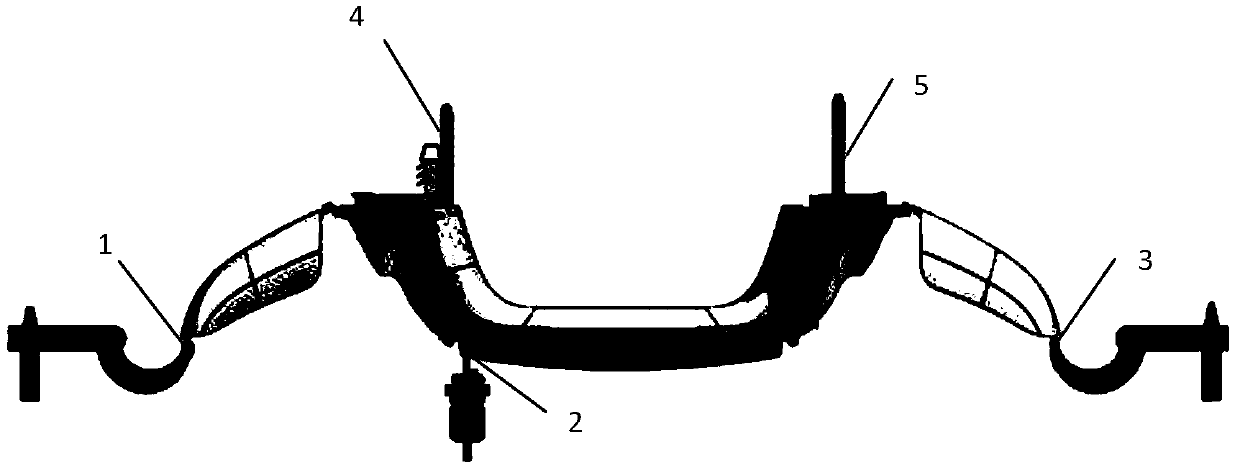

Gas auxiliary injection molding method of car roof handle

ActiveCN109624202APrevent warpageImprove injection molding efficiencyVehicle arrangementsInjection molding machineInjection moulding

The invention belongs to the technical field of car parts and particularly relates to a gas auxiliary injection molding method of a car roof handle. The method comprises the following steps that 1, molten plastic is injected into a die cavity through two or more pouring gates, and after injection of a die is full, pressure is maintained; 2, inert gas is injected into the molten plastic in the diecavity through two or more gas inlets, pressure of the injected inert gas is larger than storing pressure of injection molding, a part of the molten plastic in the die cavity returns to the pouring gates, and the hollow state is formed; and 3, the pressure is maintained, cooling is carried out, the die is opened, and a product is taken out.

Owner:NINGBO SHUAITELONG GRP CO LTD