Packaging method

A packaging method and a plastic sealing layer technology, which are applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as poor reliability and low yield of packaging structures, achieve reliability enhancement, eliminate chip drift problems, The effect of eliminating the warpage of the plastic seal layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] As mentioned in the background, the reliability of the existing wafer level packaging technology is poor, and the yield rate of the packaging structure formed by the existing wafer level packaging technology is low.

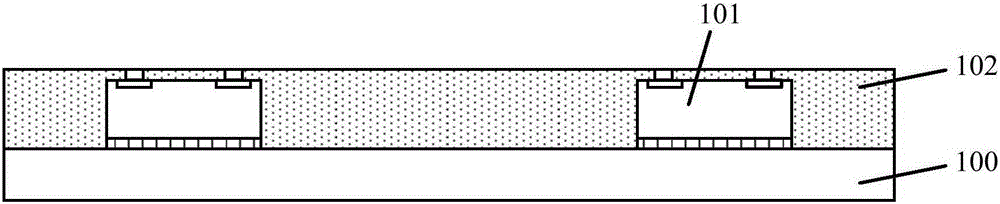

[0039] Please refer to figure 1 , figure 1 It is a schematic cross-sectional structure diagram of an embodiment of a wafer-level packaging structure, including: a carrier 100; several chips 101 fixed on the surface of the carrier 100, the chips 101 including a functional surface; covering the carrier 100 and several chips The plastic sealing layer 102 on the surface of 101. Wherein, after the chip 101 is bonded on the surface of the carrier 100 , the plastic sealing layer 102 is formed through a plastic sealing process such as injection molding or transfer injection, and the plastic sealing layer 102 wraps the chip 101 . After forming the plastic encapsulation layer 102, it also includes: removing the carrier 100 and exposing the functional surface of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More