Nanosecond digital programmable delay circuit based on FPGA (Field-Programmable Gate Array)

A delay circuit, nanosecond technology, applied in program control, instrument, computer control, etc., can solve the problems of large delay time scale, poor delay accuracy, fixed delay time, etc. High applicability and versatility, controllable delay time effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings.

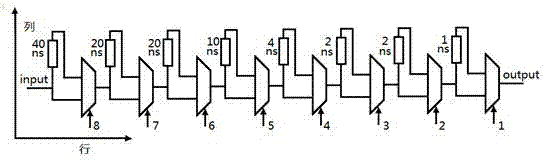

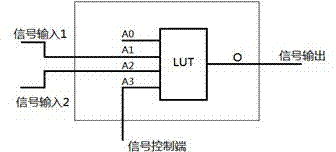

[0016] The FPGA-based nanosecond-level digital programmable delay circuit of the present invention is formed by cascading programmable delay units; the programmable delay unit is composed of a two-to-one selector and a vertical delay unit, and the specific structure is as follows figure 1 shown. figure 1 The delay circuit shown can realize any delay of 0~99ns; according to the needs of users, the delay circuit can be expanded to realize any time delay circuit. The present invention uses figure 1 The circuit shown is taken as an example to illustrate the specific implementation of the invention. The delay generated by the signal passing through the one-two selector in the programmable delay unit structure is the system delay of the circuit of the present invention. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More