Dynamically reconfigurable multi-stage parallel single instruction multiple data array processing system

A single-instruction multi-data, array processing technology, applied in the field of visual image processing, can solve the problems of lack of fast feature recognition, inability to meet high-speed real-time requirements, and inability to achieve fast and flexible wide-area processing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0056] It should be noted that, in the drawings or descriptions of the specification, similar or identical parts all use the same figure numbers. In the drawings, elements or implementations not shown or described are forms known to those skilled in the art. Additionally, while illustrations of parameters including particular values may be provided herein, it should be understood that the parameters need not be exactly equal to the corresponding values, but rather may approximate the corresponding values within acceptable error margins or design constraints.

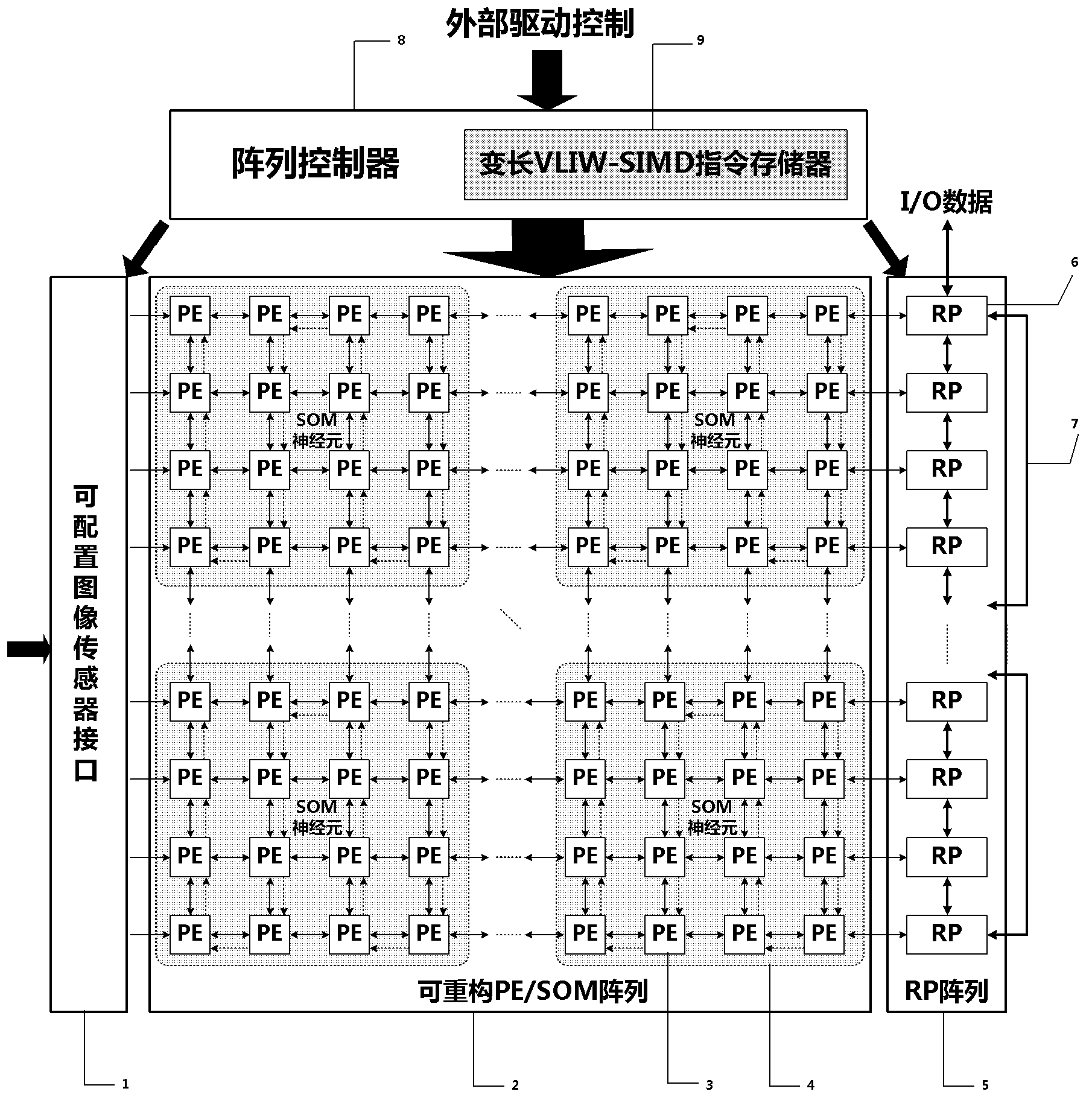

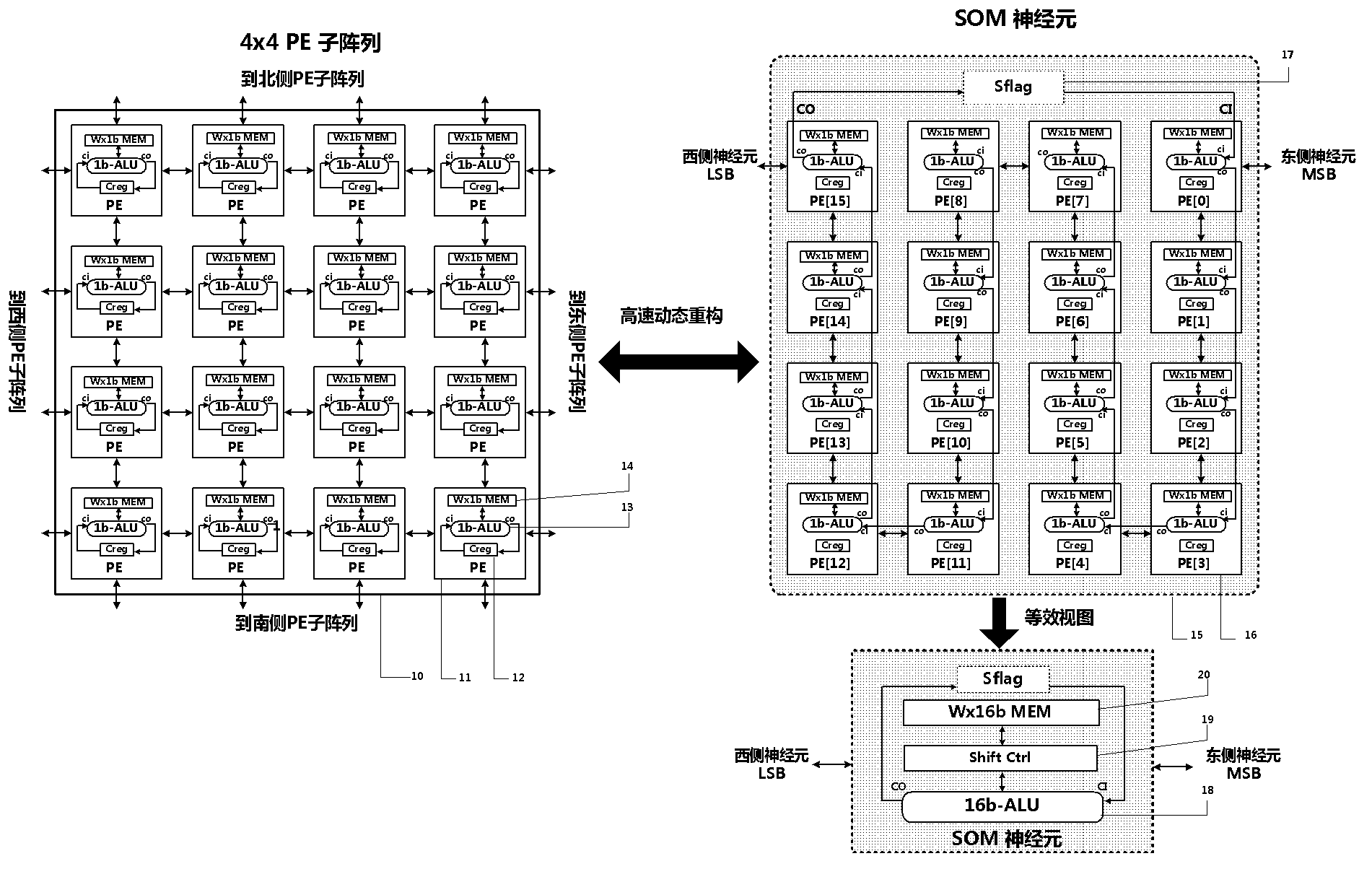

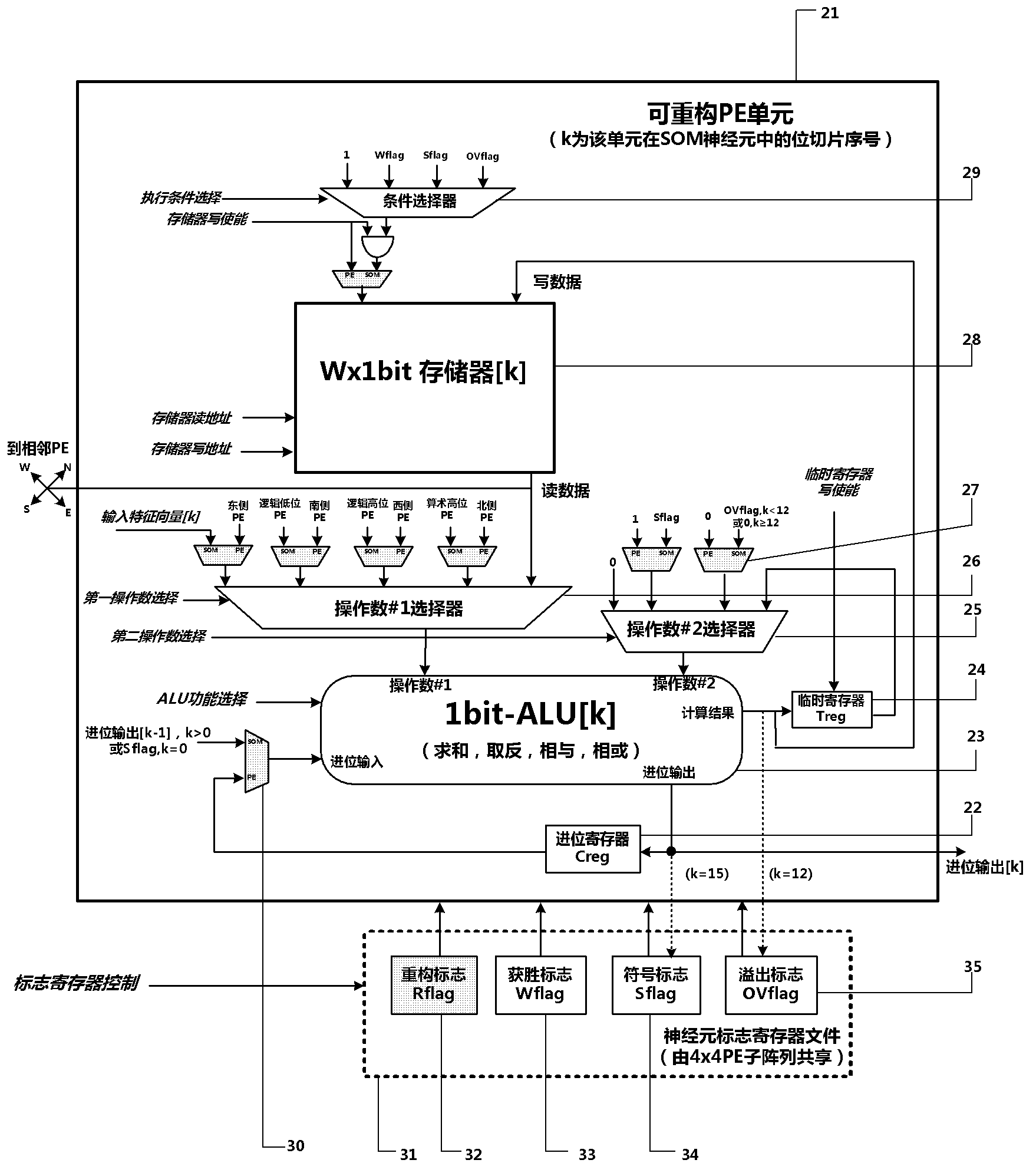

[0057] In an exemplary embodiment of the present invention, a dynamically reconfigurable multi-level parallel SIMD array processing system is provided. Such as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More