Standard cell library layout design method, layout method and standard cell library

A standard cell library and layout design technology, applied in computing, electrical components, instruments, etc., can solve the problems of occupying wiring resources, transistor size restrictions, and reducing wiring resources, etc., to achieve the effect of increasing wiring resources and optimizing size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

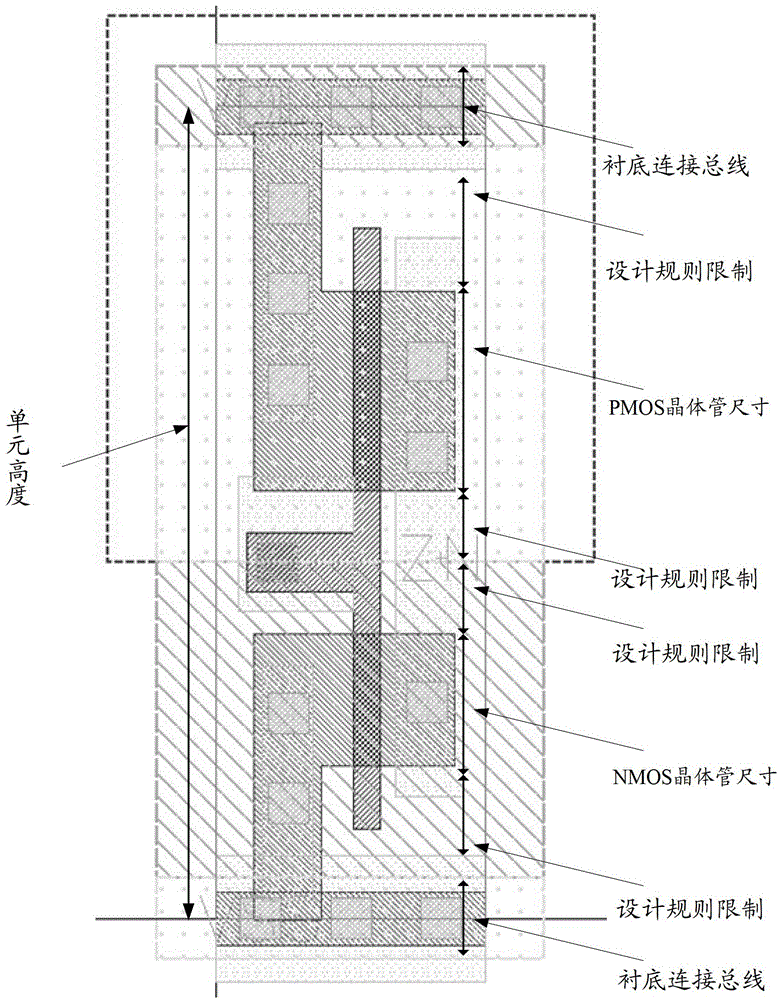

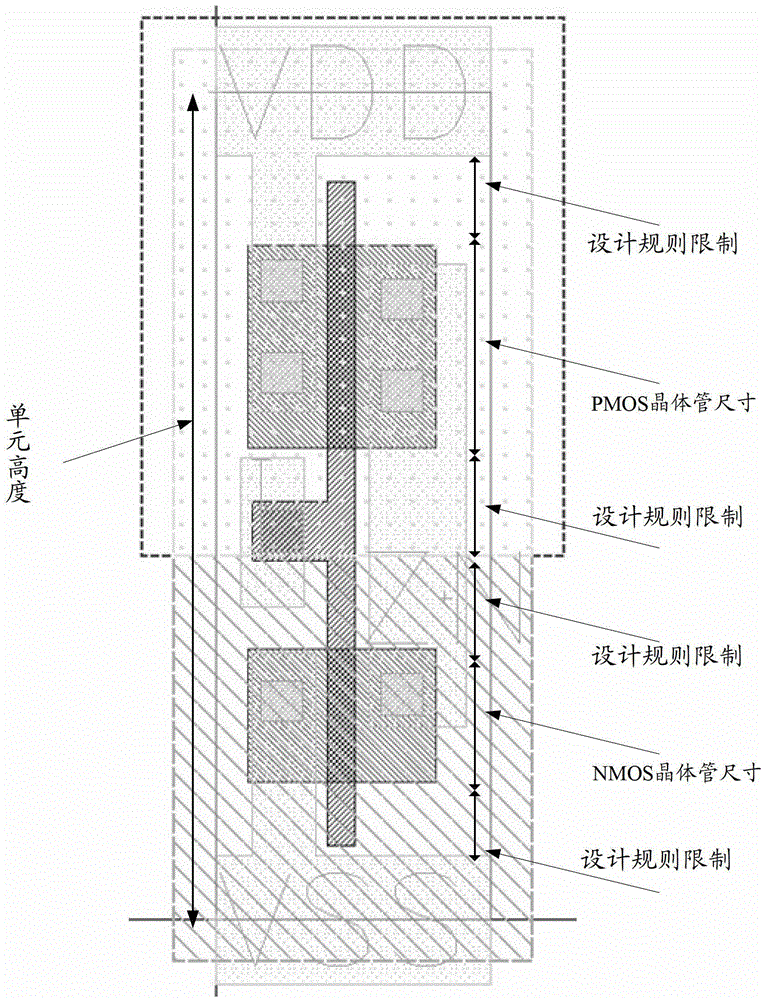

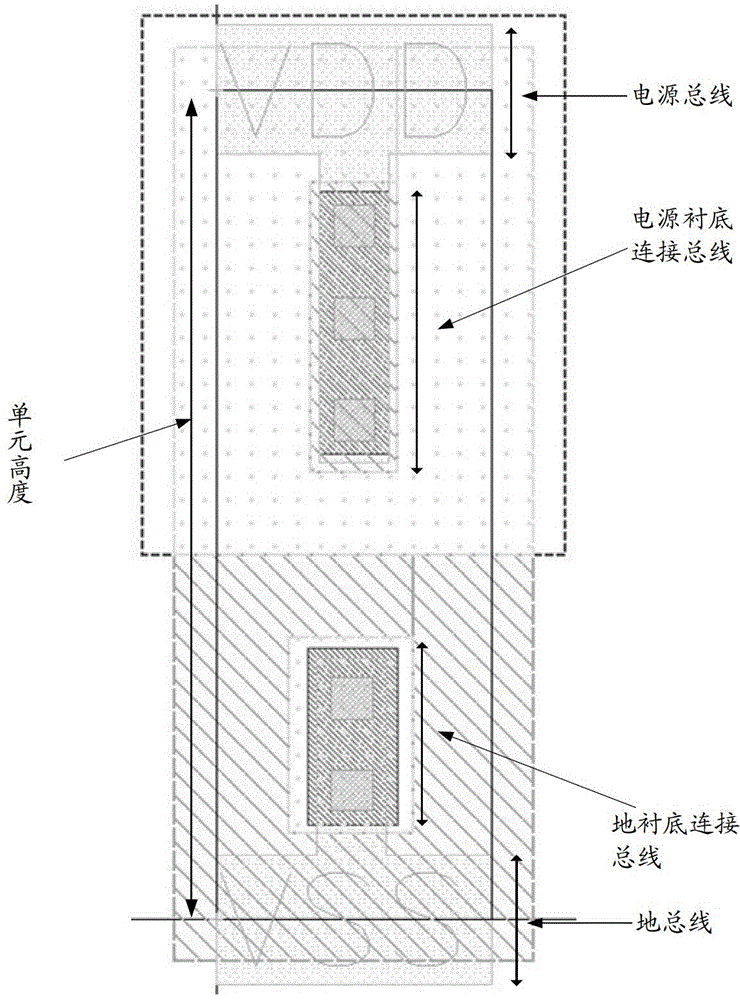

[0031] Generally, the standard cell library includes circuit logic units and special cells. The standard cell layout in the standard cell library in the prior art includes a substrate bus to connect the power supply and the ground bus to provide substrate voltage for the standard cell, but the substrate is connected to the bus. Occupy the wiring resources of the standard cell, so the size of the transistor is obviously limited, causing the wiring resources in the standard cell to decrease. In order to solve this problem, the present invention adds a separate substrate connection unit in the standard cell library, which can optimize The size of the transistor in the standard cell, and can increase the routing resources in the layout of the standard cell.

[0032] An embodiment of the present invention prov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More