Epitaxial wafer manufacturing method suitable for super junction device

A manufacturing method and technology of epitaxial wafers, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as poor BV uniformity and inconsistent concentration ratio distribution, and achieve the effect of improving uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

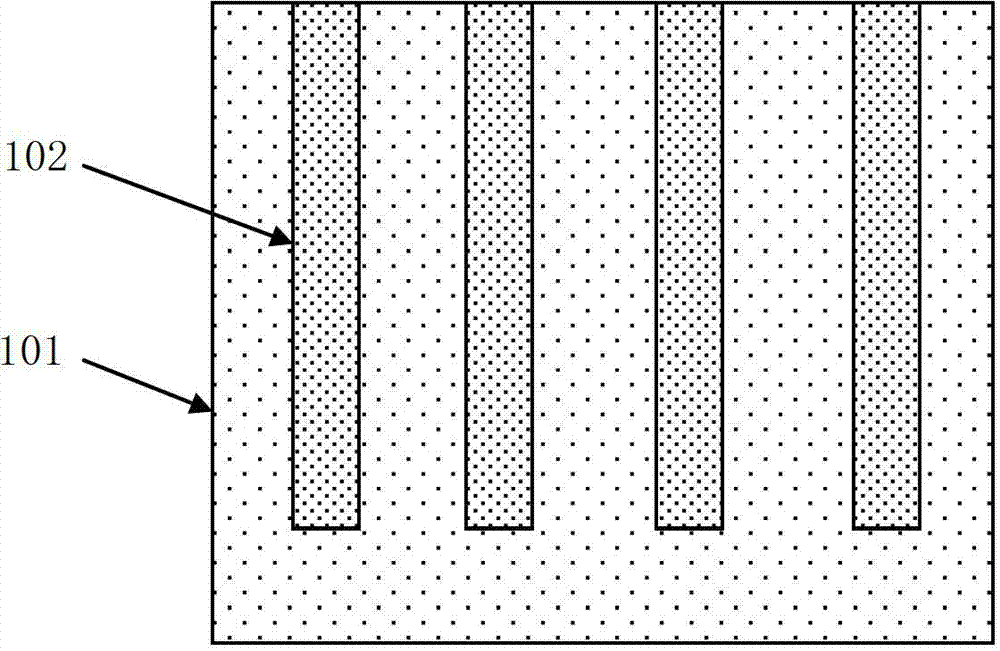

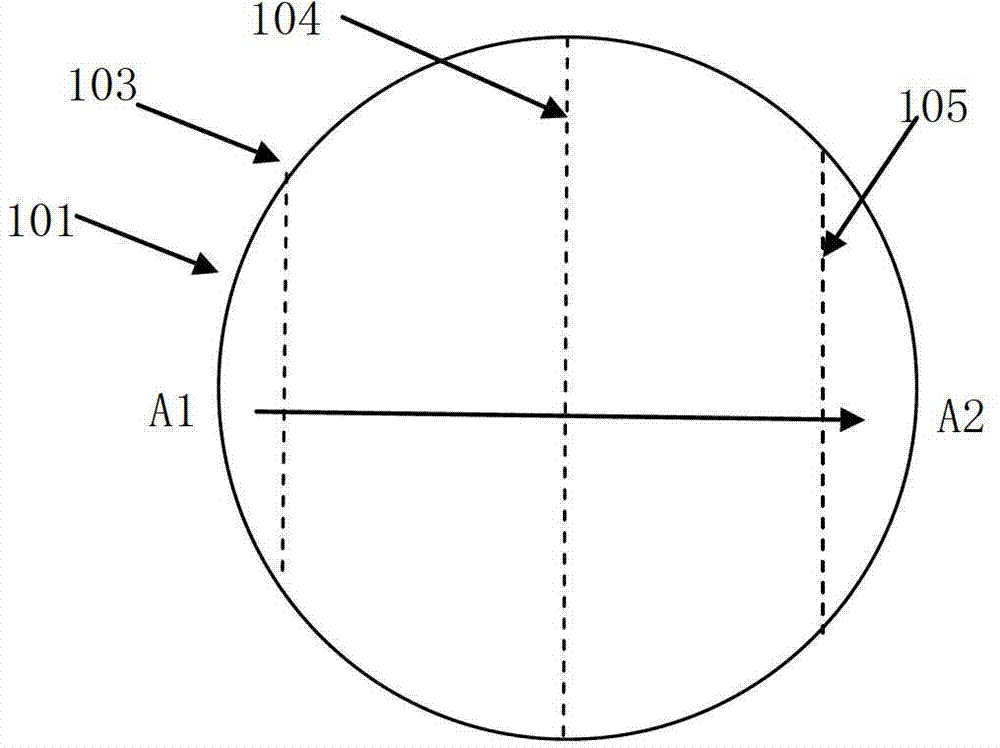

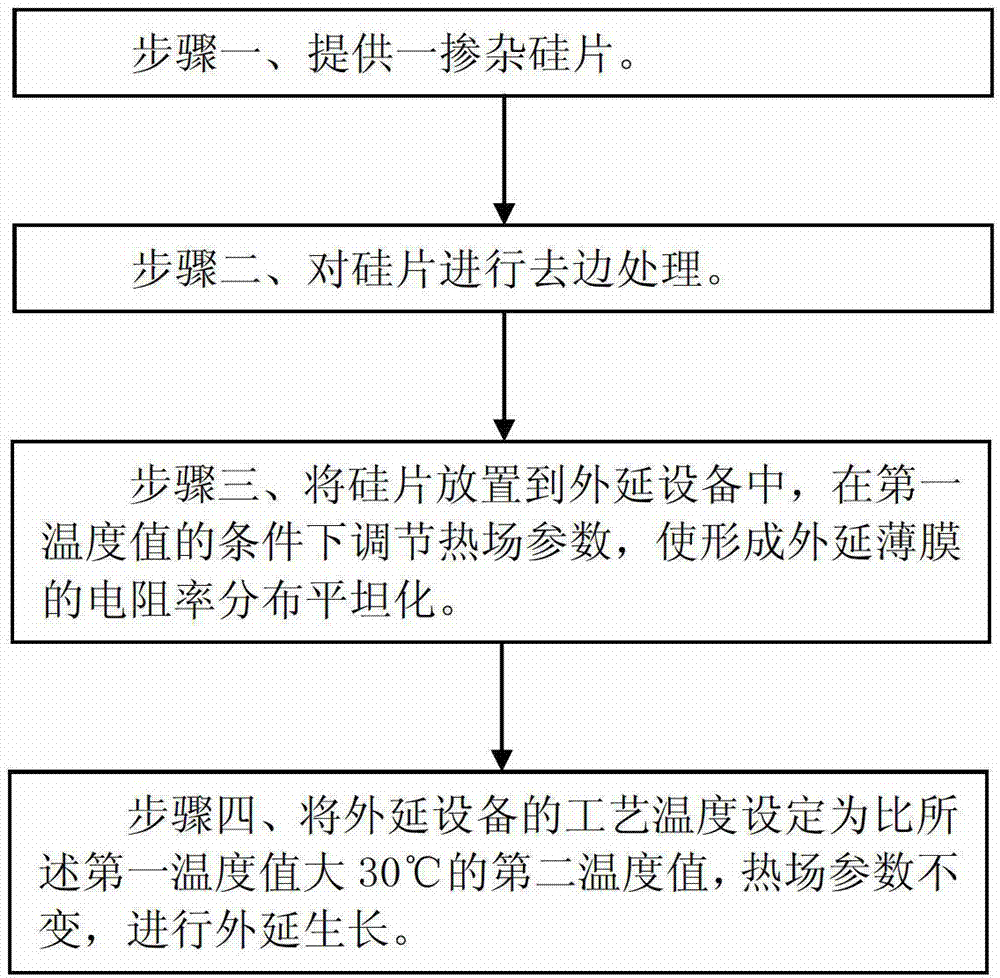

[0023] Such as image 3 Shown is the flow chart of the embodiment of the present invention; Figure 4 Shown is a schematic diagram of the resistivity distribution of the epitaxial wafer produced by the method of the embodiment of the present invention. The embodiment of the present invention is applicable to the epitaxial wafer manufacturing method of the super junction device including steps:

[0024] Step 1. Provide a silicon wafer, the doping type of the silicon wafer is the same as that of the epitaxial layer 1 to be formed later and both are N-type, and the doping concentration of the silicon wafer is higher than that of the epitaxial layer 1 to be formed later. The doping concentration of the epitaxial layer.

[0025] Step 2. De-edge treatment is performed on the silicon wafer, the de-edge treatment is used to remove the thermal oxide layer at the back edge of the silicon wafer, and the de-edge treatment is 2 mm. The edge removal process specifically includes: coverin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More