A real-time correction method for time error of time-alternating analog-to-digital conversion system

An analog-to-digital conversion and time error technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve problems such as difficulty and limit the sampling speed of TIADC system, and achieve the effect of strong versatility, easy hardware implementation, and low computational complexity.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

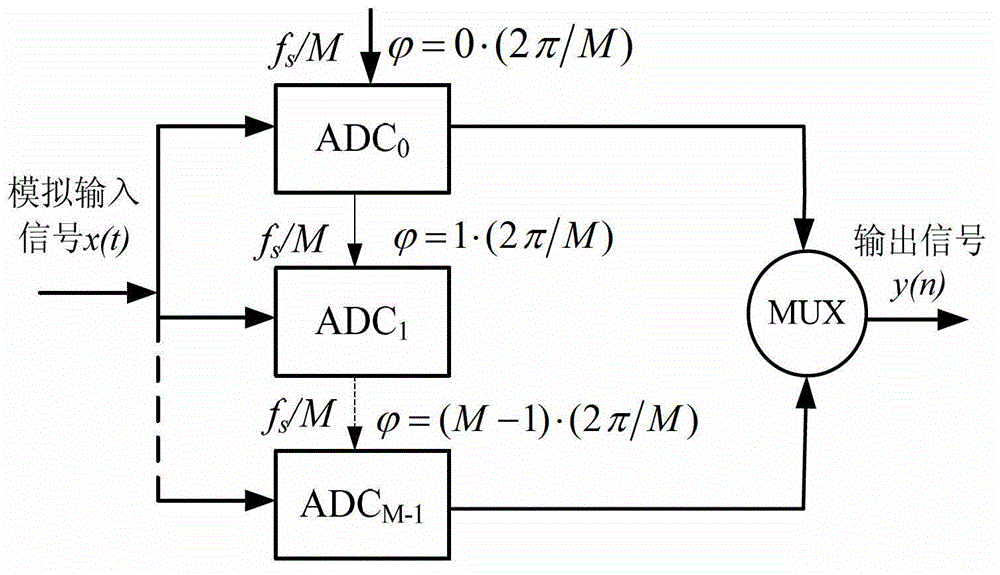

[0037] Such as figure 1 Shown is the TIADC sampling system, which can also be called the structural block diagram of the M-channel parallel time-alternating analog-to-digital converter sampling system. Assuming that the sampled input analog signal is x(t), the sampling interval T of the entire sampling system s =1 / f s , then the single channel sampling interval T=M T s . figure 1 It is a parallel sampling system of M channels, and the sampled signals of M channels are spliced together by a multiplexer MUX to restore an output signal y(n). Then use the compensation method in the present invention to perform the calibration operation.

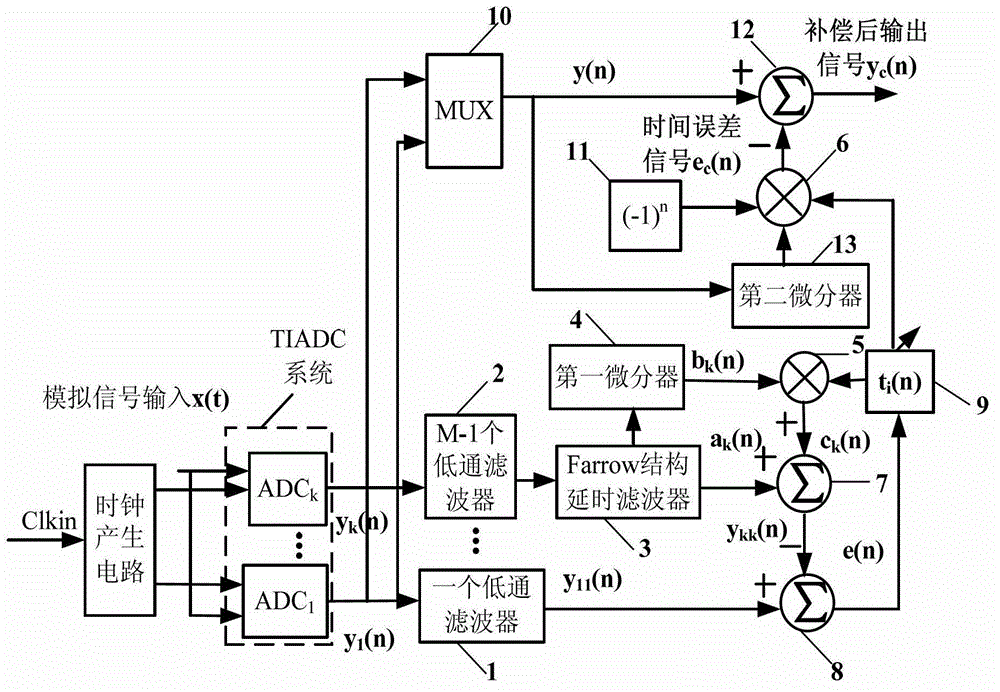

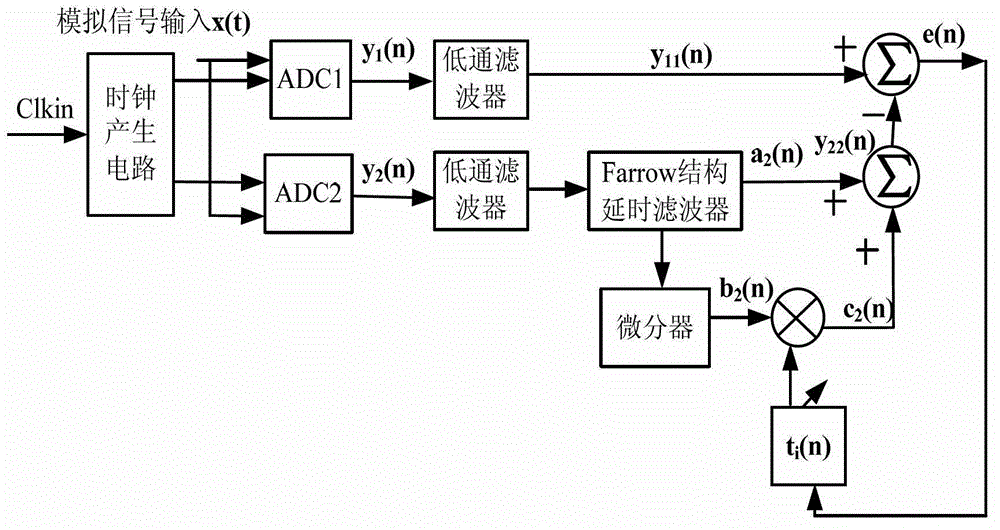

[0038] figure 2 is a model diagram of the time error correction method of the TIADC system.

[0039] Such as figure 2 As shown, the method for correcting the TIADC time error based on the LMS method o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More