Sampler circuit

A sampler and circuit technology, applied in the demodulation of oscillation sampling angle, circuits that oscillate independently of each other, electrical components, etc., can solve problems such as metastability effects, hysteresis, and the insensitivity of digital phase detectors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

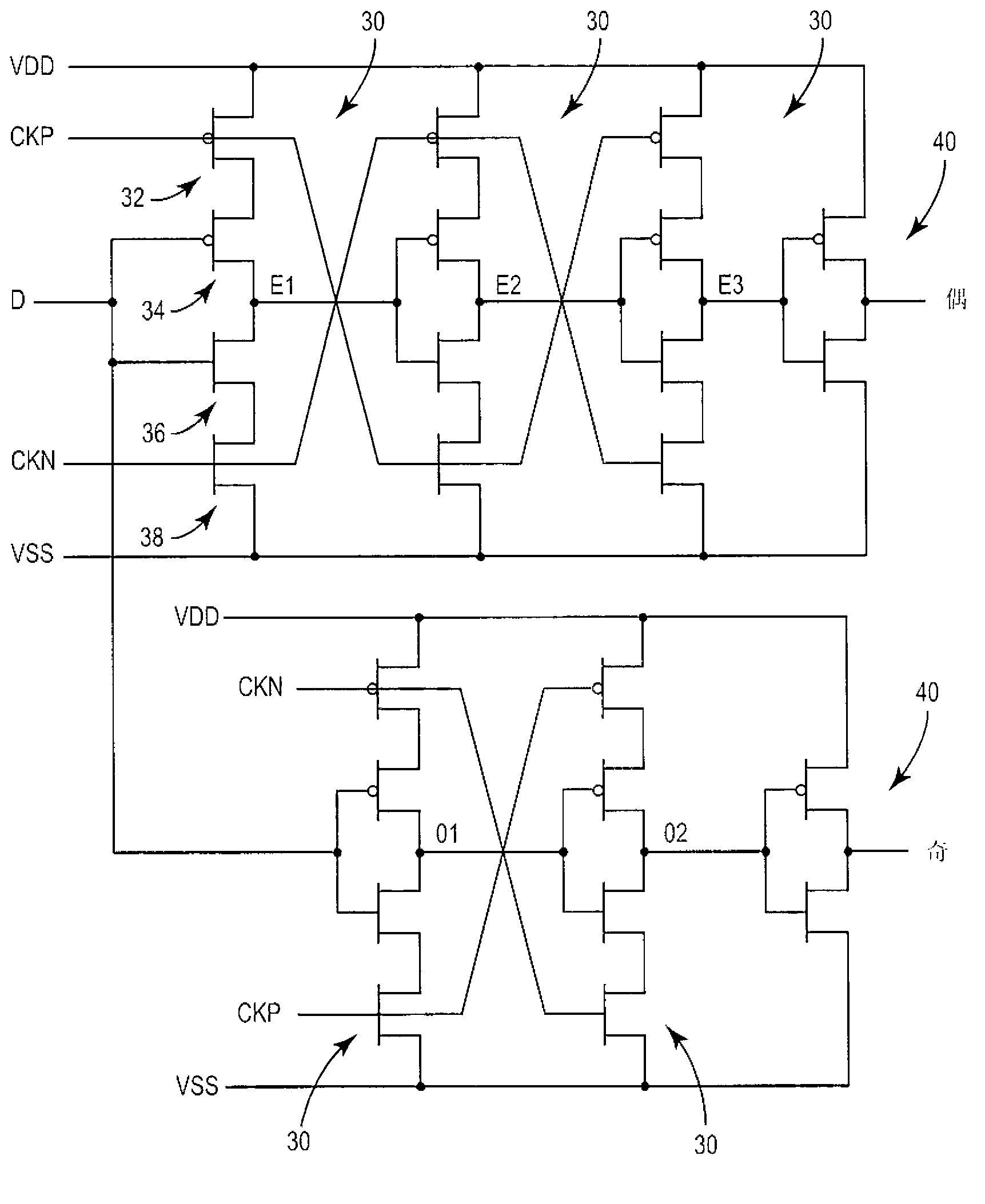

[0020] In a DPLL, the reference clock and DCO output are asynchronous to each other. In fact, the two signals are locked to each other only by DPLL corrective action. Thus, sampling the reference clock with a clock derived from the DCO output raises significant metastability concerns. The phase difference between these two clocks is constantly changing. When the phase difference is close to 0, there are brief durations in which it is not clear whether the sampled value is a logic 0 or a logic 1. In a practical implementation, this duration is actually a small time window for which the correct level of the sampled signal cannot be properly resolved. This is called the metastability window.

[0021] Most sampler circuits employ some form of regenerative feedback to derive a logic 0 or a logic 1 from the sampled input signal. The speed at which a regenerative circuit can resolve an input signal as a logic 0 or a logic 1 depends exponentially on the magnitude of the input sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More