Shift register, display device, gate drive circuit and driving method

A technology of shift register circuit and shift register, which is applied in the direction of static memory, electrical analog memory, digital memory information, etc., which can solve the problems that are not conducive to the bonding process of module driver IC, the control signal cannot be controlled by the circuit, and the length of the driver IC increases. Large and other problems, to achieve the effect of improving voltage and drift problems, good control, and reduced drop rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

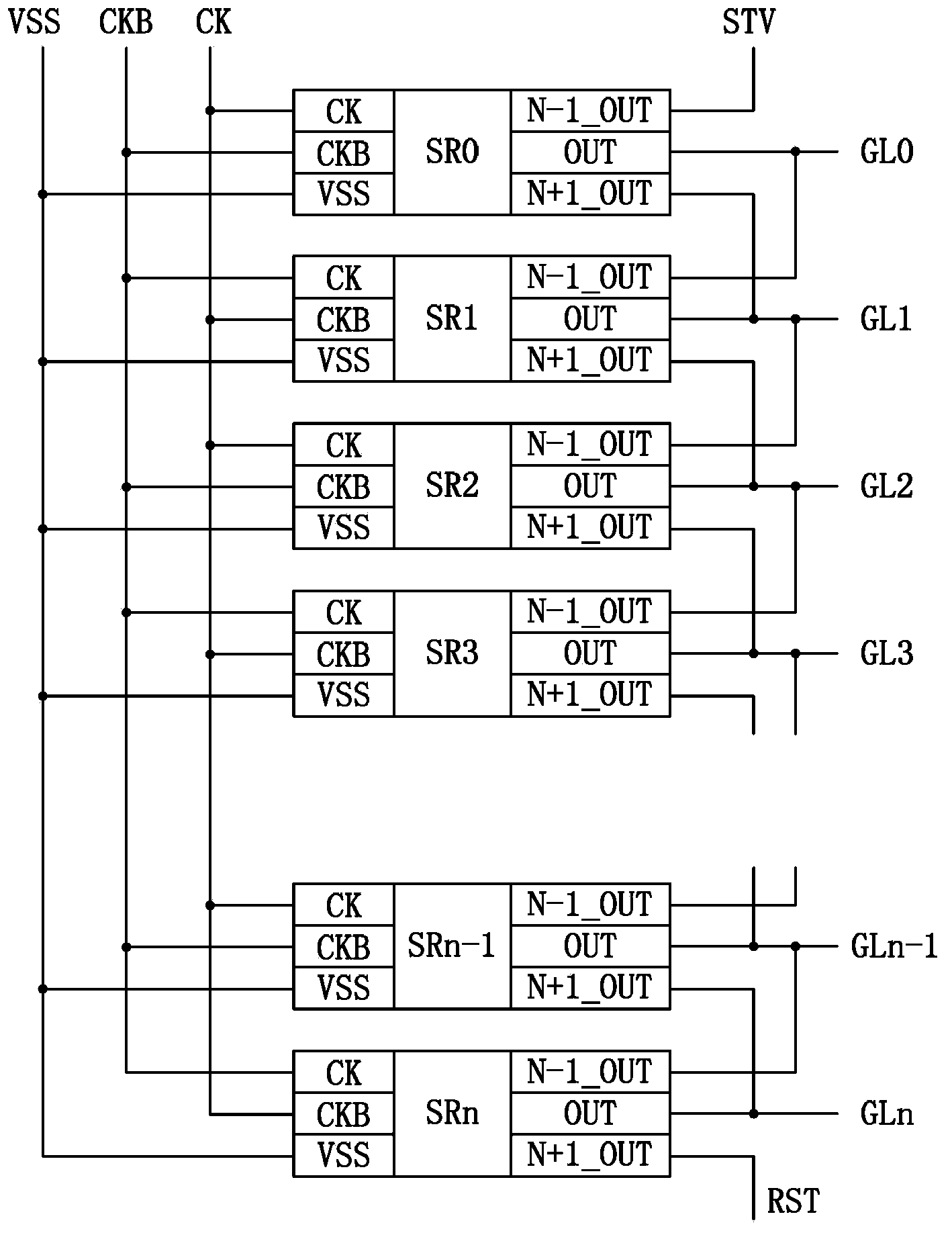

[0045] A shift register according to an embodiment of the present invention, the shift register includes a multi-stage shift register circuit such as figure 2 As shown in the figure, SR0-SRn is each stage of the n-stage shift register circuit, GL0-GLn is the output terminal of the n-stage shift register circuit, STV is the start signal, and the output of each stage of the shift register is used as the The STV start signal, the output of the lower level is used as the Reset reset signal, and it works under the double clock CK and CKB to realize the top-down gate drive scan output.

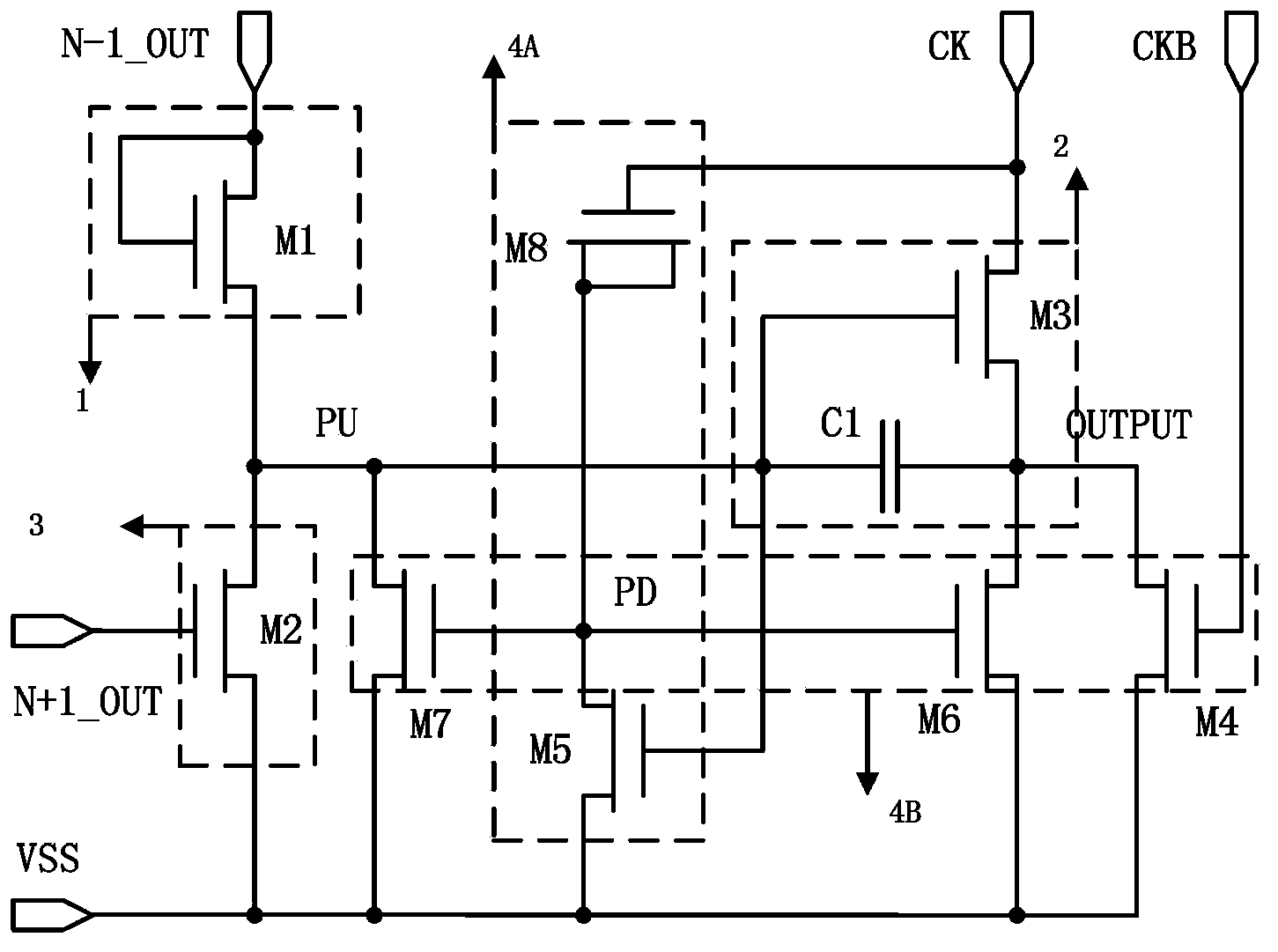

[0046] Such as image 3 As shown, the Nth stage shift register circuit of the multi-stage shift register circuit includes:

[0047] A pre-charging circuit 1 for pre-charging the pull-up circuit;

[0048] The pull-up circuit 2 is used to make the output terminal OUTPUT output a high level after the pre-charging is completed;

[0049] The reset circuit 3 resets the shift register circuit of the Nt...

Embodiment 2

[0074] A kind of shift register of the embodiment of the present invention such as Image 6 As shown, its features are basically the same as those in Embodiment 1, except that the first holding circuit includes a fifth transistor and an eighth transistor, and the control terminal of the eighth transistor is the first control terminal of the holding circuit , the source and drain of the eighth transistor are connected to the source of the fifth transistor, the gate of the fifth transistor is connected to the control terminal of the pull-up circuit, and the drain of the fifth transistor grounding;

[0075] The second holding circuit includes a fourth transistor, a sixth transistor, and a seventh transistor, the gate of the fourth transistor is the second control terminal of the holding circuit, and the source of the fourth transistor is connected to the seventh transistor. The source is connected to the output end of the pull-up circuit, the drain of the fourth transistor is gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More