A mos device for integrated circuit chip esd protection

A MOS device and integrated circuit technology, applied in the electronic field, can solve the problems of increased device production cost, increased chip area, increased device size, etc., and achieves increased substrate resistance, increased substrate resistance, and improved secondary breakdown. effect of current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

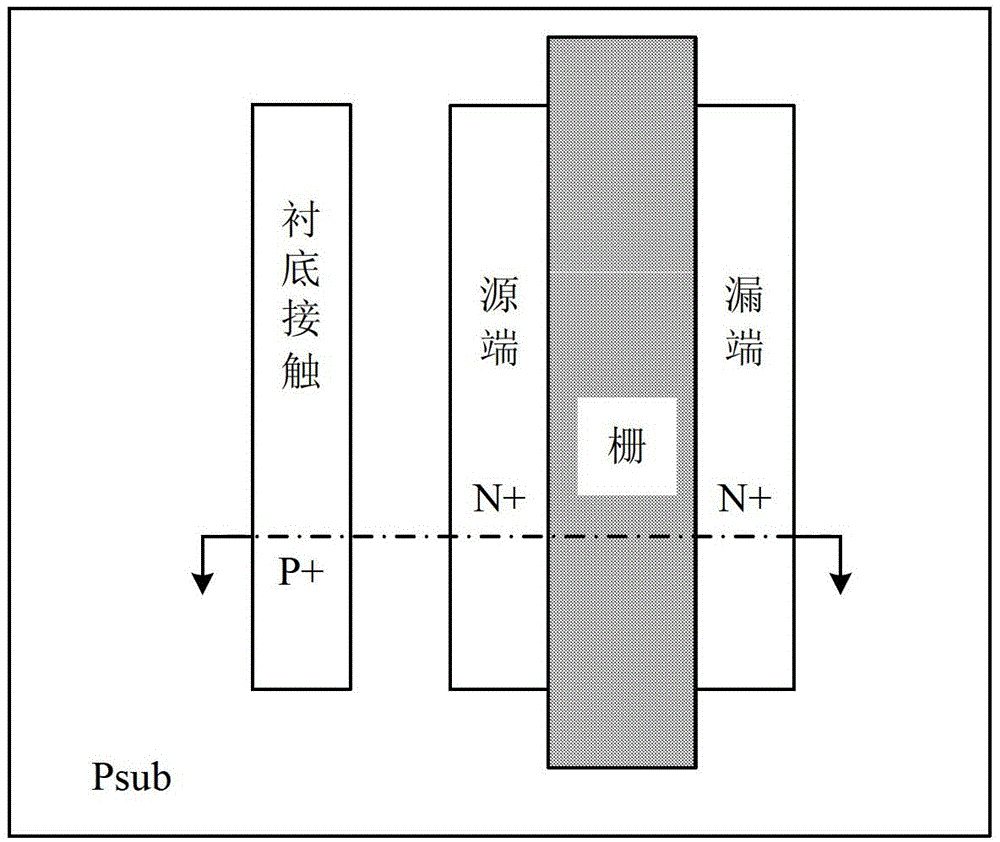

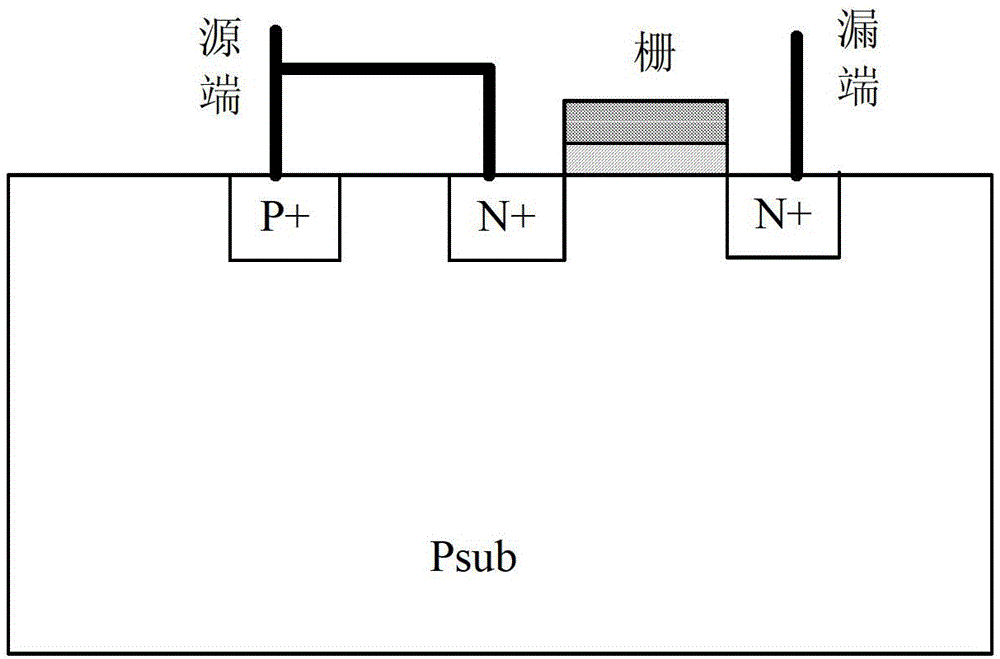

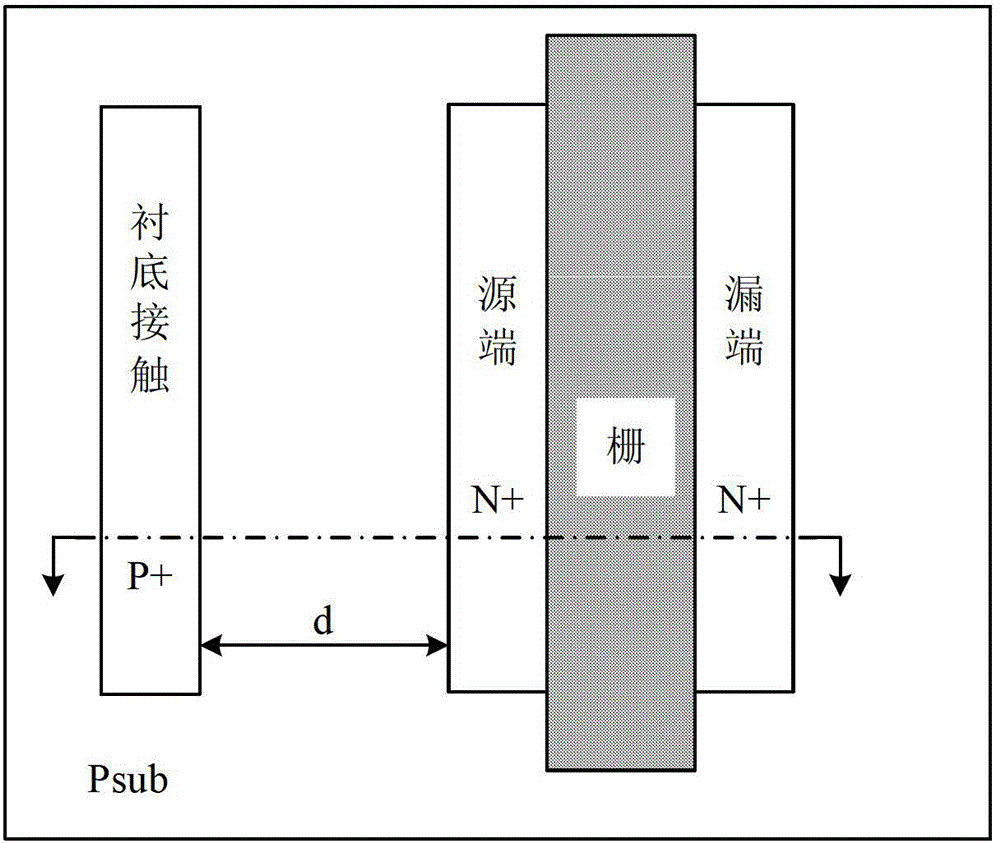

[0020] An NMOS device for ESD protection of integrated circuit chips, such as Figure 5 As shown, it includes a P-type semiconductor substrate, a P-type semiconductor source-substrate contact region, an N-type semiconductor source region, and an N-type semiconductor drain region; the P-type semiconductor source-substrate contact region, the N-type semiconductor source region and the The N-type semiconductor drain regions are all located on the surface of the P-type semiconductor substrate, wherein the P-type source end substrate contact region and the N-type semiconductor source region are connected to the source metal, and the N-type semiconductor drain region is connected to the drain metal; the N-type semiconductor drain region is connected to the drain metal; The semiconductor source region is located between the contact region of the P-type semiconductor source end substrate and the N-type semiconductor drain region, and the surface of the P-type semiconductor substrate be...

specific Embodiment approach 2

[0022] A PMOS device for ESD protection of integrated circuit chips, such as Image 6 As shown, it includes an N-type semiconductor substrate, an N-type semiconductor source-substrate contact region, a P-type semiconductor source region, and an N-type semiconductor drain region; the N-type semiconductor source-substrate contact region, the P-type semiconductor source region and the The P-type semiconductor drain regions are all located on the surface of the N-type semiconductor substrate, wherein the N-type source end substrate contact region and the P-type semiconductor source region are connected to the source metal, and the P-type semiconductor drain region is connected to the drain metal; the P-type semiconductor drain region is connected to the drain metal; The semiconductor source region is located between the contact region of the N-type semiconductor source end substrate and the P-type semiconductor drain region, and the surface of the N-type semiconductor substrate bet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More