Patents

Literature

45results about How to "Reduce effective width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

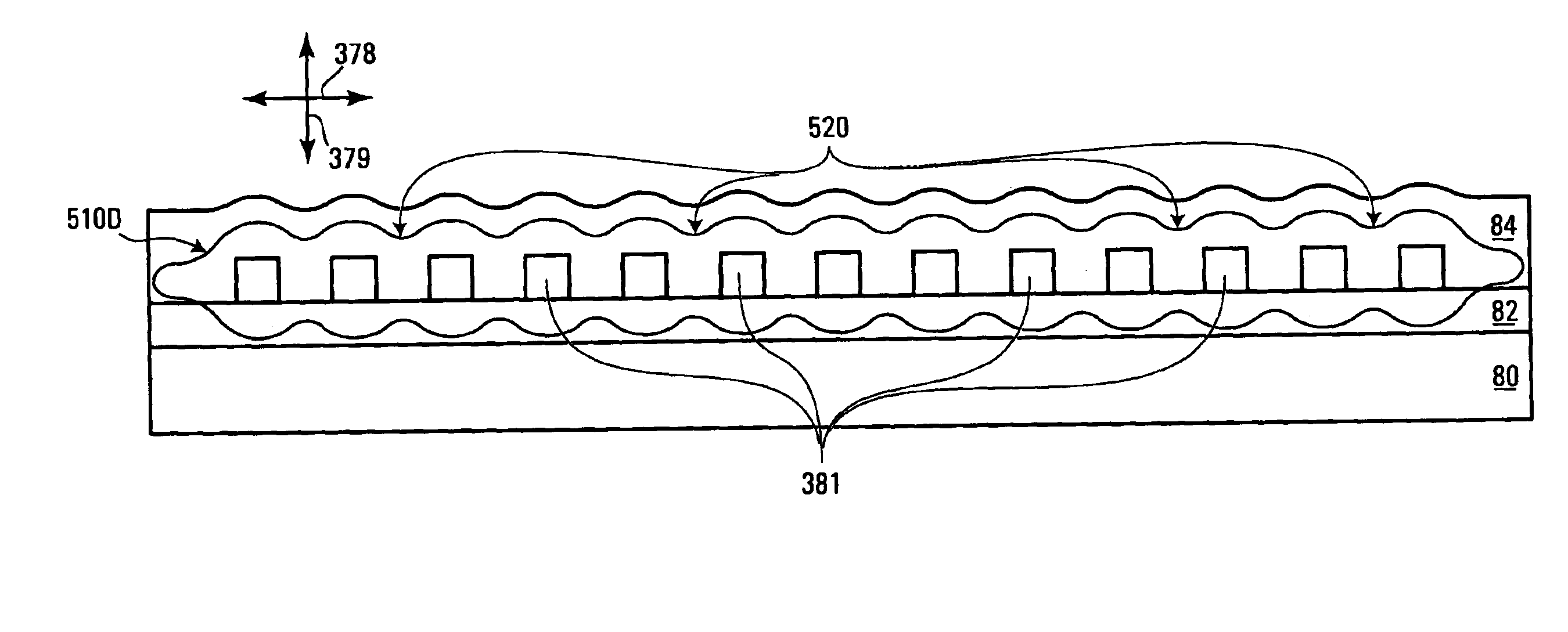

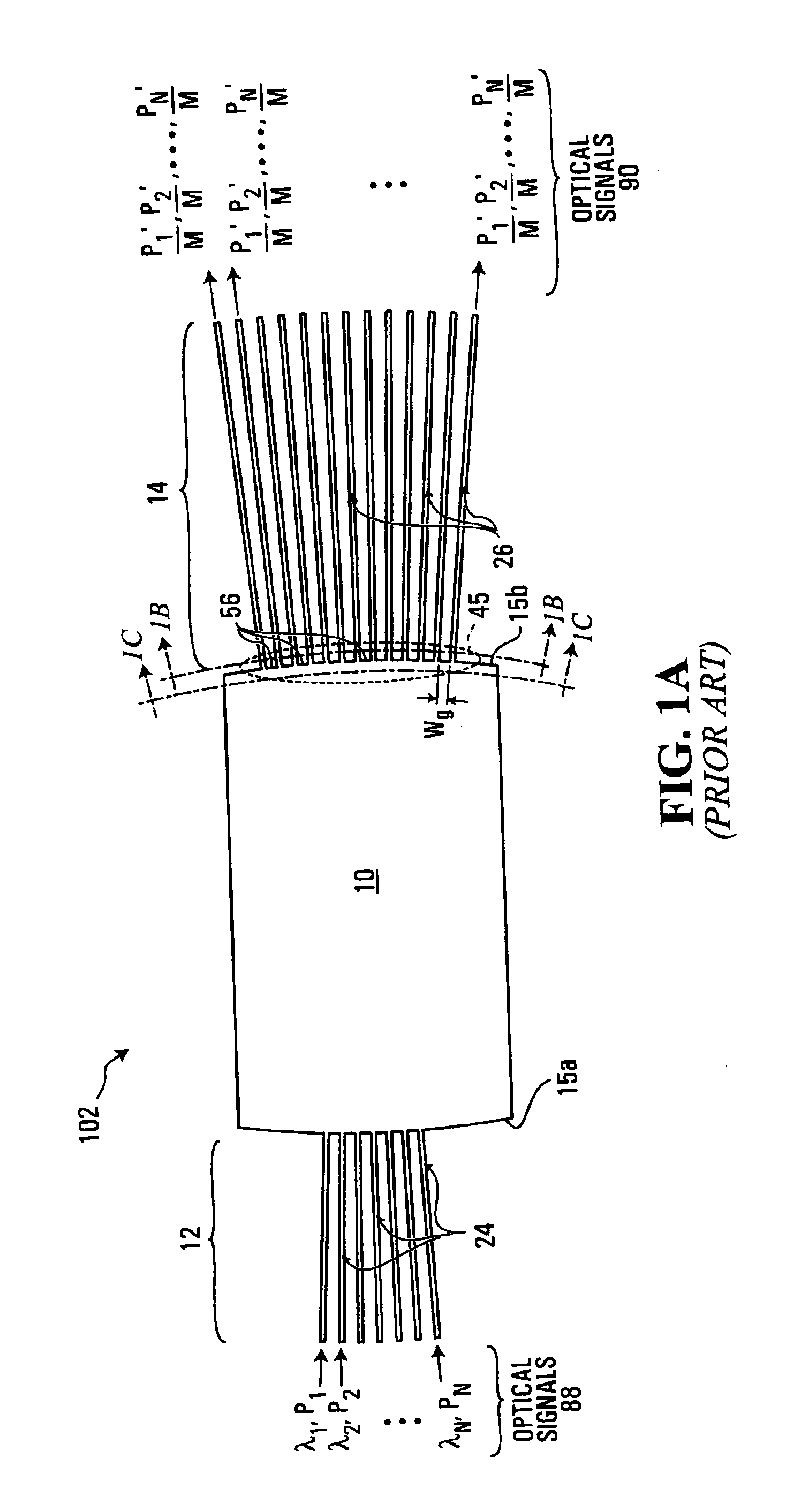

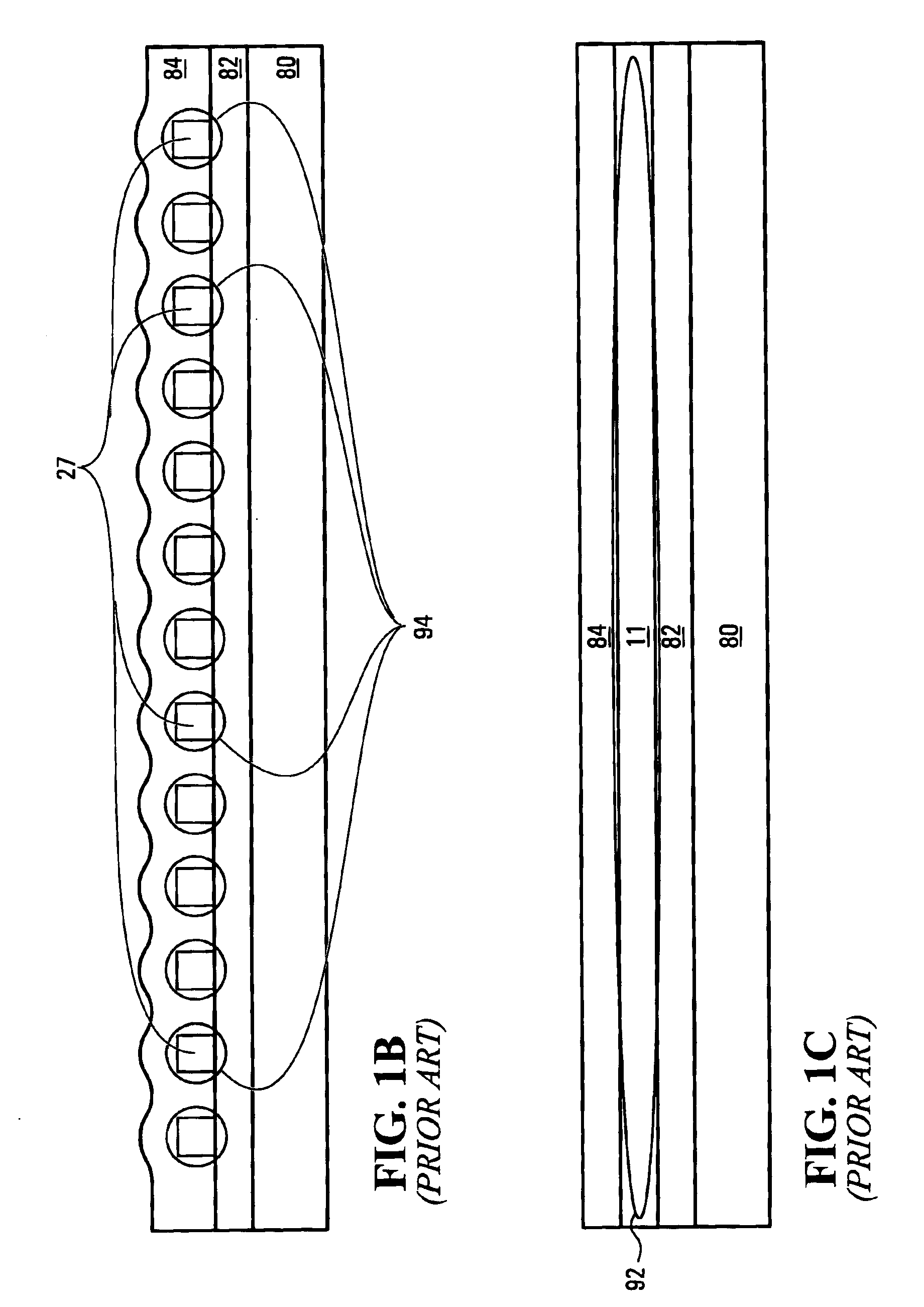

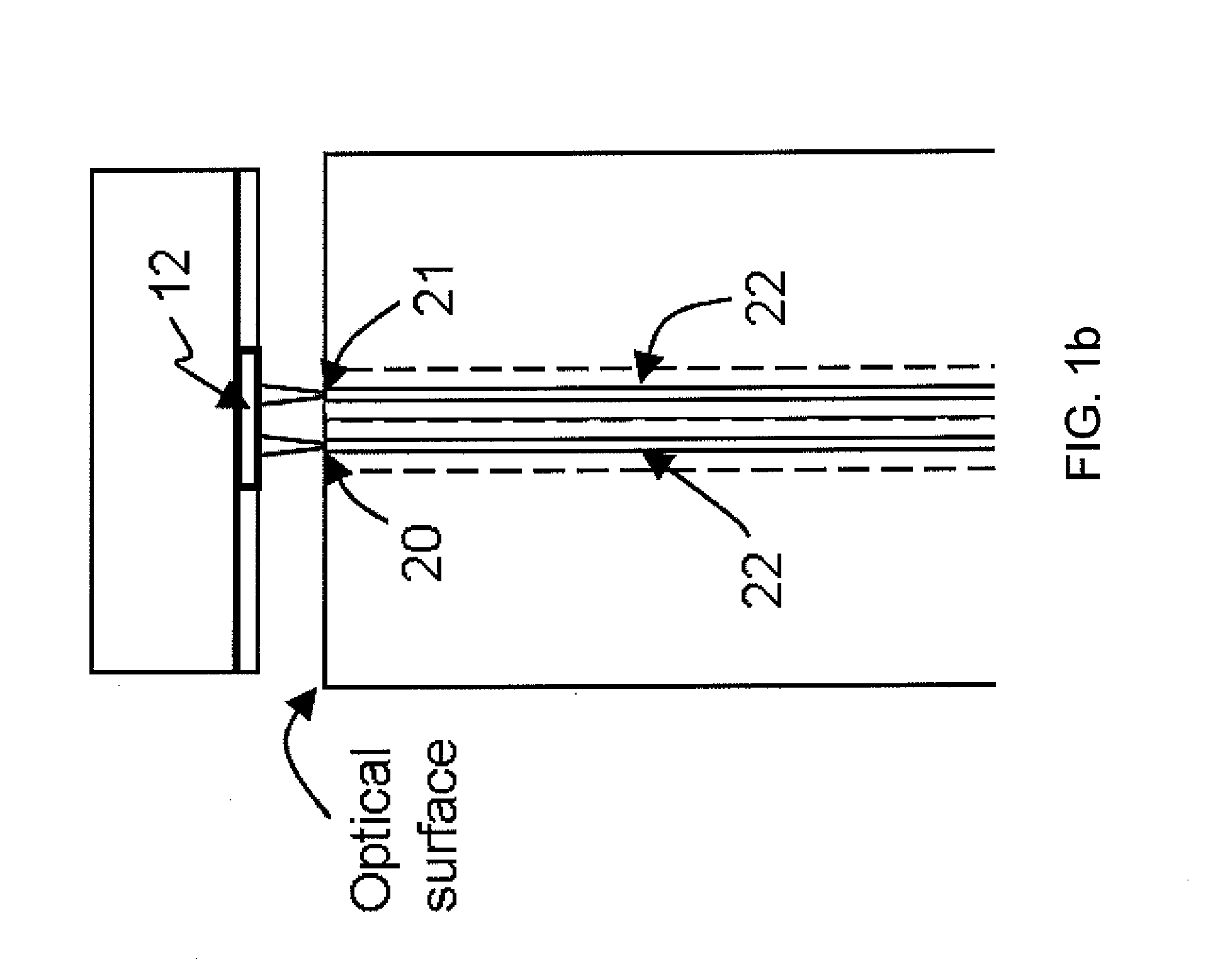

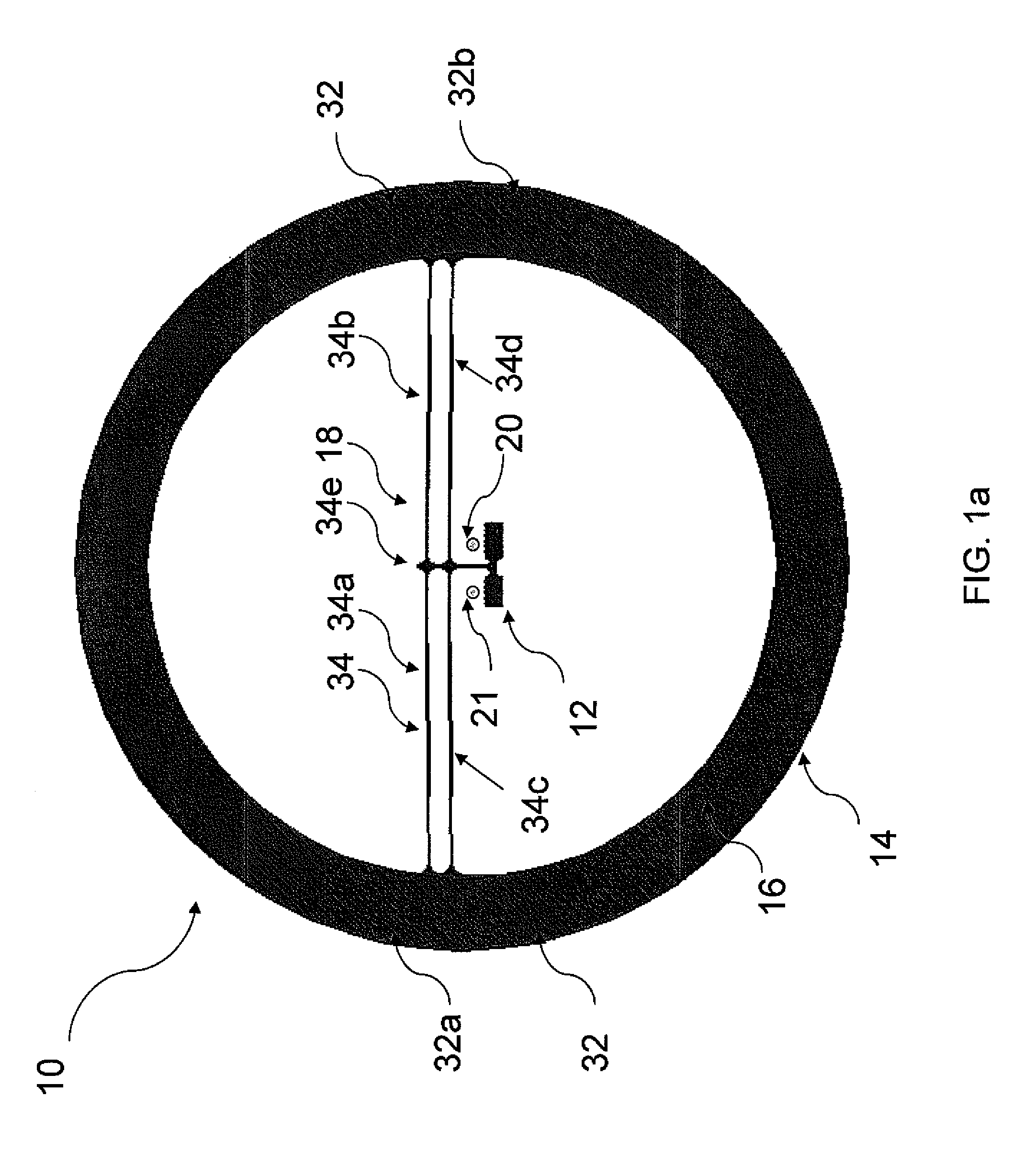

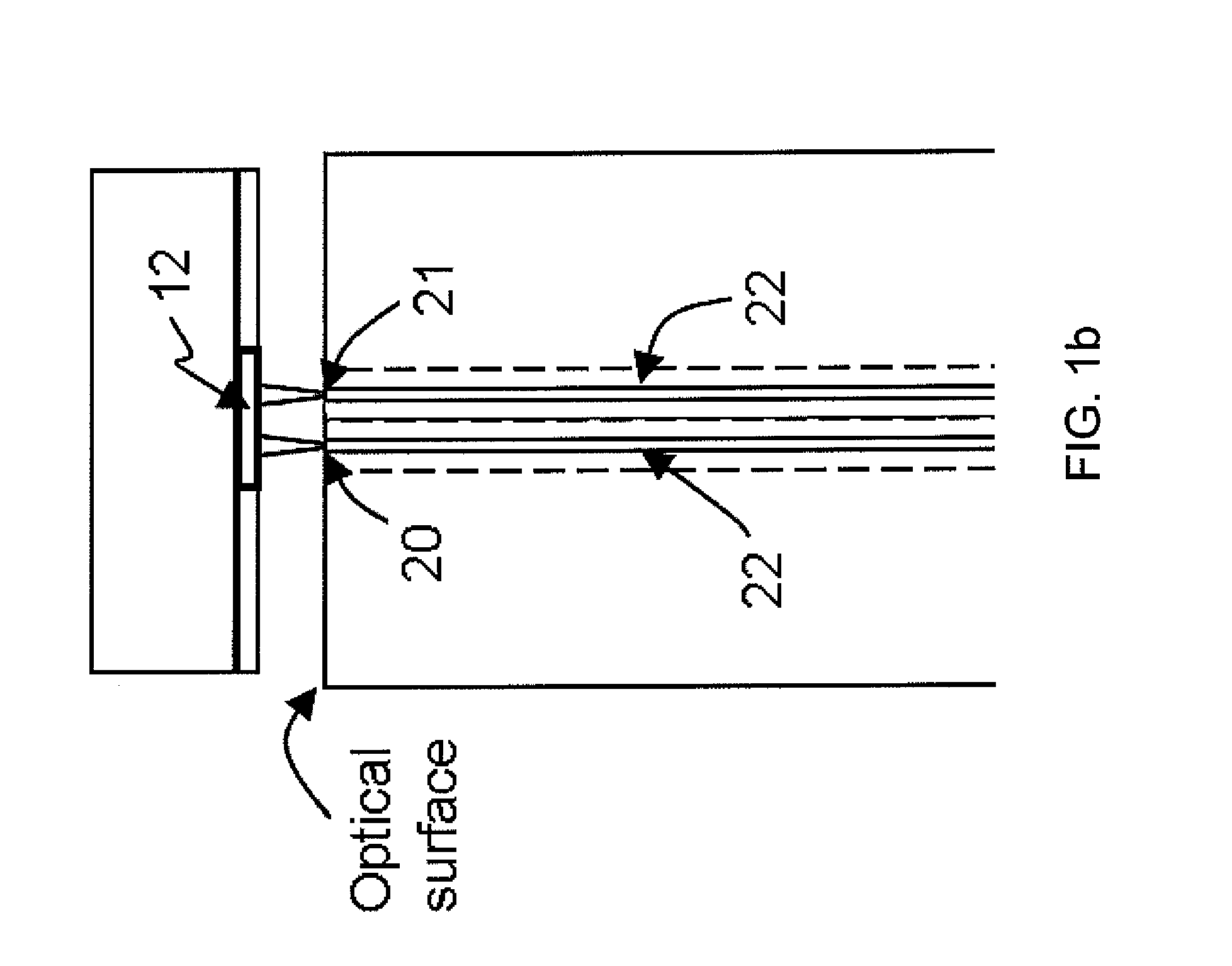

Optical coupling arrangement having low coupling loss and high production yield

InactiveUS6892004B1Effective width of gapCoupling loss of couplingCoupling light guidesCoupling lossMultiplexer

An optical coupling arrangement has a first transition region having a plurality of first segmented waveguides and a plurality of transverse segments of alternating indices of refraction with at least some of the transverse segments traversing the first segmented waveguides. The first segmented waveguides are formed by core segments in some of the transverse segments. The arrangement may also have a second transition region having a plurality of second segmented waveguides each aligned with a respective one of the first segmented waveguides. The arrangement is manufactured with a high production yield and is used in an optical coupling device for combining / splitting optical signals to reduce the insertion loss. The optical coupling device is also used in other devices such as Mach-Zehnder devices and arrayed waveguide grating demultiplexers / multiplexers.

Owner:YU GUOMIN

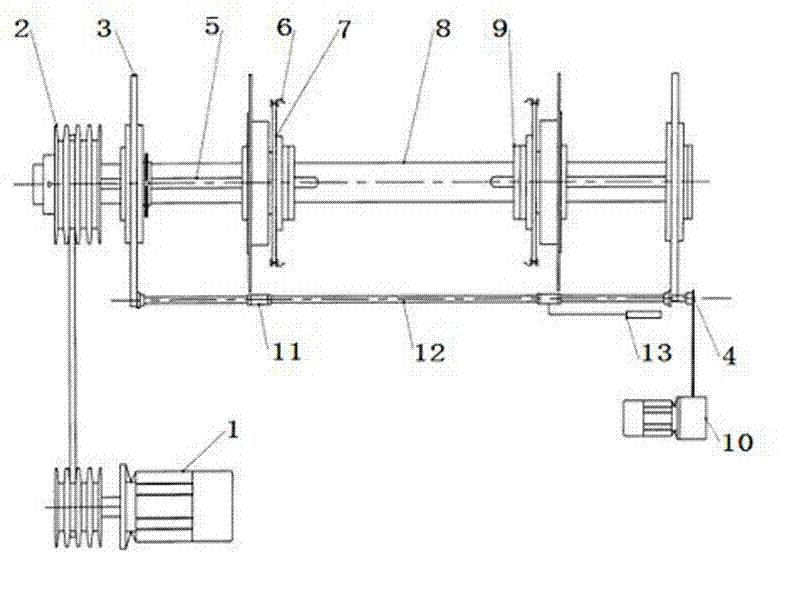

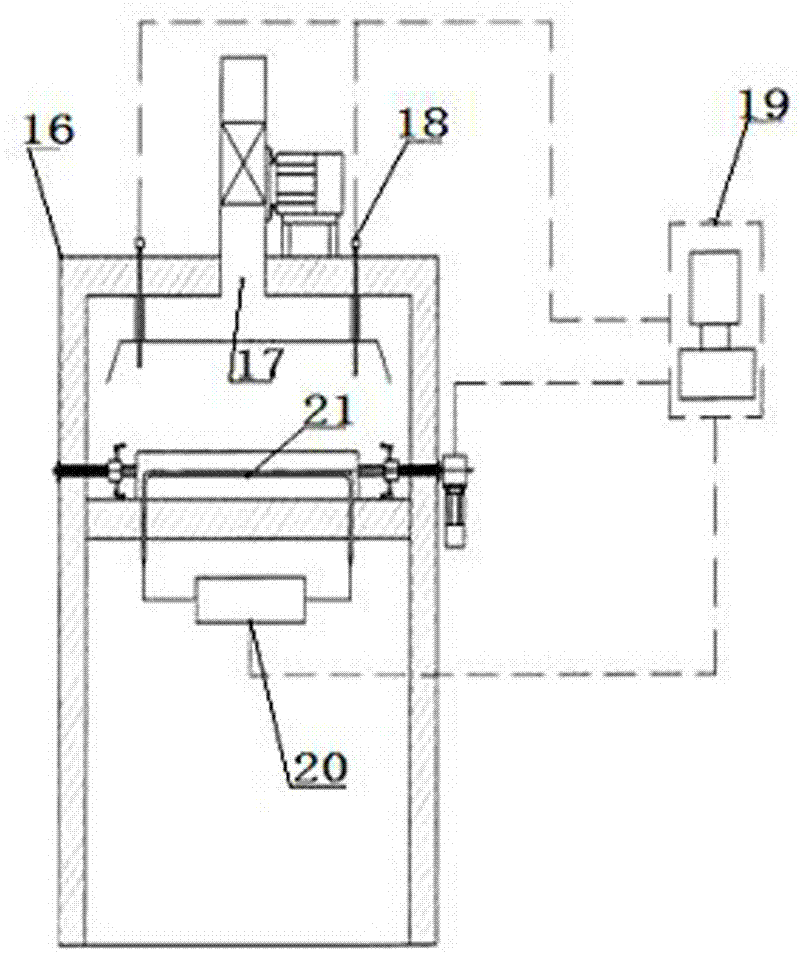

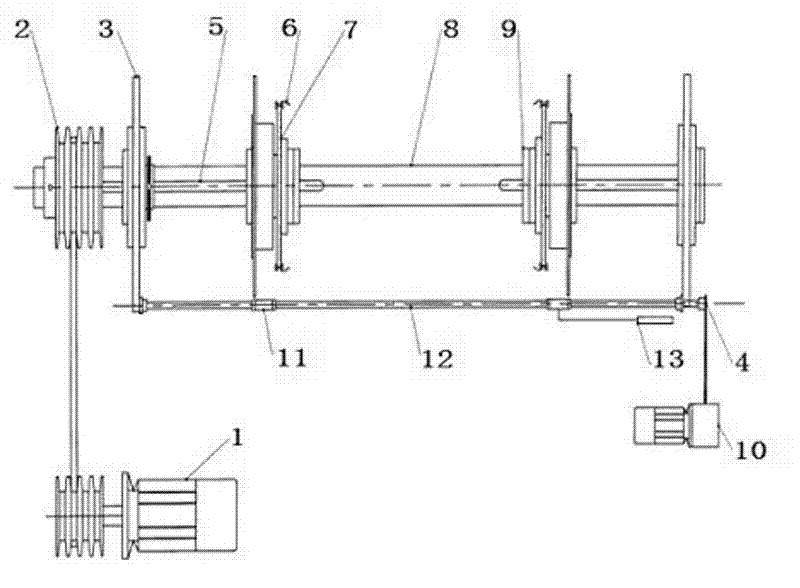

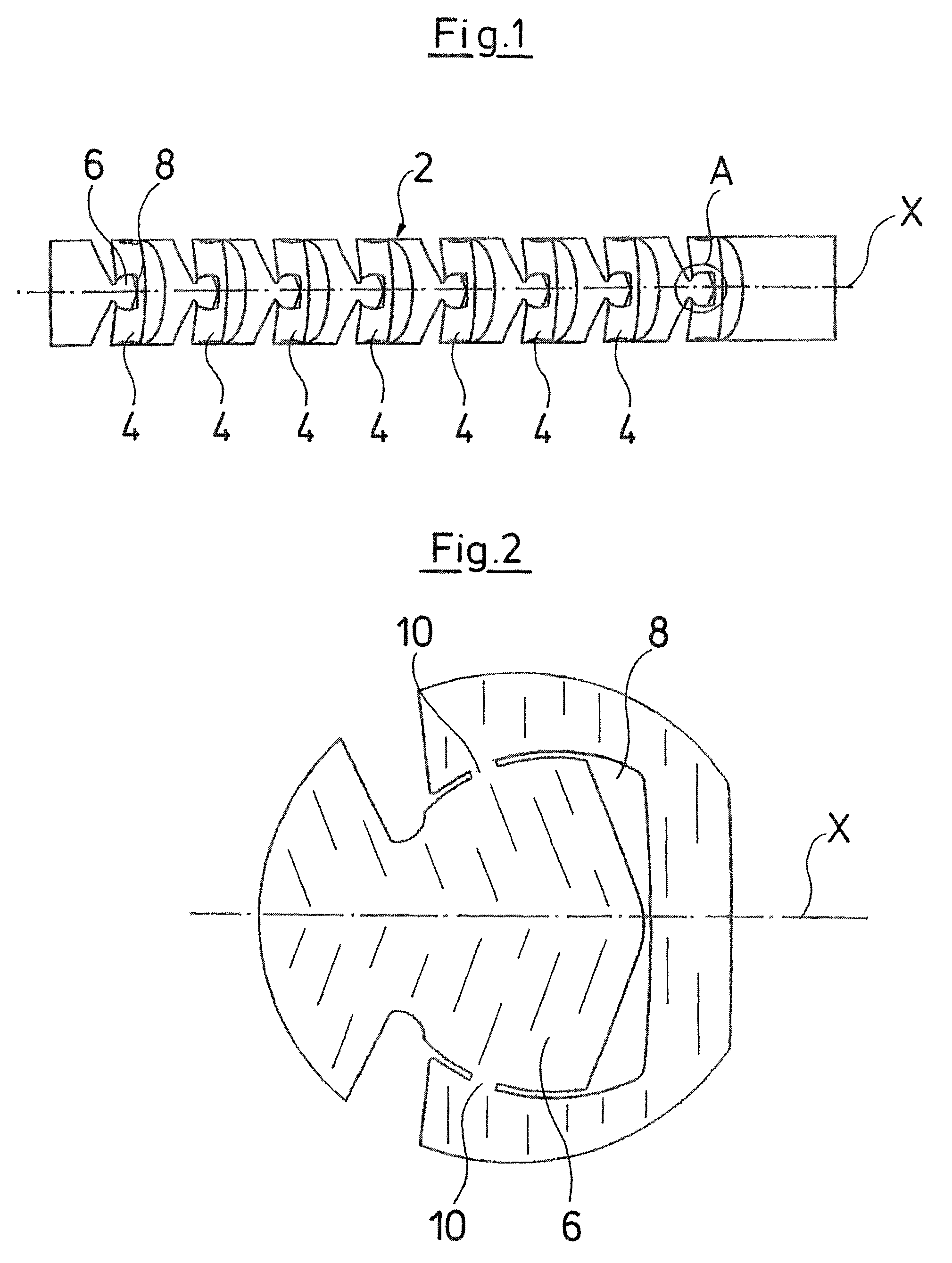

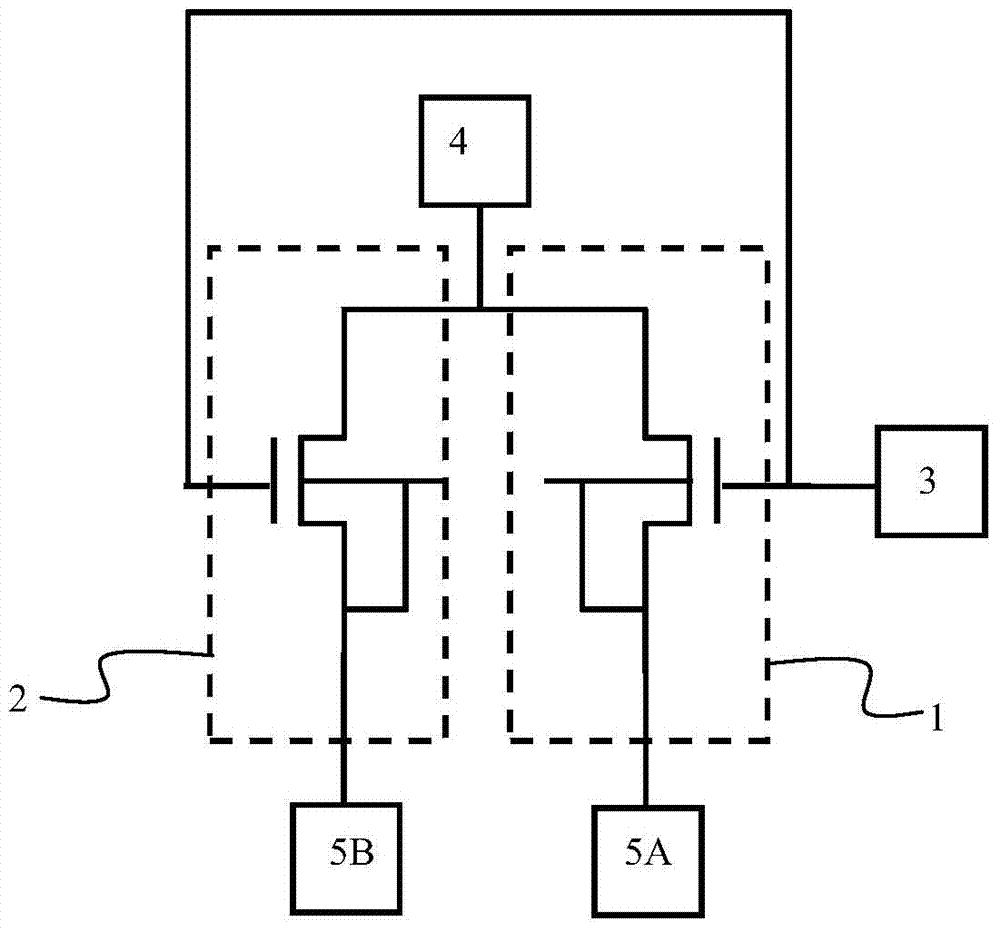

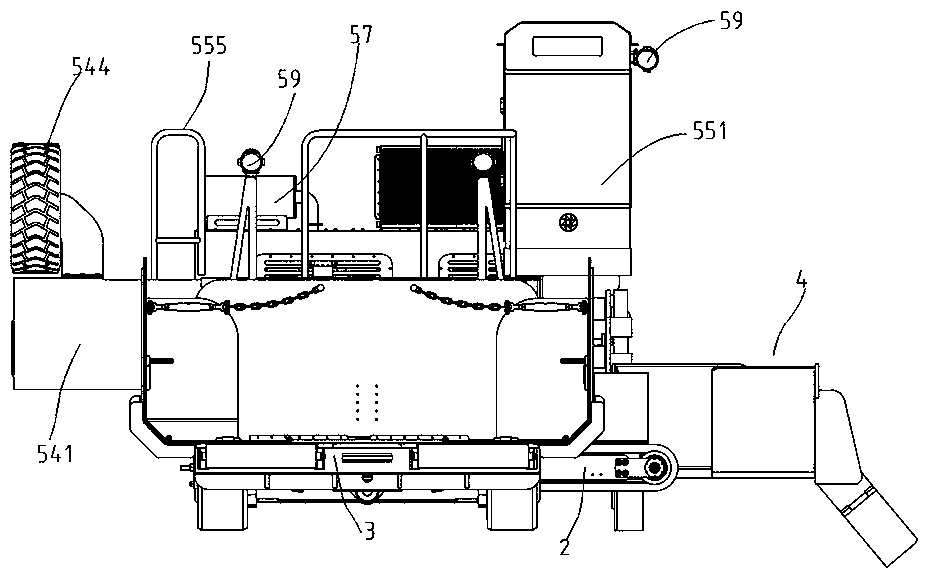

Bidirectional drawing machine for polymide films

The invention provides a bidirectional drawing machine for polymide films; the bidirectional drawing machine comprises a needle plate type chain mechanism, a drawing machine box body, a vertical chain and transmission mechanism, an automatic expanding mechanism, an automatic closed loop heating system and an inner circulating air bellows, wherein the vertical chain and transmission mechanism comprises a main driving motor, a belt pulley, a main shaft, a guide key and a chain wheel; the automatic expanding mechanism comprises a speed reducing motor, a small chain wheel, a breadth adjusting screw rod, a nut and a sliding seat; the electric heating system comprises an embedded type electric heater, a temperature sensor, a temperature controller and an upper computer; by adopting the bidirectional drawing machine, the films are uniformly stressed during stretching and have consistent thickness and high quality, the space of a heating area is reduced, the heating power is minimized, the electric energy is saved, and the exhaust emission is reduced; and therefore, the bidirectional drawing machine is more environmental-friendly.

Owner:万达集团股份有限公司

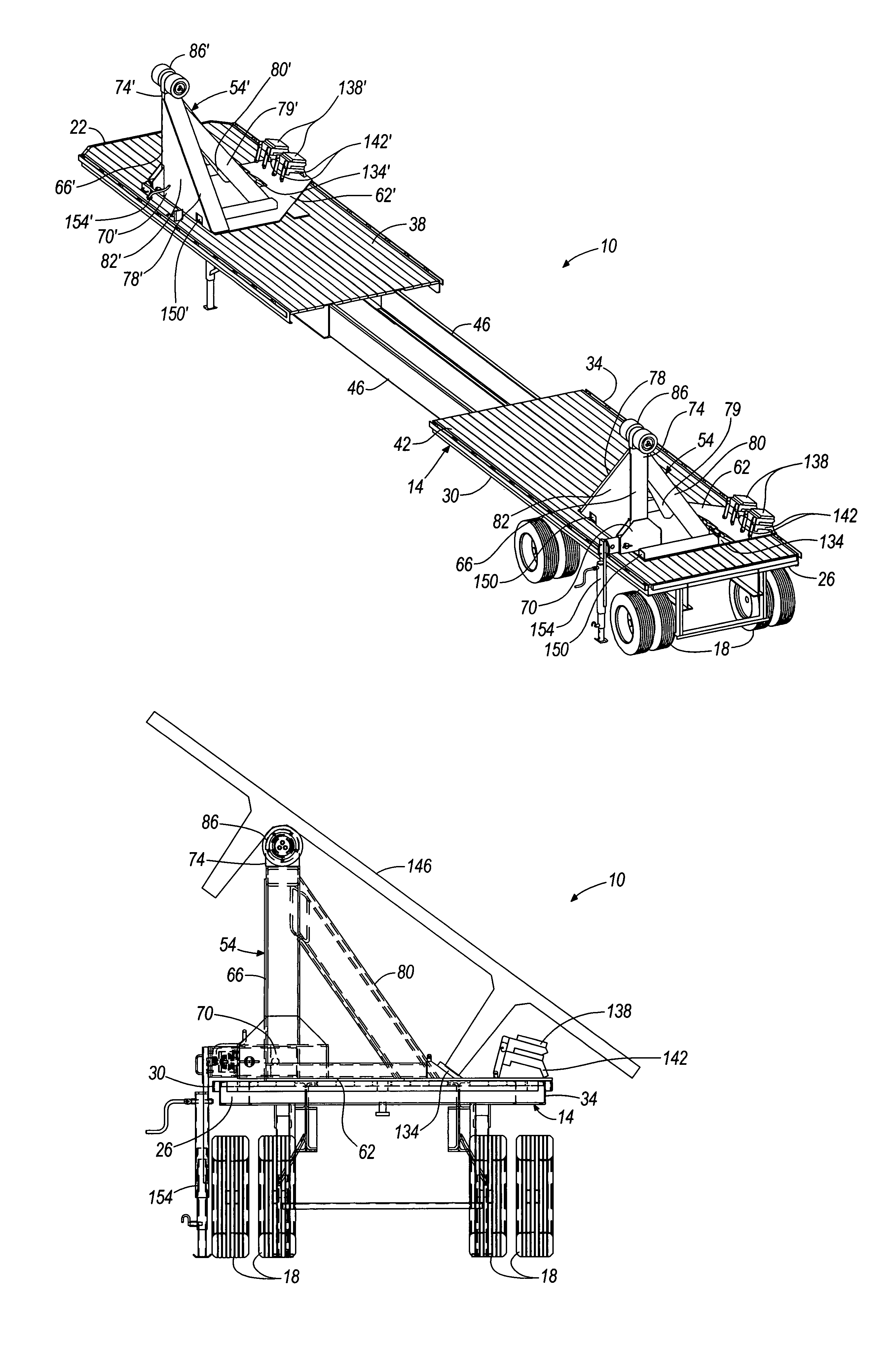

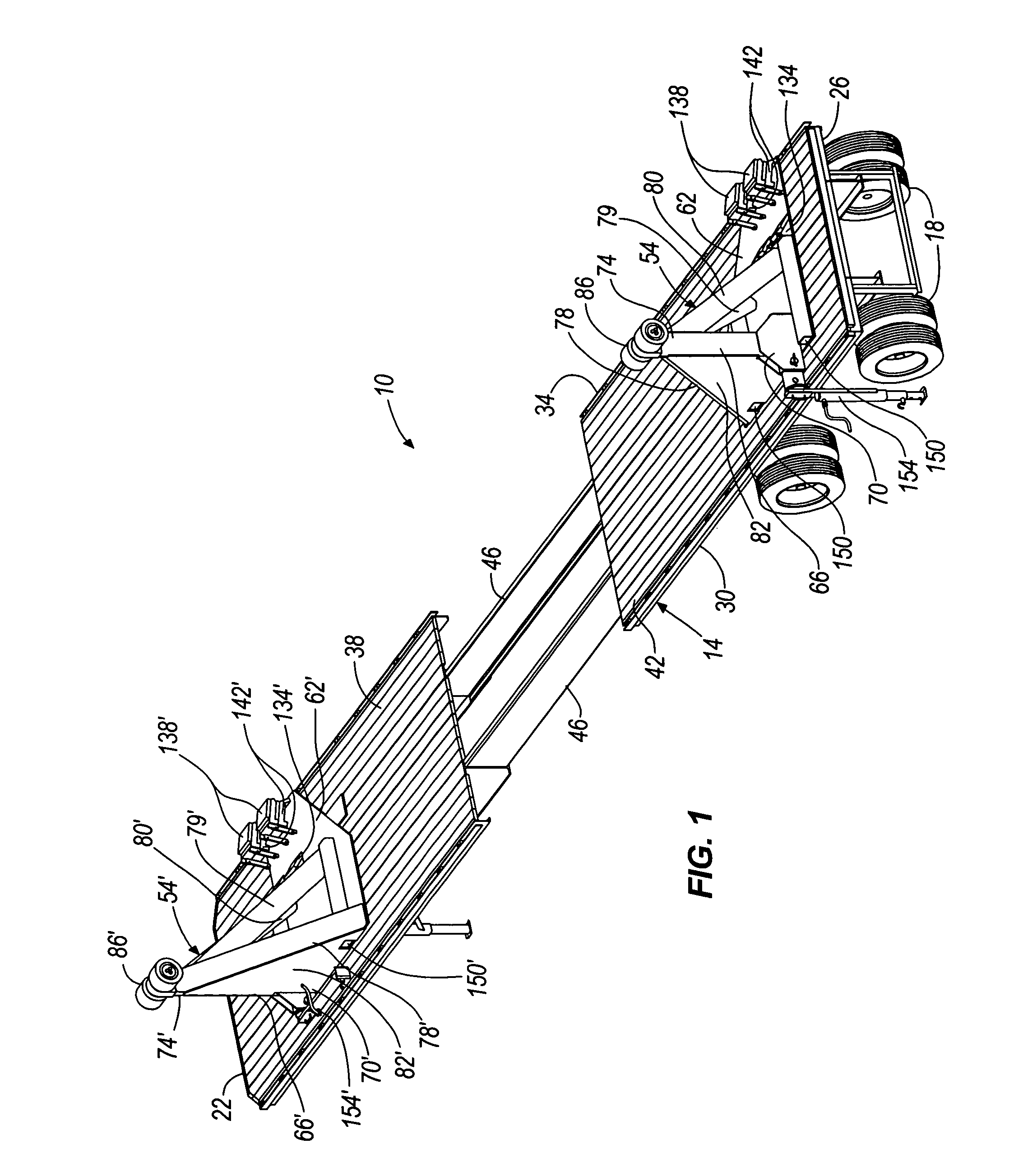

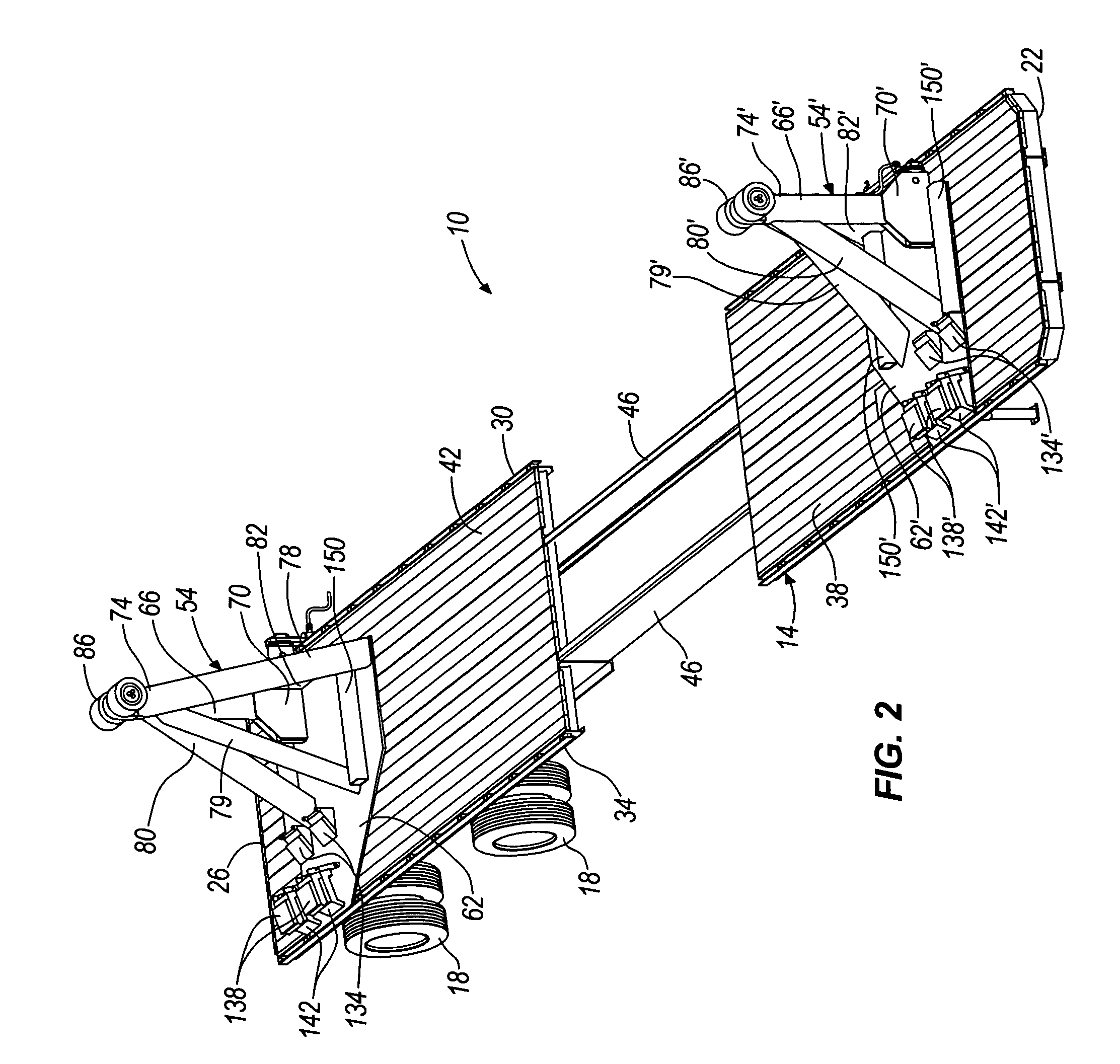

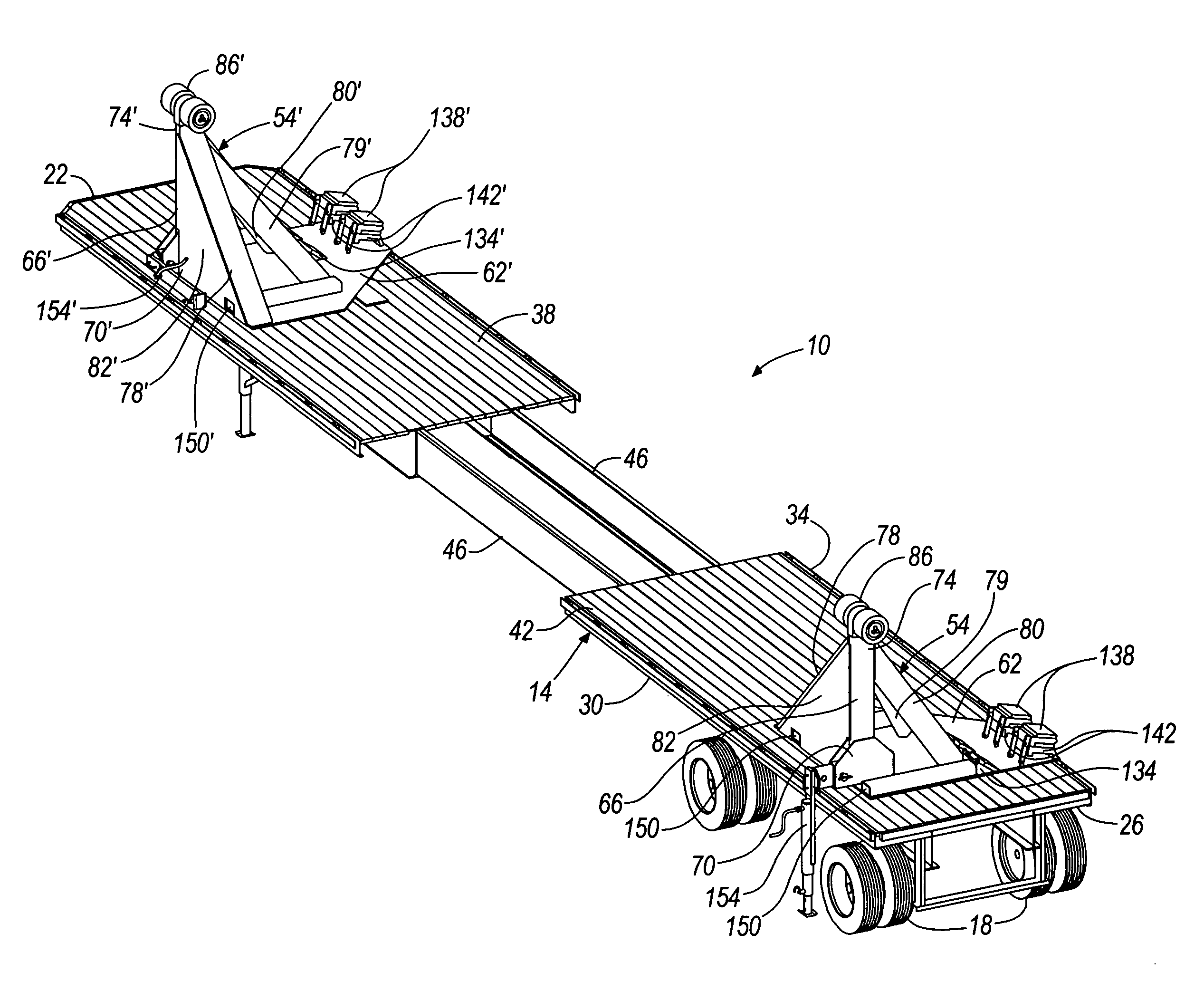

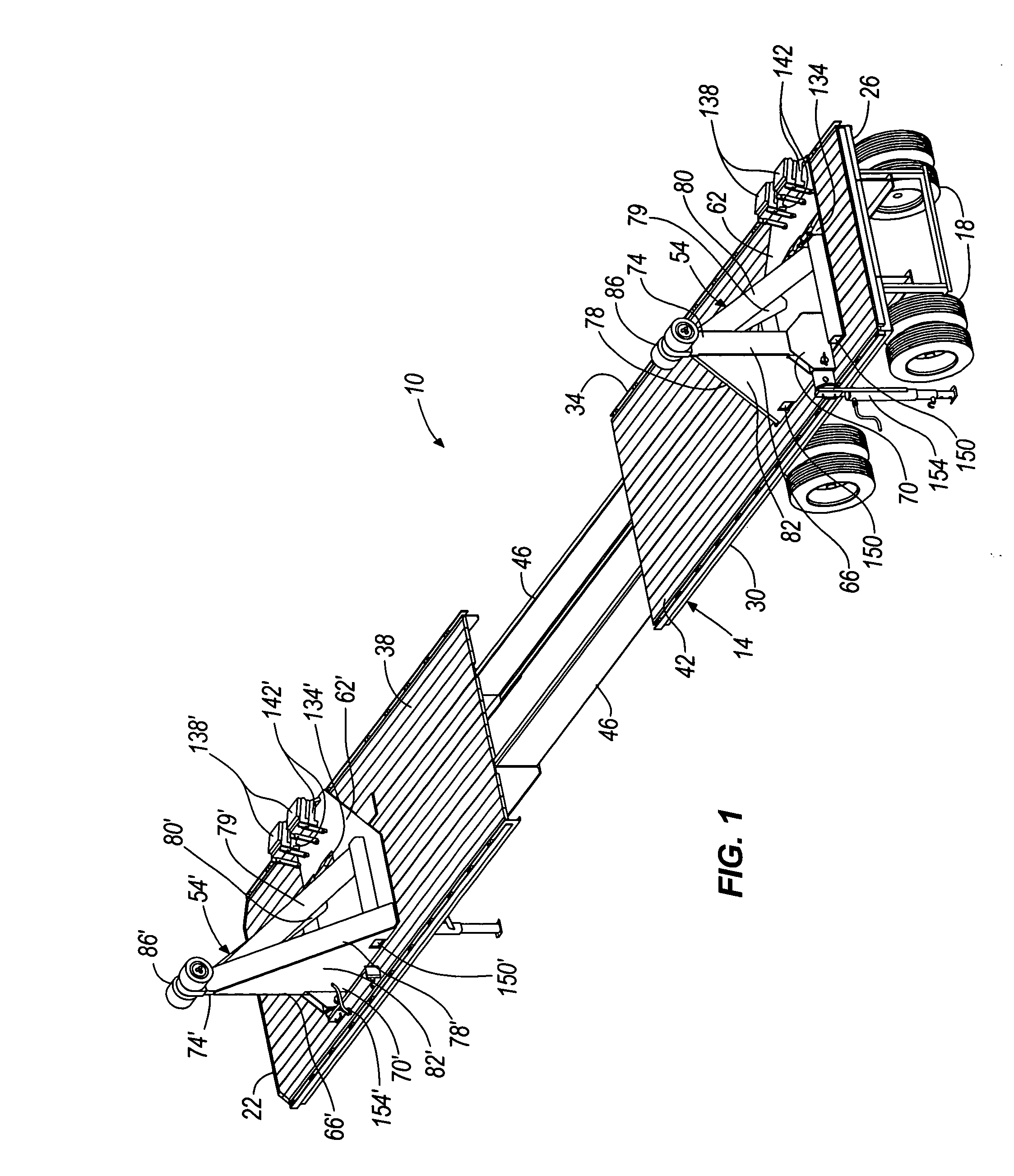

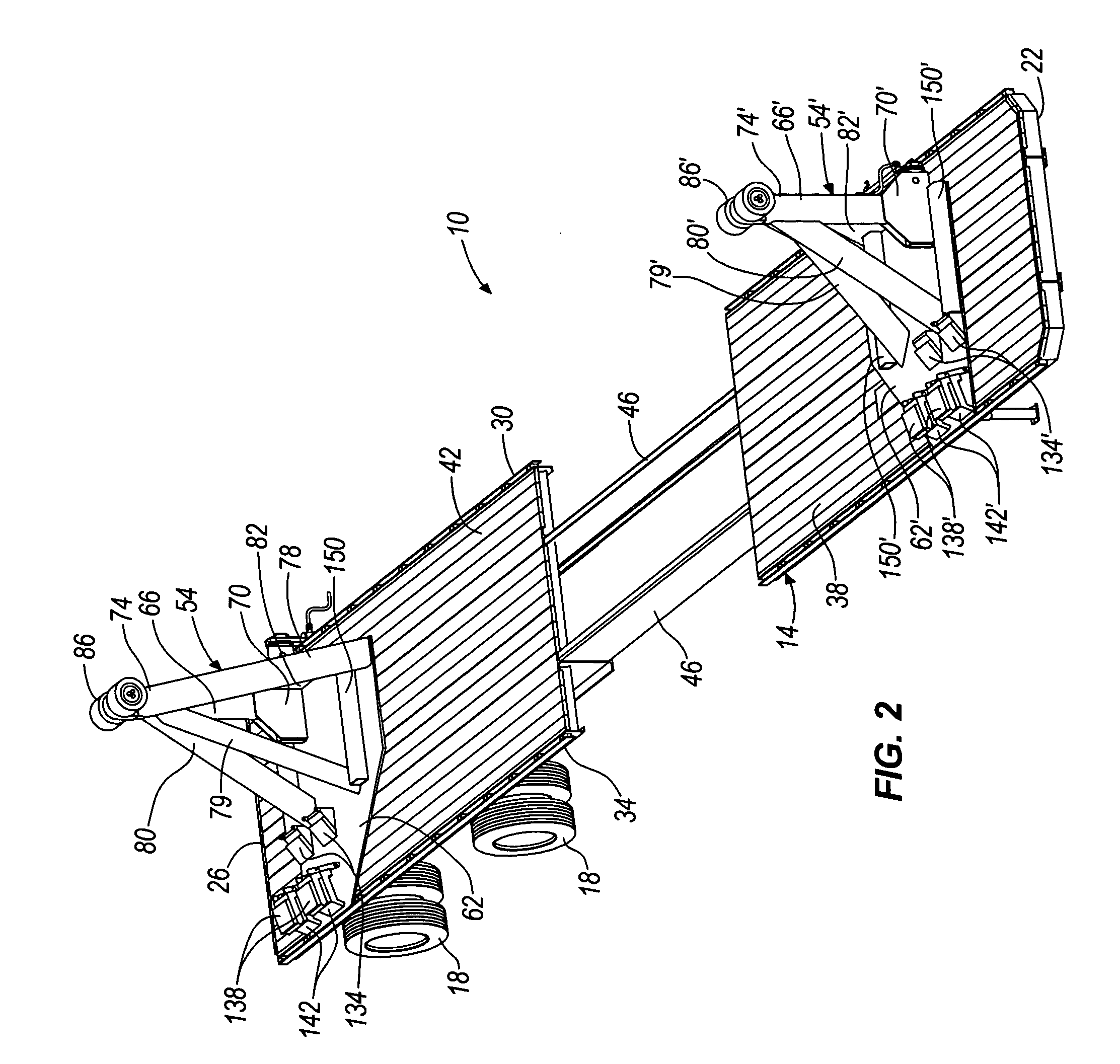

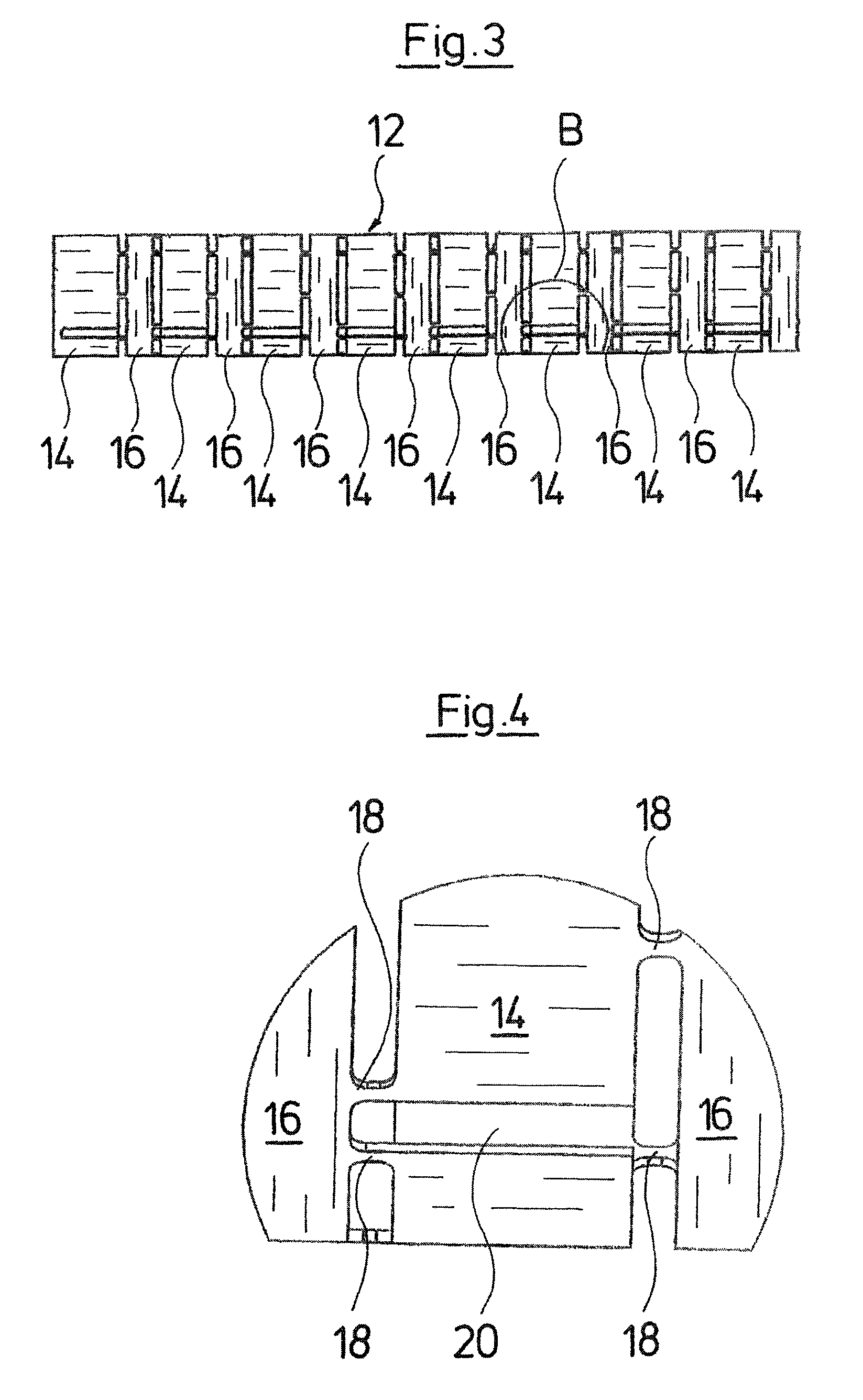

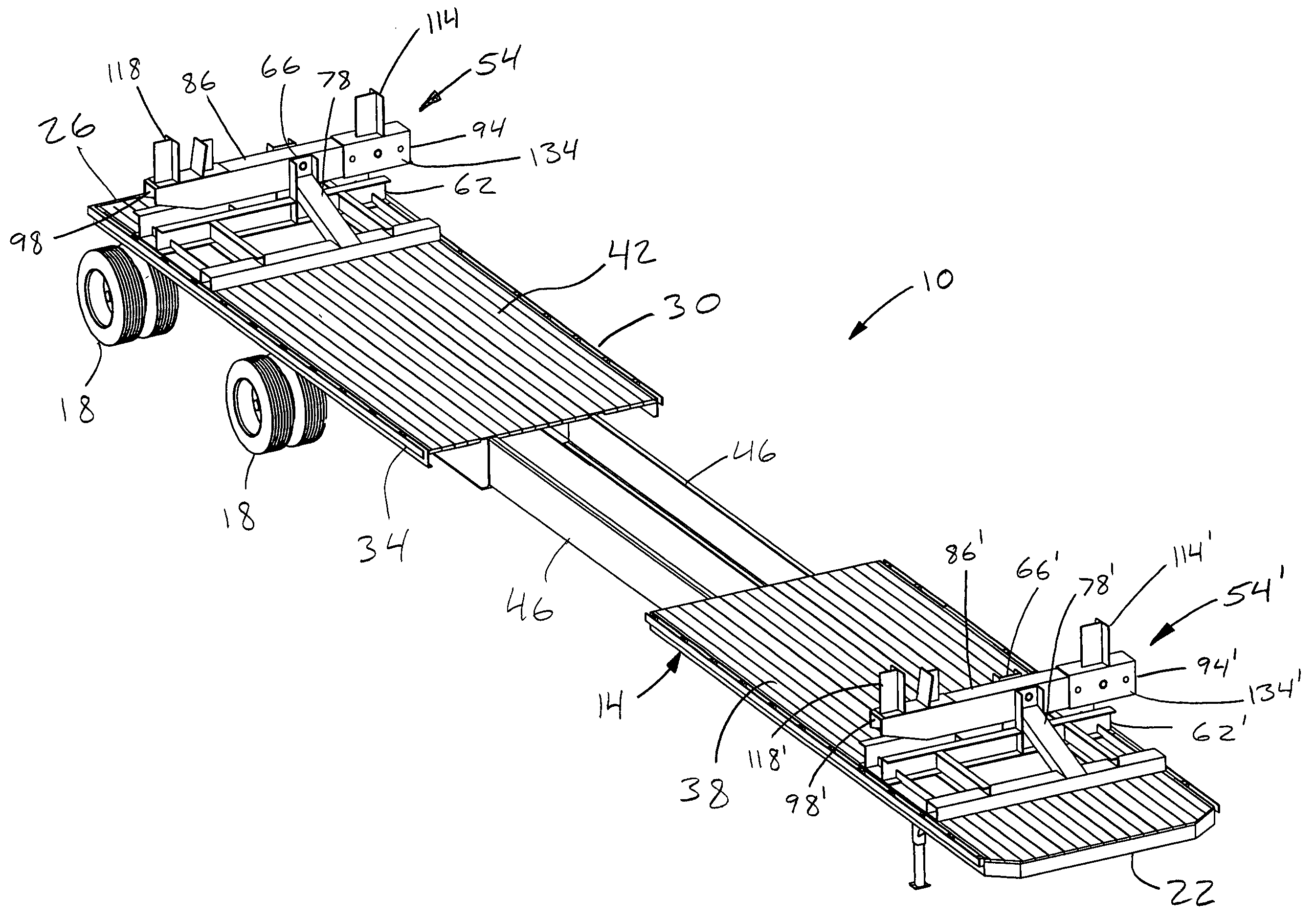

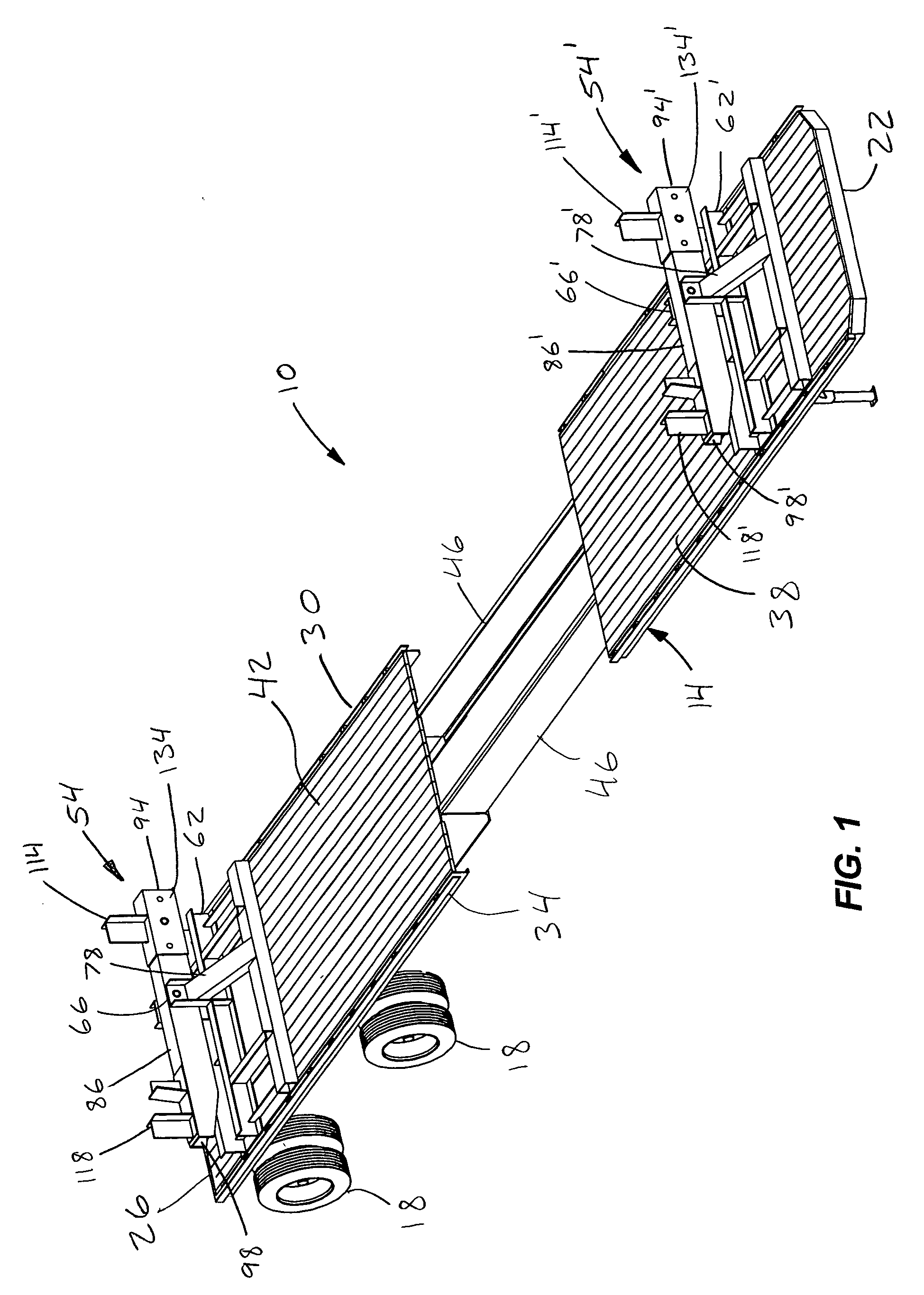

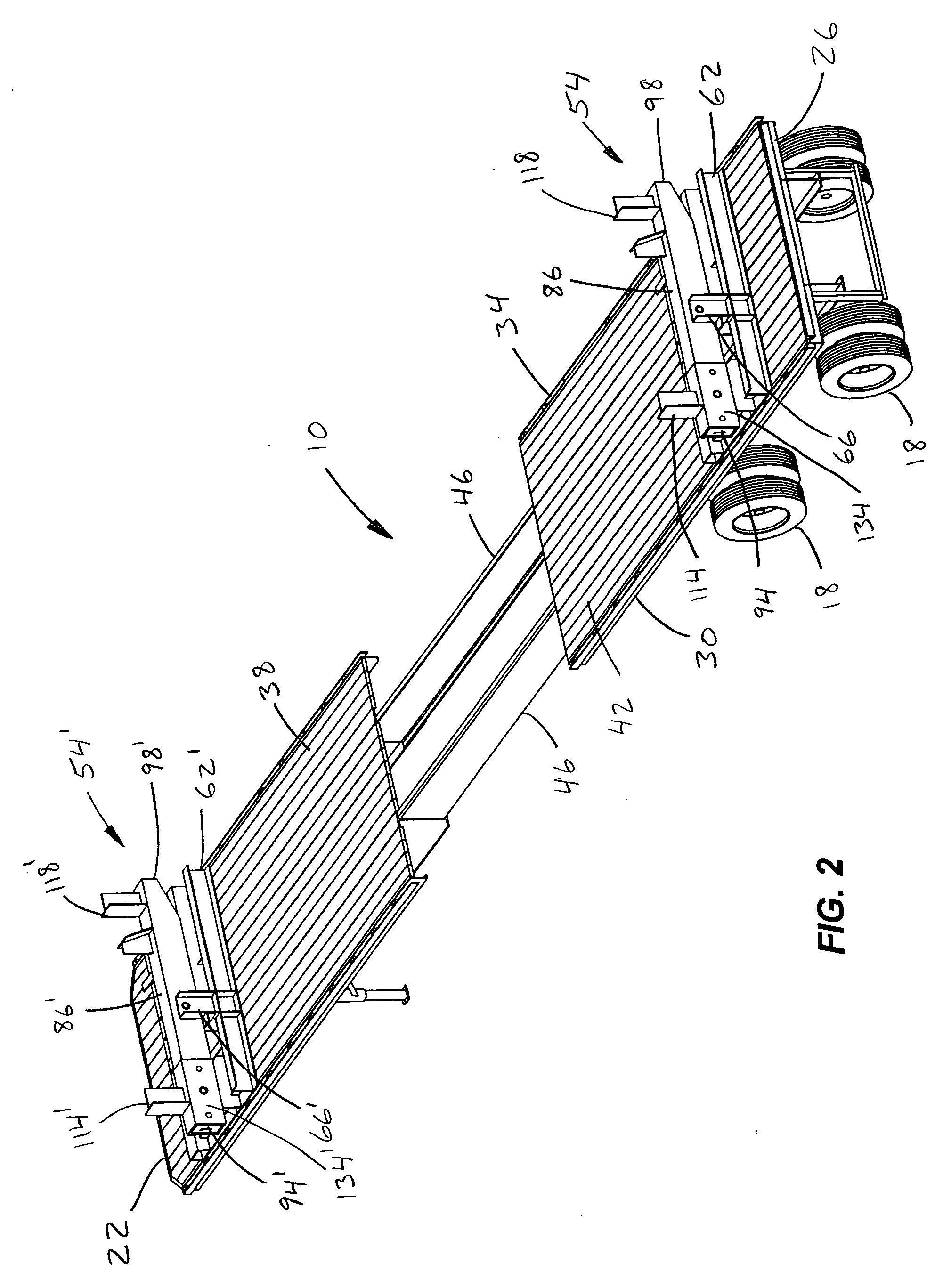

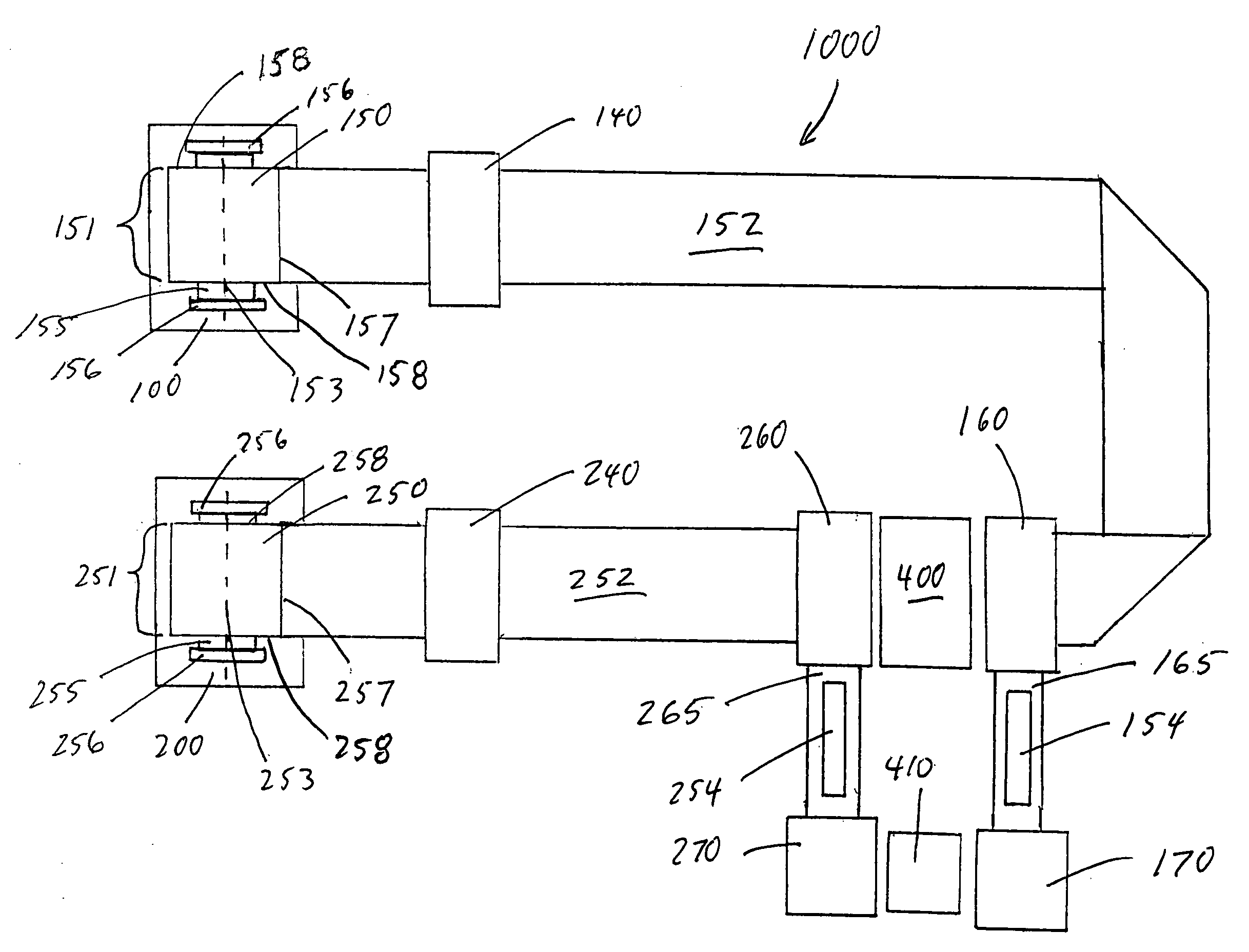

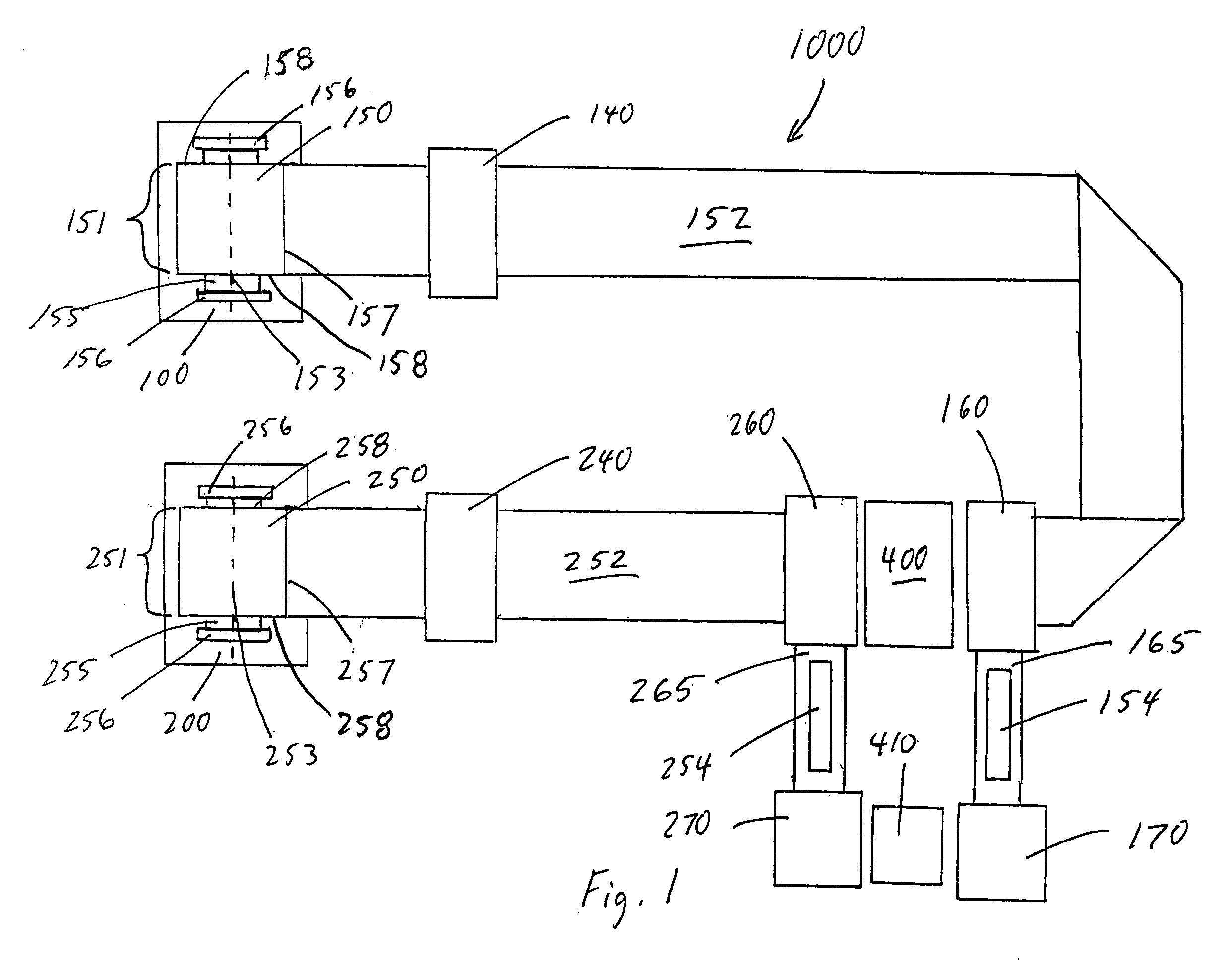

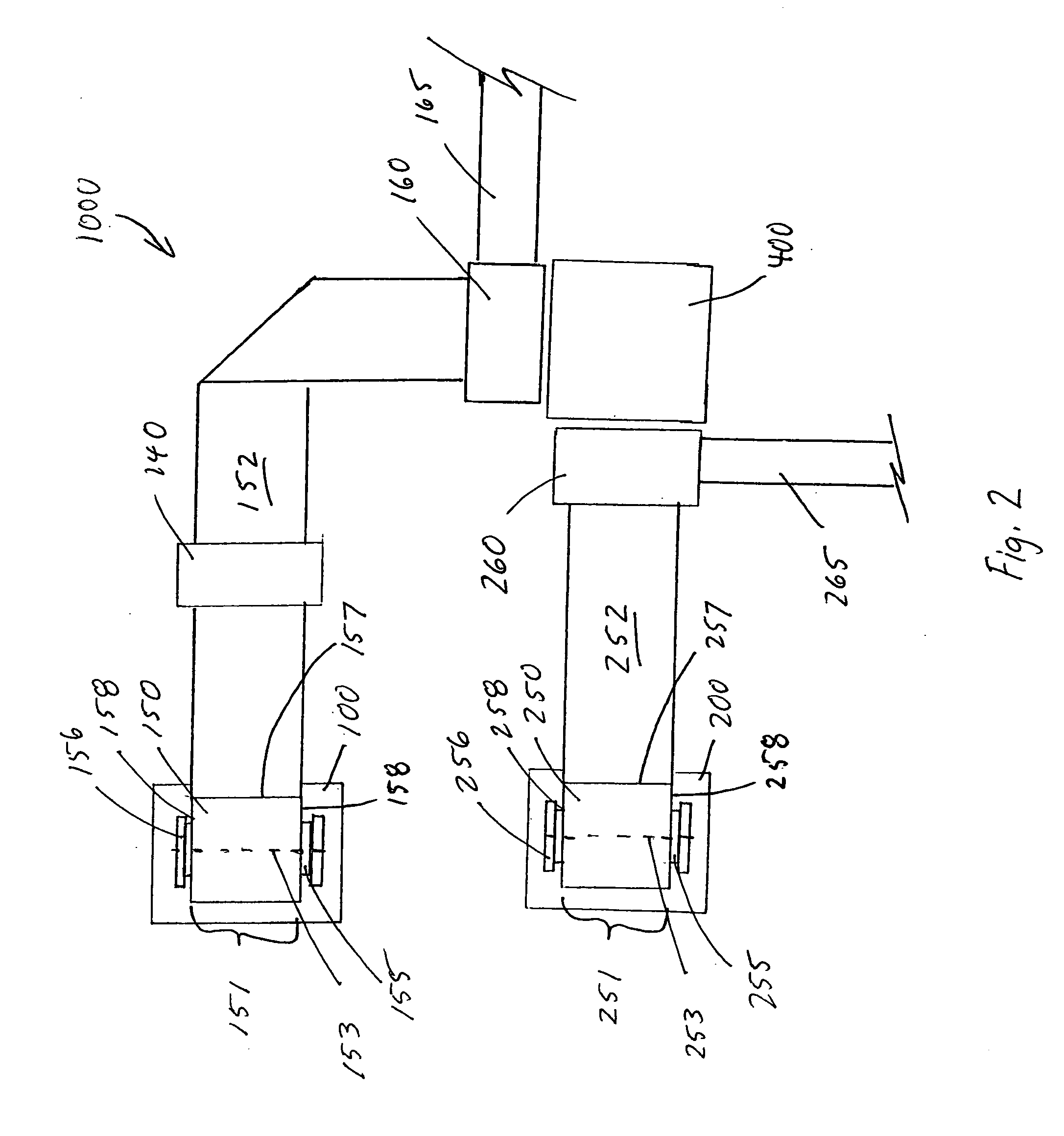

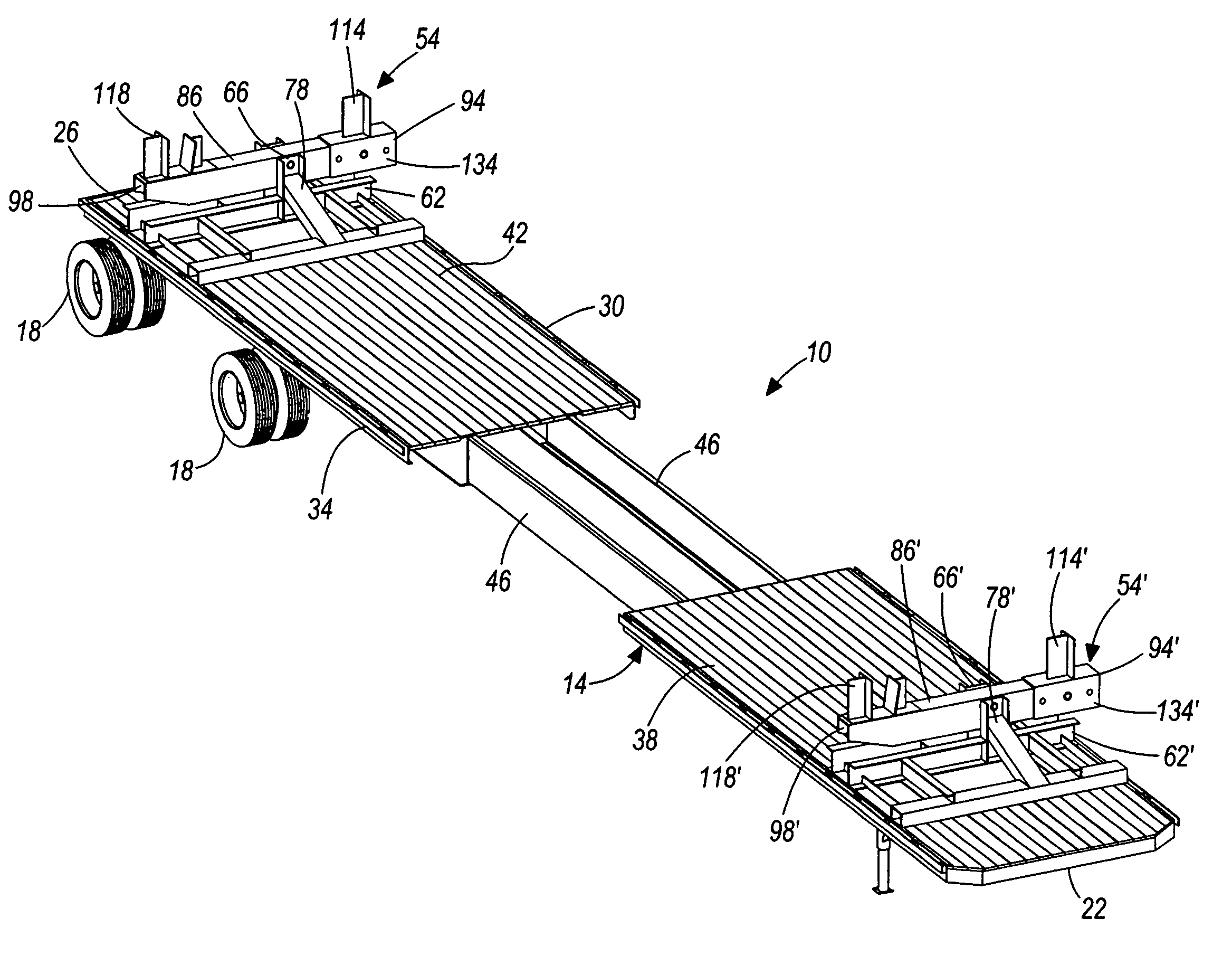

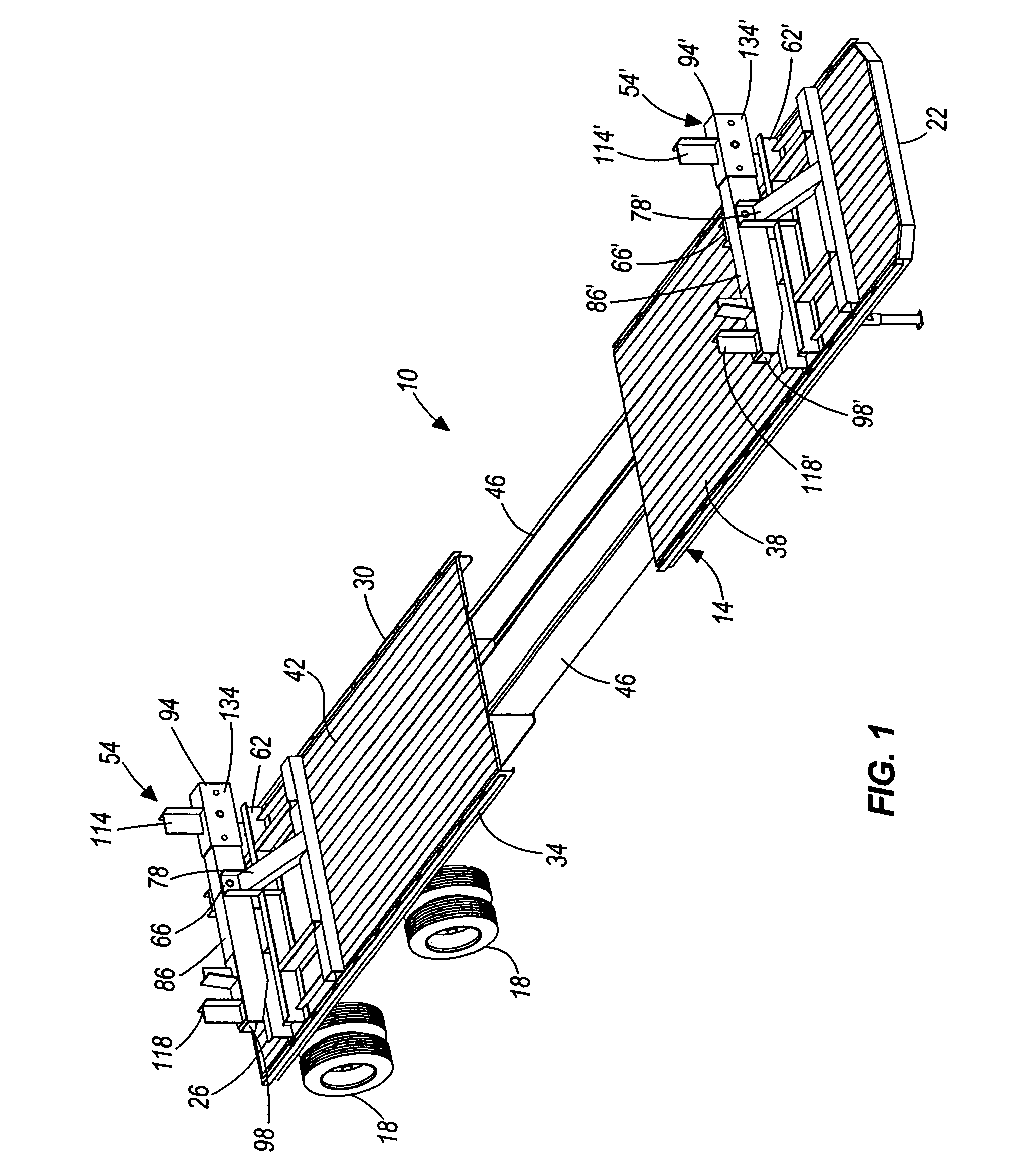

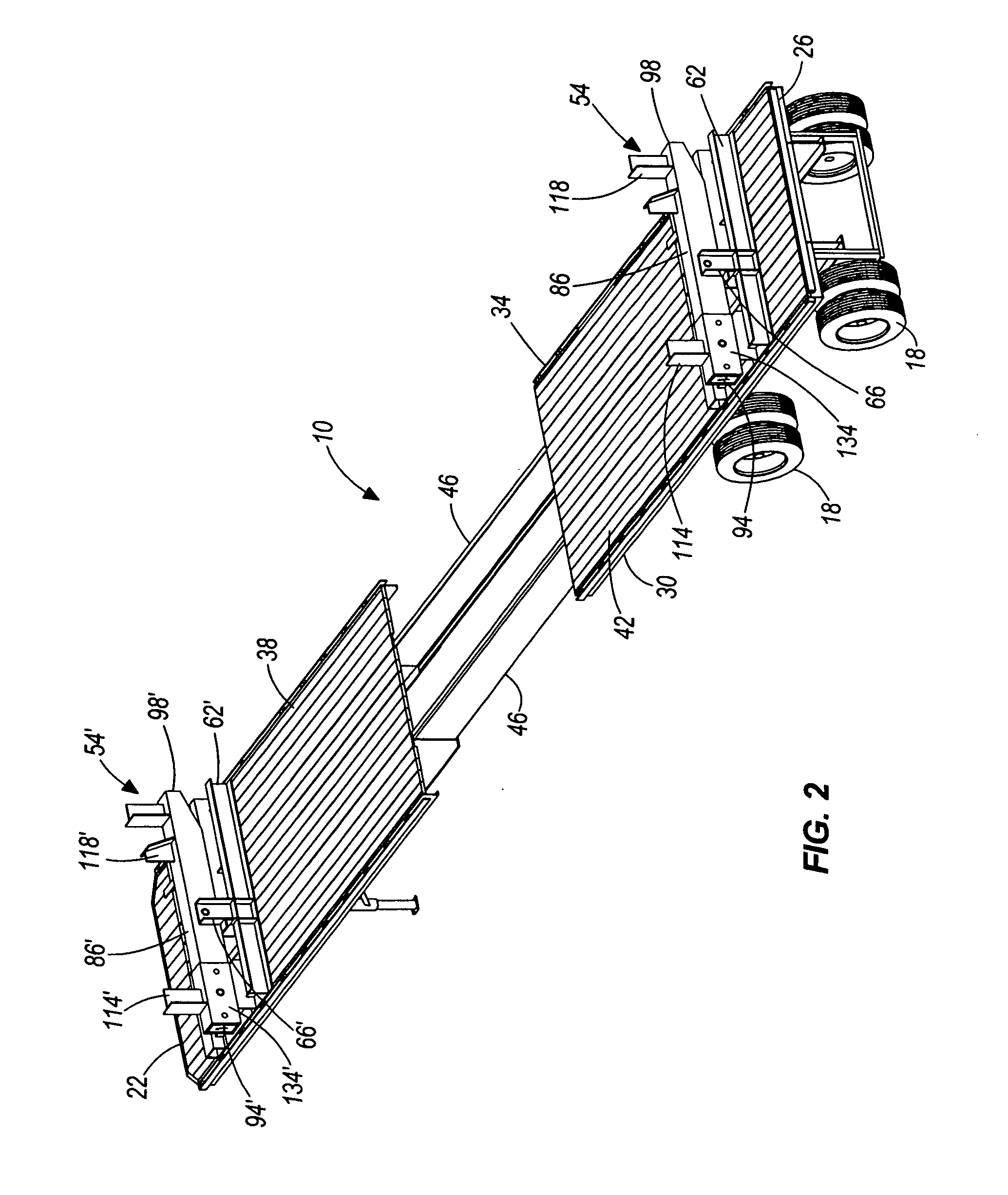

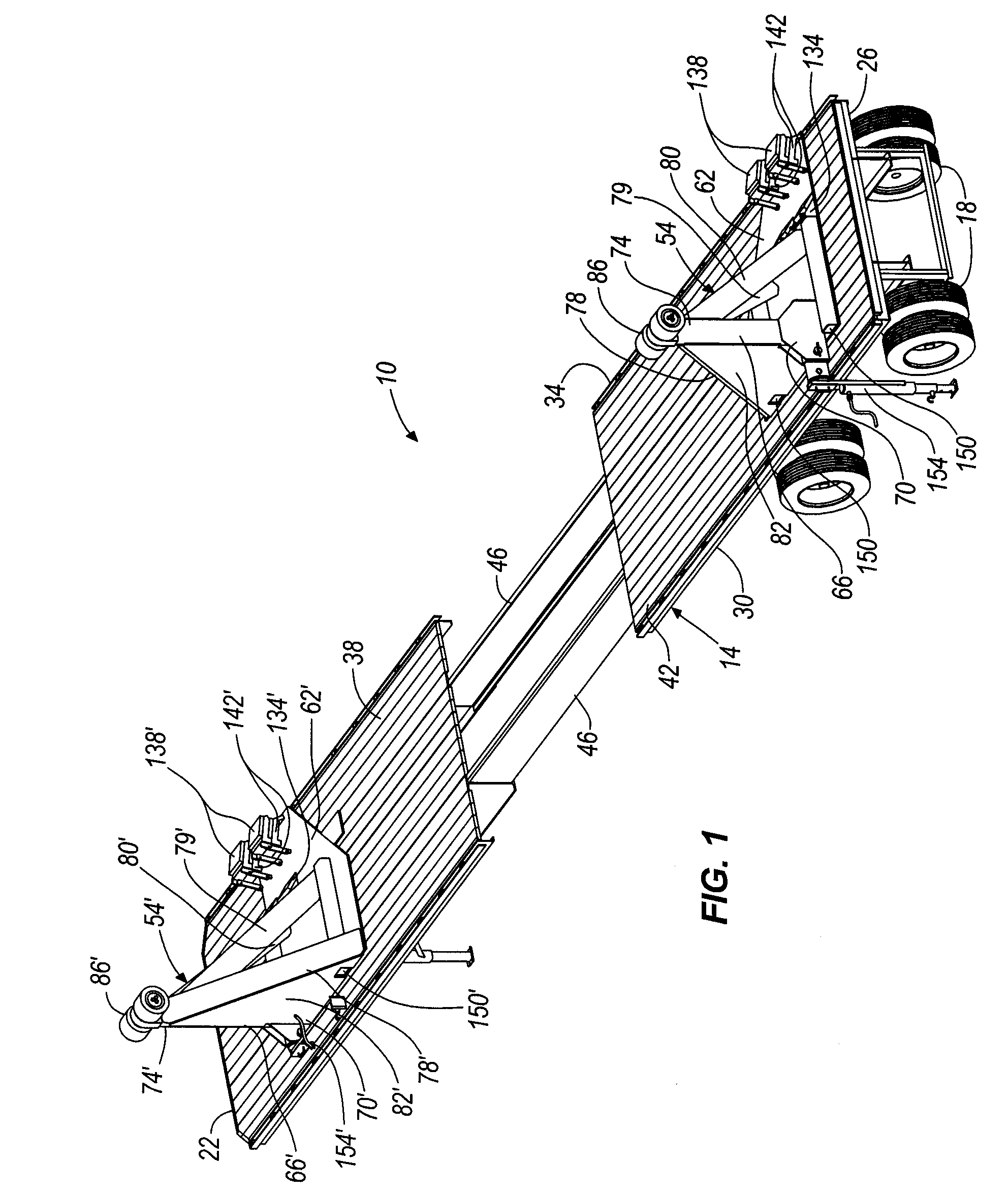

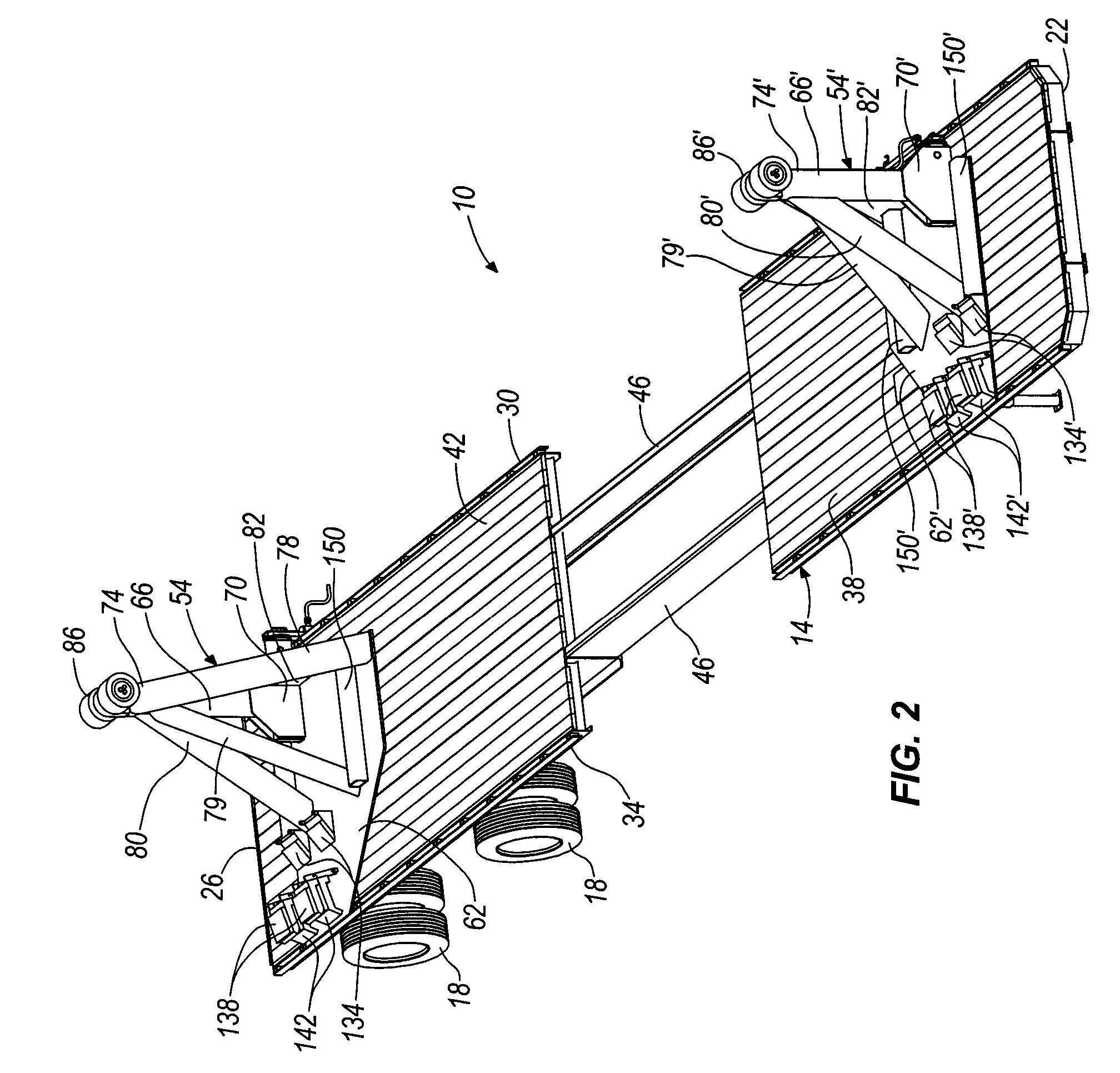

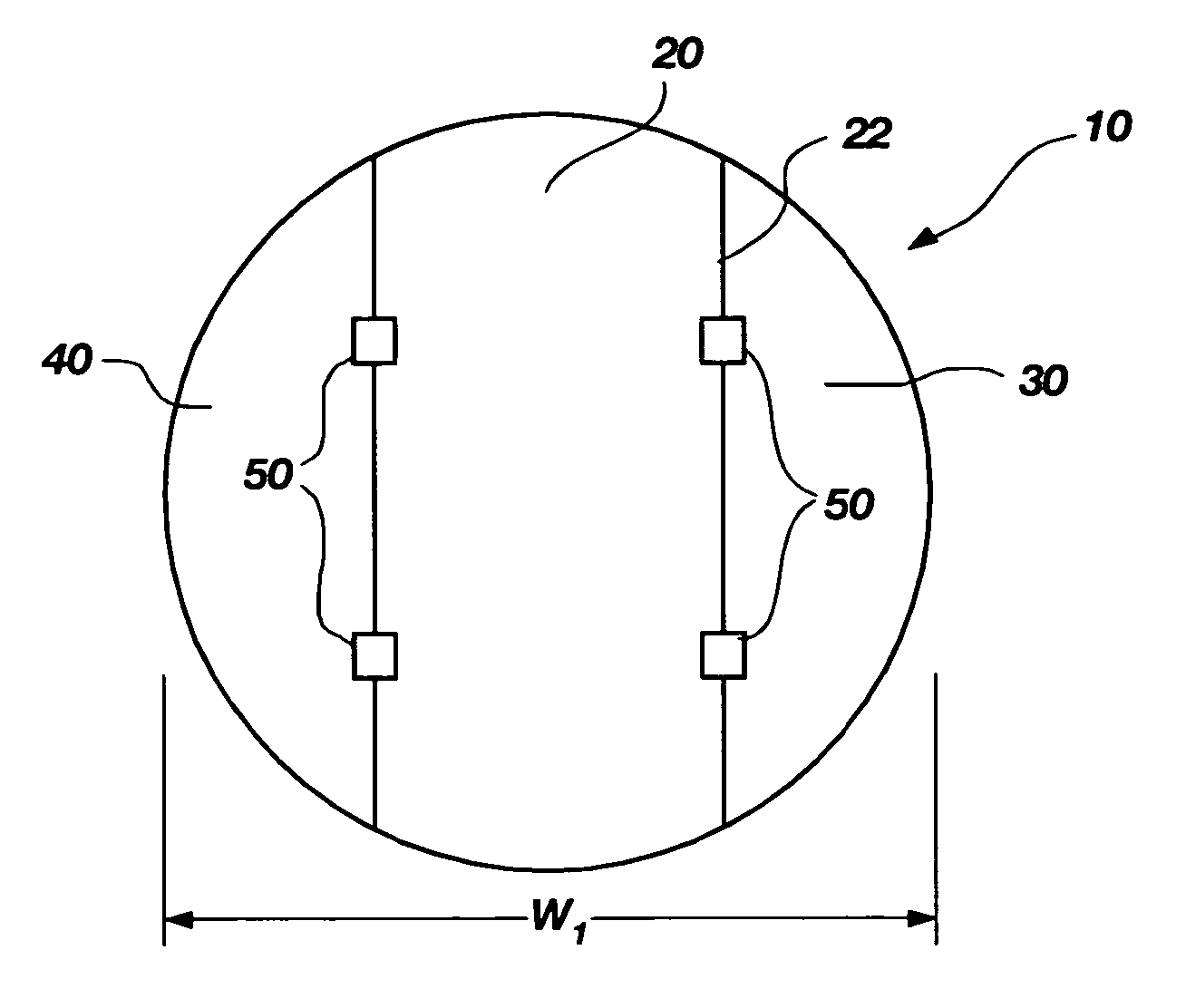

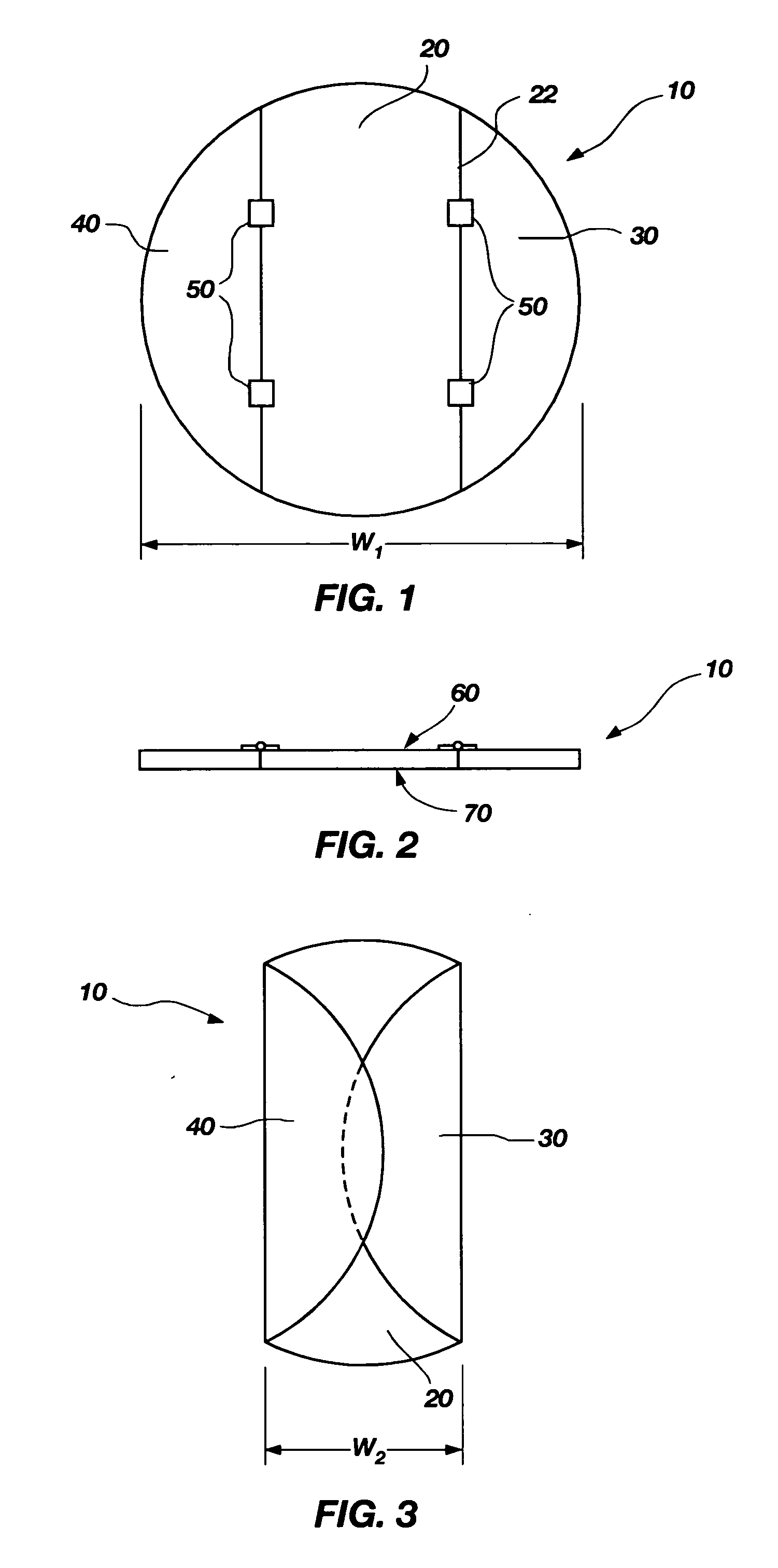

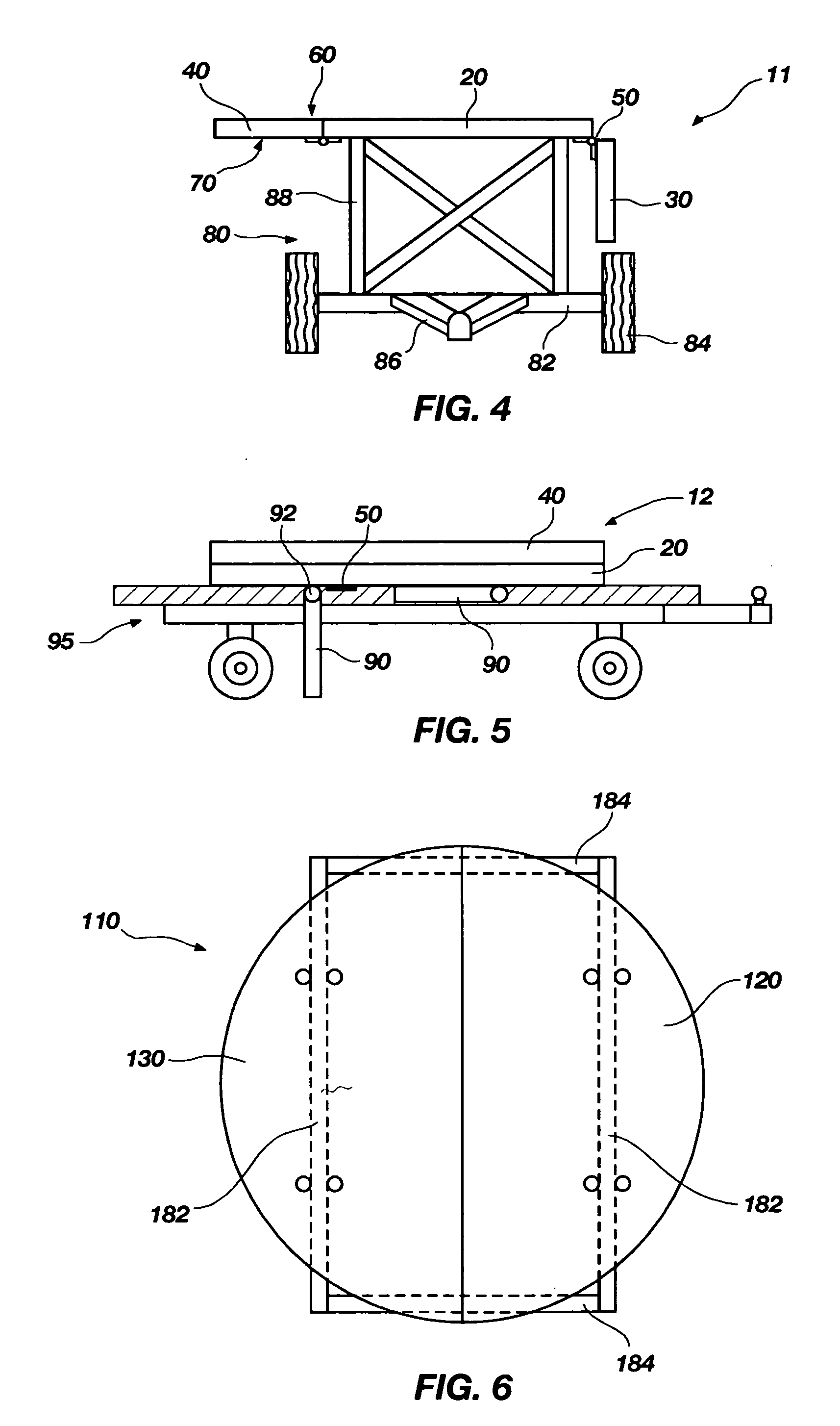

Support structure apparatus and method

InactiveUS7204665B2Reduce effective widthAvoid restrictionsVehicle to carry long loadsLoad securingRotational axisBolster

A support structure for supporting and tilting an oversized cargo to reduce the effective width of the cargo. The structure comprises a bolster frame having a base and a stanchion connected to the base. The stanchion extends upwardly from a lower end connected to the base to an upper end opposite the lower end. A cylindrical roller supported is by the upper end of the stanchion for rotational movement relative to the stanchion about a rotational axis. The cylindrical roller is also supported by the stanchion for pivotal movement relative to the stanchion such that the rotational axis pivots relative to the stanchion. The bolster frame also includes a bearing pad connected to the base. The cylindrical roller and the bearing pad at least partially support the oversized cargo. The support structure may be mounted on a trailer for transporting oversized cargo, such as concrete double-tees.

Owner:CRETEX

Support structure apparatus and method

InactiveUS20050220558A1Reduce effective widthAvoid restrictionsVehicle to carry long loadsLoad securingRotational axisBraced frame

A support structure for supporting and tilting an oversized cargo to reduce the effective width of the cargo. The structure comprises a bolster frame having a base and a stanchion connected to the base. The stanchion extends upwardly from a lower end connected to the base to an upper end opposite the lower end. A cylindrical roller supported is by the upper end of the stanchion for rotational movement relative to the stanchion about a rotational axis. The cylindrical roller is also supported by the stanchion for pivotal movement relative to the stanchion such that the rotational axis pivots relative to the stanchion. The bolster frame also includes a bearing pad connected to the base. The cylindrical roller and the bearing pad at least partially support the oversized cargo. The support structure may be mounted on a trailer for transporting oversized cargo, such as concrete double-tees.

Owner:CRETEX

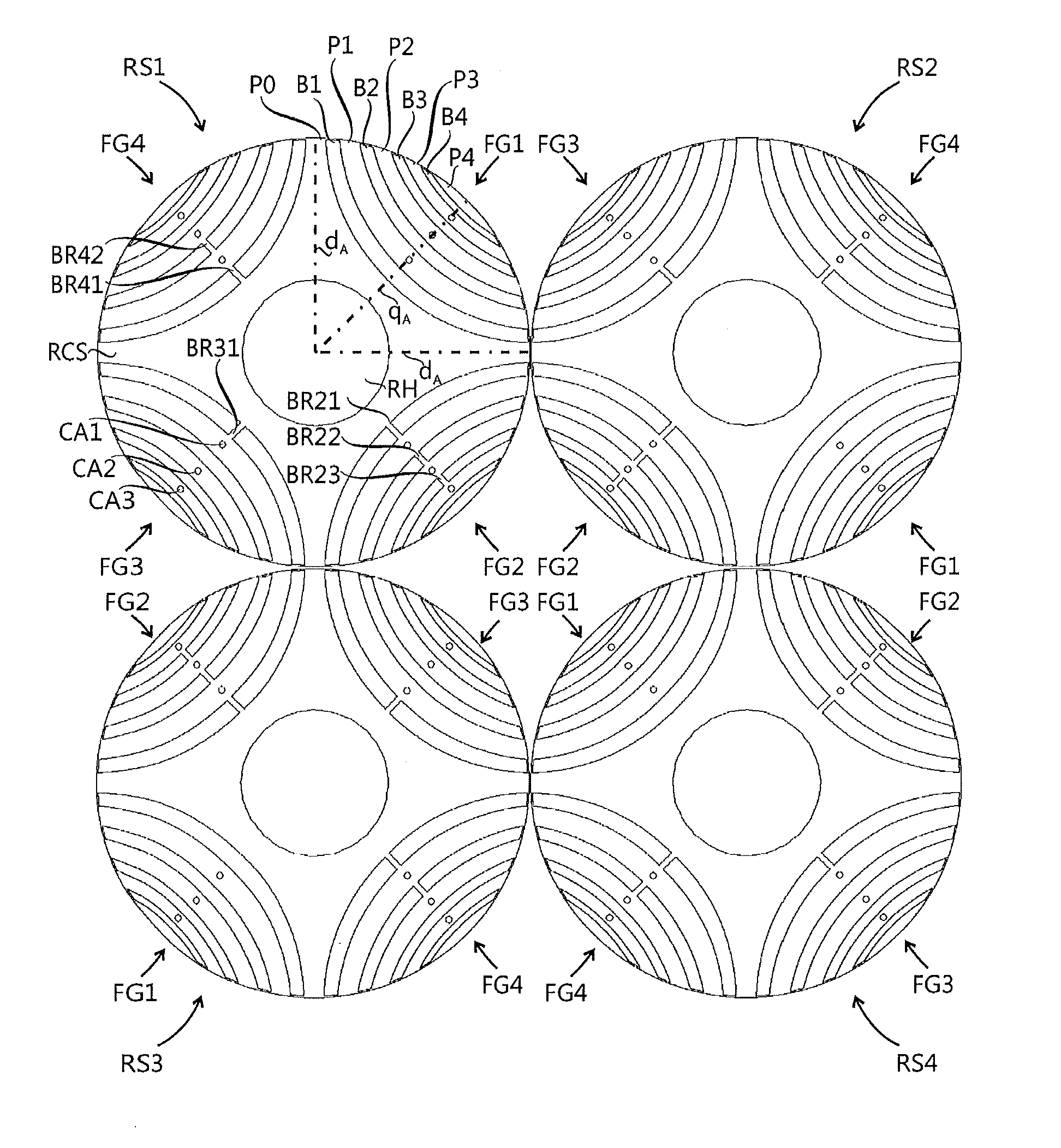

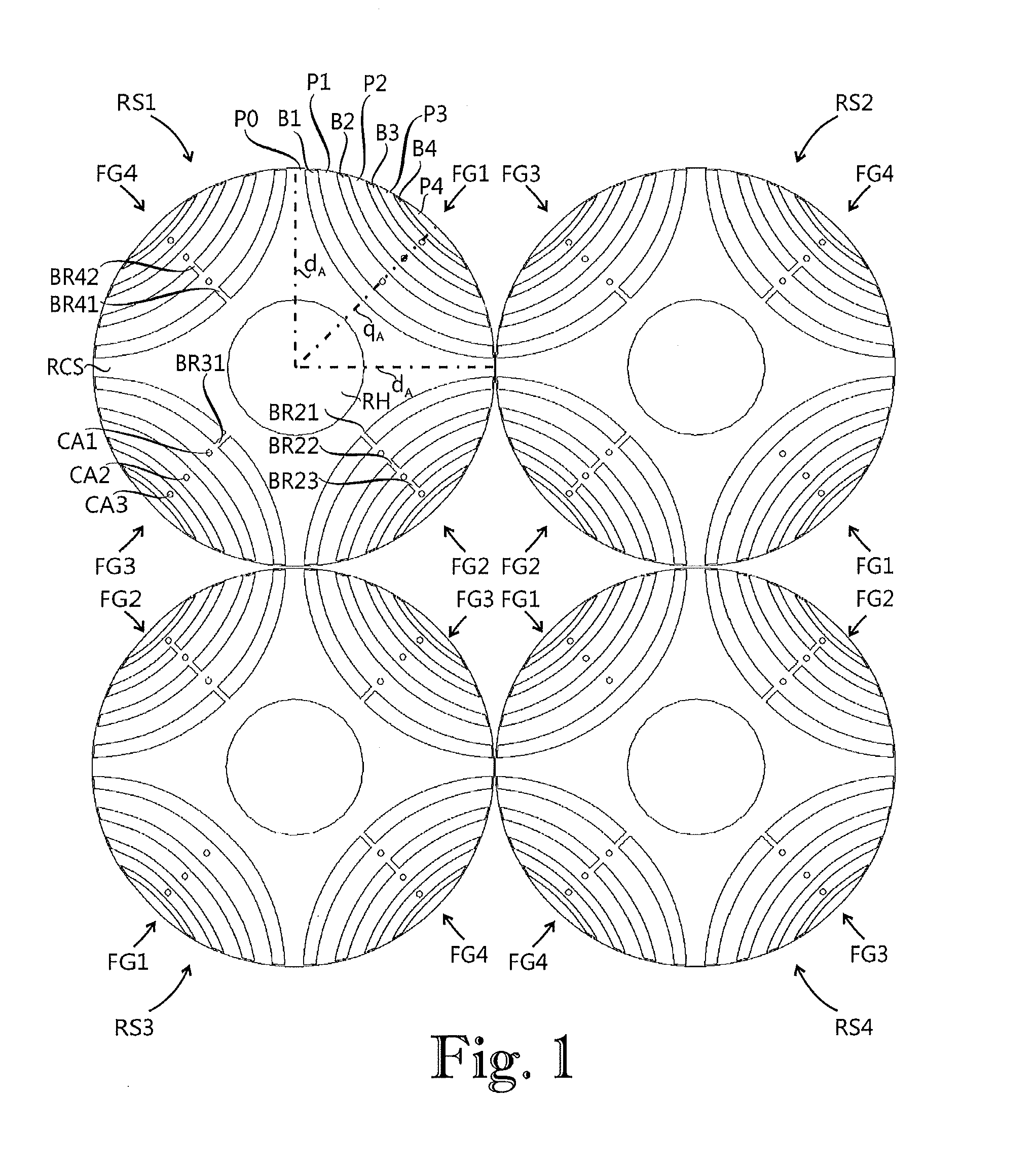

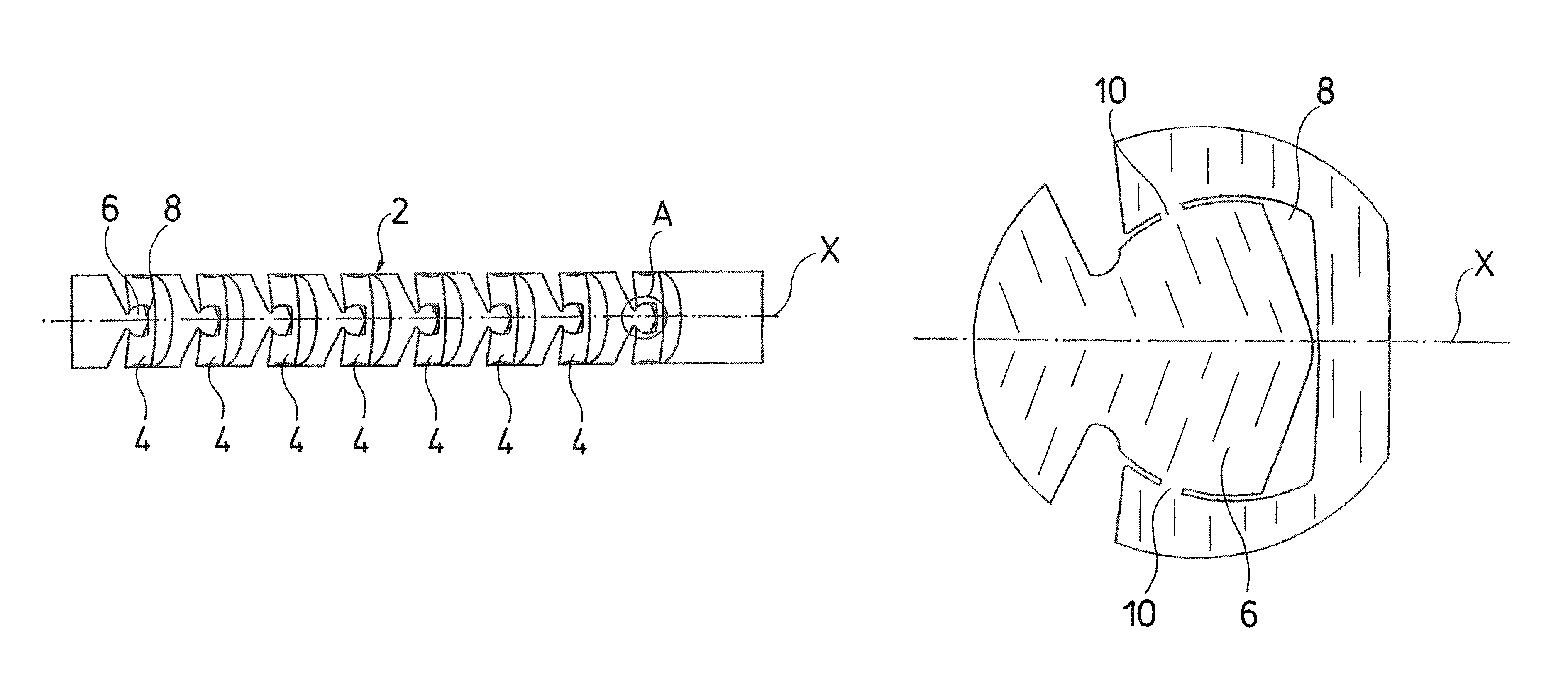

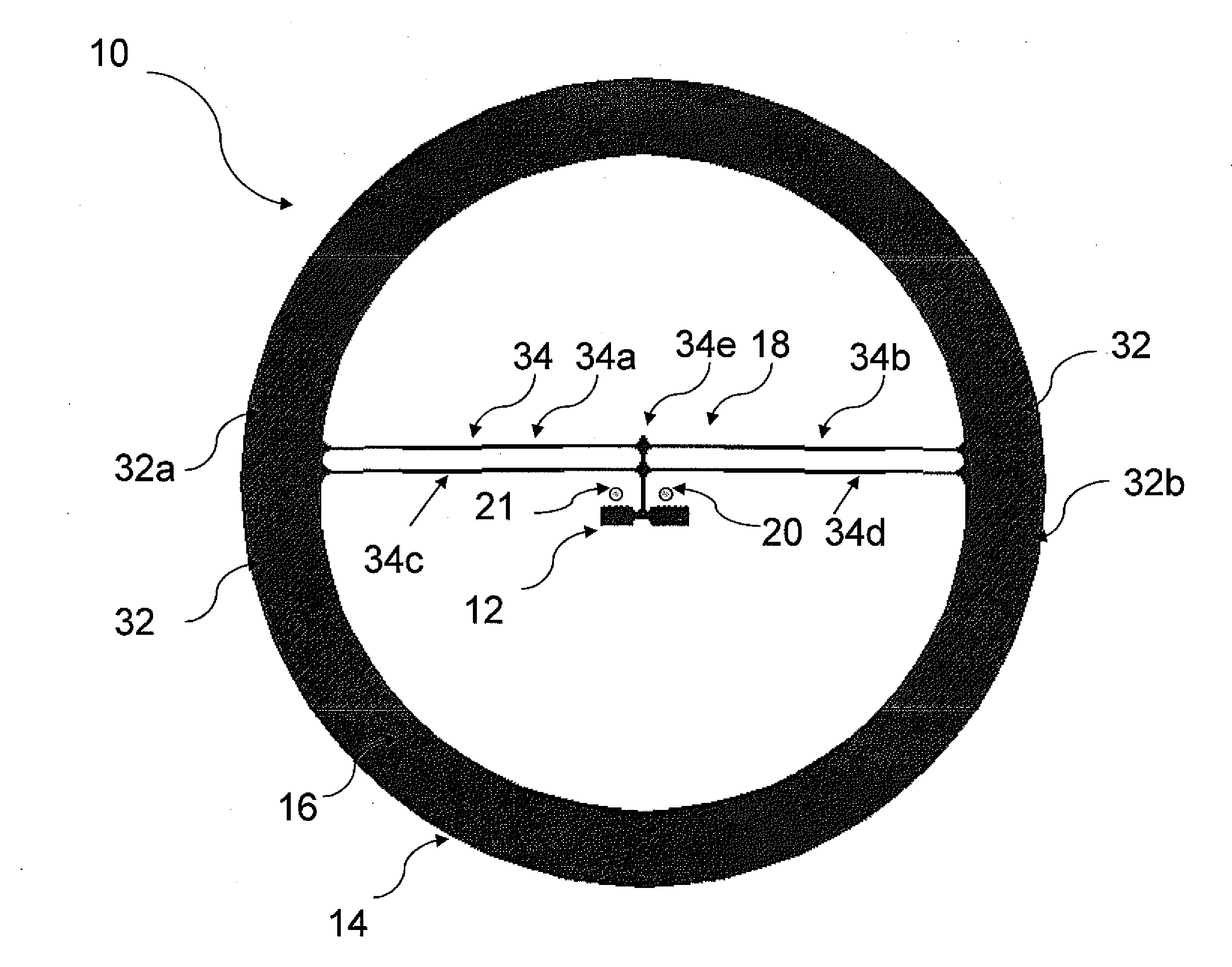

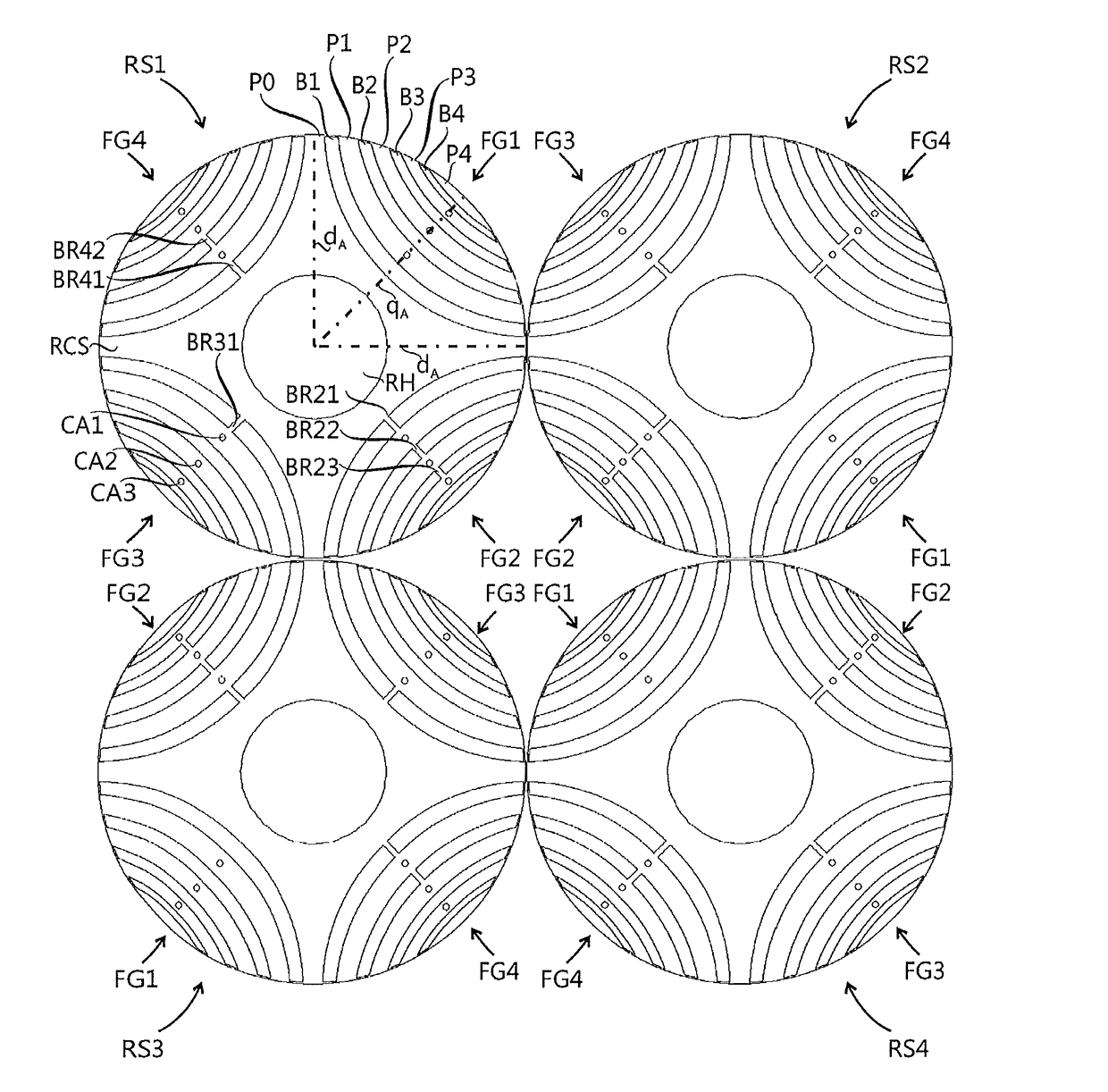

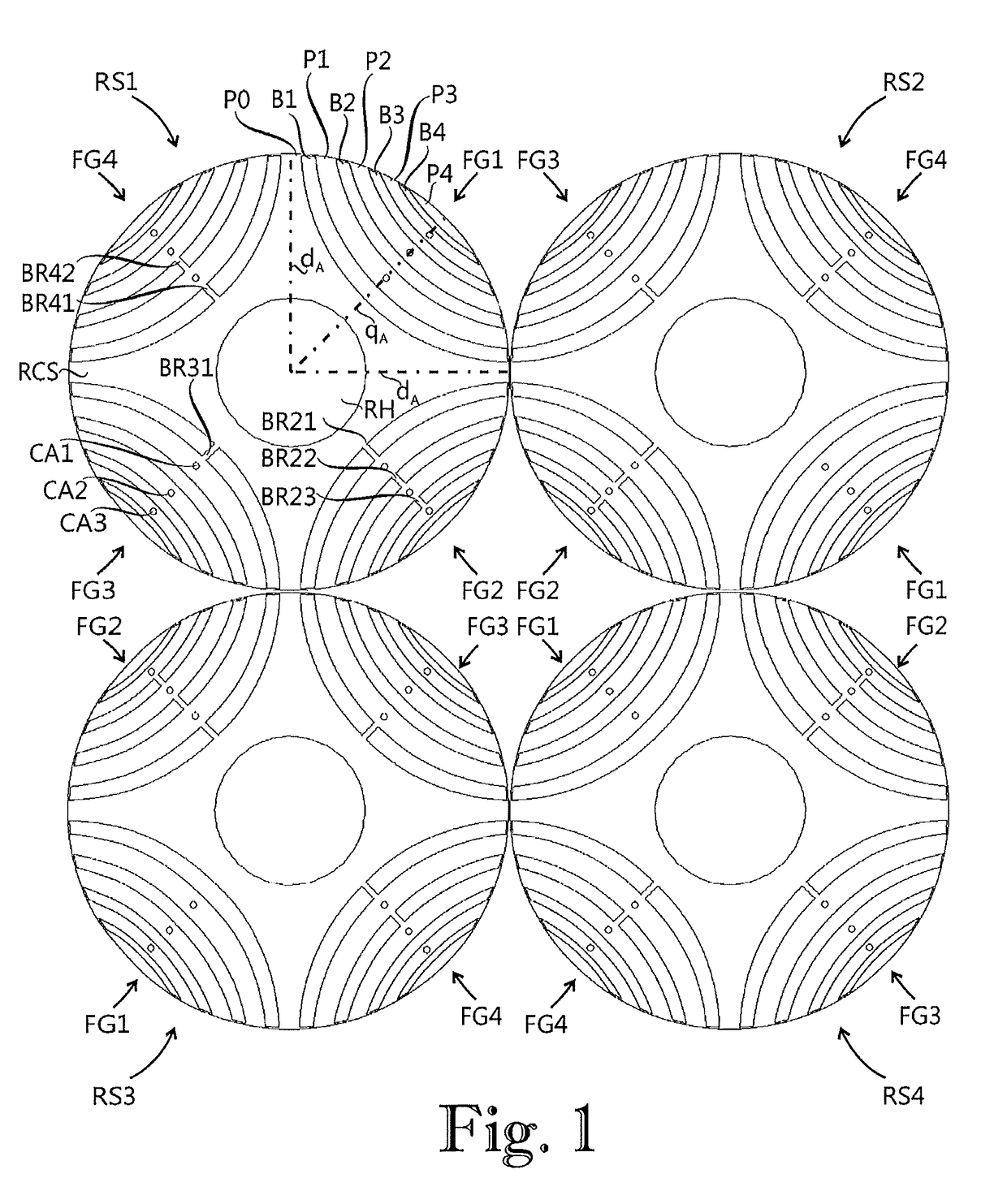

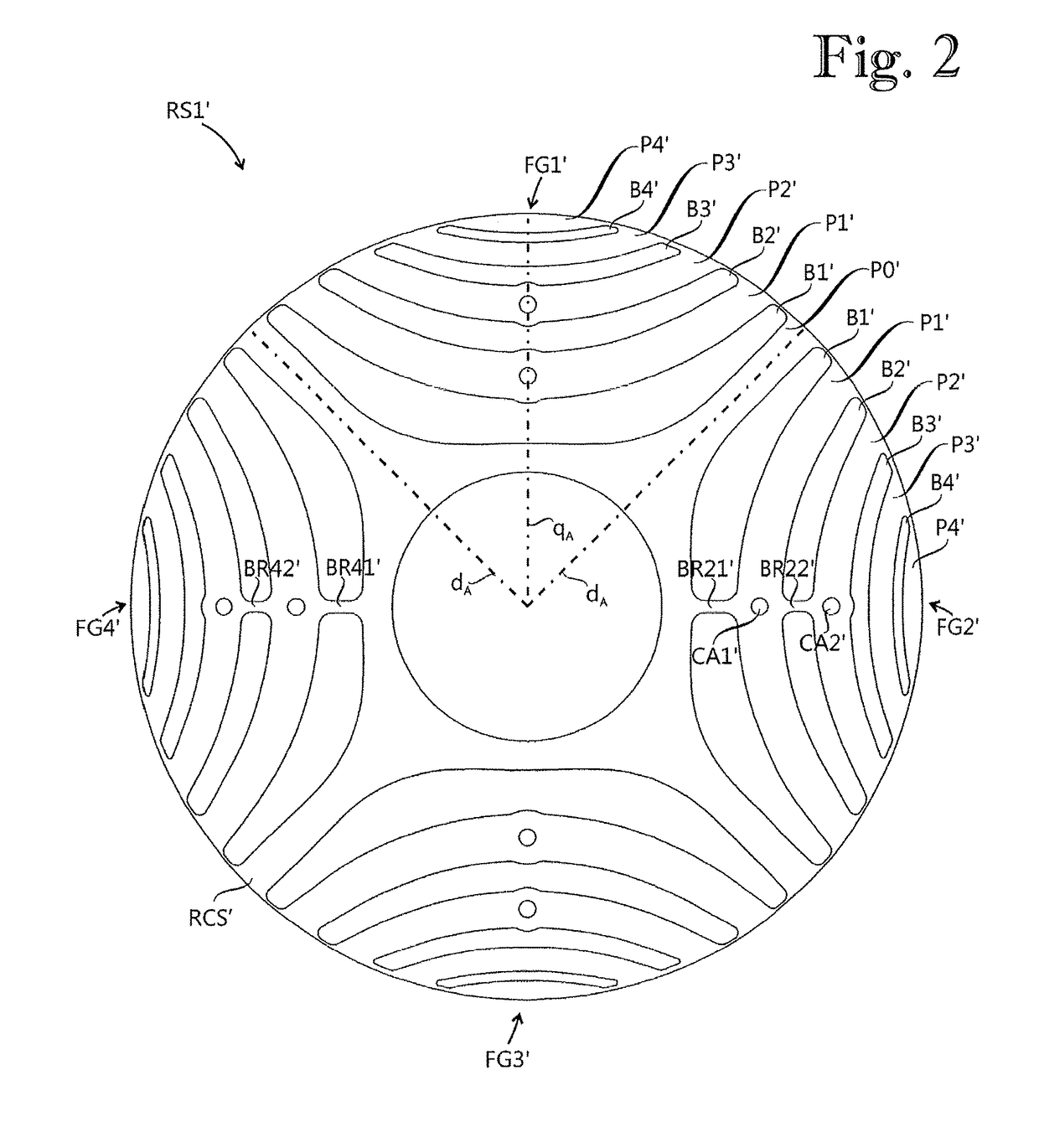

Rotor for an electric machine, an electric machine and method for manufacturing an electric machine

ActiveUS20150280498A1Reduce widthReduce effective widthMagnetic circuit rotating partsManufacturing stator/rotor bodiesElectric machineEngineering

A rotor for an electric machine includes a rotor core having a plurality of rotor sheets (RS1), each of the plurality of rotor sheets including a plurality of flux guide sections, each of the plurality of flux guide sections having a plurality of flux paths and a plurality of flux barriers. The plurality of flux guide sections having a first flux guide section in which a first number of the plurality of flux barriers has a bridge interrupting the flux barrier, and a second flux guide section in which a second number of the plurality of flux barriers has a bridge interrupting the flux barrier. Each bridge is made of a material of high permeance, and the first number of the first flux guide section is different than the second number of the second flux guide section.

Owner:ABB (SCHWEIZ) AG

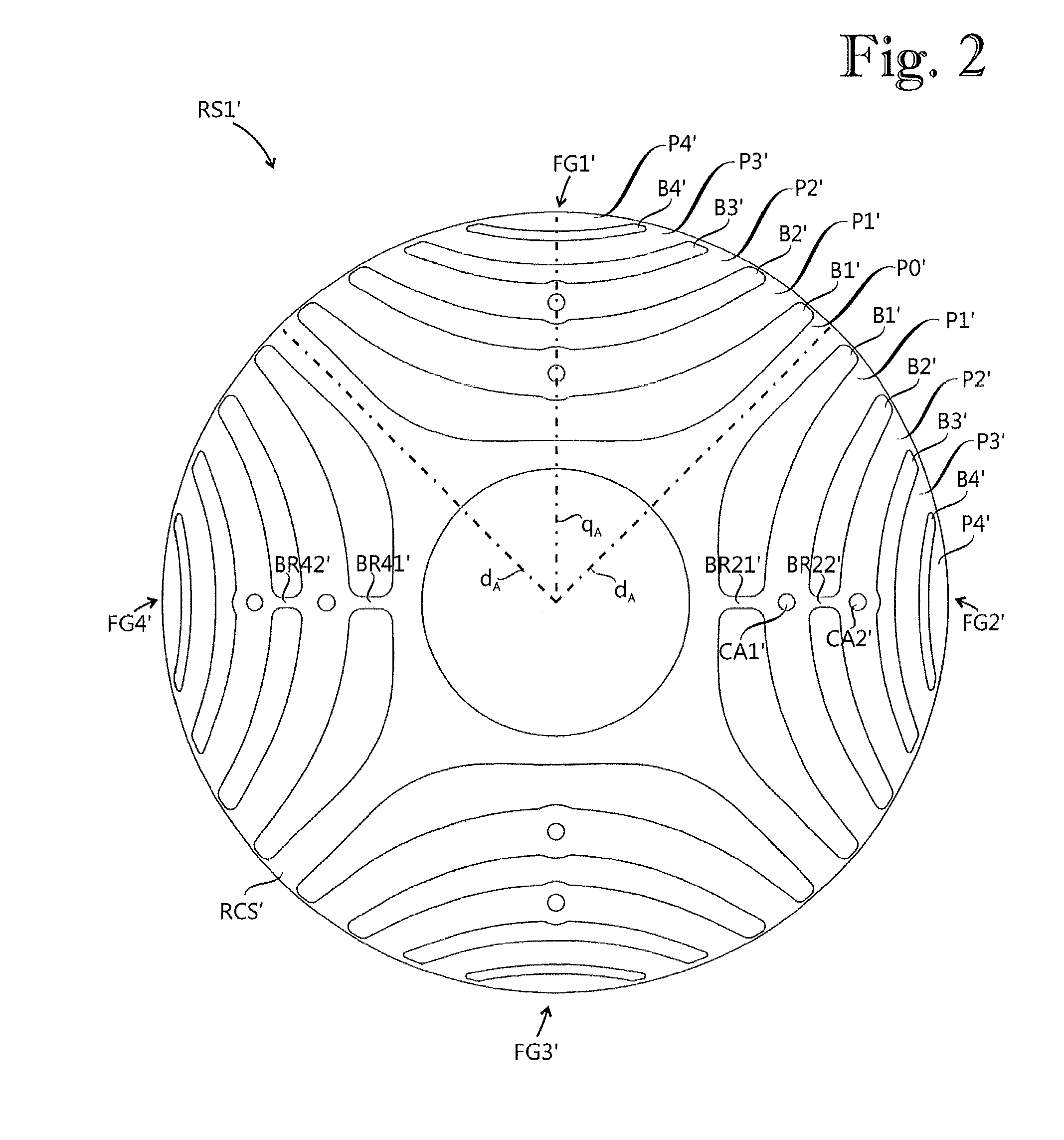

Method for manufacturing a bendable tube

InactiveUS8327518B2Improved stability characteristicsProcess economyMetal rolling stand detailsSurgeryEngineering

Owner:RICHARD WOLF GMBH

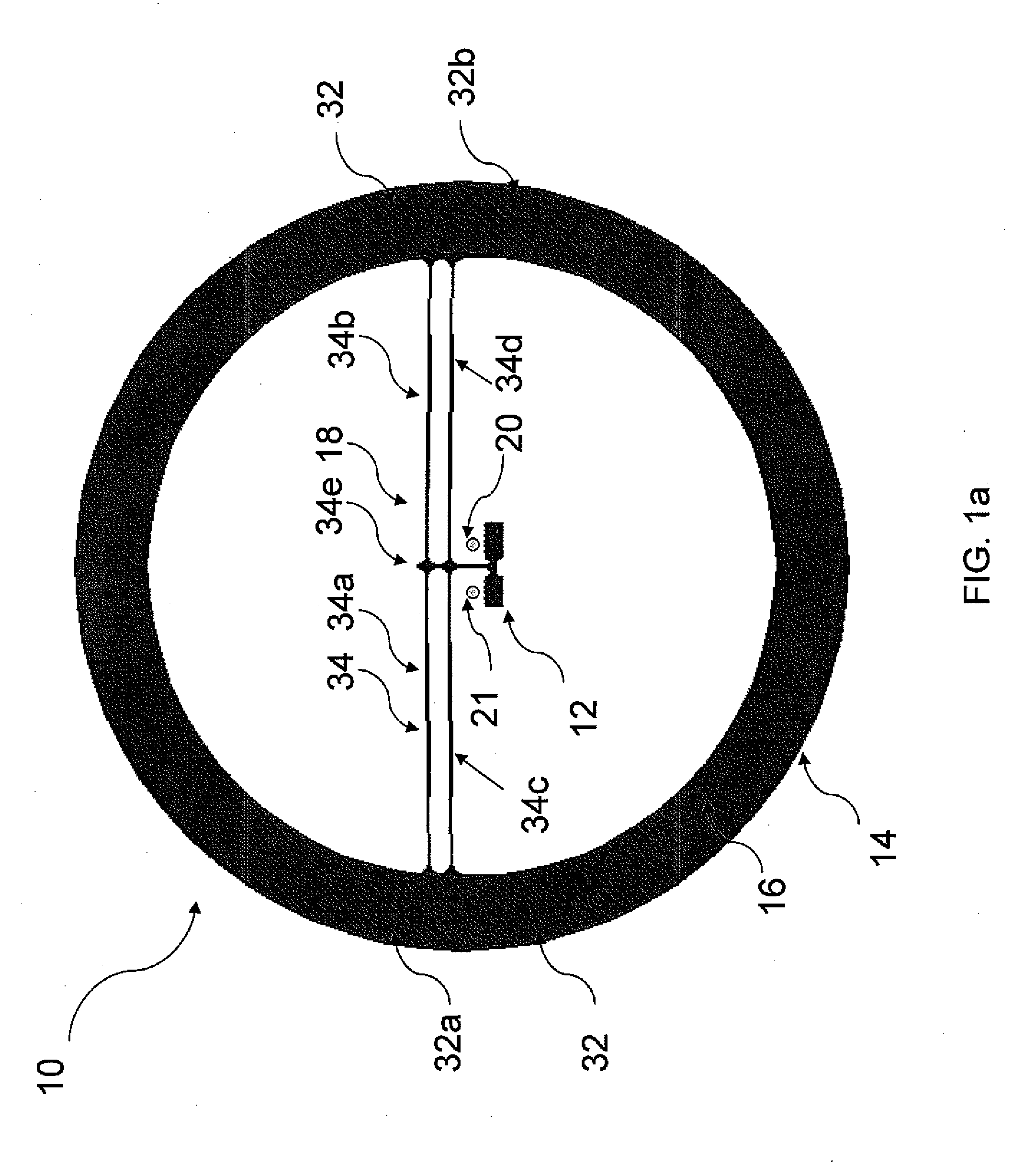

Compact thermal actuated variable optical attenuator

InactiveUS20110217018A1Improved optical shutterLow costMetal working apparatusOptical light guidesOptical attenuatorThermal expansion

A MEMS variable optical attenuator (VOA) chip includes a frame having a planar surface, a micro-electric actuator with a movable optical shutter arranged with respect to the planar surface of the frame, where the VOA is actuated by thermal expansion. The micro-electric actuator comprises semiconductor conductors (“wires”) that can be moved, upon applying an electrical current, by thermal expansion. In one embodiment, the MEMS VOA chip is configured in a multiple wire arrangement that restricts the shutter movement in a plane.

Owner:AGILTRON

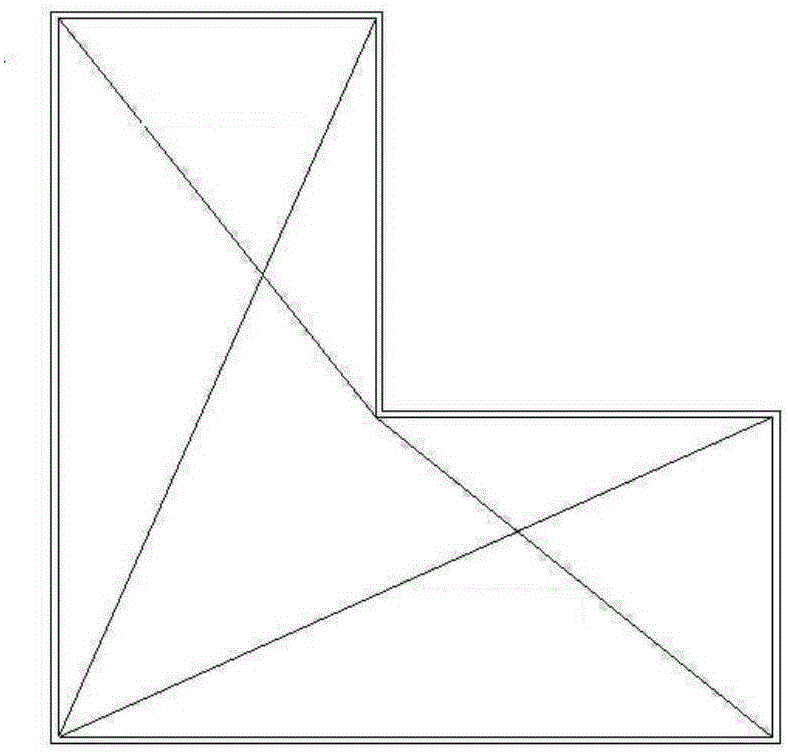

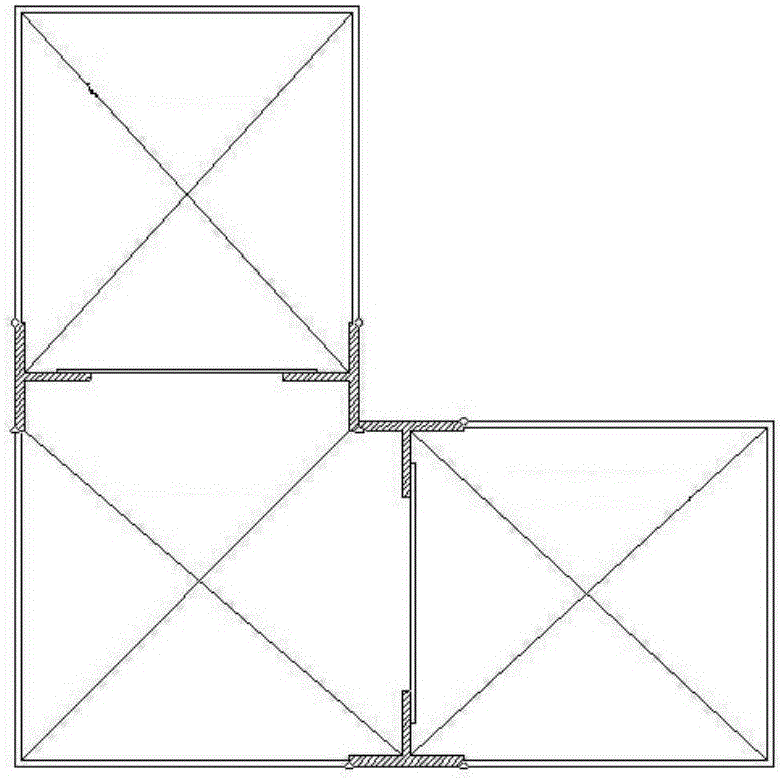

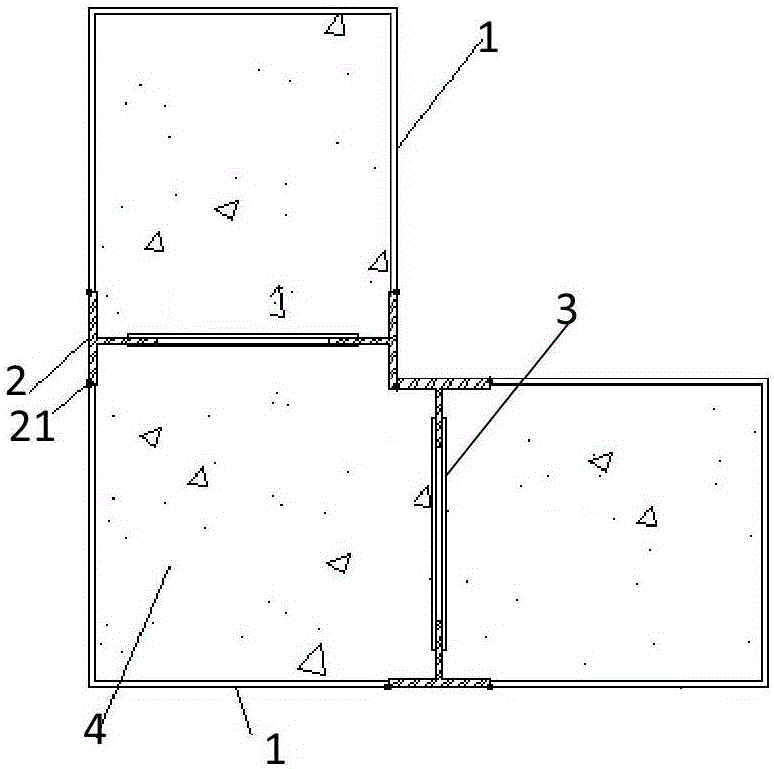

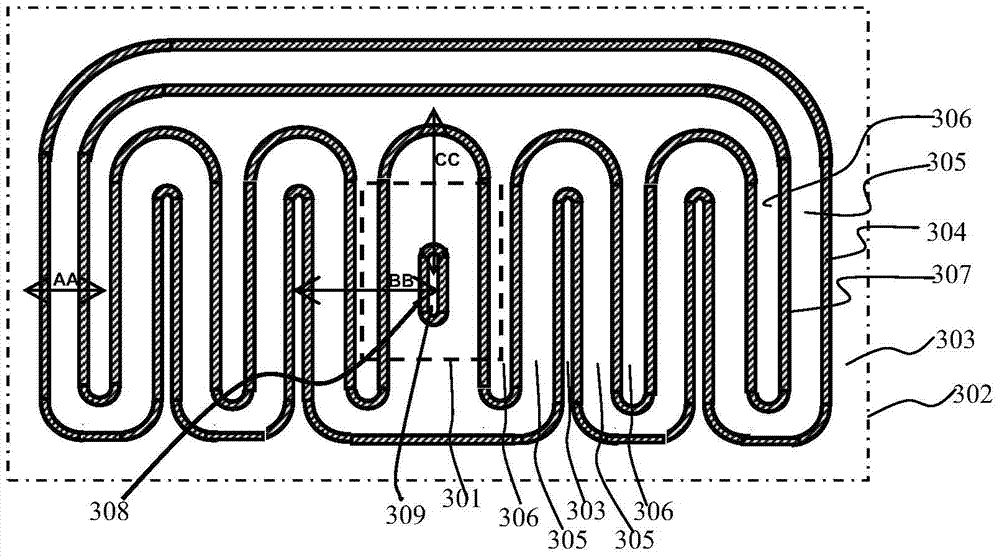

Inner truss type steel tube concrete L-shaped column and construction method thereof

InactiveCN105113717AReduce effective widthImprove bearing capacityStrutsBuilding material handlingSteel platesSteel tube

The invention discloses an inner truss type steel tube concrete L-shaped column and a construction method thereof. The inner truss type steel tube concrete L-shaped column comprises a wrapping steel tube, filling concrete and an inner truss; the inner truss comprises T-shaped steel, inner truss subunits and T-shaped steel web lacing bars; the inner truss subunits are formed by welding the T-shaped steel; the T-shaped steel web lacing bars are longitudinally welded in a T-shaped steel web and the inner truss subunits along the T-shaped steel in a stacked manner; the T-shaped steel and the inner truss subunits are positioned at edges and corners of a quadrangle; the cross section of the wrapping steel tube is inversely L-shaped or n-shaped; and the wrapping steel tube is fixedly welded with flange plates of the T-shaped steel. The inner truss is tensioned at a corner of a special-shaped steel tube, so that effective width of a steel plate is reduced, a fulcrum is provided for deformation of the steel plate out of a plane, anti-unsteady capability of the steel plate can be improved, a hooping effect of the column is improved, and the bearing capacity of a steel tube concrete special-shaped column is improved obviously.

Owner:HOHAI UNIV

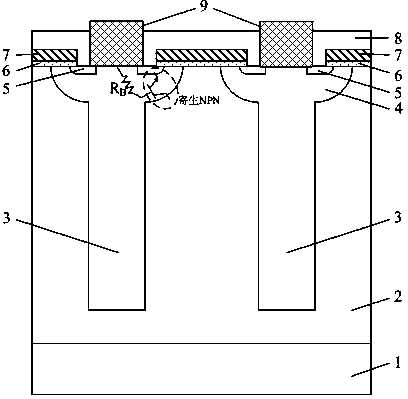

Super junction semiconductor device manufacturing method capable of improving avalanche capacity

ActiveCN103560086AImproved avalanche capabilityReduce the equivalent resistance R

<sub>B</sub>

resistance valueSemiconductor/solid-state device manufacturingSemiconductor devicesElectron avalancheHigh dosage

The invention relates to a super junction semiconductor device manufacturing method capable of improving the avalanche capacity. On-resistance is increased correspondingly due to transverse diffusion caused by the traditional high dosage concentration of a column P, and puncture voltage is reduced due to electric charge unbalance of the column P and a column N. According to the method, the epitaxy technology is utilized to form an N-type epitaxy layer; a P-type and N-type epitaxy layer is formed by injecting boron ions; the injection amount of the boron ions increases gradually, and the boron ions are pushed under the high temperature to form a P-type and N-type alternant epitaxy layer; a Pbody area is formed by injecting the boron ions; a polycrystalline silicon gate electrode is formed by etching polycrystalline silicon through the dry method; an N+ source area is formed by injecting arsenic ions; a layer of aluminum is deposited on the upper surface of a whole device, a source metal electrode is formed by etching the aluminum, and a drain electrode is formed on the back face through metallization. According to the super junction semiconductor device obtained through the method, the avalanche capacity of the super junction semiconductor device is improved, and at the same time, on-resistance is reduced.

Owner:XIAN LONTEN RENEWABLE ENERGY TECH +1

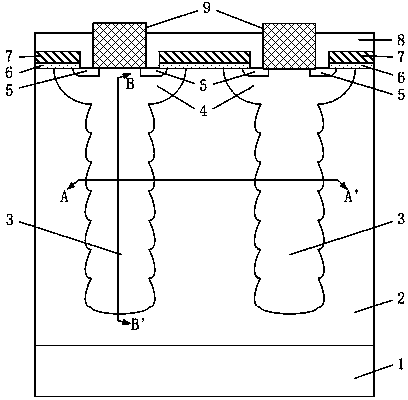

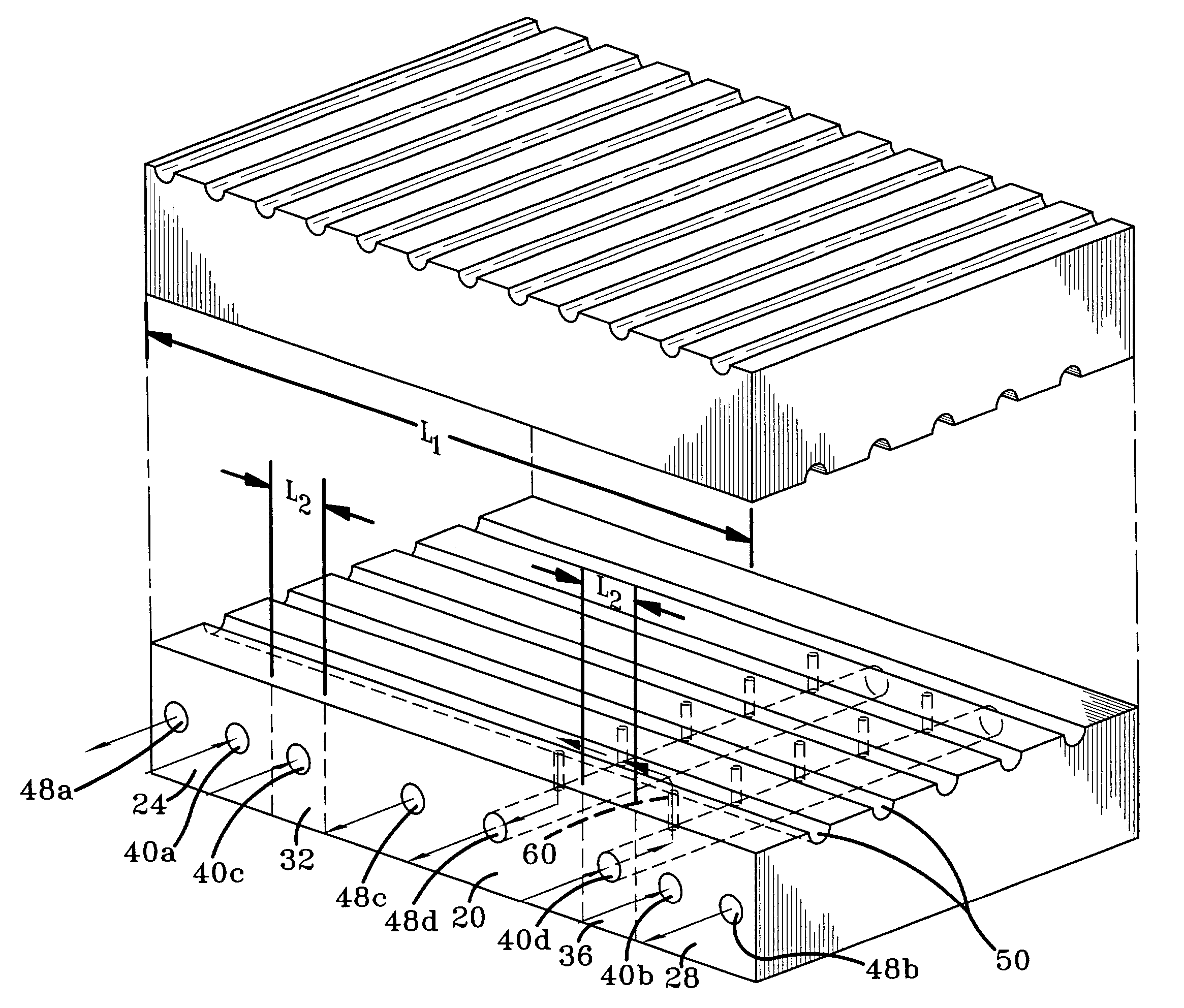

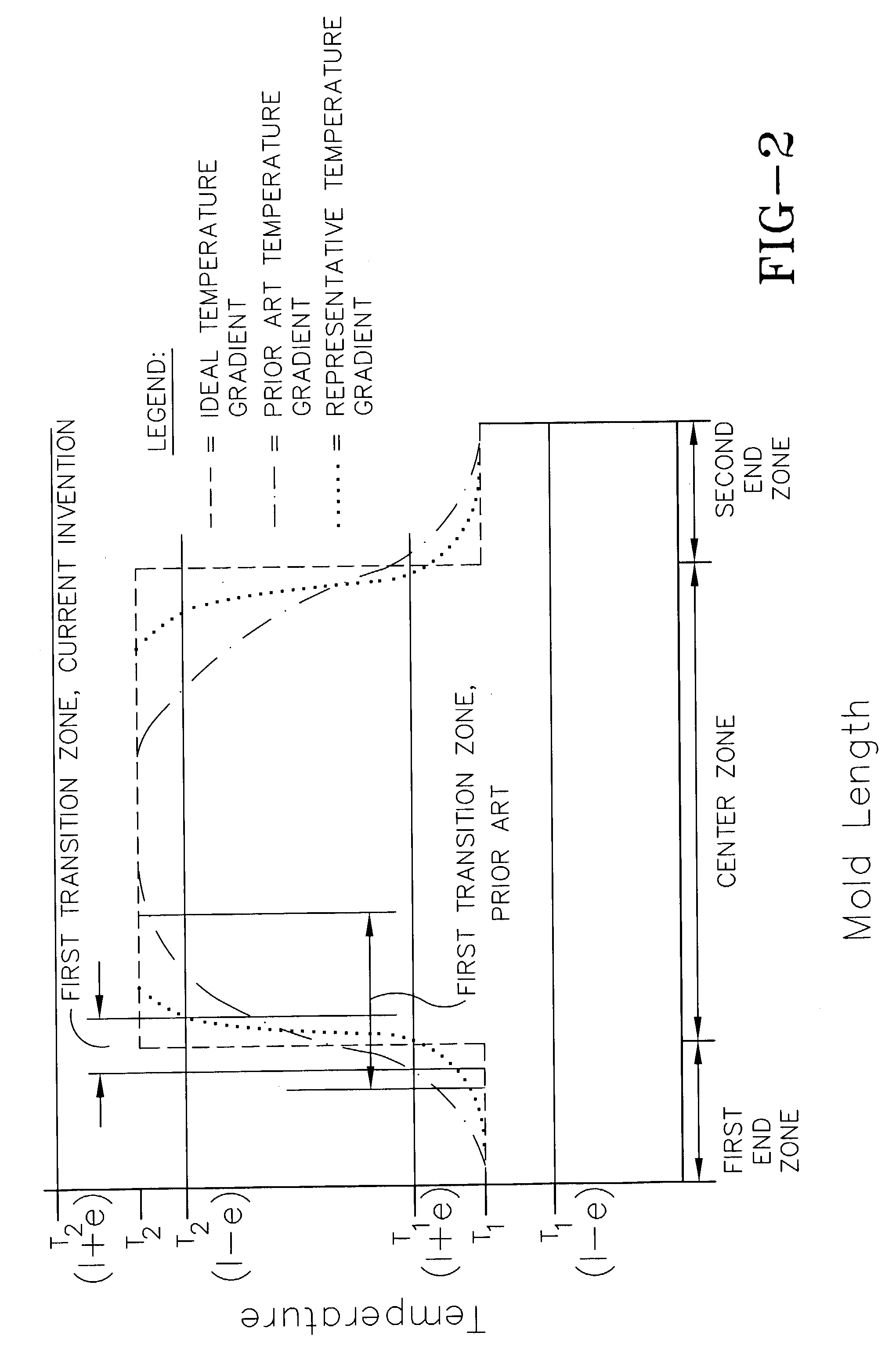

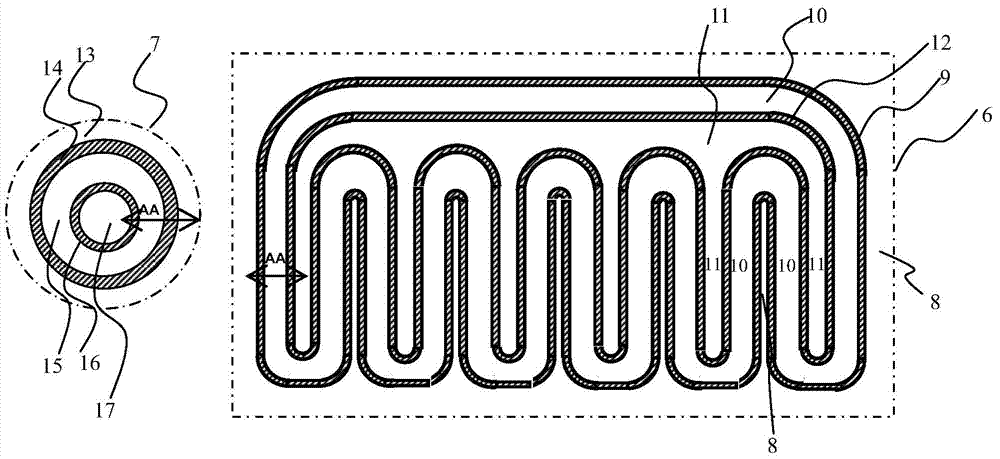

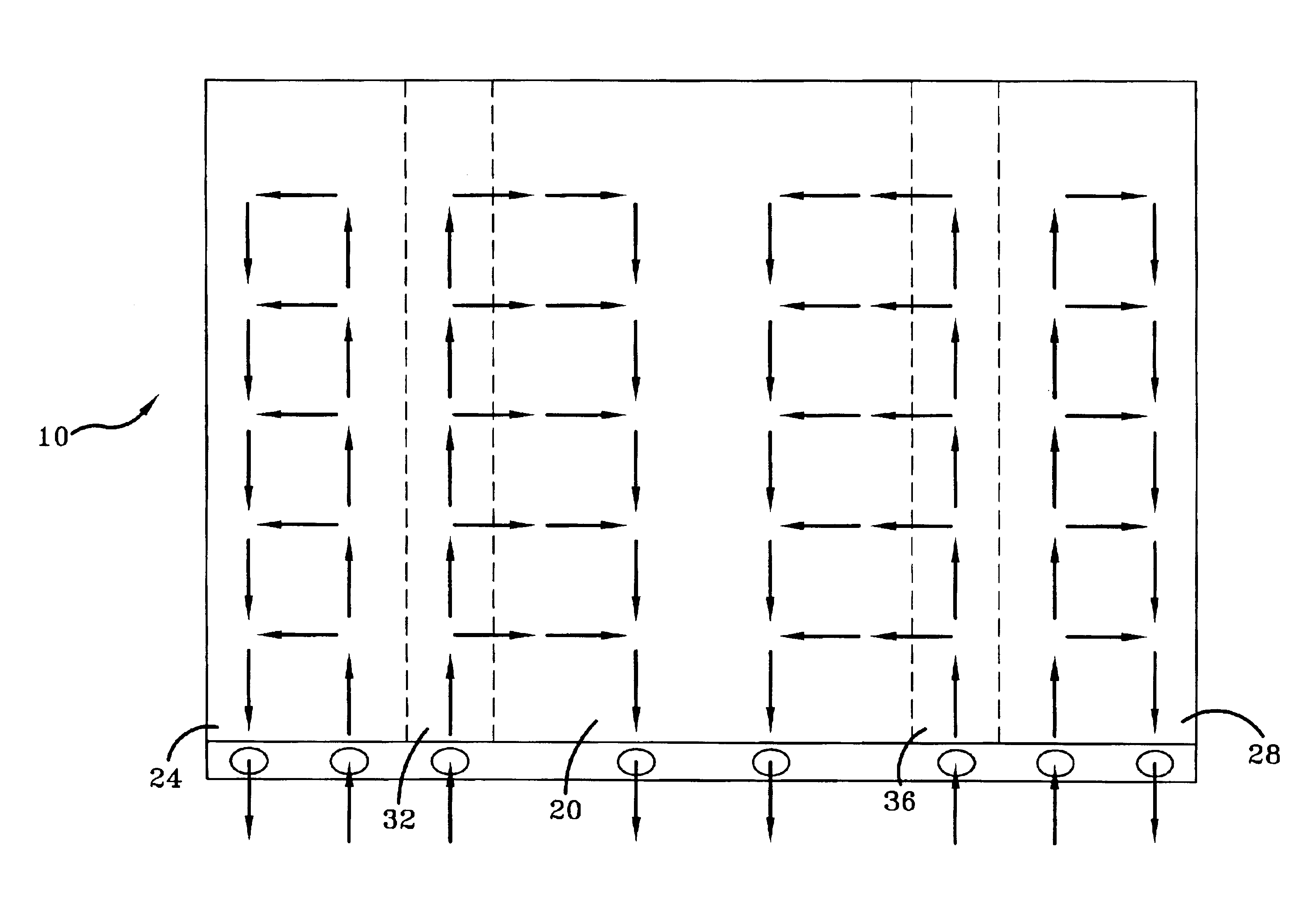

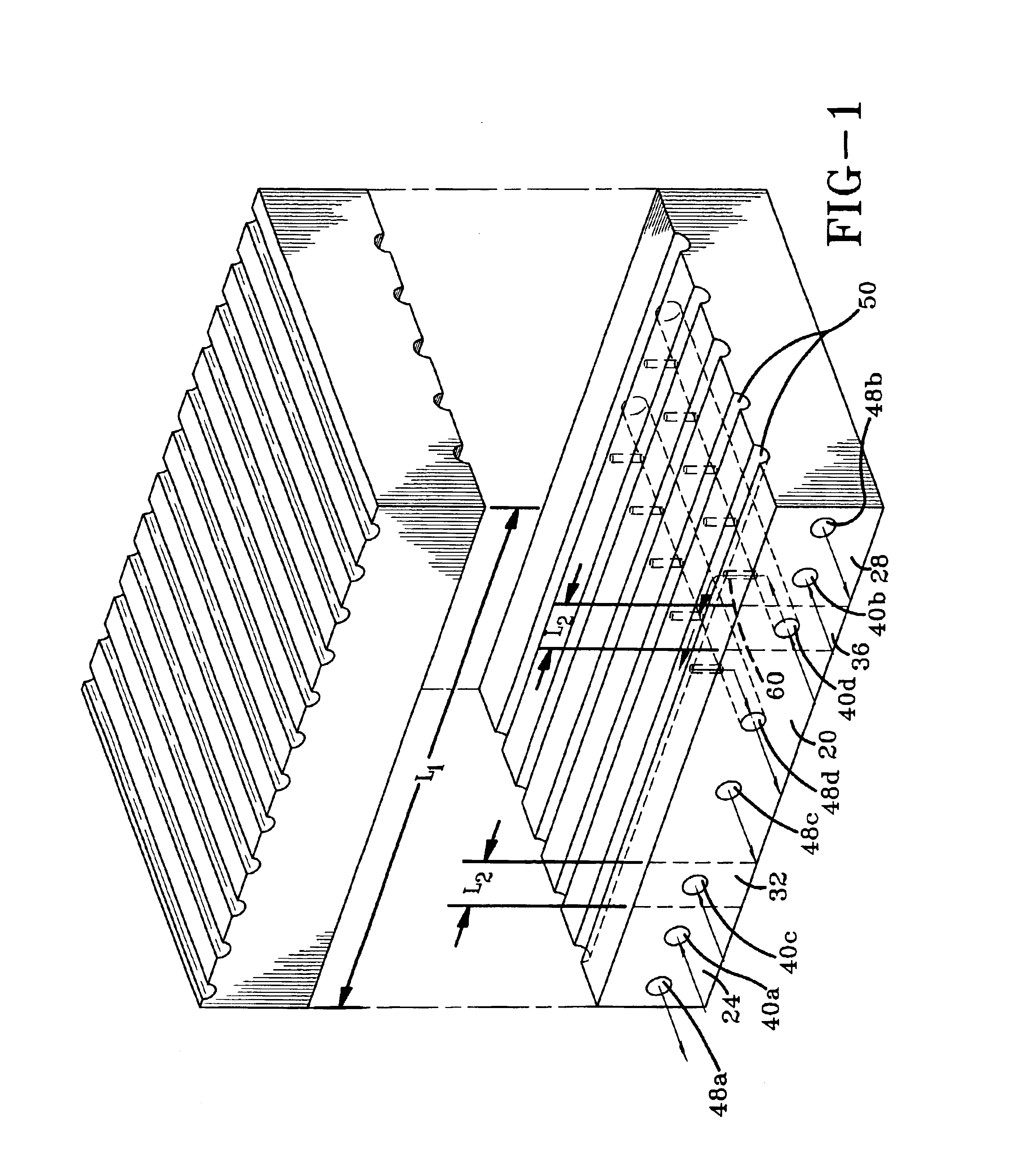

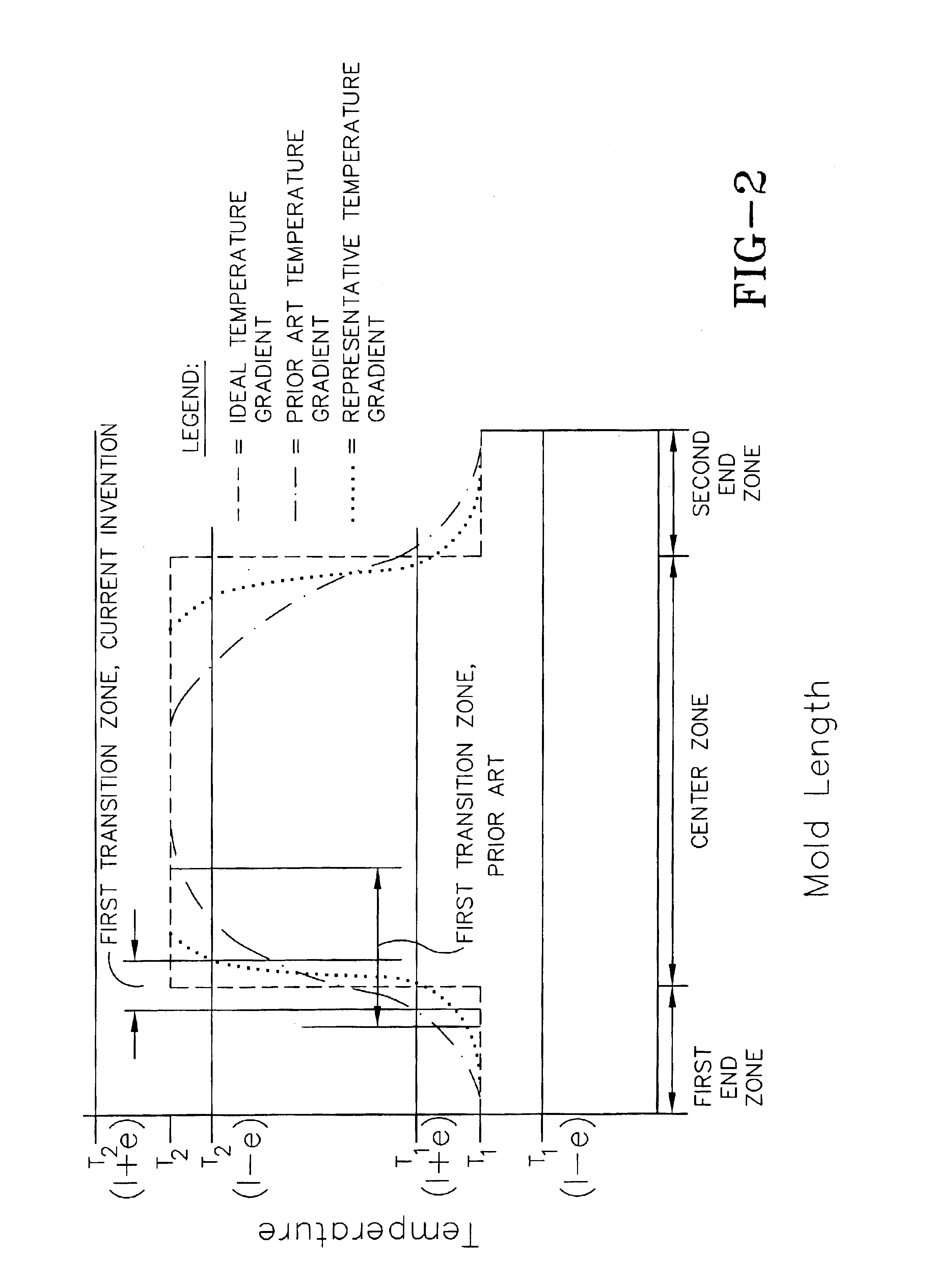

Self-leveling high heat transfer mold

A mold for sequentially curing sections of a belt includes two end zones, a center zone, and transition zones between each end zone and the center zone. The mold is heated and / or cooled by heat transfer fluid flowing from intake manifolds through heat transfer cavities. The intake manifolds are preferably arranged perpendicular to the mold length. In the end zones and in the center zone, the heat transfer cavities are arranged substantially parallel to the length of the mold. The arrangement of the heat transfer cavities provides for a more controlled cure of the belt by allowing the center zone to maintain a consistent temperature throughout the center zone while allowing a cooler consistent temperature to be maintained in the end zones. The transition zones allow a steep temperature gradient from the cooler end zones to the hotter center zone. Heat transfer rates are adjustable without modification to the body of the mold.

Owner:VEYANCE TECH

Support structure apparatus and method

InactiveUS20060067802A1Reduce effective widthAvoid restrictionsVehicle with removable loadingVehicle to carry long loadsRocker armEngineering

A support structure for supporting and tilting an oversized cargo to reduce the effective width of the cargo. The structure comprises a frame having a base and a stanchion connected to the base. A rocker arm is pivotally coupled to the stanchion to pivot about a pivot axis. The arm includes a first and second end disposed opposite one another. The arm has a center of gravity disposed between the first end and the pivot axis and that biases the arm to pivot in a first pivotal direction. First and second brackets are positioned near the first and second ends of the arm for receiving the cargo. The cargo has a center of gravity disposed between the pivot axis and the second end that causes the arm to pivot in a second pivotal direction opposite the first pivotal direction.

Owner:CRETEX

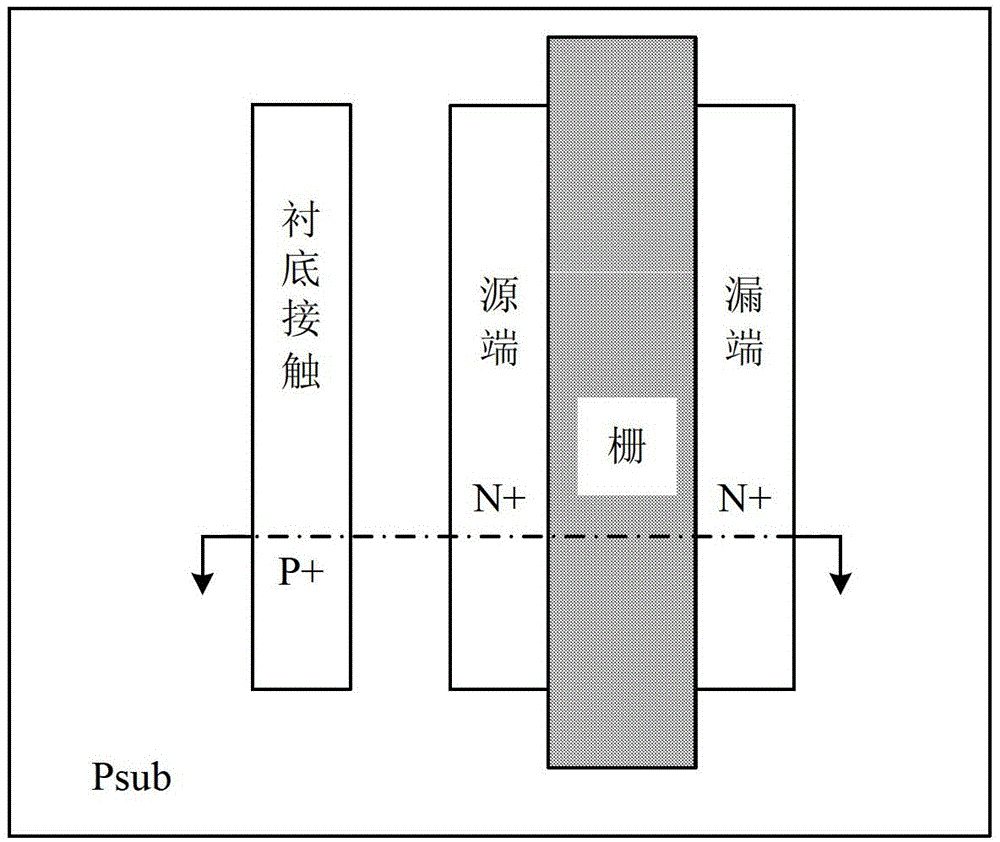

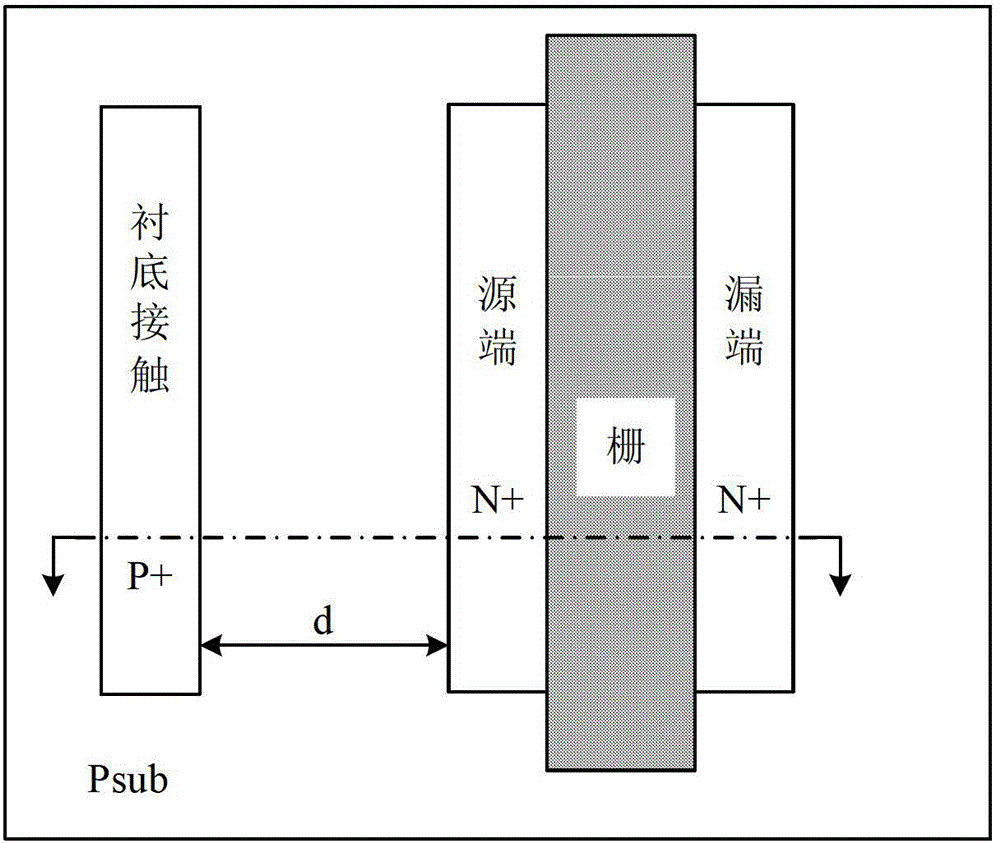

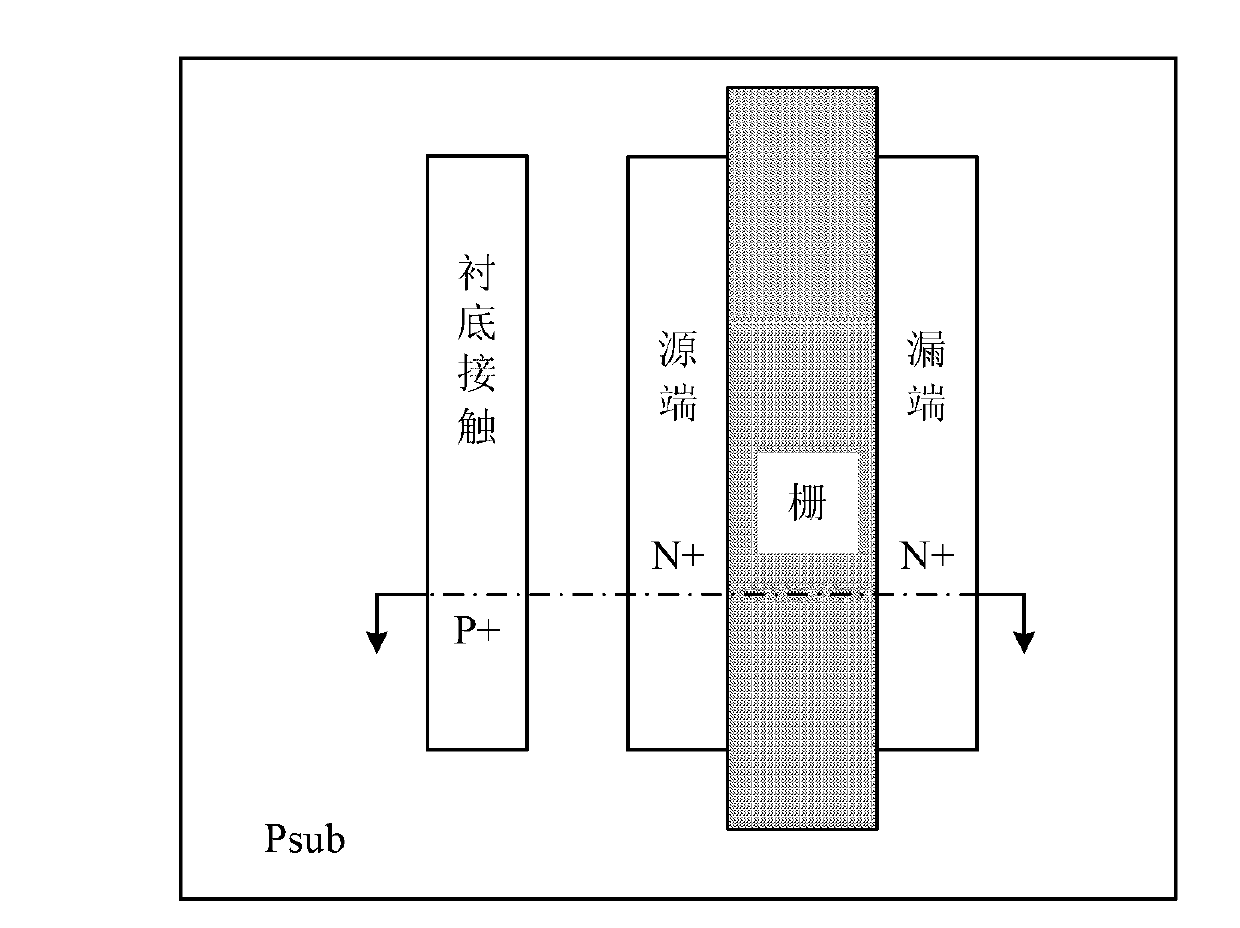

A mos device for integrated circuit chip esd protection

InactiveCN103280458BImprove turn-on uniformityIncrease the secondary breakdown currentSemiconductor devicesElectrical resistance and conductancePower flow

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

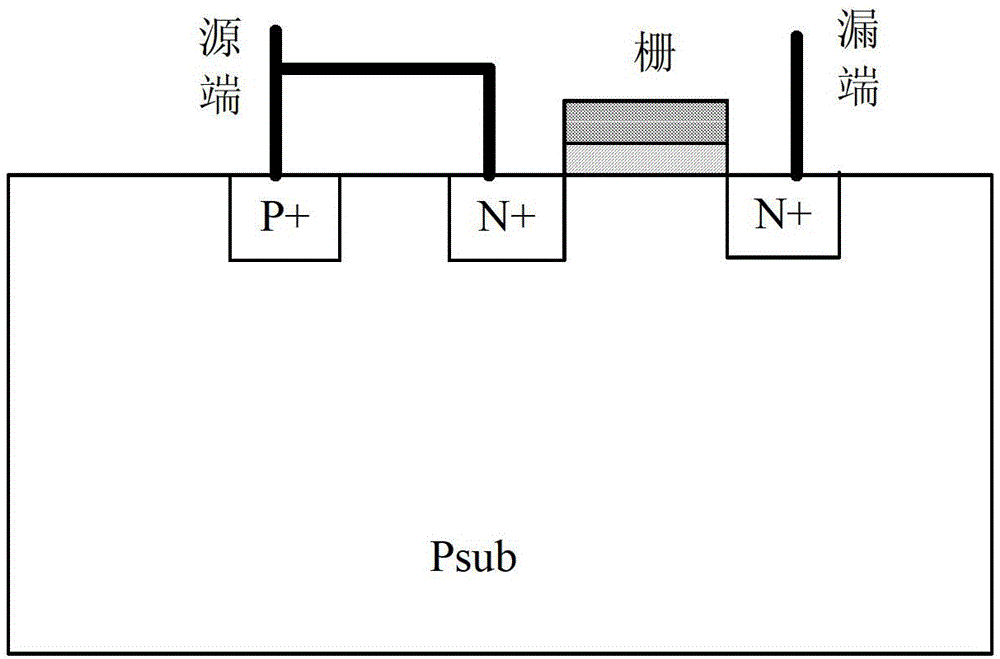

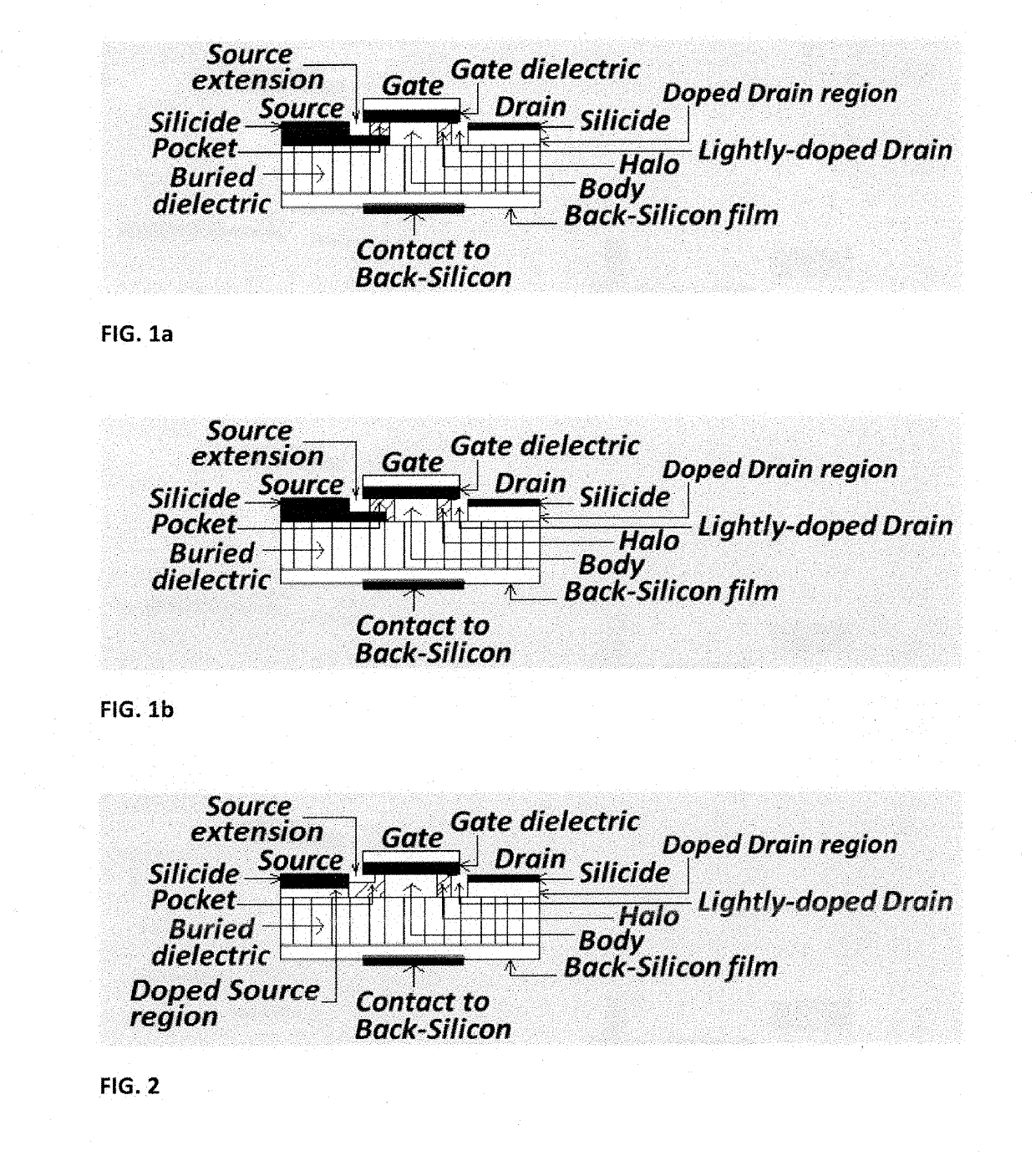

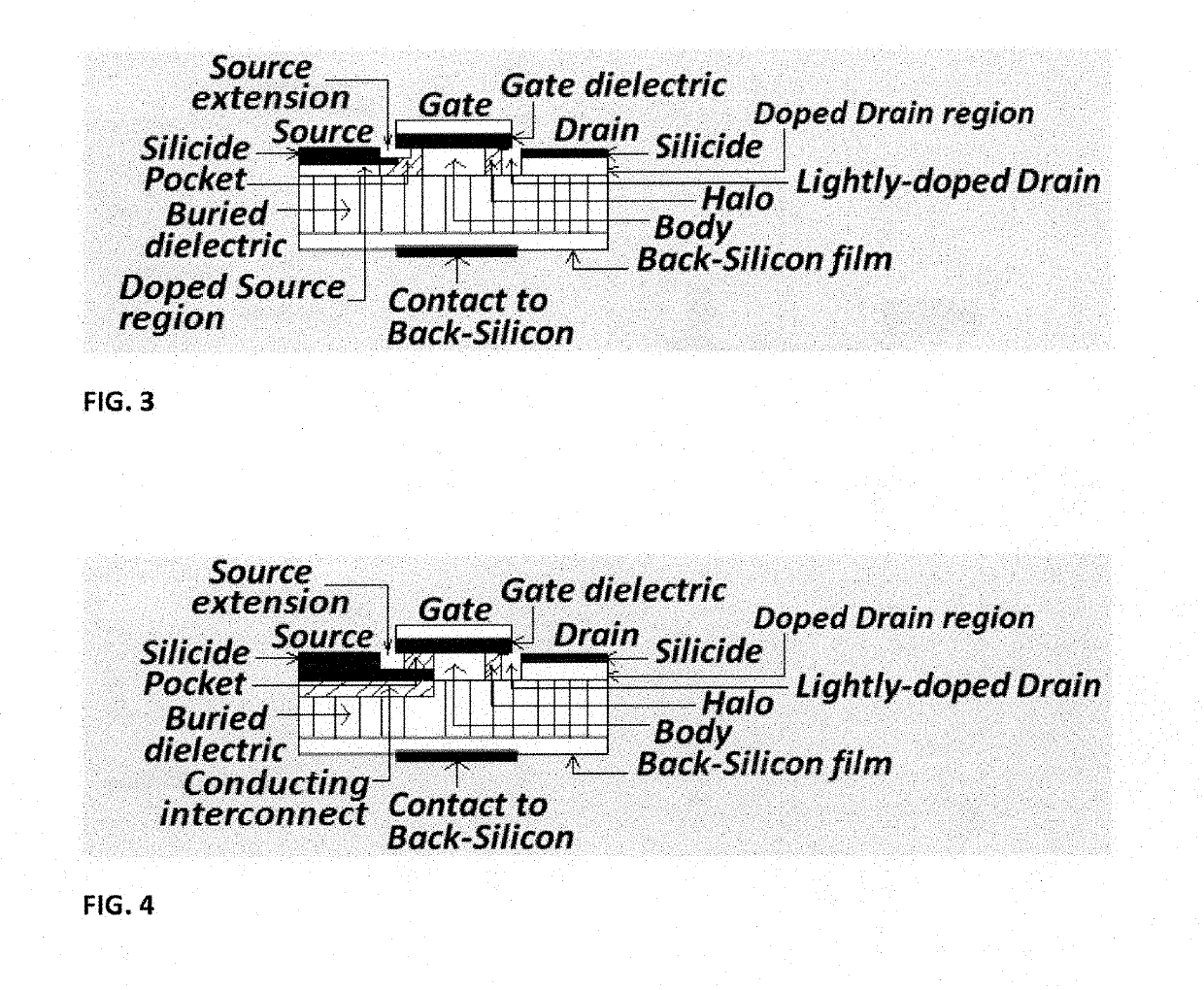

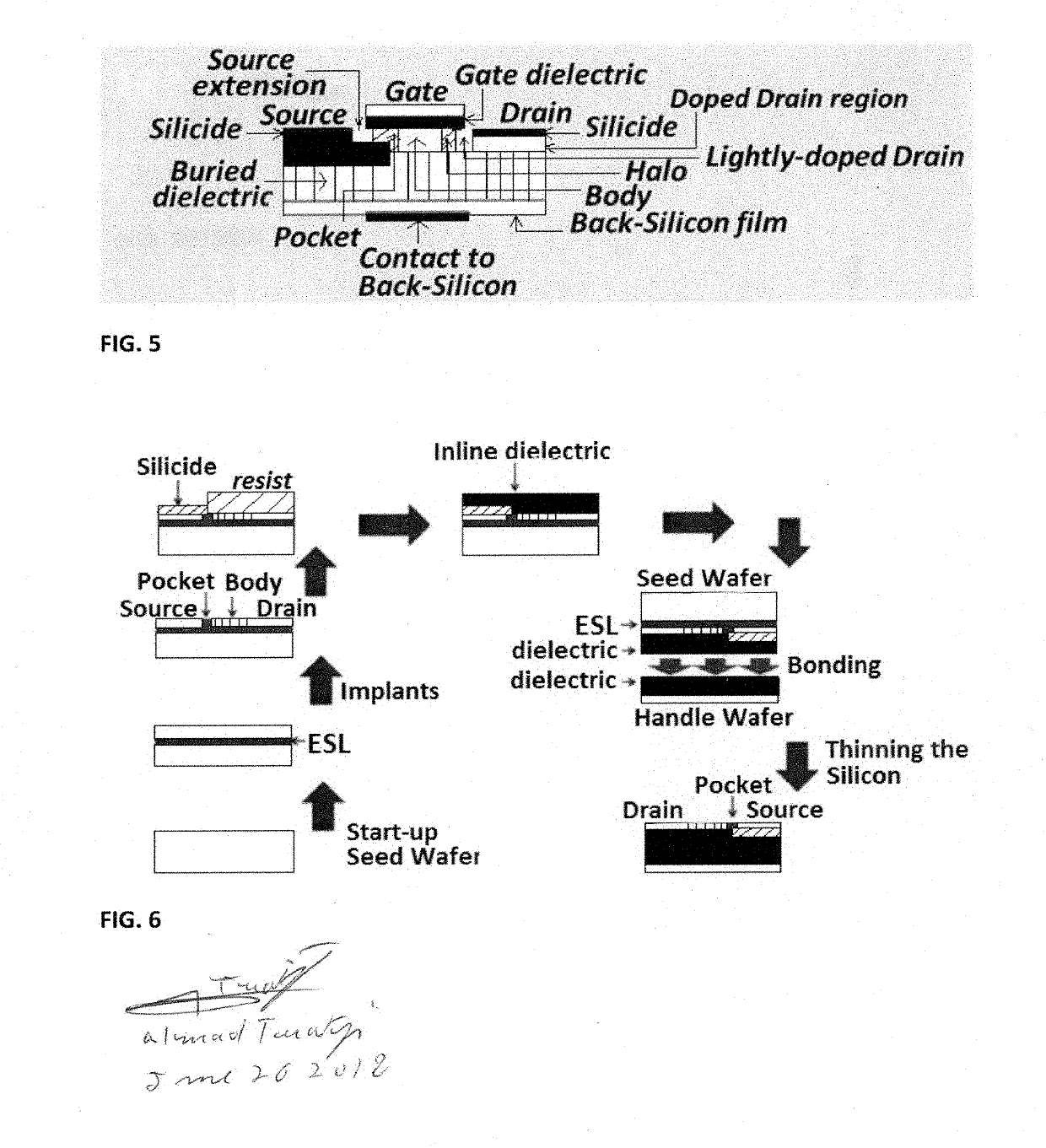

Area-Efficient Single-legged SOI MOSFET structure immune to single-event-effects and bipolar latch-up

ActiveUS20190097062A1Reduce the impactGuaranteed current efficiencyTransistorSolid-state devicesMOSFETImpact ionization

New device structure for single-legged Silicon-On-Insulator Metal-Oxide-Semiconductor (SOI MOS) transistor is presented. This new structure imposes a hard barrier for an Impact-Ionization current and for transients due to Single-Event-Effects (SEE's) in Body to laterally conduct (or diffuse) to the Source through the Body / Source junction. It forces these currents to conduct instead to the Source through an alternate path made of highly conductive Silicide. This alternate path effectively suppresses the latch-up of the built-in parasitic Bipolar structure without necessitating the incorporation of Body-Tied-Source (BTS) implant into the device structure that increases the total device periphery without correspondingly scaling its device current.

Owner:TARAKJI AHMAD HOUSSAM

Apparatus and method for the concurrent converting of multiple web materials

ActiveUS20060124229A1Reduce effective widthMechanical working/deformationFunction indicatorsComputer scienceProcess engineering

An apparatus for the concurrent converting of multiple web products includes at least a first unwind station and a second unwind station. The apparatus further includes a first web transformation station associated with a first web material unwound from the first unwind station, and a second web transformation station associated with the second web material unwound from the second unwind station. The first and second web transformation stations are disposed such that less than twice the width of the widest web material separates a portion of the first web material in the first web transformation station from a portion of the second web material in the second web transformation station. The method of the invention includes steps of unwinding web materials from rolls at each of the first and second unwind stations and transforming the respective web materials using the first and second web transformation stations.

Owner:THE PROCTER & GAMBNE CO

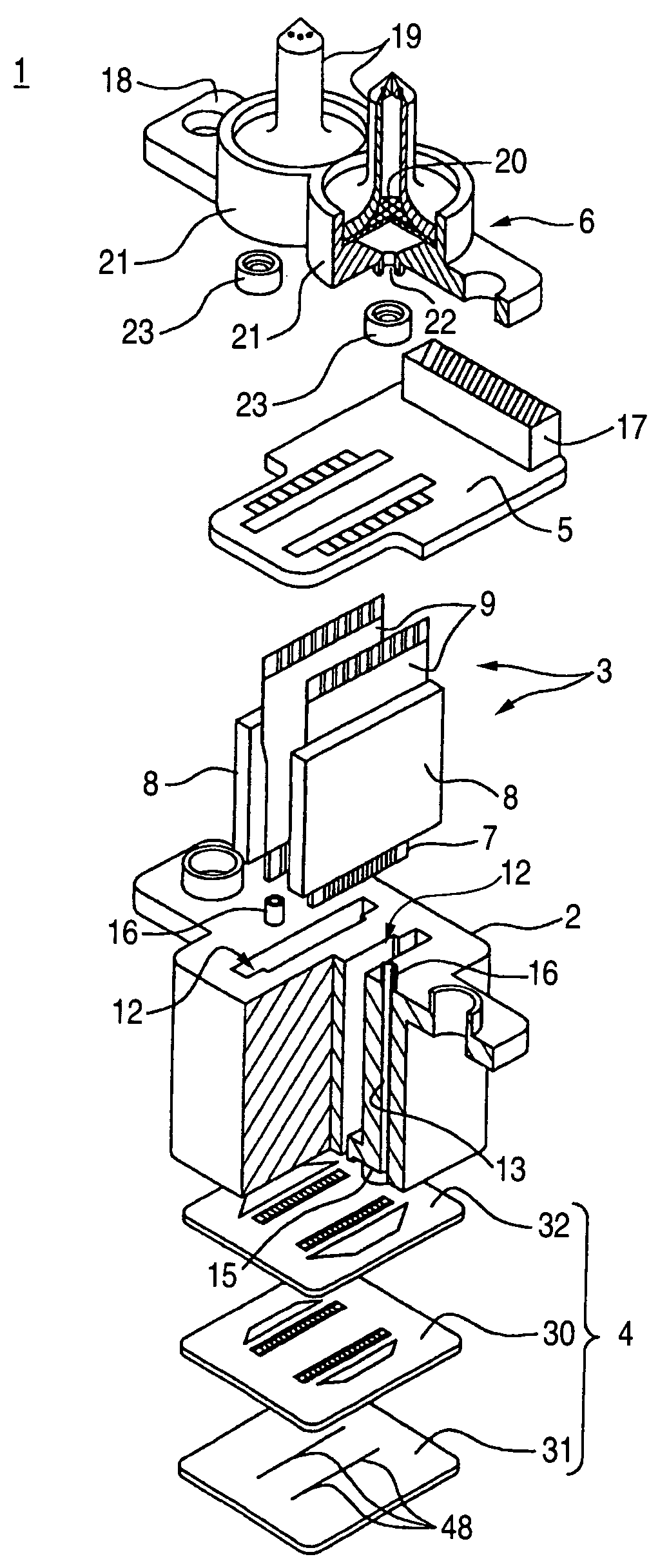

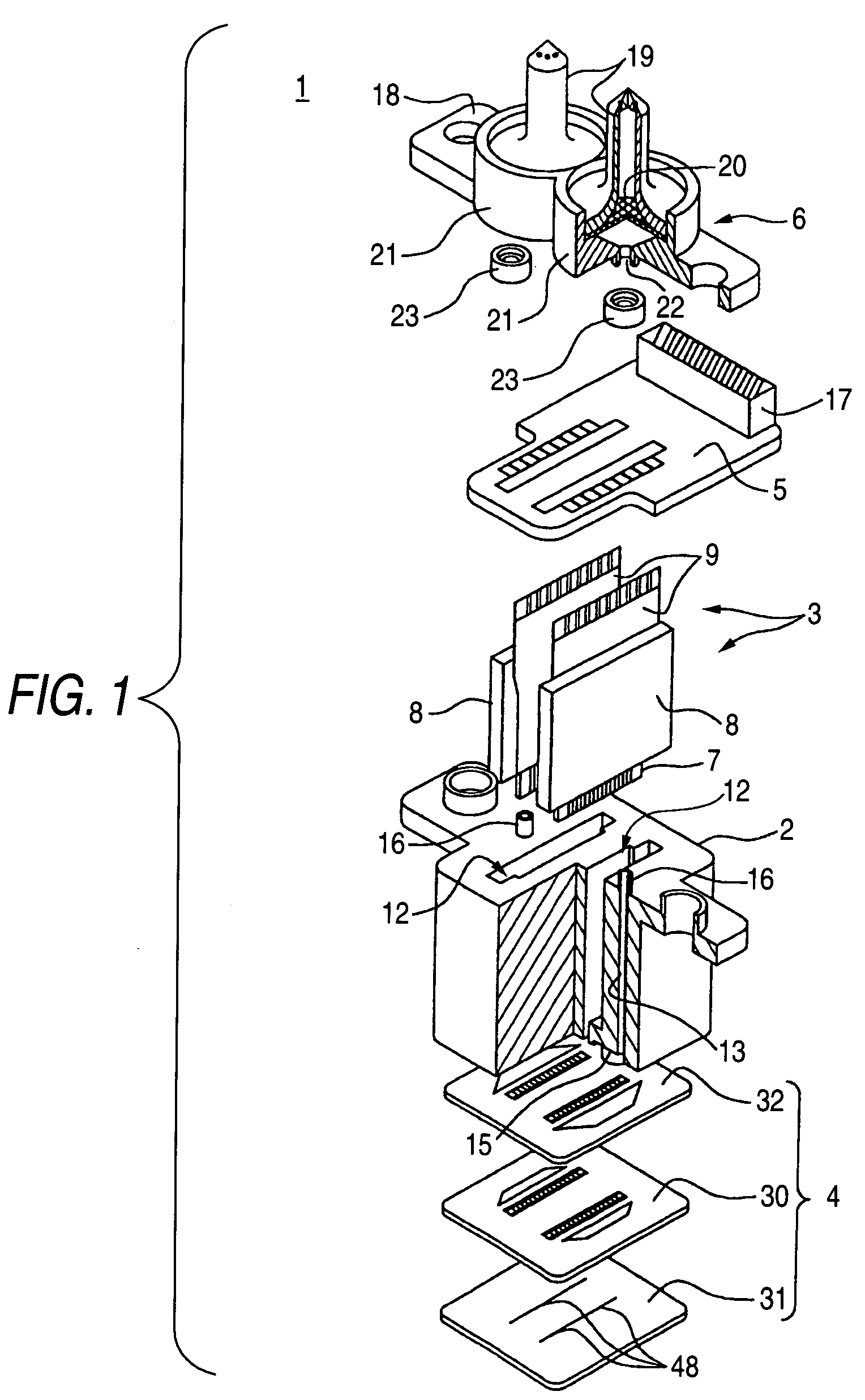

Liquid ejection head, and method of manufacturing the same

InactiveUS20050248626A1Reduce effective widthAvoid flowWriting implementsComponent unification devicesLiquid jetEngineering

In order to manufacture a liquid ejection apparatus, a metal board is prepared. The metal board is subjected to a plastic working to form a plurality of recesses on a first face in a first region of the metal board. Through holes are punched so as to communicate the recesses and a second face of the metal board. The metal board is subjected to a plastic working to form a plurality of dents in a second region of the meal board. A metallic nozzle plate formed with nozzles is joined onto the second face of the metal board, such that each of the nozzles is communicated with one of the through holes.

Owner:SEIKO EPSON CORP

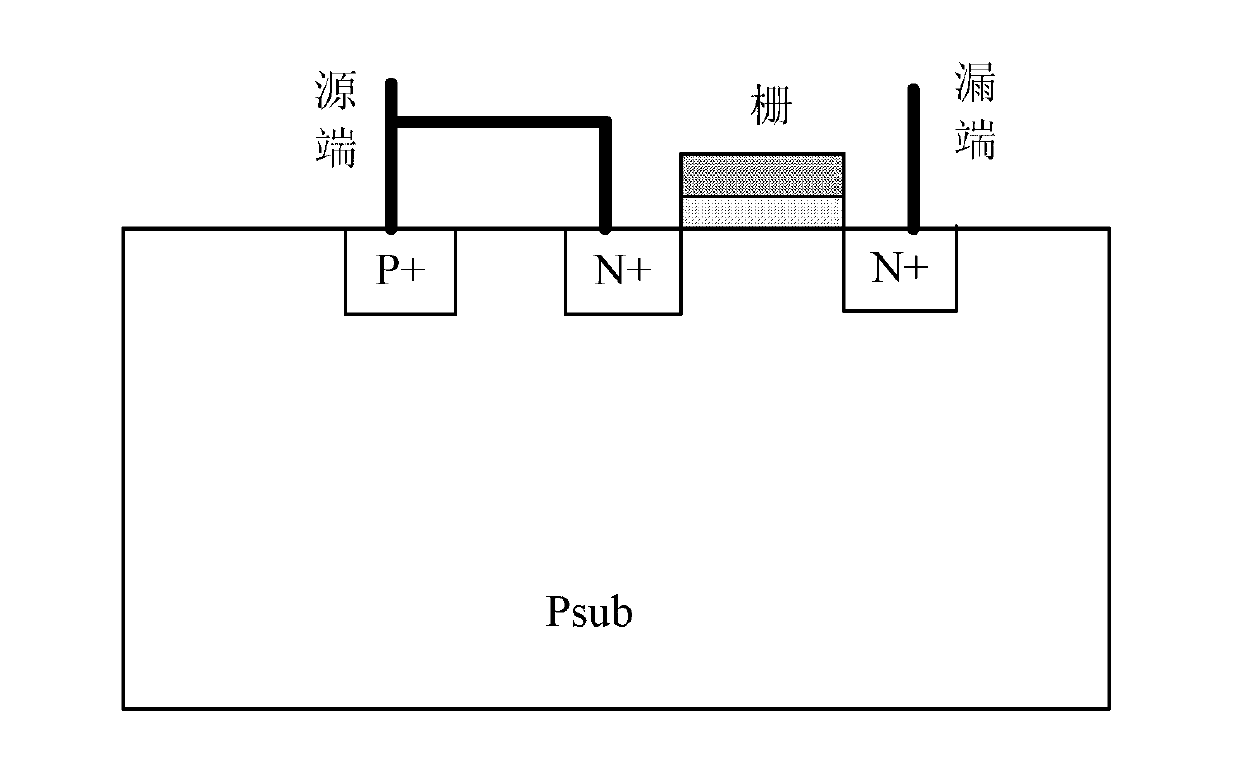

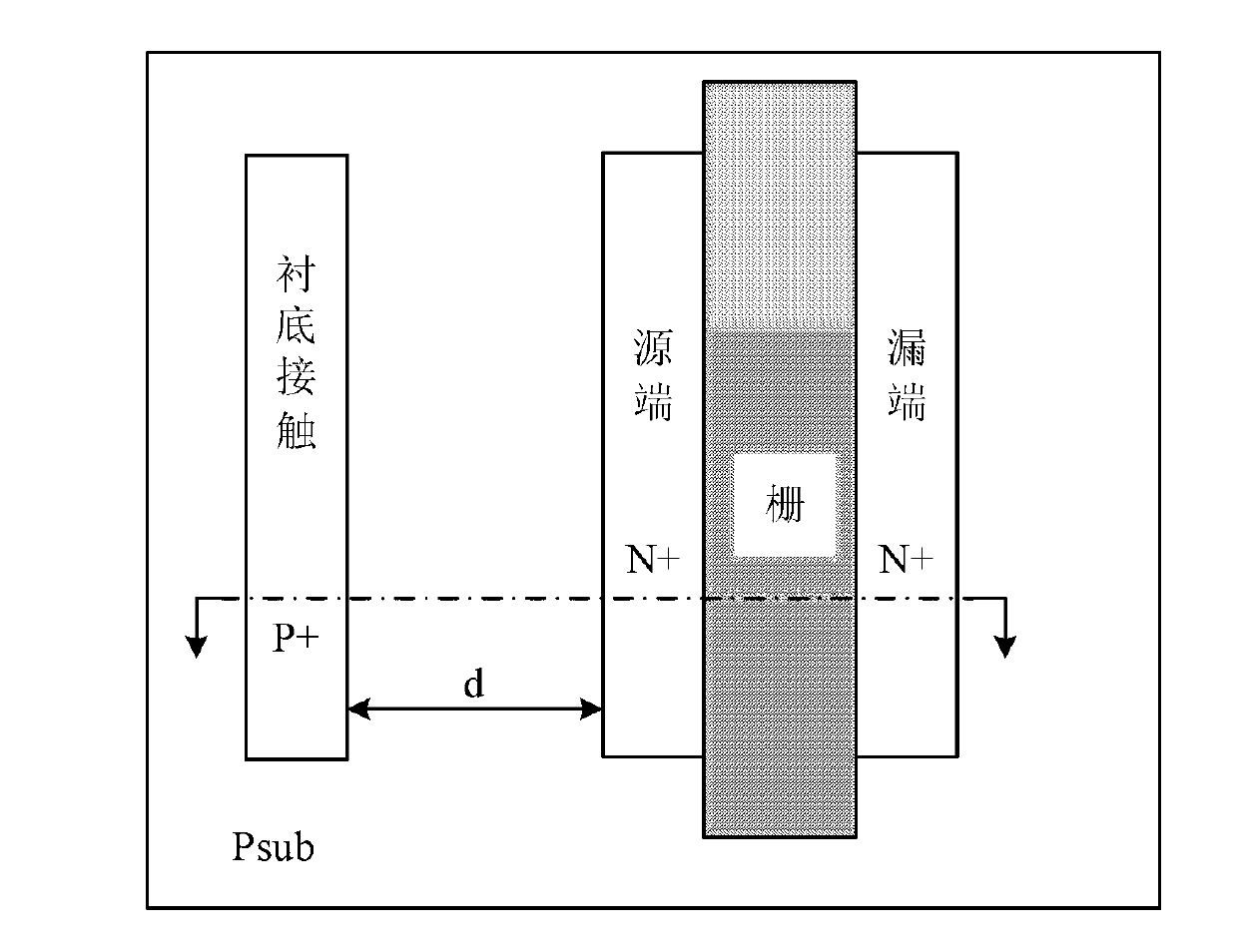

Current sampling circuit achieved through LDMOS devices

ActiveCN104714073ASmall footprintImprove matchCurrent/voltage measurementSemiconductor devicesLDMOSElectrical current

The invention discloses a current sampling circuit achieved through LDMOS devices. A sampling tube and a sampled tube are both the LDMOS devices, the sampling tube is arranged in the middle area of the sampled tube, and the effective width of a source region of the sampling tube is determined by the contact width of an N+ region of the resource region and a grid electrode. A voltage resisting buffer layer is arranged in a drift region of a drain region of the sampling tube, the voltage resisting buffer layer can define the effective drain region drift region aligned to the effective part of the source region, and meanwhile the surrounding range of the whole drain region drift region is not reduced. The sampling ratio of the circuit can be improved by reducing the effective width of the source region, and due to the fact that the effective drain region drift region is aligned to the N+ region of the source region, parasitic resistance between the source region and the drain region of the sampling tube and parasitic resistance between the source region and the drain region of the sampled tube are in proportion, and the stability of the sampling ratio can be improved. The matching degree and stability of the sampling tube and the sampled tube can be improved, the occupied area of the circuit can be reduced, and the integration degree can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Compact thermal actuated variable optical attenuator

InactiveUS8666218B2Improved optical shutterLow costOptical light guidesEngineeringOptical attenuator

A MEMS variable optical attenuator (VOA) chip includes a frame having a planar surface, a micro-electric actuator with a movable optical shutter arranged with respect to the planar surface of the frame, where the VOA is actuated by thermal expansion. The micro-electric actuator comprises semiconductor conductors (“wires”) that can be moved, upon applying an electrical current, by thermal expansion. In one embodiment, the MEMS VOA chip is configured in a multiple wire arrangement that restricts the shutter movement in a plane.

Owner:AGILTRON

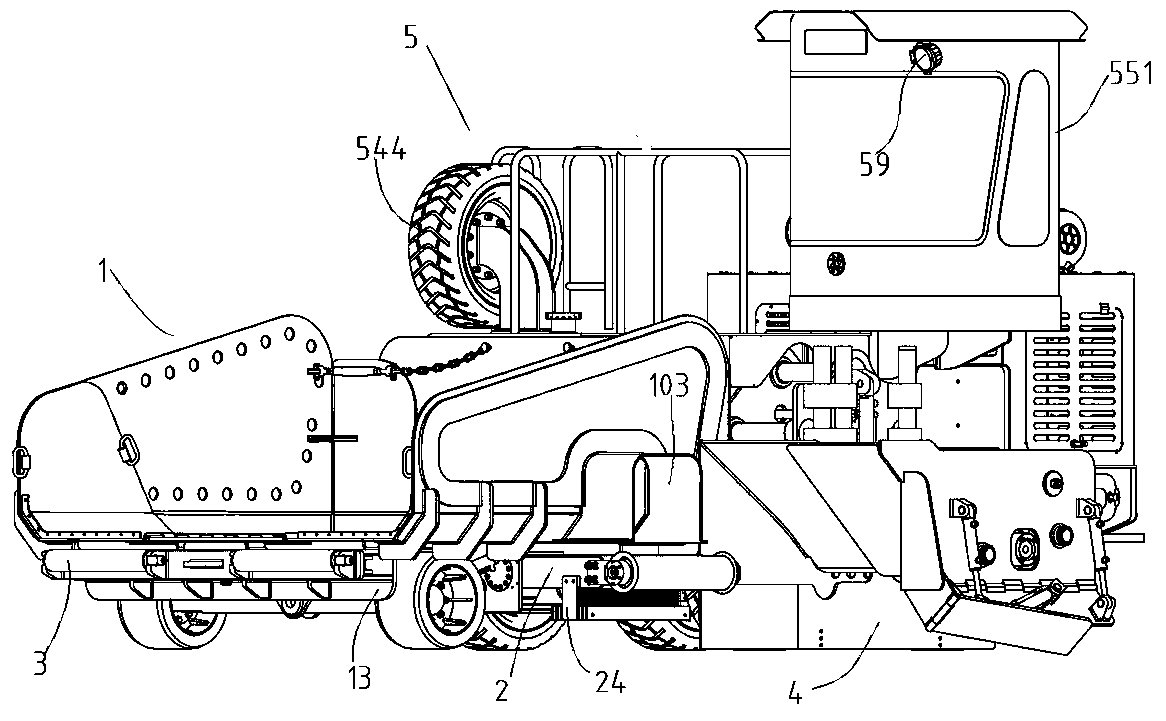

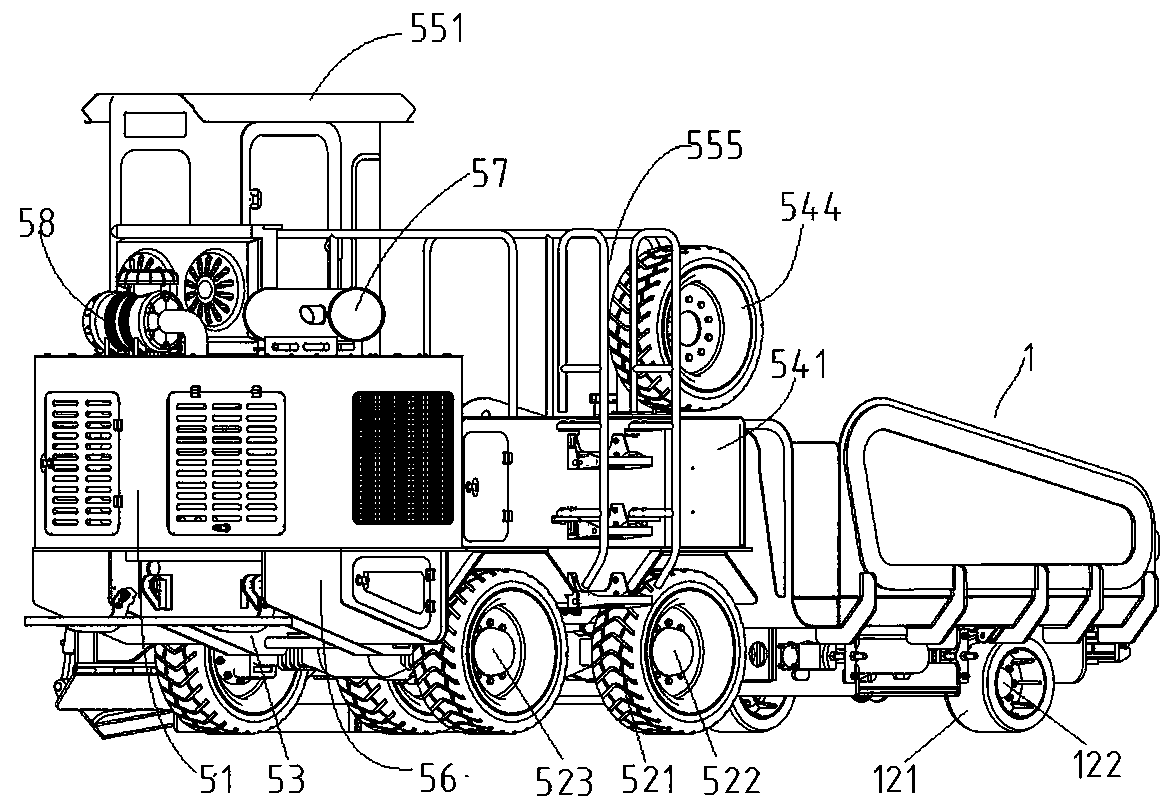

Earth road shoulder forming paver

InactiveCN109853339AAvoid secondary pollutionReduce construction proceduresRoads maintainenceEngineeringAutomation

The invention belongs to the field of the road shoulder forming project, and particularly relates to an earth road shoulder forming paver. The earth road shoulder forming paver comprises a hopper assembly, a sliding form mould and a main machine, wherein the main machine comprises a main machine base frame and a power box arranged on the main machine base frame; the hopper assembly is arranged onthe front side of the main machine, the hopper assembly comprises a hopper and a hopper base frame used for carrying the hopper, and a discharging opening is formed in the left side of the hopper; thesliding form mould is installed on the left front side of the main machine base frame, and the sliding form mould can lift and descent to adjust the height of the road shoulder forming and can laterally translate left and right to adjust the position of the road shoulder forming. The earth road shoulder forming paver is capable of completing the construction of the continuous forming of earth road shoulders on the two sides of a road, the automation degree is high, and labor coast is greatly saved.

Owner:陈建军

MOS (Metal Oxide Semiconductor) device for ESD (Electrostatic Discharge) protection of integrated circuit chip

InactiveCN103280458AImprove turn-on uniformityIncrease the secondary breakdown currentSemiconductor devicesElectrical resistance and conductanceEngineering

The invention relates to an MOS (Metal Oxide Semiconductor) device for ESD (Electrostatic Discharge) protection of an integrated circuit chip, belonging to the technical field of electronics. On the premise that the size of the device is not increased and more chip area is not required to be consumed, substrate resistance between a source region and a substrate contact region is increased by adding a plurality of strip-shaped well regions which are in parallel with the transverse direction of the device in a substrate region below a position between the source region and the substrate contact region, so that the ESD resisting ability of the device is improved; besides, the size of the substrate resistance of the device can be adjusted and the problem of poor starting uniformity of the device can be solved by adjusting the quantity and the width of the strip-shaped well regions and the mutual distances among the strip-shaped well regions, so that the secondary breakdown current of the device is further improved; meanwhile, the manufacturing process of the MOS device is compatible with the standard CMOS process. In conclusion, the MOS device for the ESD protection of the integrated circuit chip provided by the invention has stronger ESD resisting ability due to the increase of the substrate resistance and the production cost of the device is not increased because the size of the device is not increased.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA +1

Support structure apparatus and method

InactiveUS7144211B2Reduce effective widthAvoid restrictionsVehicle with removable loadingVehicle to carry long loadsGravity centerRocker arm

A support structure for supporting and tilting an oversized cargo to reduce the effective width of the cargo. The structure comprises a frame having a base and a stanchion connected to the base. A rocker arm is pivotally coupled to the stanchion to pivot about a pivot axis. The arm includes a first and second end disposed opposite one another. The arm has a center of gravity disposed between the first end and the pivot axis and that biases the arm to pivot in a first pivotal direction. First and second brackets are positioned near the first and second ends of the arm for receiving the cargo. The cargo has a center of gravity disposed between the pivot axis and the second end that causes the arm to pivot in a second pivotal direction opposite the first pivotal direction.

Owner:CRETEX

Self-leveling high heat transfer mold

A mold for sequentially curing sections of a belt includes two end zones, a center zone, and transition zones between each end zone and the center zone. The mold is heated and / or cooled by heat transfer fluid flowing from intake manifolds through heat transfer cavities. The intake manifolds are preferably arranged perpendicular to the mold length. In the end zones and in the center zone, the heat transfer cavities are arranged substantially parallel to the length of the mold. The arrangement of the heat transfer cavities provides for a more controlled cure of the belt by allowing the center zone to maintain a consistent temperature throughout the center zone while allowing a cooler consistent temperature to be maintained in the end zones. The transition zones allow a steep temperature gradient from the cooler end zones to the hotter center zone. Heat transfer rates are adjustable without modification to the body of the mold.

Owner:VEYANCE TECH

Support structure apparatus and method

InactiveUS20070166119A1Reduce effective widthAvoid restrictionsVehicle to carry long loadsLoad securingRotational axisBraced frame

A support structure for supporting and tilting an oversized cargo to reduce the effective width of the cargo. The structure comprises a bolster frame having a base and a stanchion connected to the base. The stanchion extends upwardly from a lower end connected to the base to an upper end opposite the lower end. A cylindrical roller supported is by the upper end of the stanchion for rotational movement relative to the stanchion about a rotational axis. The cylindrical roller is also supported by the stanchion for pivotal movement relative to the stanchion such that the rotational axis pivots relative to the stanchion. The bolster frame also includes a bearing pad connected to the base. The cylindrical roller and the bearing pad at least partially support the oversized cargo. The support structure may be mounted on a trailer for transporting oversized cargo, such as concrete double-tees.

Owner:CRETEX

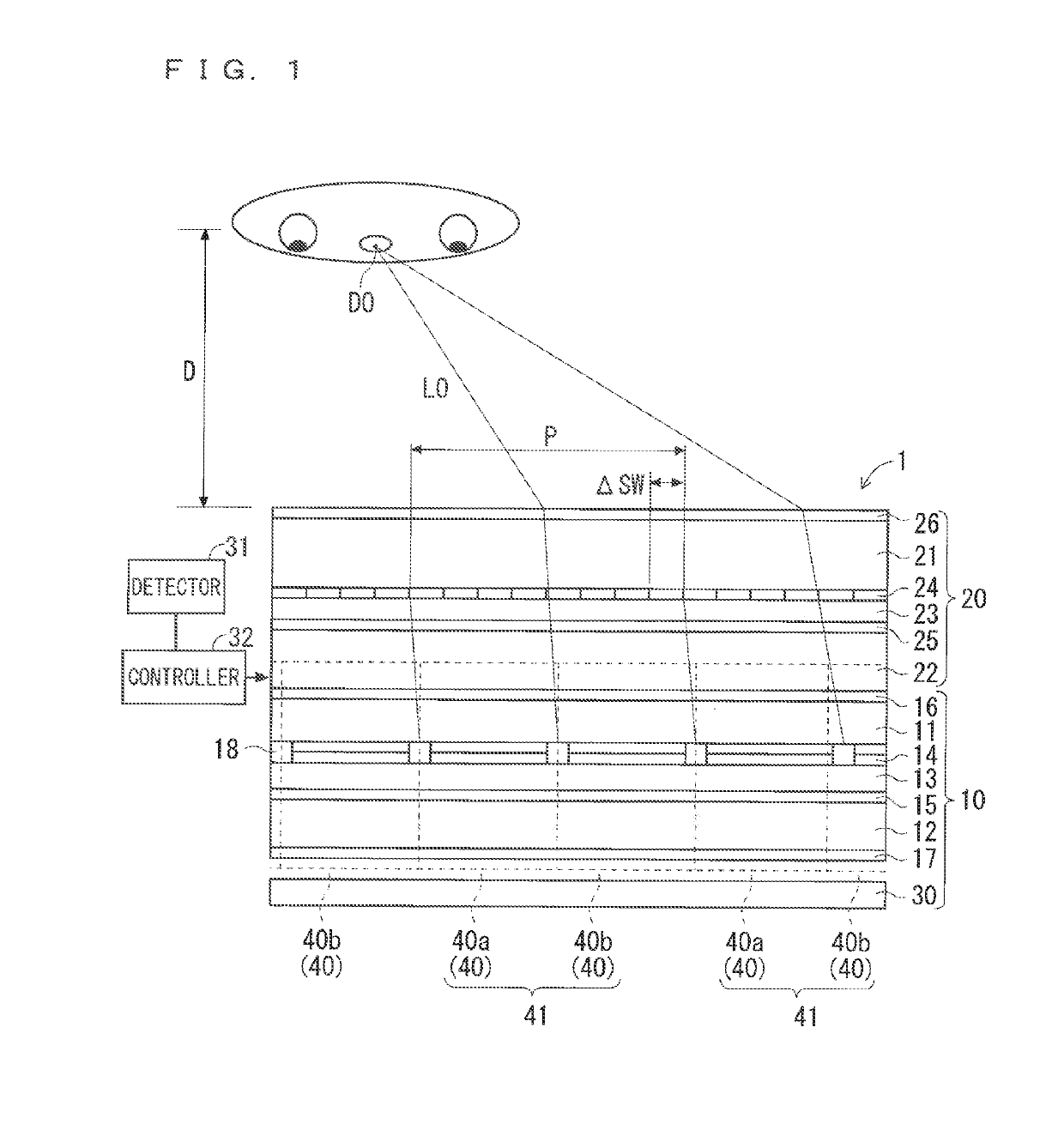

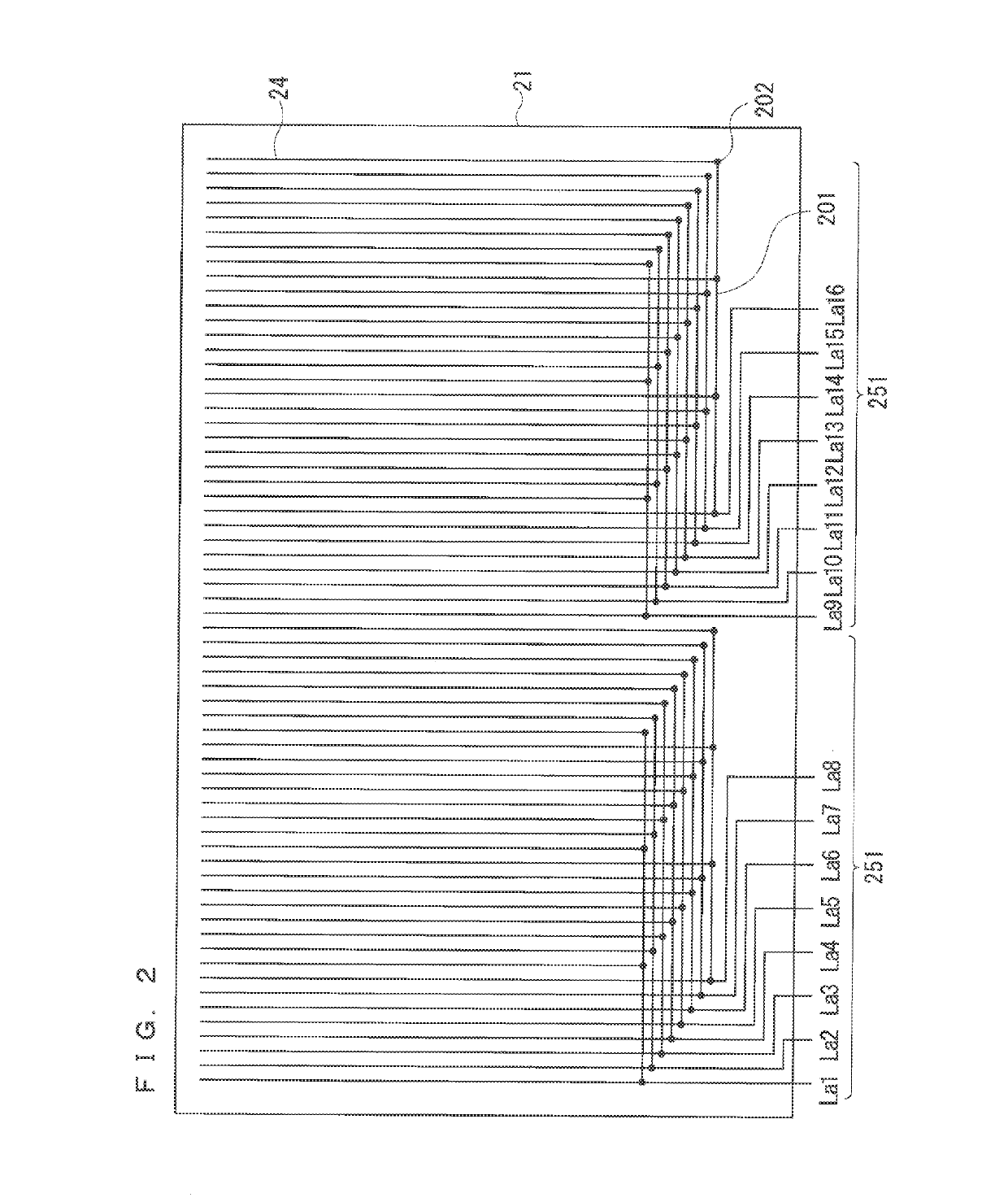

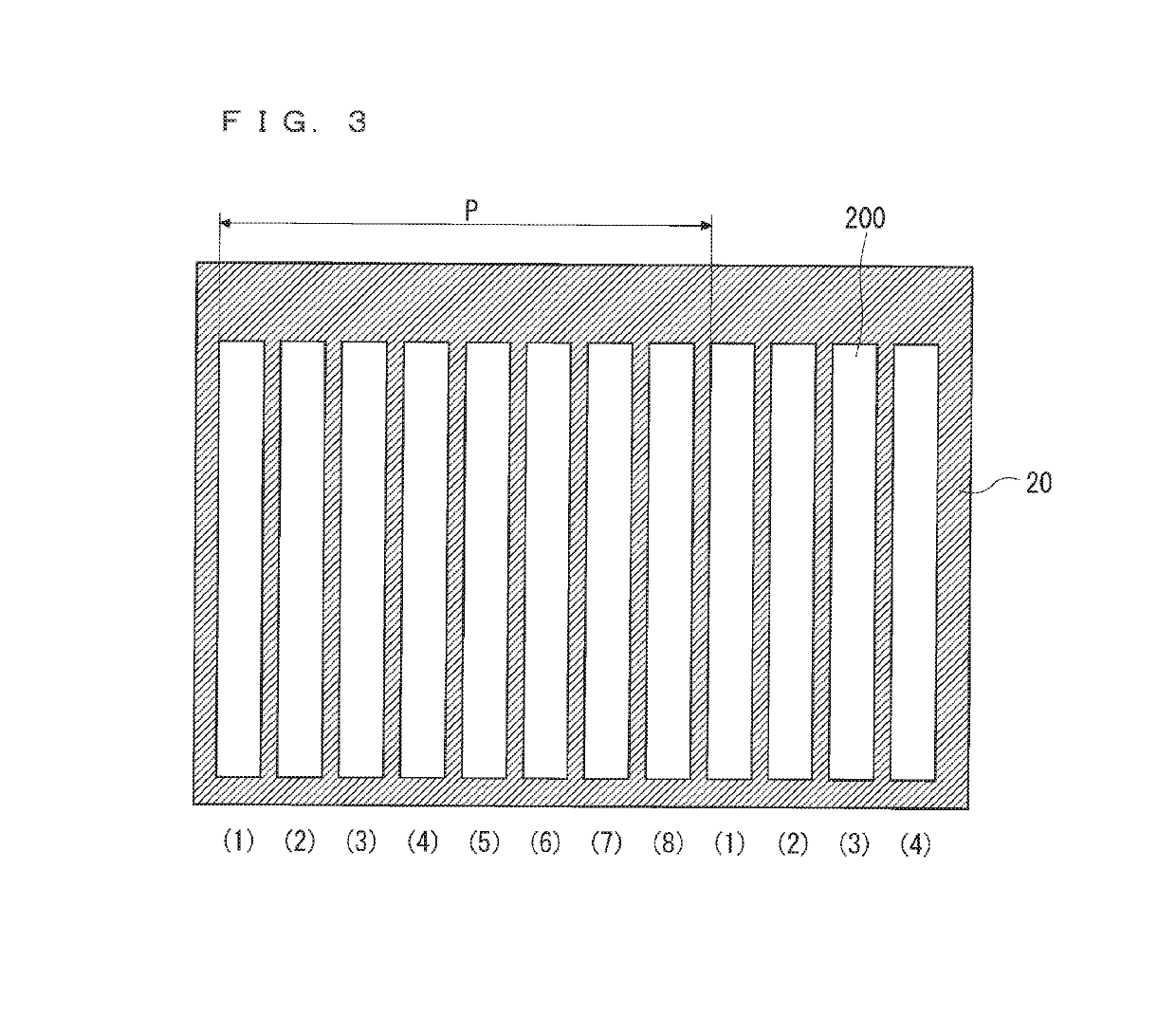

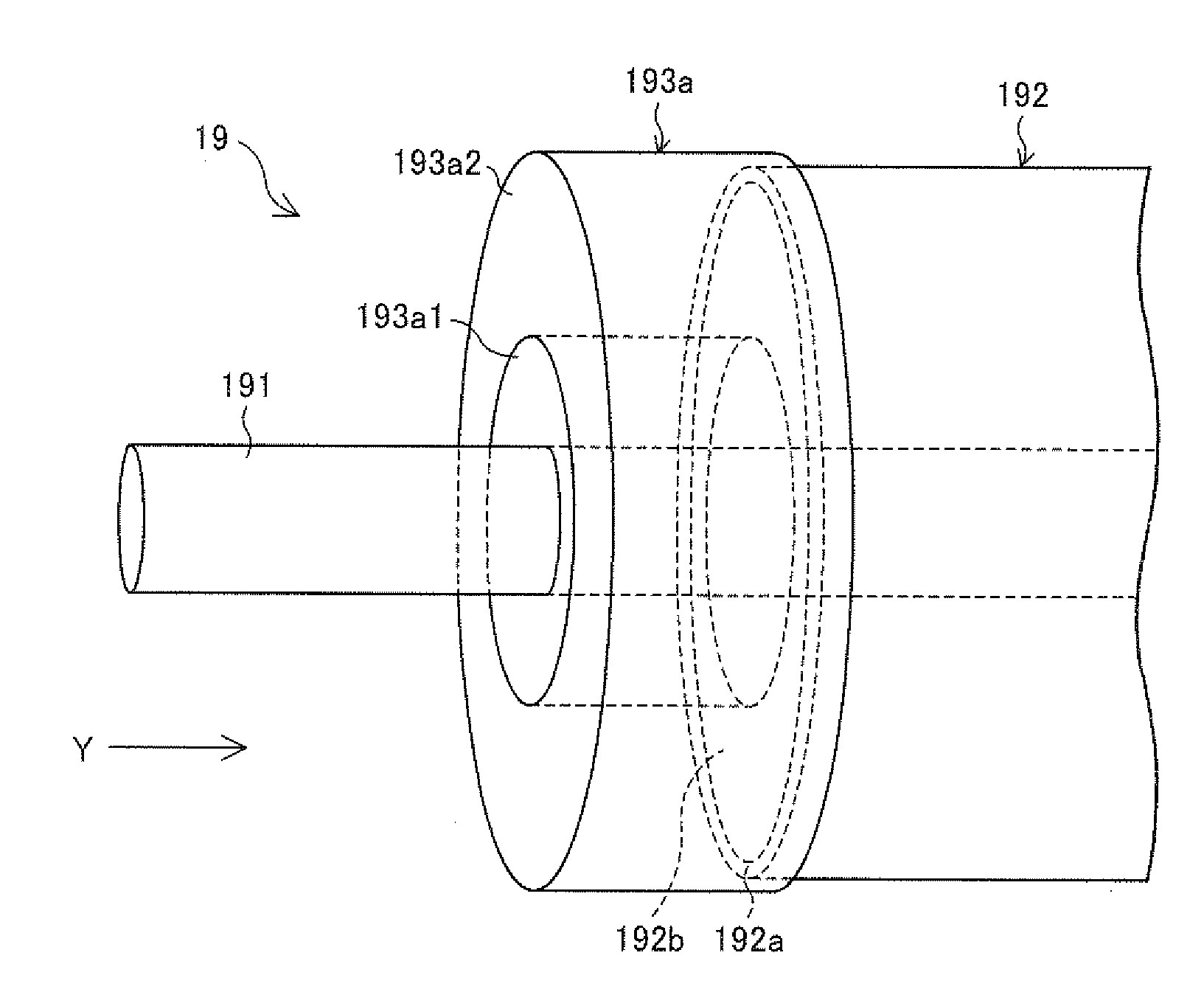

Image display device

InactiveUS20190158816A1Reduce defectsReduce widthSteroscopic systemsOptical elementsControl signalEngineering

A first transparent substrate of a parallax barrier shutter panel includes, in a display area, lower-layer transparent electrodes disposed below an interlayer insulation film and upper-layer transparent electrodes disposed on the interlayer insulation film as vertically extending first transparent electrodes. The first transparent substrate includes, in an input-side connection area adjacent to the display area, a wire for inputting a barrier control signal that is output from a drive IC into the first transparent electrodes. The first transparent substrate includes, in a counter-input-side connection area adjacent to the display area on an opposite side to the input-side connection area with respect to the display area, a common wire for connecting first transparent electrodes that receive input of the same barrier control signal.

Owner:TRIVALE TECH

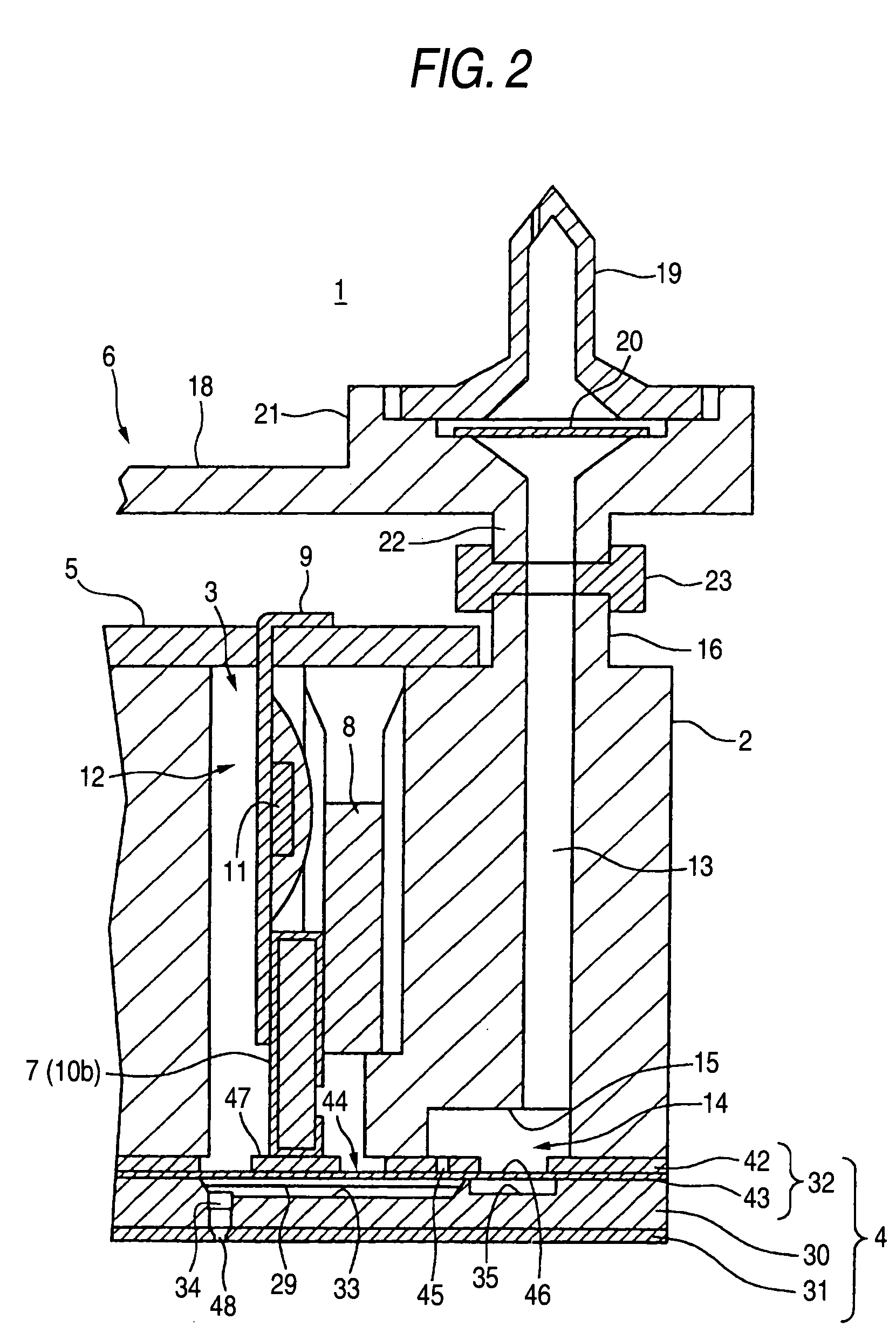

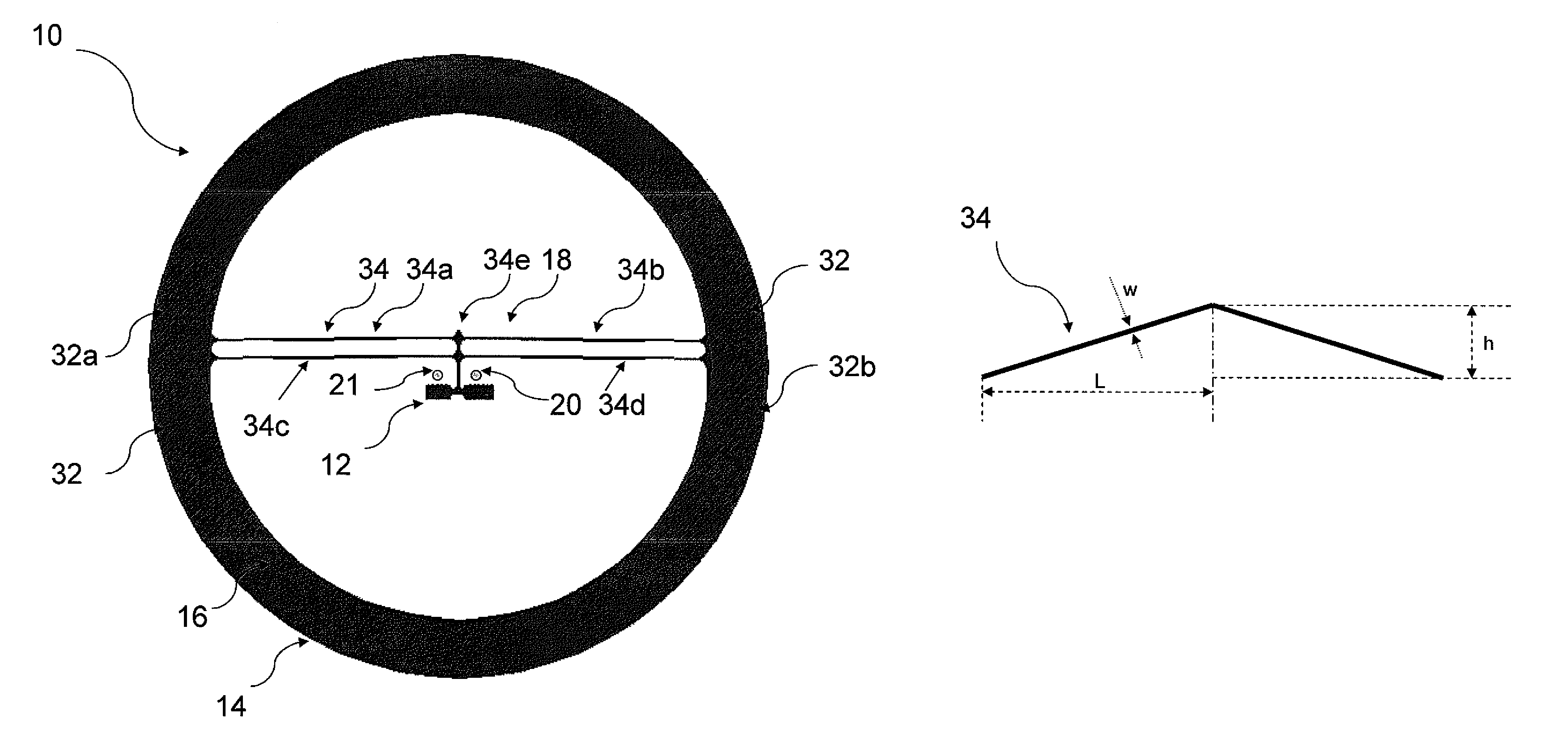

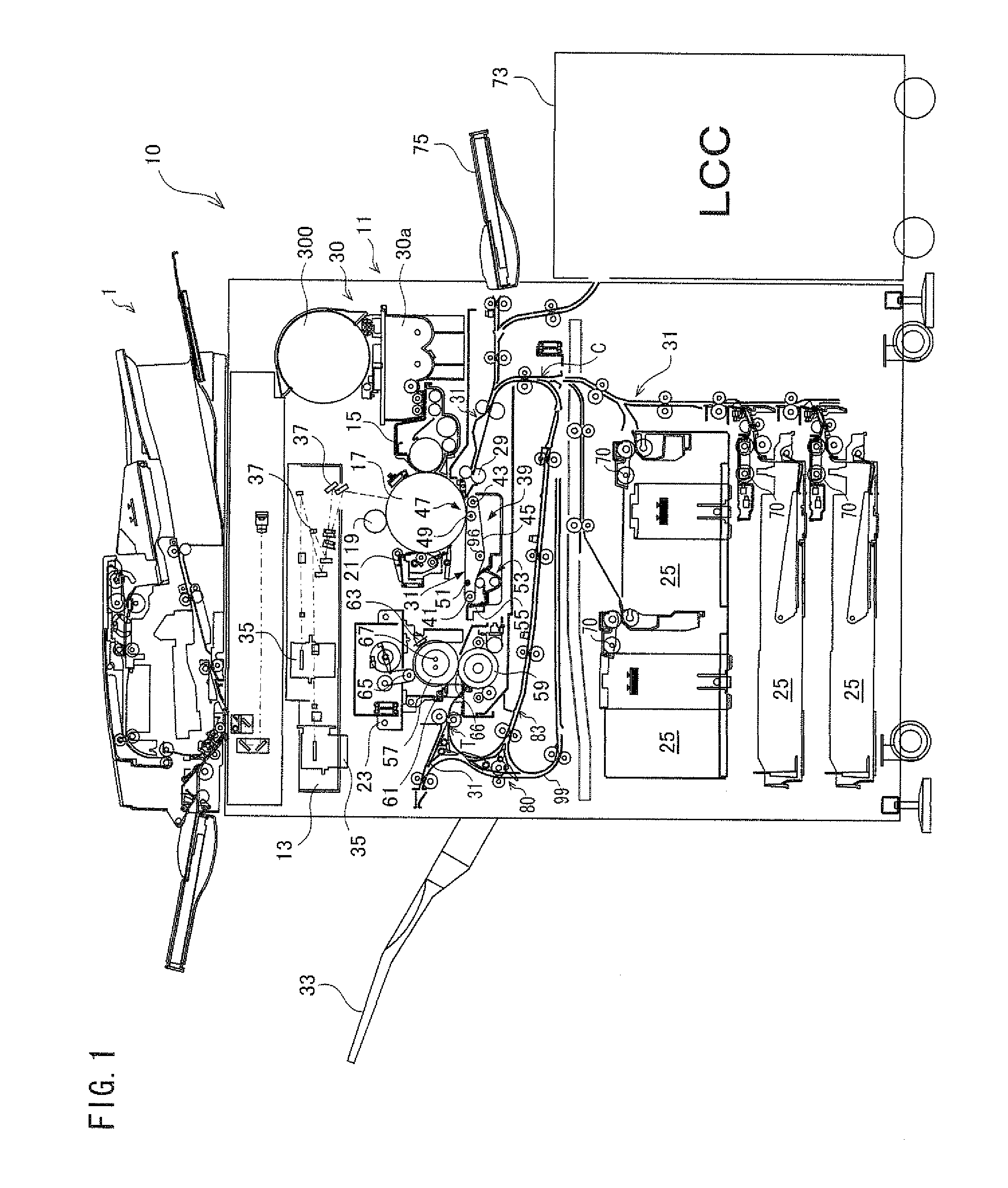

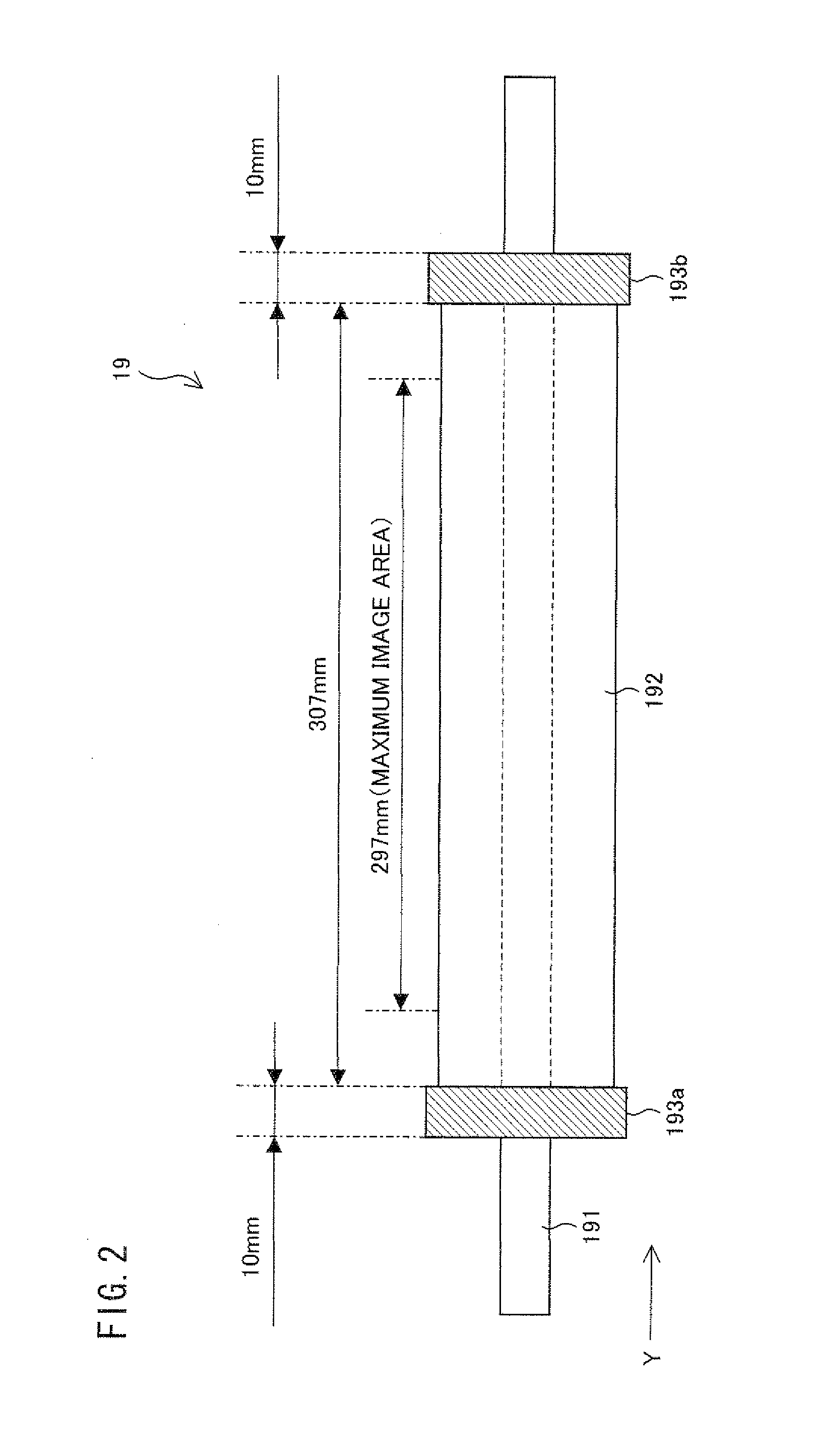

Charging roller, image forming apparatus, and recycling method

ActiveUS20120082482A1Without reduce effective widthReduce effective widthLamination ancillary operationsLaminationElectricityAdhesive

A charging roller has a conductive shaft, a charge emission member provided to the shaft, and a gap securing member provided to the shaft. The gap securing member (i) protrudes toward the photoreceptor drum so as to be closer to the photoreceptor drum than the charge emission member is to the photoreceptor drum and (ii) is in contact with the photoreceptor drum so as to secure a gap between the charge emission member and the photoreceptor drum. A conductive part of the gap securing member and the shaft are bonded to each other by electrically releasing adhesive, so that the gap securing member is provided to the shaft.

Owner:SHARP KK

Rotor for an electric machine, an electric machine and method for manufacturing an electric machine

ActiveUS9941756B2Reduce widthReduce effective widthMagnetic circuit rotating partsManufacturing stator/rotor bodiesElectric machineMechanical engineering

A rotor for an electric machine includes a rotor core having a plurality of rotor sheets (RS1), each of the plurality of rotor sheets including a plurality of flux guide sections, each of the plurality of flux guide sections having a plurality of flux paths and a plurality of flux barriers. The plurality of flux guide sections having a first flux guide section in which a first number of the plurality of flux barriers has a bridge interrupting the flux barrier, and a second flux guide section in which a second number of the plurality of flux barriers has a bridge interrupting the flux barrier. Each bridge is made of a material of high permeance, and the first number of the first flux guide section is different than the second number of the second flux guide section.

Owner:ABB (SCHWEIZ) AG

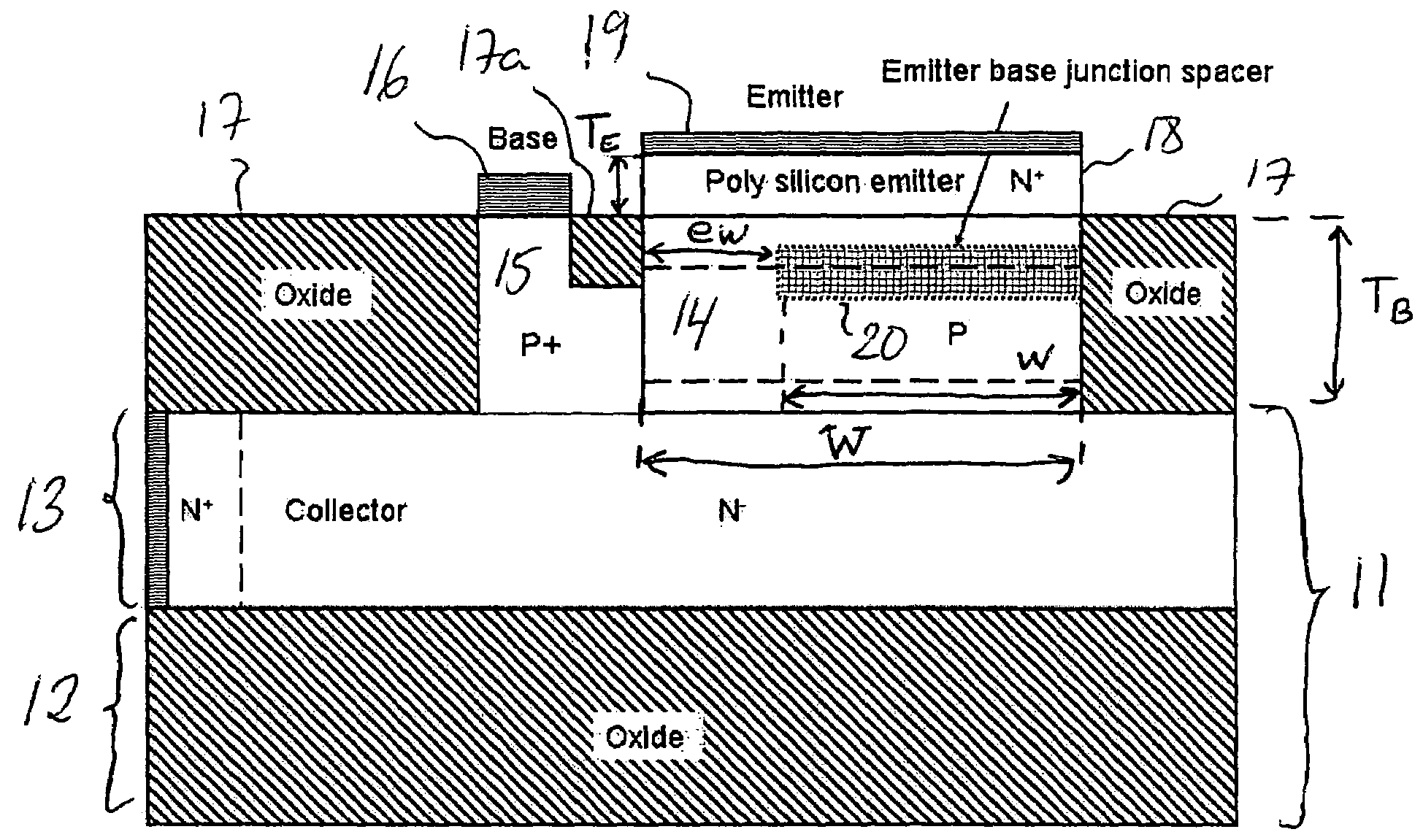

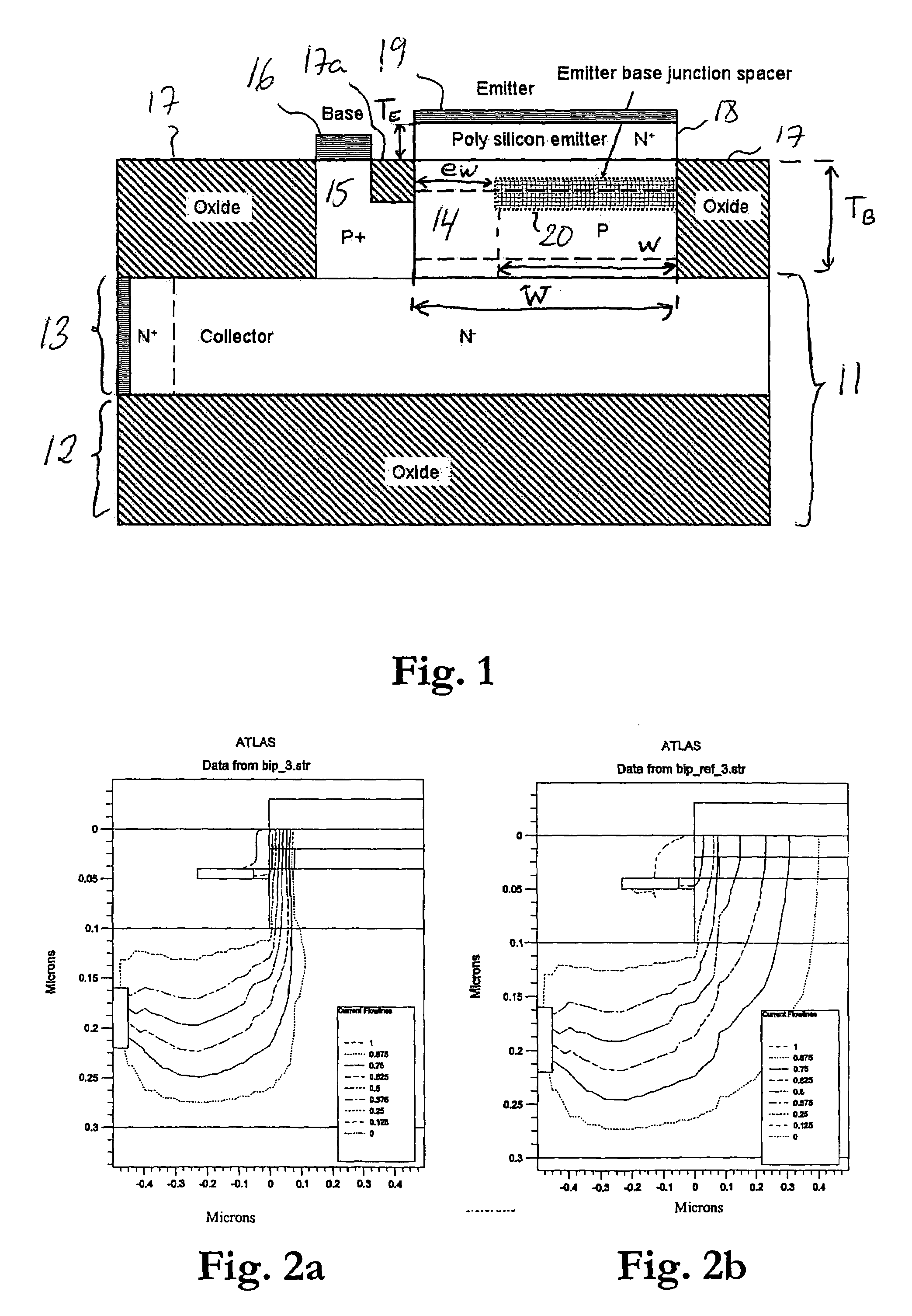

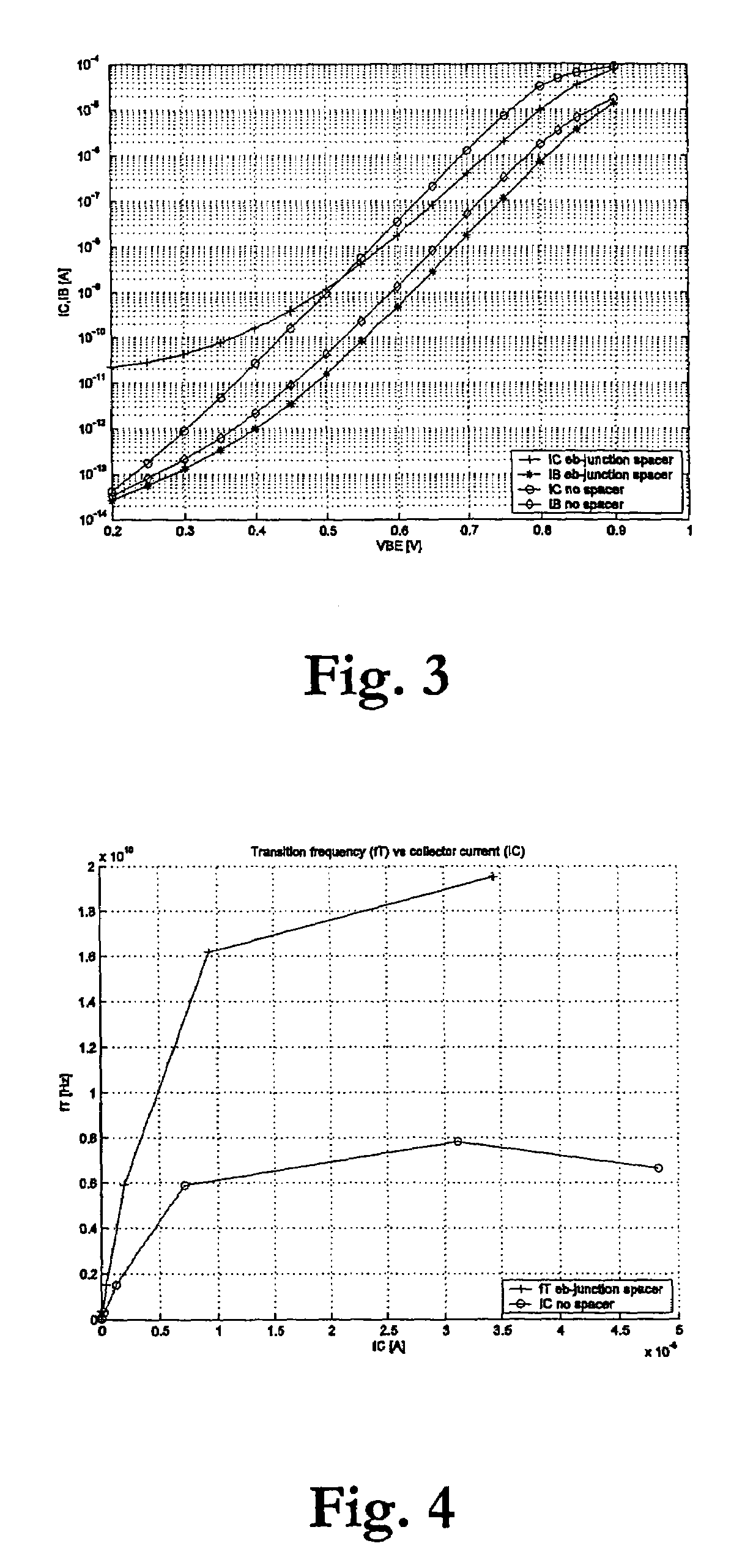

Bipolar transistor

InactiveUS7397108B2Eliminate the effects ofReduce effective widthTransistorSolid-state devicesSoi substrateNitride

A monolithically integrated bipolar transistor has an SOI substrate, a collector region in the SOI substrate, a base layer region on top of and in contact with the collector region, and an emitter layer region on top of and in contact with the base layer region, wherein the collector, base layer, and emitter layer regions are provided with separate contact regions. Further, a region of an insulating material, preferably an oxide or nitride, is provided in the base layer region, in the emitter layer region, or between the base and emitter layer regions, wherein the insulating region extends laterally at a fraction of a width of the base and emitter layer regions to reduce an effective width of the bipolar transistor to thereby eliminate any base push out effects that would otherwise occur.

Owner:INFINEON TECH AG

Roadway-transportable artificial golf practice green apparatus

InactiveUS20060128490A1Reduce widthReduce effective widthGolfing accessoriesEngineeringMechanical engineering

Owner:COX ALVIN E

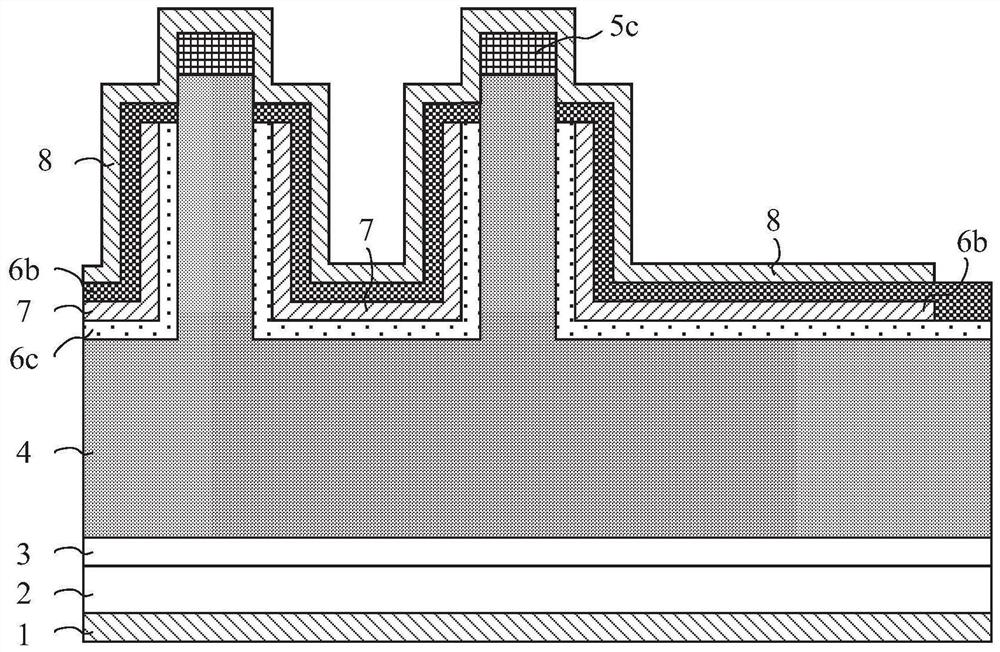

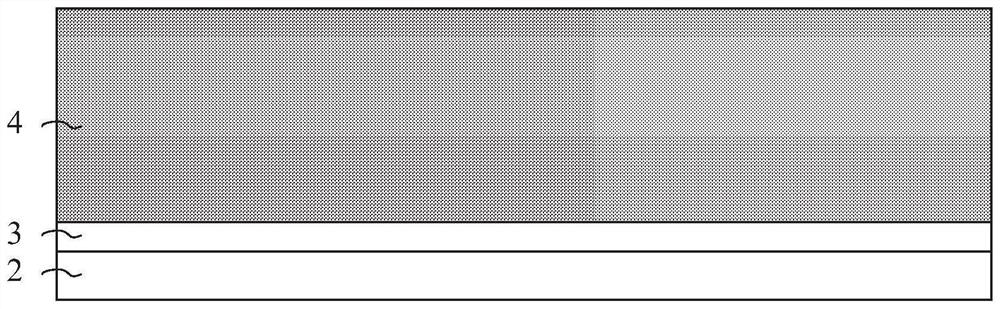

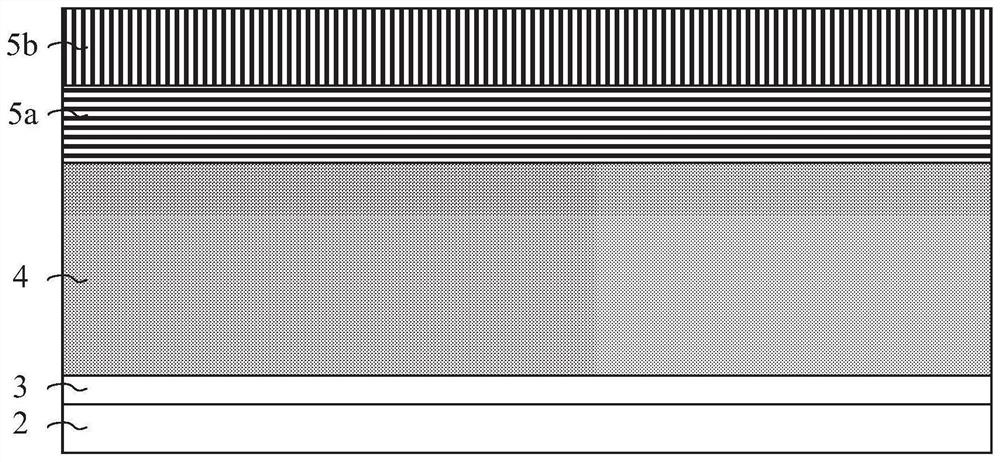

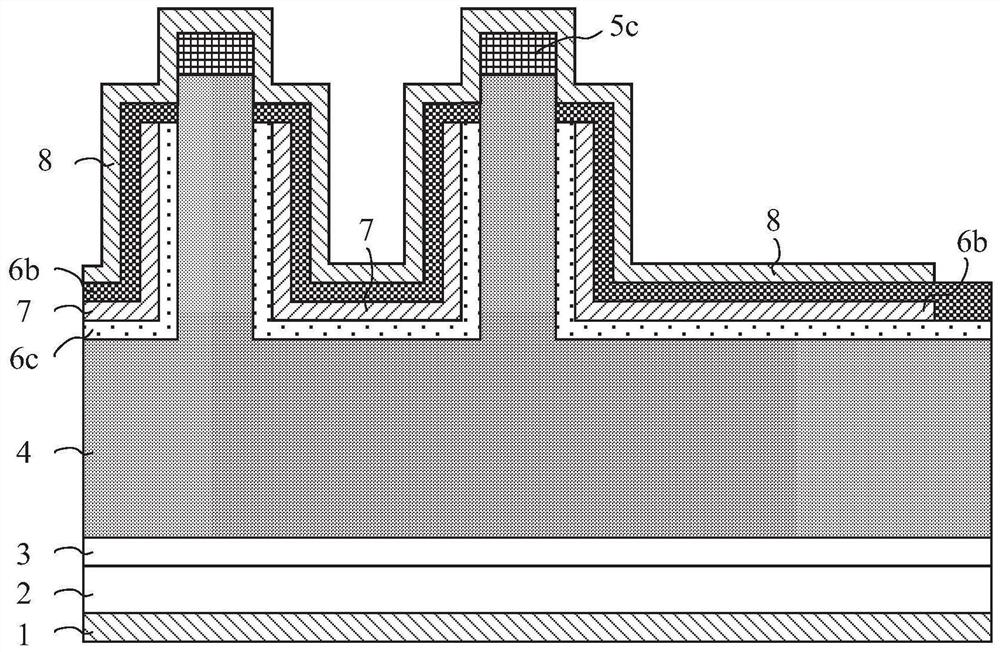

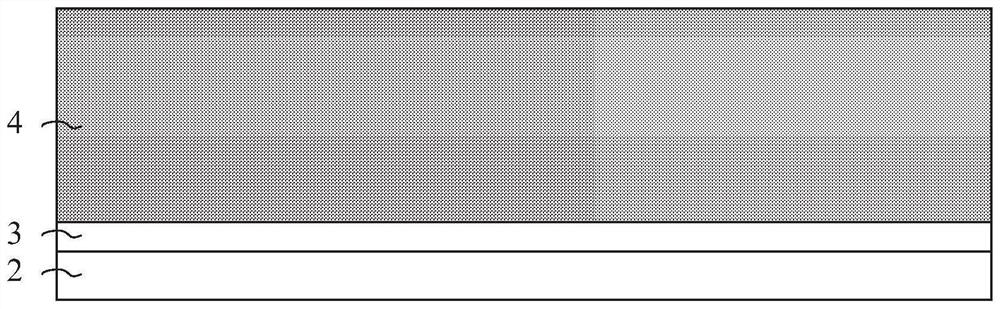

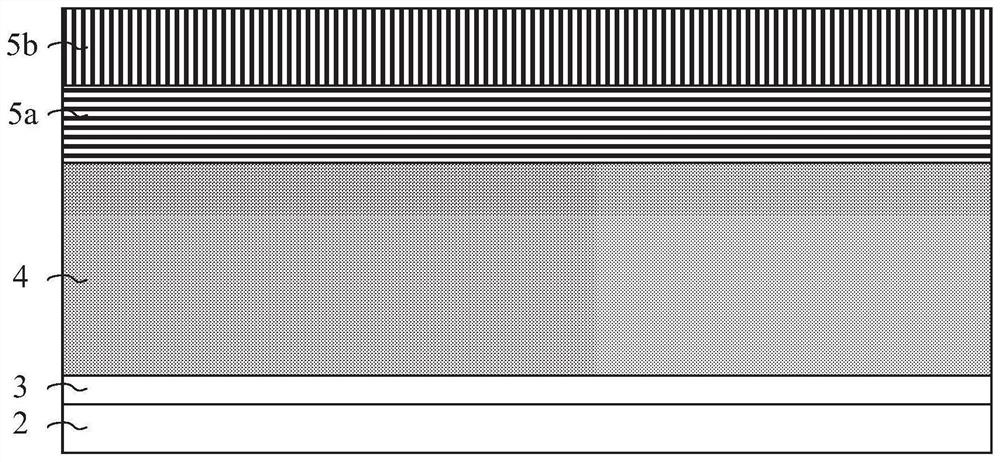

High-threshold power semiconductor device and manufacturing method thereof

ActiveCN112164725AReduce the effective channel widthGood uniformity over a large areaSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention discloses a high-threshold power semiconductor device and a manufacturing method thereof. The high-threshold power semiconductor device sequentially comprises a drain metal electrode, asubstrate, a buffer layer and a drift region from bottom to top, and also comprises: a composite column body on the drift region, formed by a drift region protrusion, a columnar p region and a columnar n region, and a channel layer, a passivation layer, a dielectric layer, a heavily doped semiconductor layer, a gate metal electrode and a source metal electrode. The composite column body is formedby sequentially depositing a p-type semiconductor layer and an n-type semiconductor layer on the drift region and then etching the p-type semiconductor layer and the n-type semiconductor layer; wherein the channel layer and the passivation layer are formed by deposition in sequence. Therefore, the device is divided into a cellular region and a terminal region. The dielectric layer, the heavily doped semiconductor layer, the gate metal electrode and the source metal electrode only exist in the cellular region, and the passivation layer of the terminal region extends upwards and wraps the outerside of the channel layer. The structure can improve the threshold voltage of the device, improve the blocking characteristic of the device, and reduce the gate capacitance.

Owner:SOUTHEAST UNIV

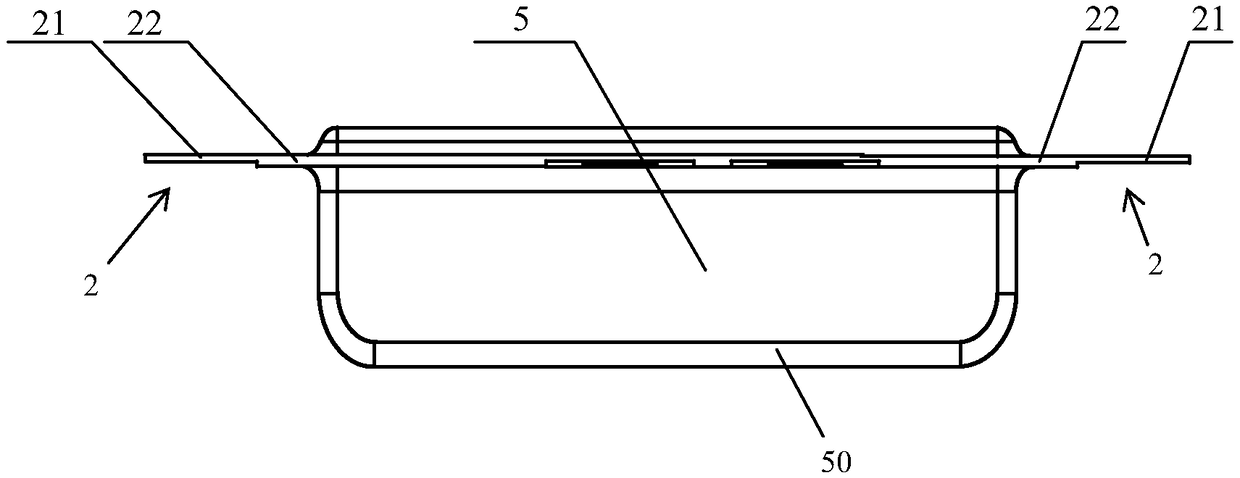

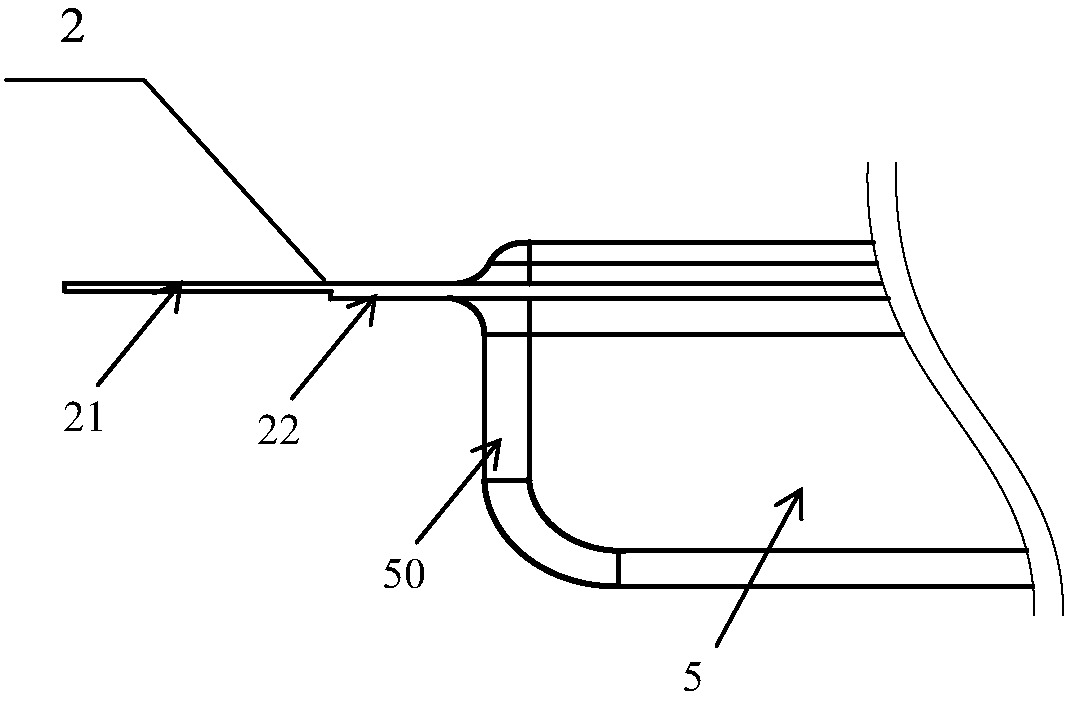

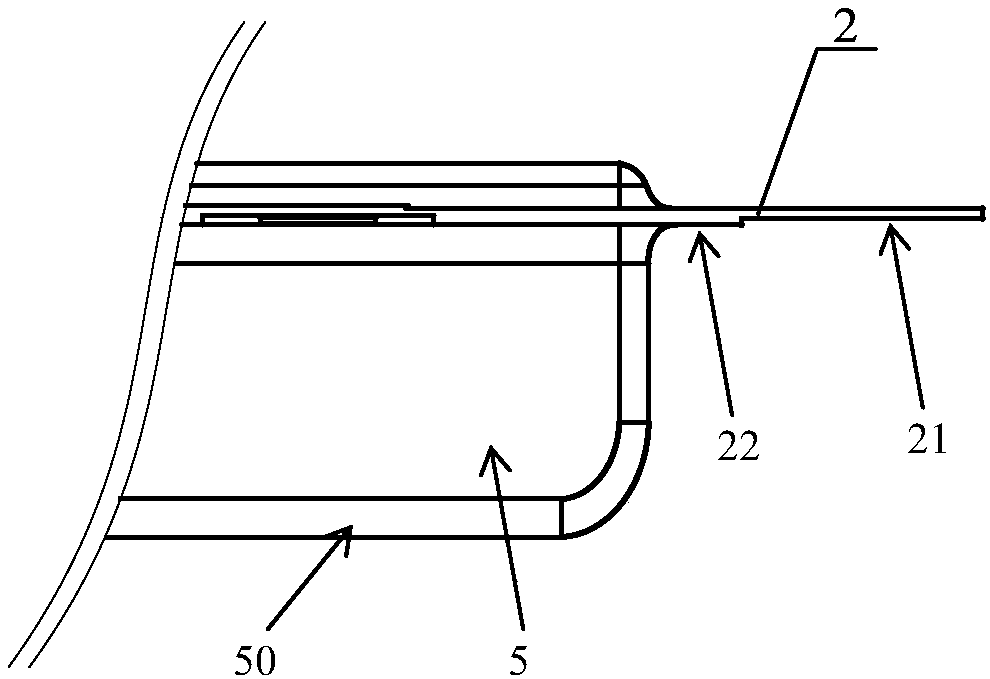

A polymer lithium ion battery and a preparation method thereof

InactiveCN109103493AReduce effective widthMultiple spaces and possibilitiesFinal product manufactureElectrolyte accumulators manufactureElectrical batteryCorrosion

The invention discloses a polymer lithium ion battery, characterized by comprising a battery body (5), the exterior of the battery body (5) is provided with a battery case (50), and left and right sides of the battery case (50) are respectively provided with a stepped side (2). In addition, the invention also discloses a preparation method of a polymer lithium ion battery. The invention disclosesa polymer lithium ion battery and a preparation method thereof, which can effectively encapsulate polymer lithium ion batteries, the side edge of the polymer lithium ion battery is ultra-thin, and theeffective width of the battery can be reduced; the technical scheme provides more space and possibility for the capacity improvement of the battery, and ensures the good sealing property of the polymer lithium ion battery, effectively avoids the bad resistance of the shell and the corrosion of the electrolyte to the aluminum plastic shell; the battery can be conveniently manufactured, which is beneficial to the wide application and has great significance in the production practice.

Owner:TIANJIN LISHEN BATTERY

A high-threshold power semiconductor device and its manufacturing method

ActiveCN112164725BReduce the effective channel widthReduce effective widthSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMetallic electrode

Owner:SOUTHEAST UNIV