Area-Efficient Single-legged SOI MOSFET structure immune to single-event-effects and bipolar latch-up

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

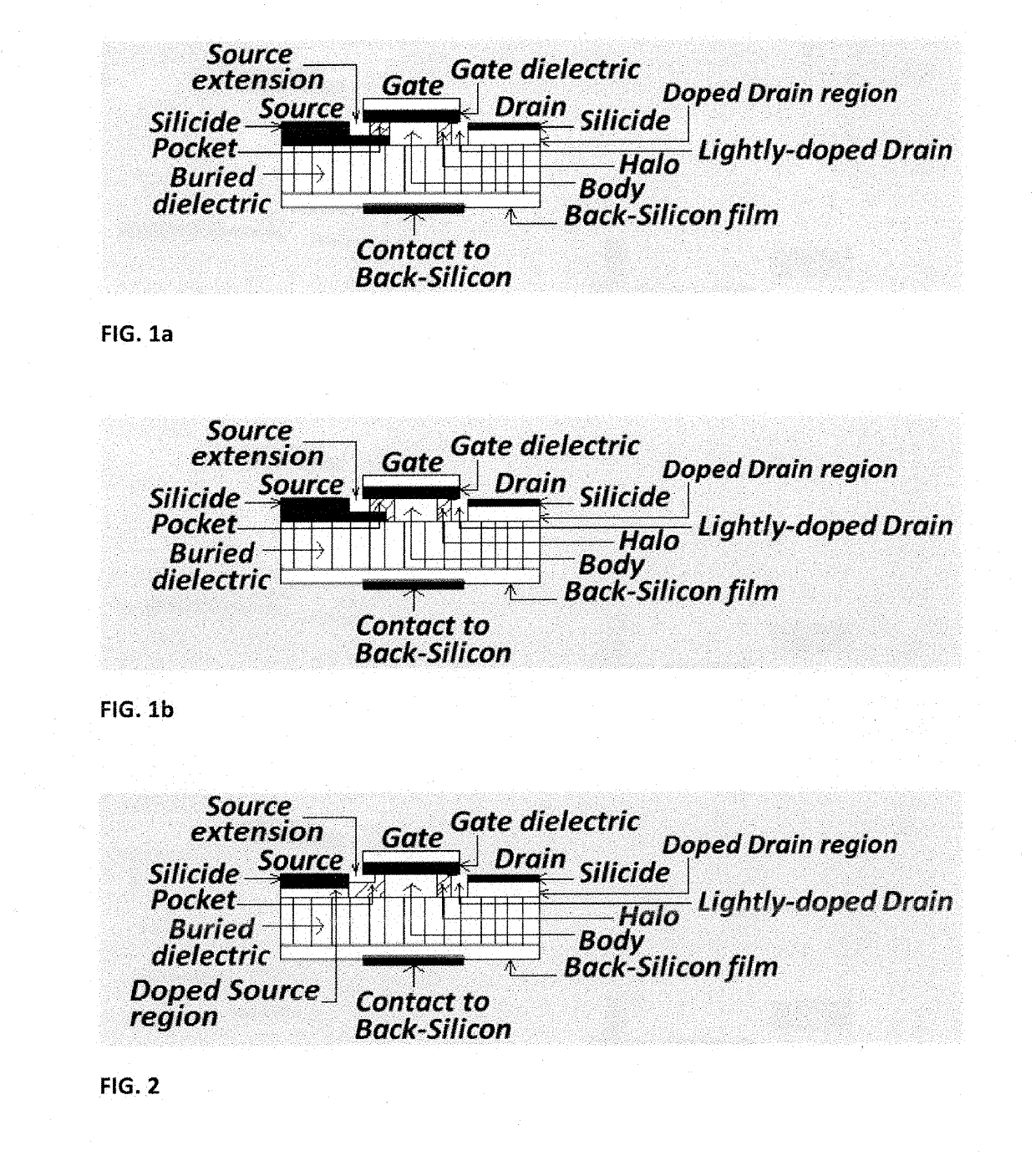

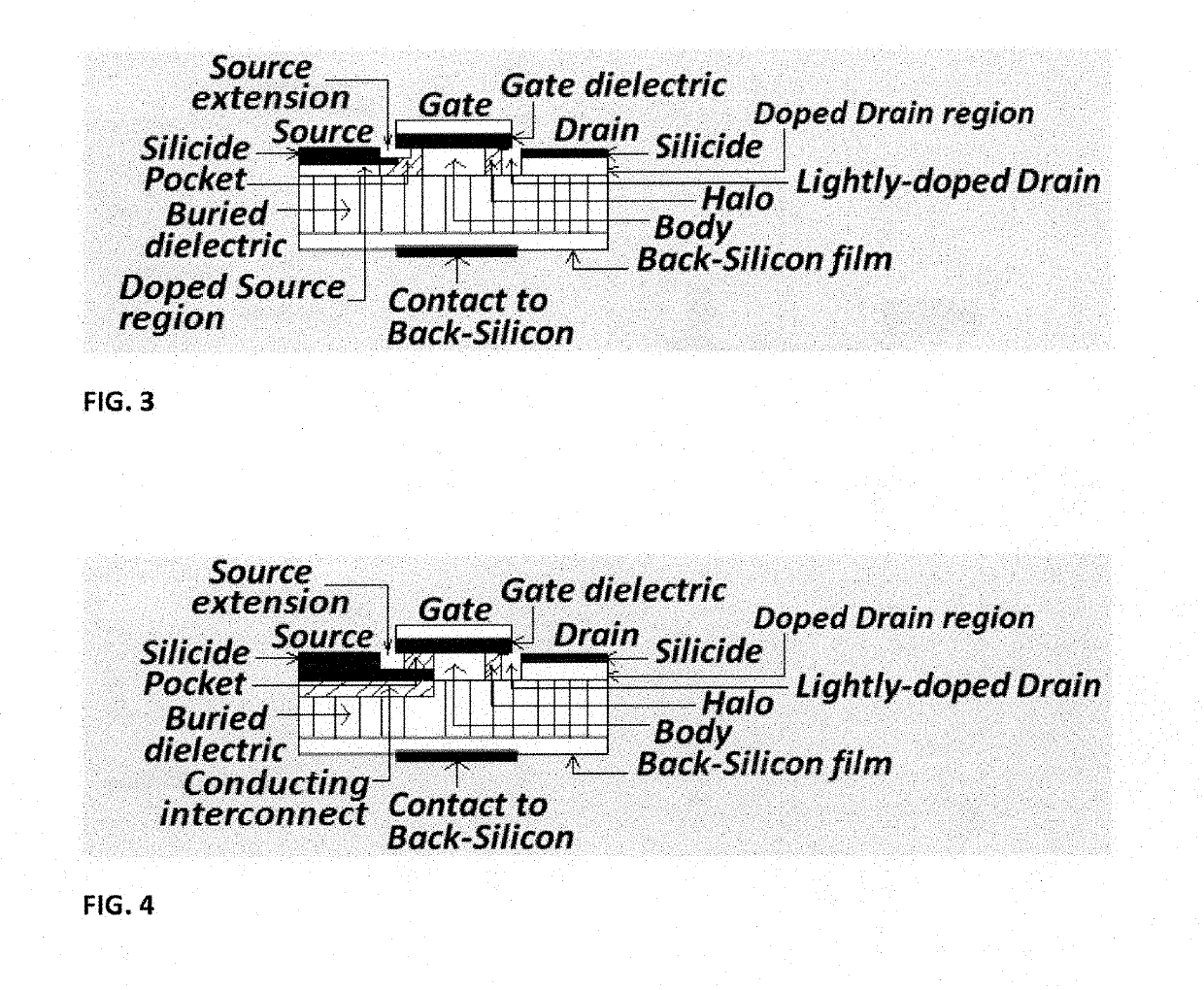

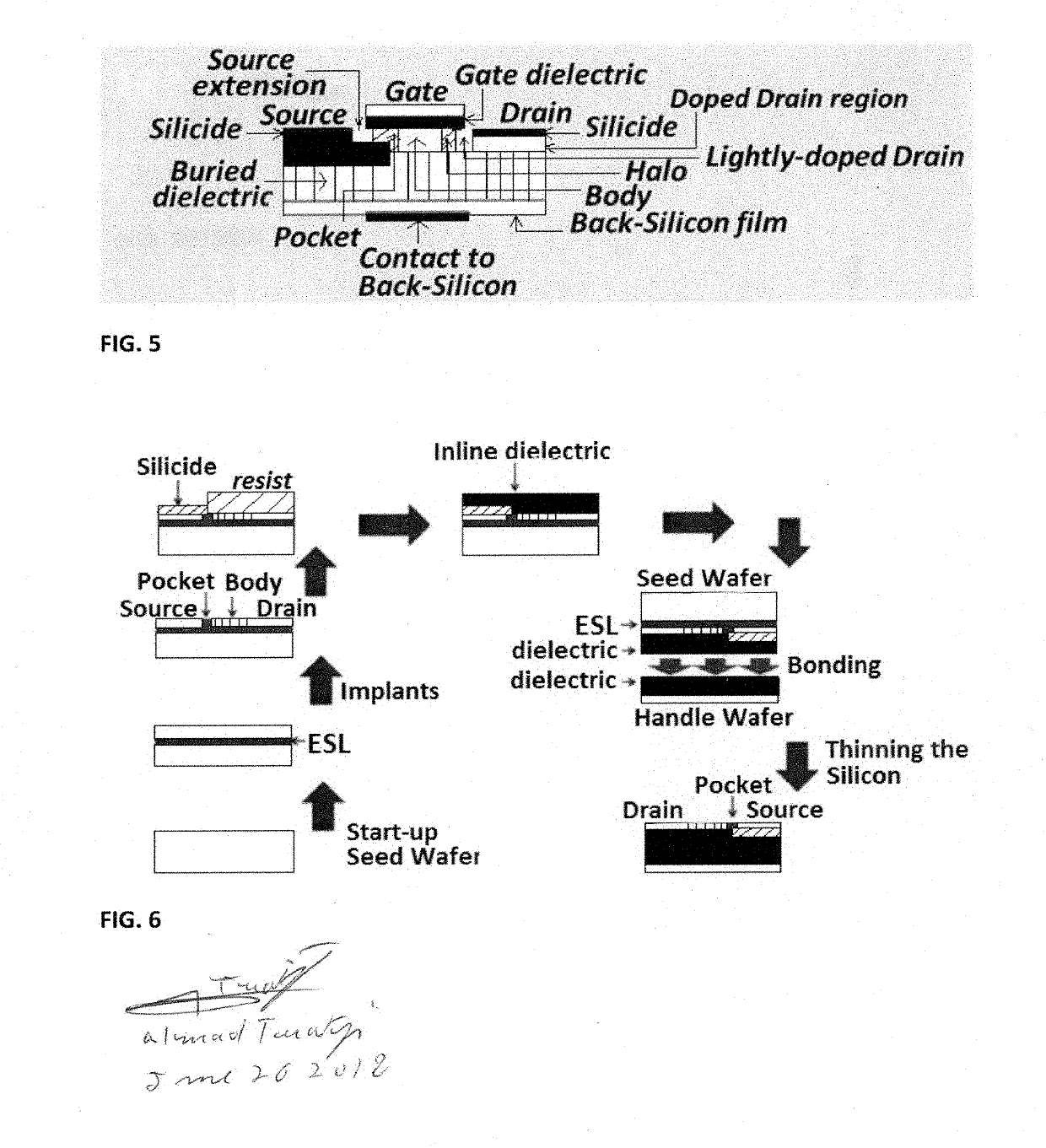

[0016]The new device architecture for SOI MOSFET traps the impact-ionization current in a band-engineered highly doped Pocket that extends in the active Silicon underneath the Gate along the entire device Width and routes this impact-ionization current to the Source-diffusion region through a highly electrically conductive path that contains a Silicide formation that solders this Pocket to the Source. This prevents the impact-ionization current from diffusing through the lateral Body-to-Source barrier and lowering it further. The Silicide in Source region can either consume the entire thickness of active Silicon or only the top portion of it. It may also extend laterally into the highly doped Pocket under the Gate. Square or trenched interconnects may also contact the Silicide to further increase the electric conductance between the device Body under the Gate and the Source. The lightly-doped Drain region helps to suppress the injection of Hot-electrons into the Gate. (Lightly doped...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More