High-threshold power semiconductor device and manufacturing method thereof

A technology of power semiconductors and manufacturing methods, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large gate capacitance, breakdown voltage that cannot meet actual requirements, small threshold voltage, etc., and achieve line width Low, reduced effective channel width, and easy-to-control thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

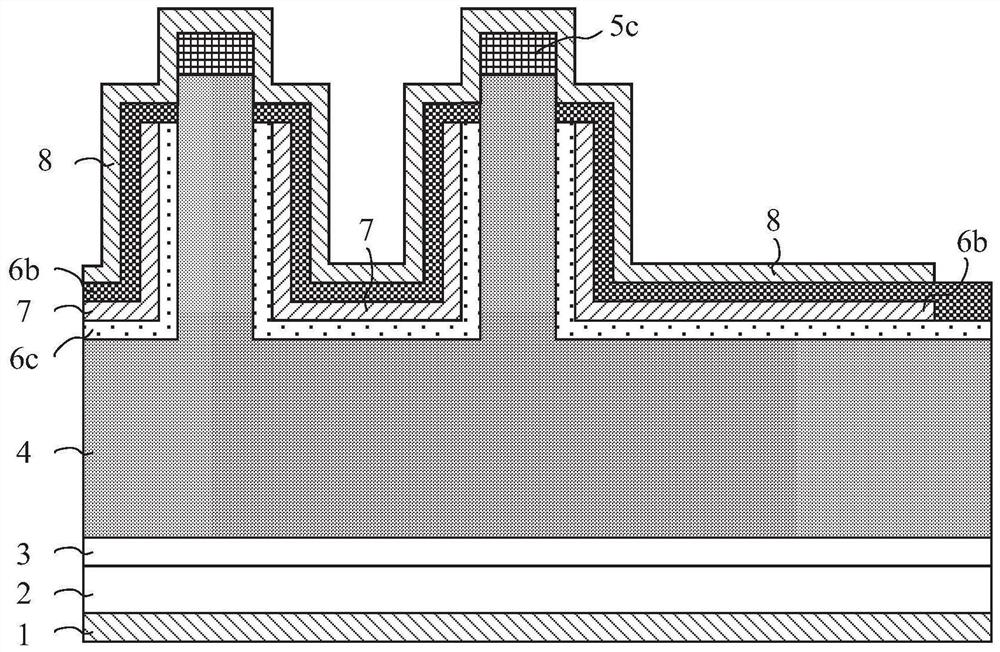

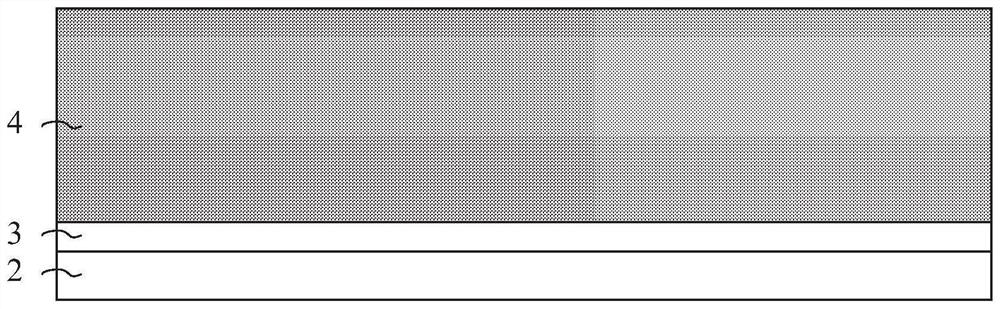

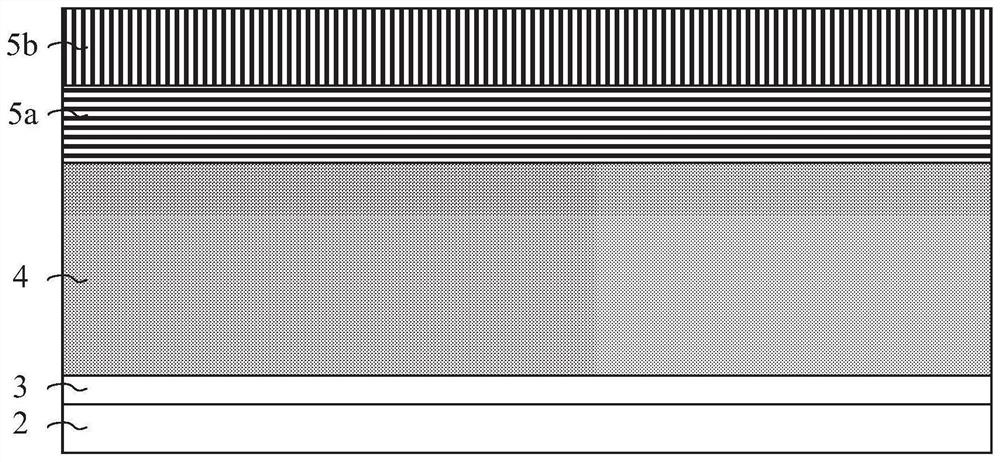

[0055] A high-threshold power semiconductor device according to the present invention includes: a drain metal electrode 1, a substrate 2, a buffer layer 3, and a drift region 4 stacked from bottom to top, and part of the drift region 4 protrudes to form a drift region protrusion A columnar p-region 5a and a columnar n-region 5b are sequentially provided on the drift region protrusion 4a, and a composite column is formed by the drift region protrusion 4a, the columnar p-region 5a and the columnar n-region 5b, and on the drift region 4 The surface, the outside of the composite cylinder and the top of the composite cylinder are provided with a channel layer 6a, the bottom surface of the channel layer 6a is provided with a passivation layer 6b, part of the drift region 4 and part of the channel layer 6a on it, passivation The layer 6b and the composite pillar are divided into the cell area 9, and another part of the drift region 4 and part of the channel layer 6a, the passivation l...

Embodiment 2

[0093] refer to Figure 14 As shown, compared with Embodiment 1, the difference of this embodiment is that the columnar p-region 5a, columnar n-region 5b, channel layer 6a, and heavily doped semiconductor layer 5c of the high-threshold power semiconductor device And the passivation layer 6b, the dielectric layer 6c, the gate metal electrode 7, and the source metal electrode 8 are distributed in straight strips without the passivation layer 6b1, and other structures are the same as in the first embodiment. The manufacturing process of inserting fingers in straight stripes is simpler, and the metal interconnection lines are reduced.

Embodiment 3

[0095] refer to Figure 15 As shown, compared with Embodiment 1, the difference of this embodiment is that the channel layer 6a of the high-threshold power semiconductor device is made of graphene material, and other structures are the same as Embodiment 1. Graphene has extremely high strength and flexibility, which improves the stability of the device; its thermal conductivity is higher than that of gallium nitride materials, so it has higher temperature stability; graphene is the best conductive material at room temperature, and its electronic The mobility is about 140 times that of electrons in silicon, lower than that of copper or silver, and the conductivity can reach 10 6 S / m, so it has lower on-resistance under the same conditions.

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical conductivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More