System and method for measuring coplanarity of integrated circuit (IC) pins through multistage reflection and raster imaging

A grating imaging and measurement system technology, applied in the direction of measuring devices, optical devices, instruments, etc., can solve the problems of slow detection speed, low detection accuracy, high equipment manufacturing cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

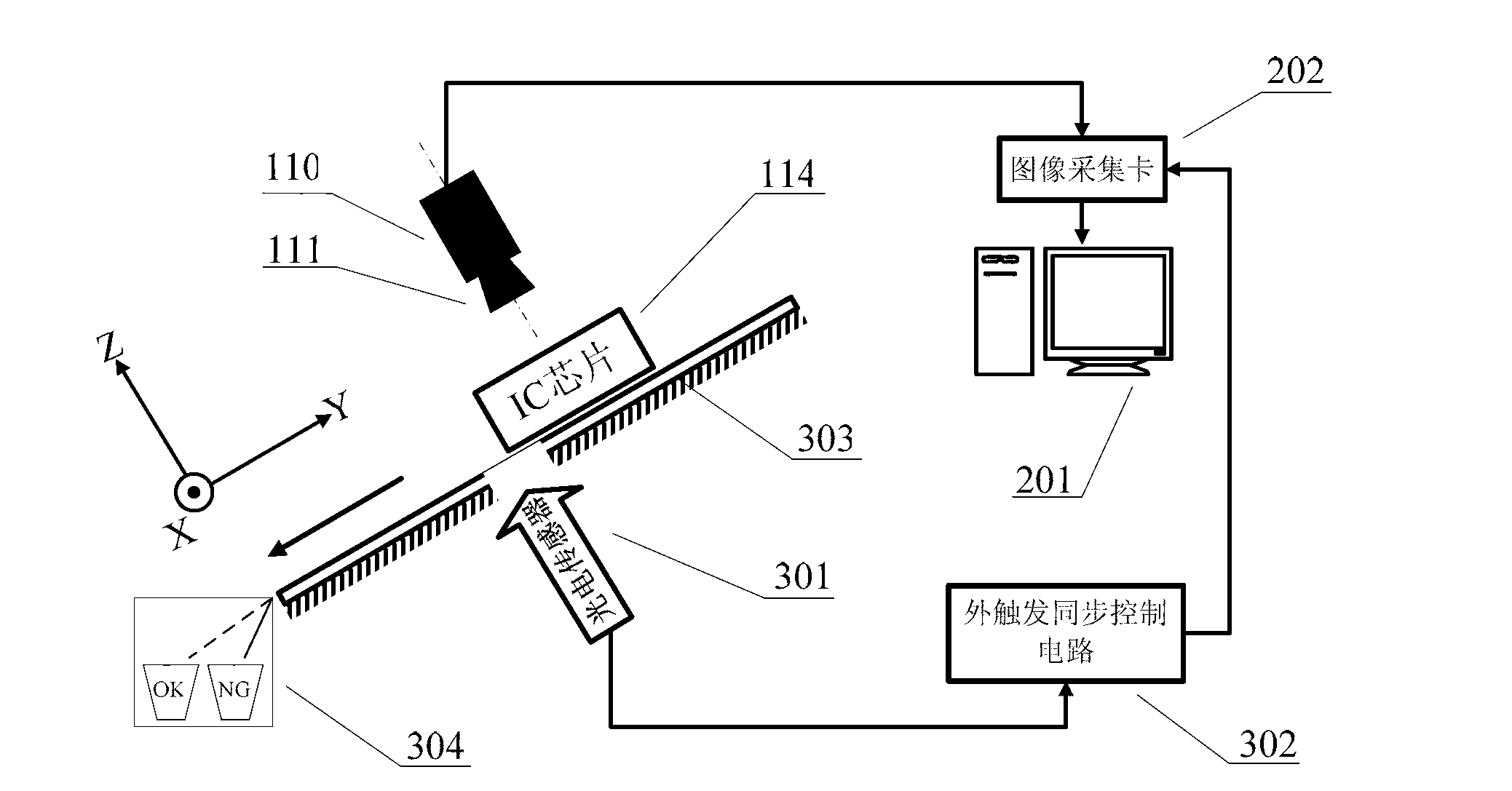

[0063] In order to better understand the present invention, the present invention will be further described below in conjunction with the accompanying drawings, but the embodiments of the present invention are not limited thereto.

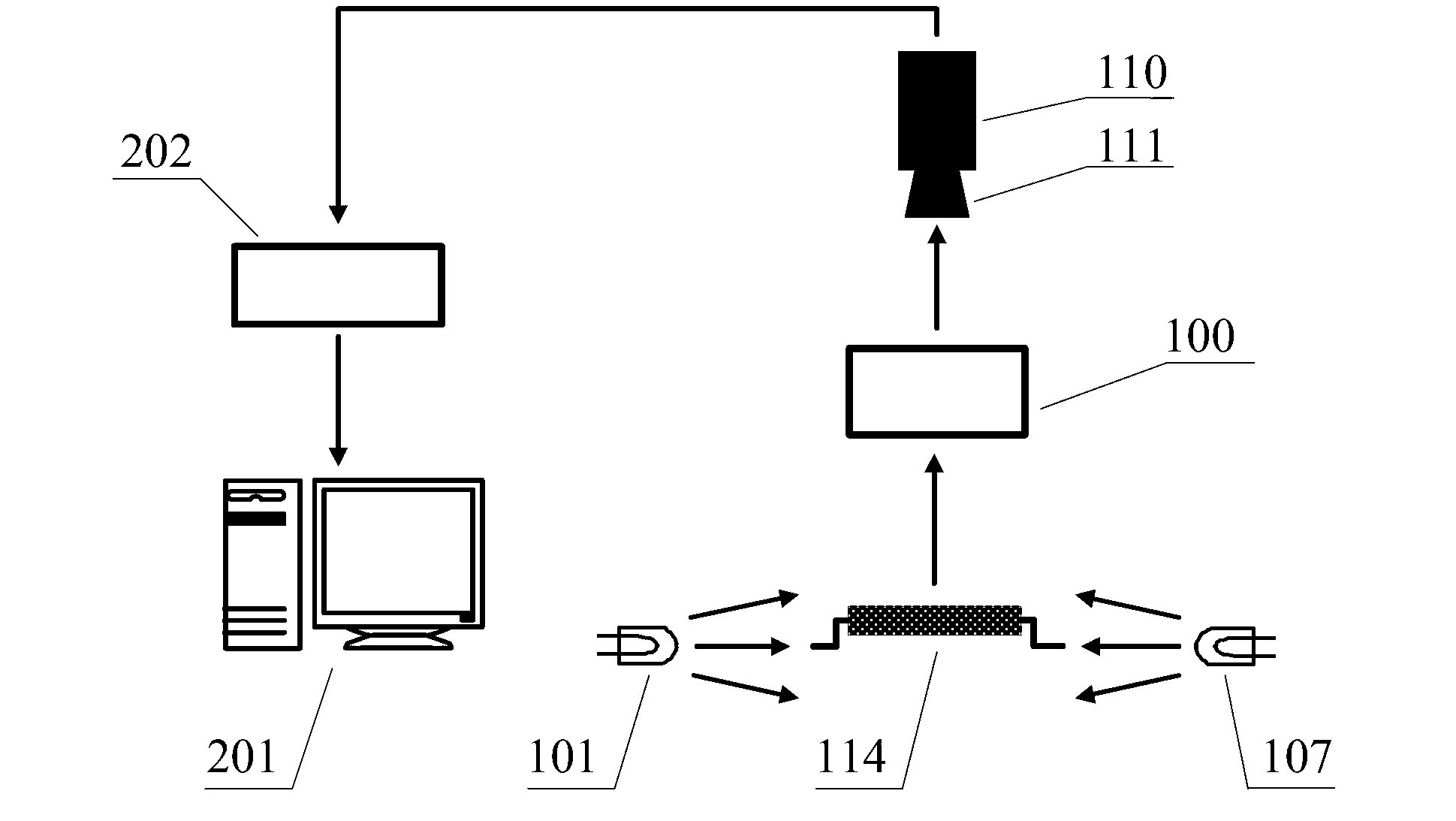

[0064] Such as figure 2 As shown, the system main frame of the present invention includes: the IC chip pin imaging optical path system 100 that multi-mirror, grating and prism constitute, IC chip self-weight oblique sliding feeding mechanism 303, image acquisition card 202, CCD camera 110 and lens 111 constitutes an imaging unit, a PC-based intelligent visual measurement system 201 , an external trigger synchronous control circuit 302 , and a superior or inferior product classification device 304 .

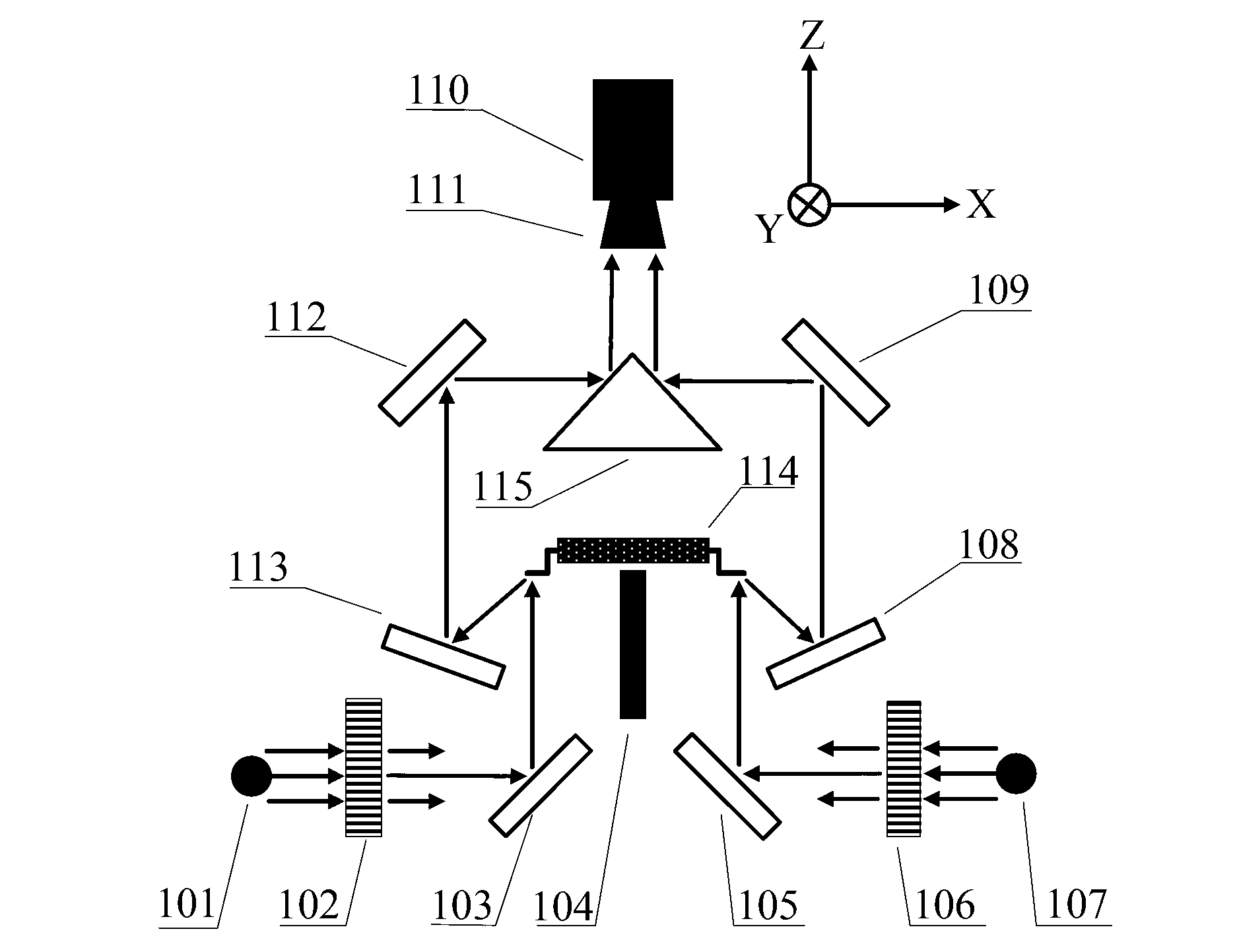

[0065] Such as figure 1As shown, it is the special optical path system proposed by the present invention: IC chip pin imaging optical path system 100, the left optical path of the IC chip pin imaging optical path system 100 includes: the left optical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More