Selection method of particle fluence rate in single particle experiment of large scale integrated circuit accelerator

A large-scale integrated circuit and particle fluence rate technology, which is applied in the field of irradiation experiments, can solve the problems of inaccurate single-particle flipping in large-scale circuits, and achieve the effect of strong operability and improved accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1A

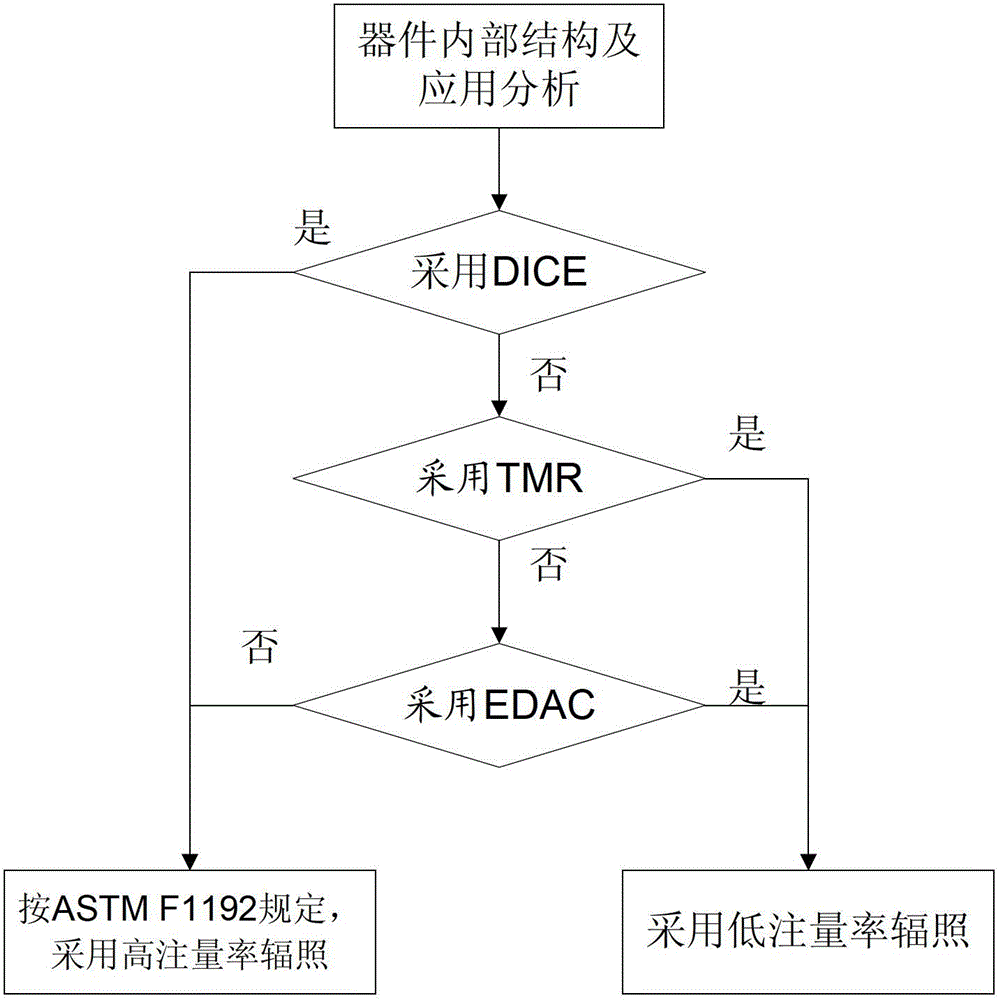

[0025] Embodiment 1 ASIC device single particle test fluence rate selection

[0026] 1) Internal design structure and application program analysis

[0027] ASIC device X has no internal TMR or EDAC design, and adopts DICE structure design, and it is judged that the single event error has nothing to do with the fluence rate.

[0028] 2) According to ASTM F1192 standard, high fluence rate is used for irradiation test

[0029] The ASTM F1192 standard stipulates the requirements for the fluence rate of the single particle test, and the high fluence rate can be used for the irradiation test according to the regulations.

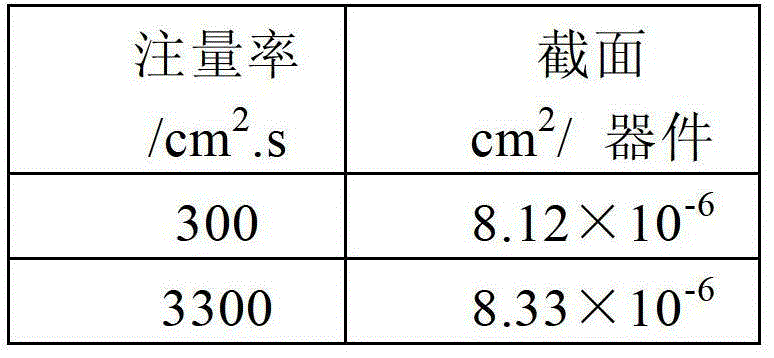

[0030] The conclusion was verified experimentally. The single particle error test was carried out under different fluence rates, and the test results are shown in Table 1. It can be seen from Table 1 that there is no significant difference in the single event error cross section of the device under different fluence rates.

[0031] Table 1 ASIC device test res...

Embodiment 2

[0033] Embodiment 2 SRAM type FPGA device single particle test fluence rate selection

[0034] 1) Internal design structure and application program analysis

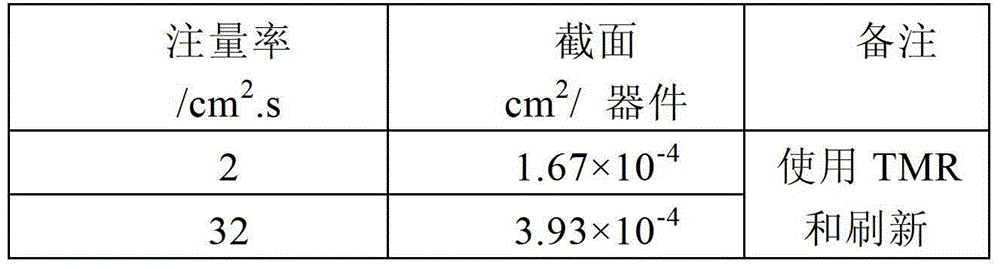

[0035] The SRAM type FPGA device Y1 does not adopt the DICE structure design internally, but adopts TMR plus refresh, and it is judged that the single event error is related to the fluence rate.

[0036] 2) Irradiation test with low fluence rate

[0037] Irradiation should be carried out at a low fluence rate. When the fluence rate is changed by more than an order of magnitude, the single particle error cross section of the device has nothing to do with the fluence rate, and the fluence rate is considered appropriate.

[0038] The conclusion was verified experimentally. The single particle error test was carried out under different fluence rates, and the test results are shown in Table 2. It can be seen from Table 2 that there are obvious differences in the single event error cross section of the device under differen...

Embodiment 3

[0041] Embodiment 3 SRAM type FPGA device single particle test fluence rate selection

[0042] 1) Internal design structure and application program analysis

[0043] The SRAM type FPGA device Y2 does not use the DICE structure design, nor does it use TMR, and the single event error is judged to have nothing to do with the fluence rate.

[0044]2) According to ASTM F1192 standard, high fluence rate is used for irradiation test

[0045] The ASTM F1192 standard stipulates the requirements for the fluence rate of the single particle test, and the high fluence rate can be used for the irradiation test according to the regulations.

[0046] The conclusion was verified experimentally. The single particle error test was carried out under different fluence rates, and the test results are shown in Table 3. It can be seen from Table 3 that there is no significant difference in the single event error cross-section of the device under irradiation at different fluence rates.

[0047] Ta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More