Semiconductor structure and method for manufacturing semiconductor structure

一种制造方法、半导体的技术,应用在半导体/固态器件制造、半导体器件、电气元件等方向,能够解决技术困难大、工艺参数要求越来越高等问题,达到掺杂浓度高、提高性能、易于控制的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

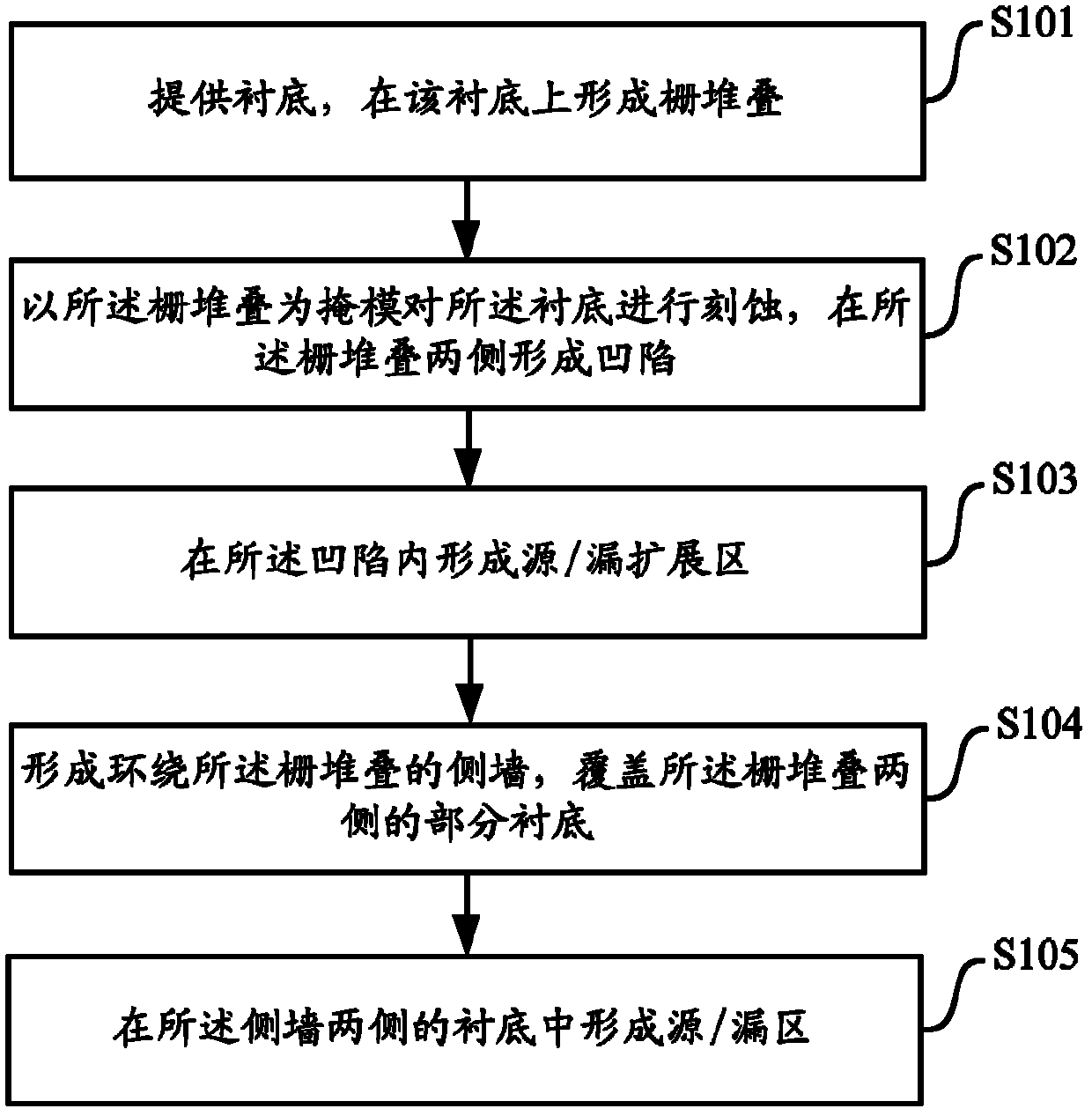

Method used

Image

Examples

Embodiment Construction

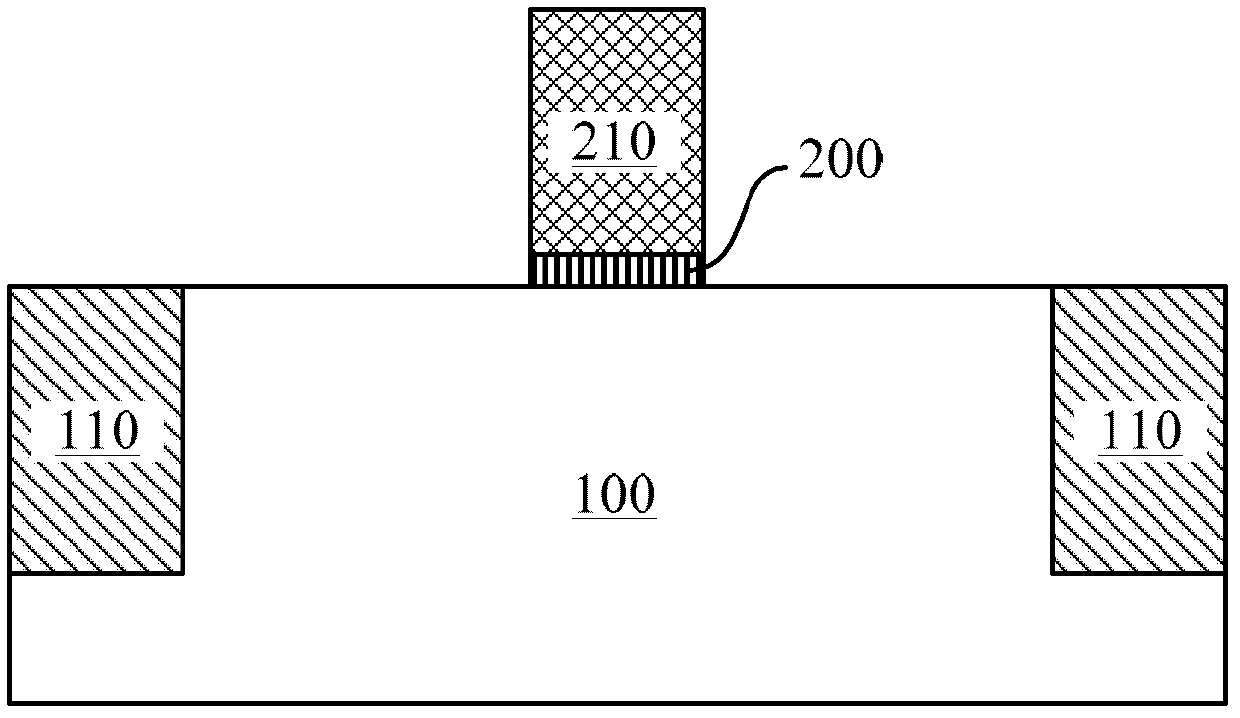

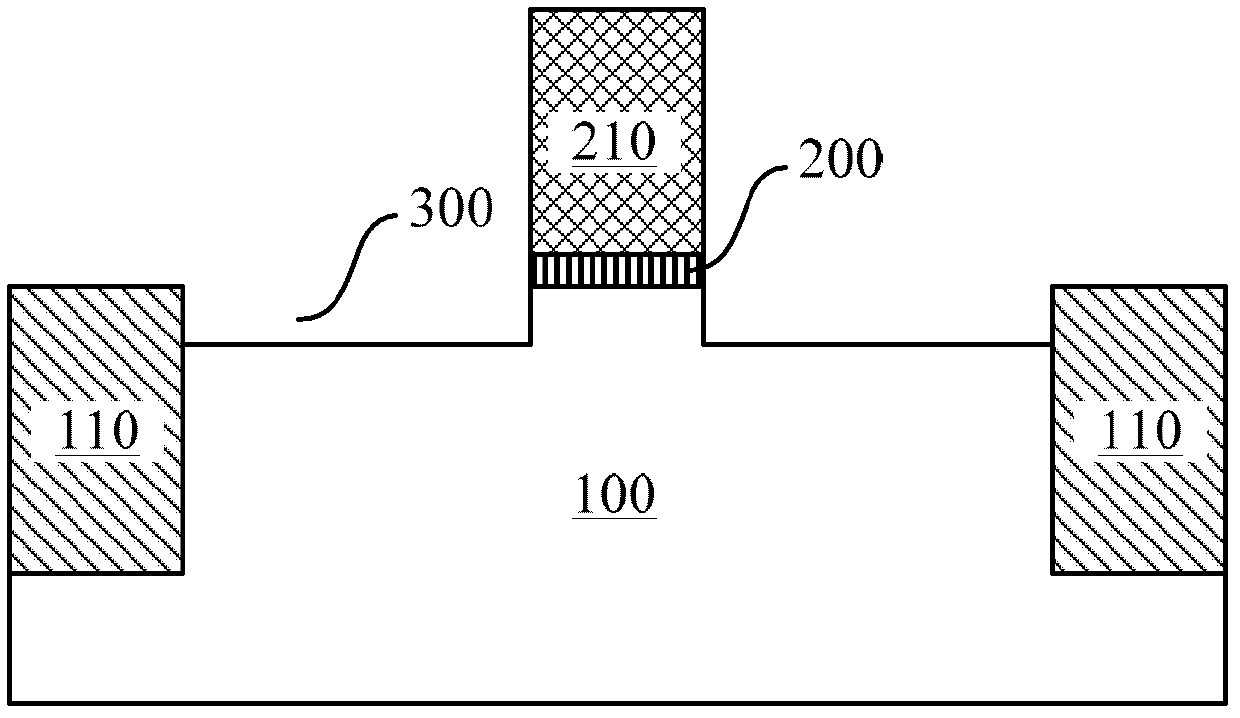

[0045] Embodiments of the present invention are described in detail below.

[0046] Examples of the described embodiments are shown in the drawings, wherein like or similar reference numerals designate like or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention. The following disclosure provides many different embodiments or examples for implementing different structures of the present invention. To simplify the disclosure of the present invention, components and arrangements of specific examples are described below. Of course, they are only examples and are not intended to limit the invention. Furthermore, the present invention may repeat reference numerals and / or letters in different instances. This repetition is for the purpose of simplicity and clarity and does not in i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More