Method and system for reducing soft error rate of processor

A soft error rate, processor technology, applied in the direction of electrical digital data processing, error detection/correction, instruments, etc., can solve problems such as incorrect instruction execution, achieve the effect of improving performance power consumption ratio and reducing soft error rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical solutions of the present invention will be described in detail below in conjunction with the embodiments and the accompanying drawings.

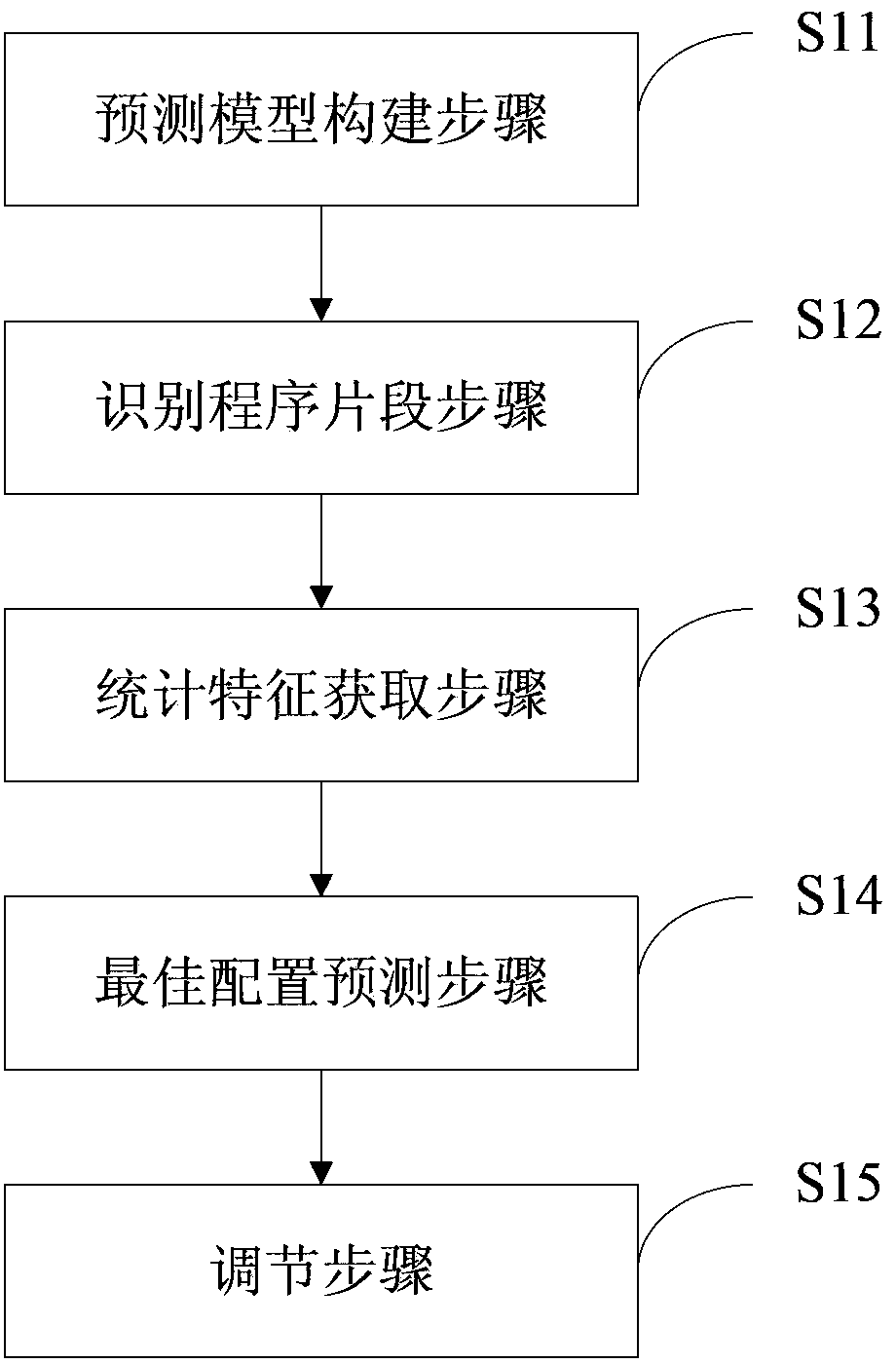

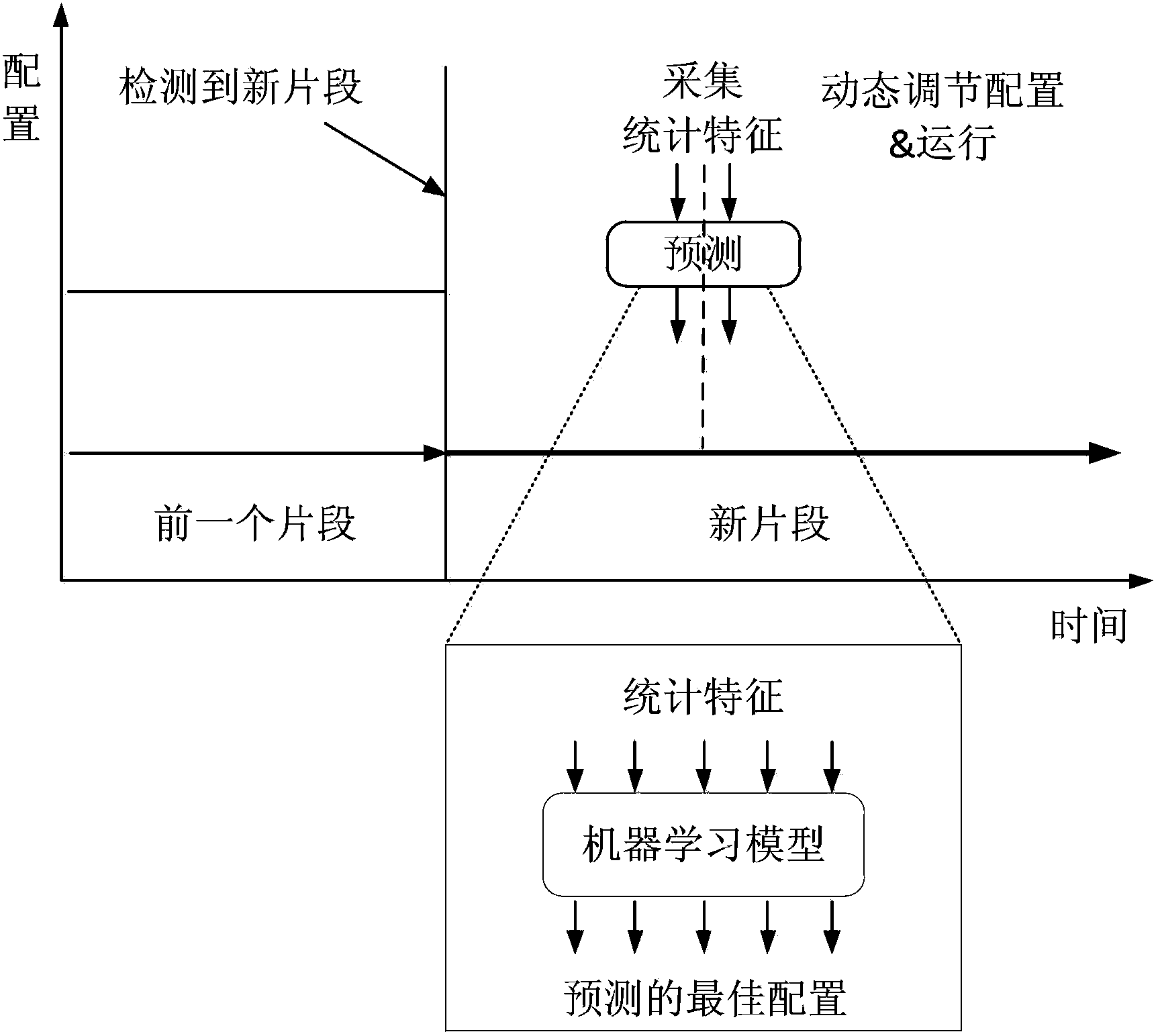

[0036] figure 1 It is a flow chart of the method for reducing the soft error rate of the processor according to the present invention, including: the step of building a prediction model (S11), the step of identifying program fragments (S12), the step of obtaining statistical features (S13), and the step of predicting the best configuration (S14) and an adjustment step (S15).

[0037] The predictive model building step (S11), constructing a predictive model using machine learning methods to predict the optimal configuration of the processor that can reduce the soft error rate of the processor with low overhead.

[0038] Between the statistical feature space X and the processor optimal configuration space Y, a predictive model f:X→Y is constructed using machine learning methods. To build a predictive model, use x(x 1 ,x...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More