Preparation method of semiconductor substrate with cavity

A semiconductor and substrate technology, applied in the field of silicon-on-insulator substrate preparation, can solve problems such as inability to ensure uniformity, and achieve good top silicon uniformity and defect control effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The specific implementation of the method for preparing a semiconductor substrate with a cavity provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

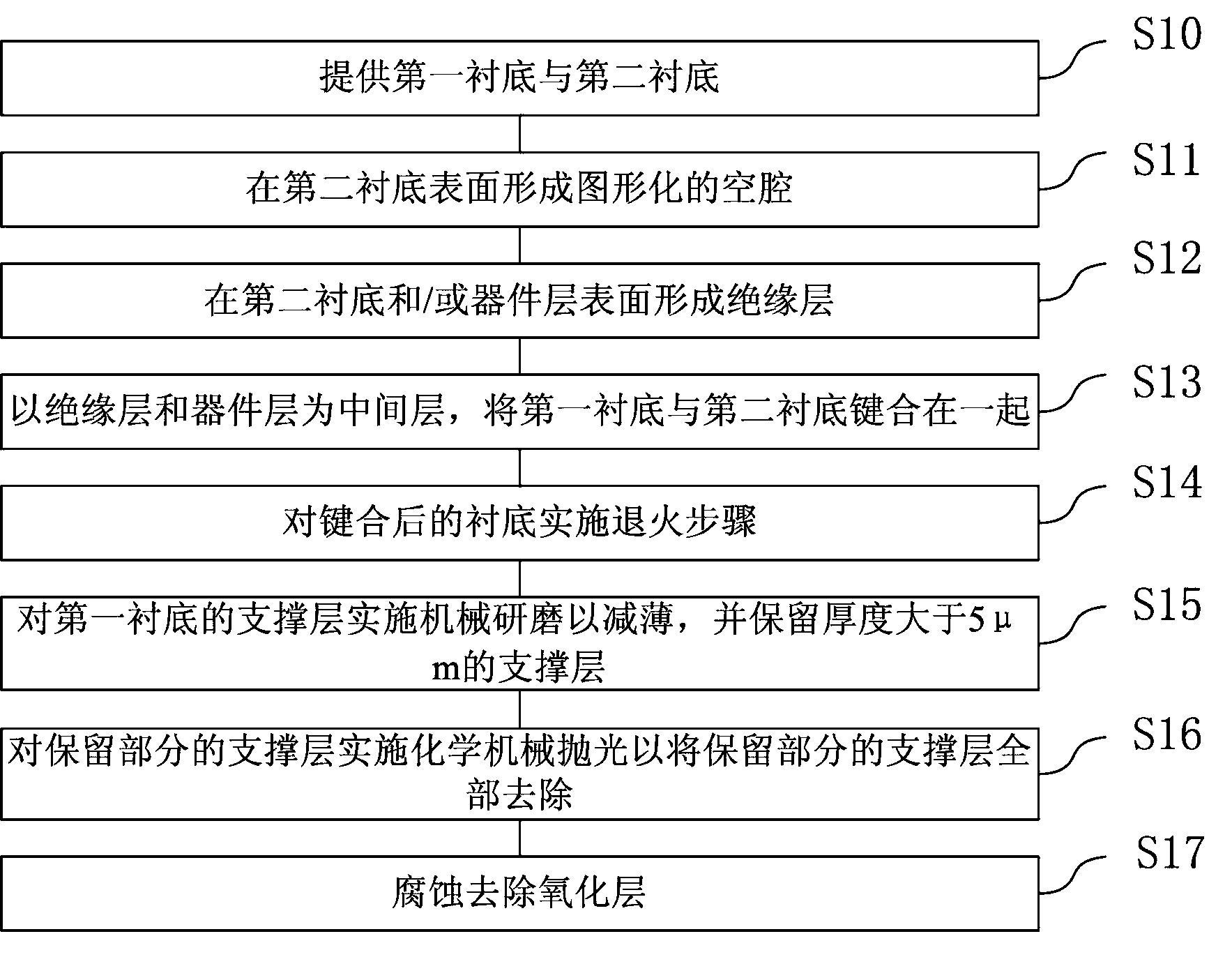

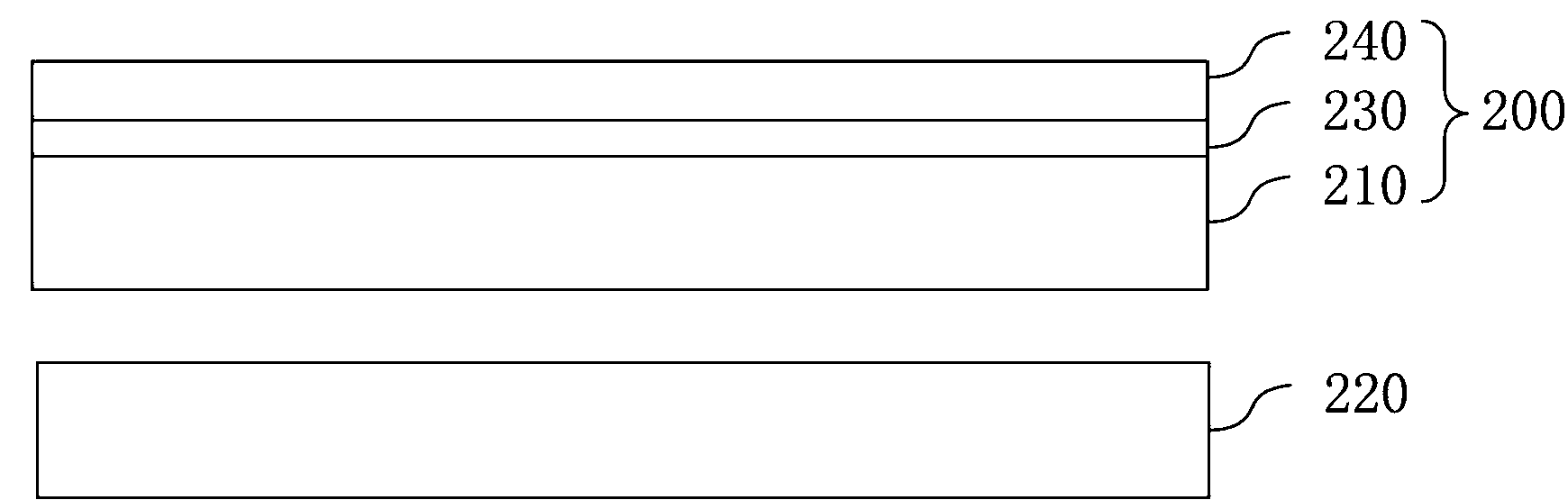

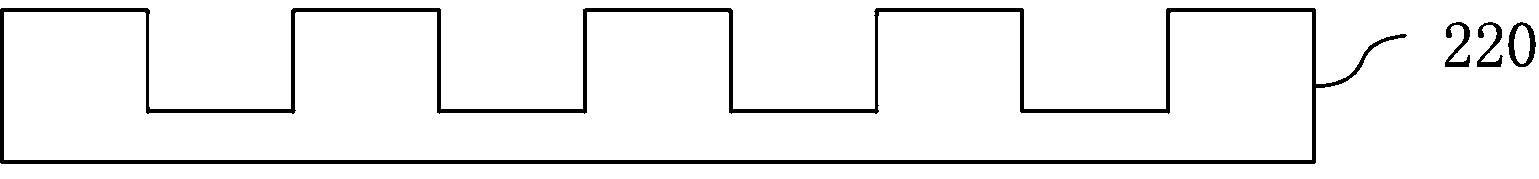

[0015] attached figure 1 Shown is a schematic diagram of the implementation of the steps of the method described in the specific embodiment of the present invention, including, step S10, providing a first substrate and a second substrate, the first substrate includes a support layer, an oxide layer on the surface of the support layer, and The device layer on the surface of the oxide layer; Step S11, forming a patterned cavity on the surface of the second substrate; Step S12, forming an insulating layer on the surface of the second substrate and / or the device layer; Step S13, forming the insulating layer and the device layer As an intermediate layer, the first substrate and the second substrate are bonded together; step S14, an annealing step is performed on the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More