Storage unit, forming method of storage unit and driving method of storage unit

A memory cell and control gate technology, applied in the semiconductor field, can solve the problems of occupying a large area and low memory integration, and achieve the effects of improving the integration, reducing the number of use, and reducing the chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] As mentioned in the background art, each group of gates of the existing EEPROM cells corresponds to at least one selection control transistor, so that the selection control transistor occupies a larger area of the memory chip.

[0021] In order to increase the integration level of the memory chip, it is necessary to reduce the number of select control transistors without affecting various read, write and erase operations on the memory cells.

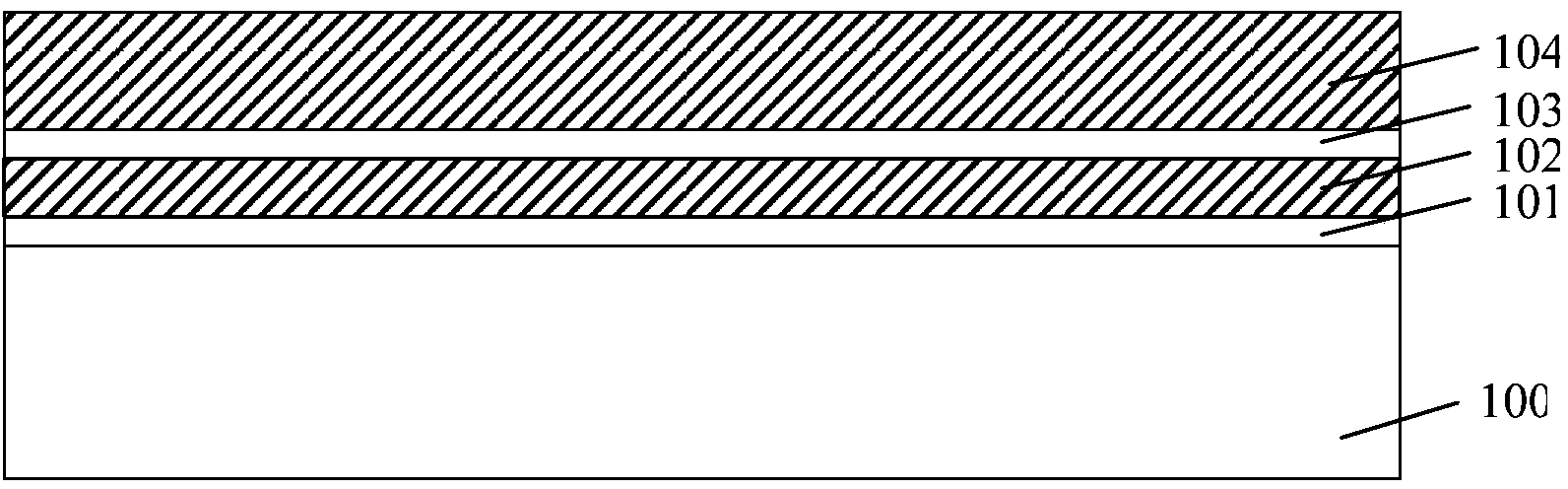

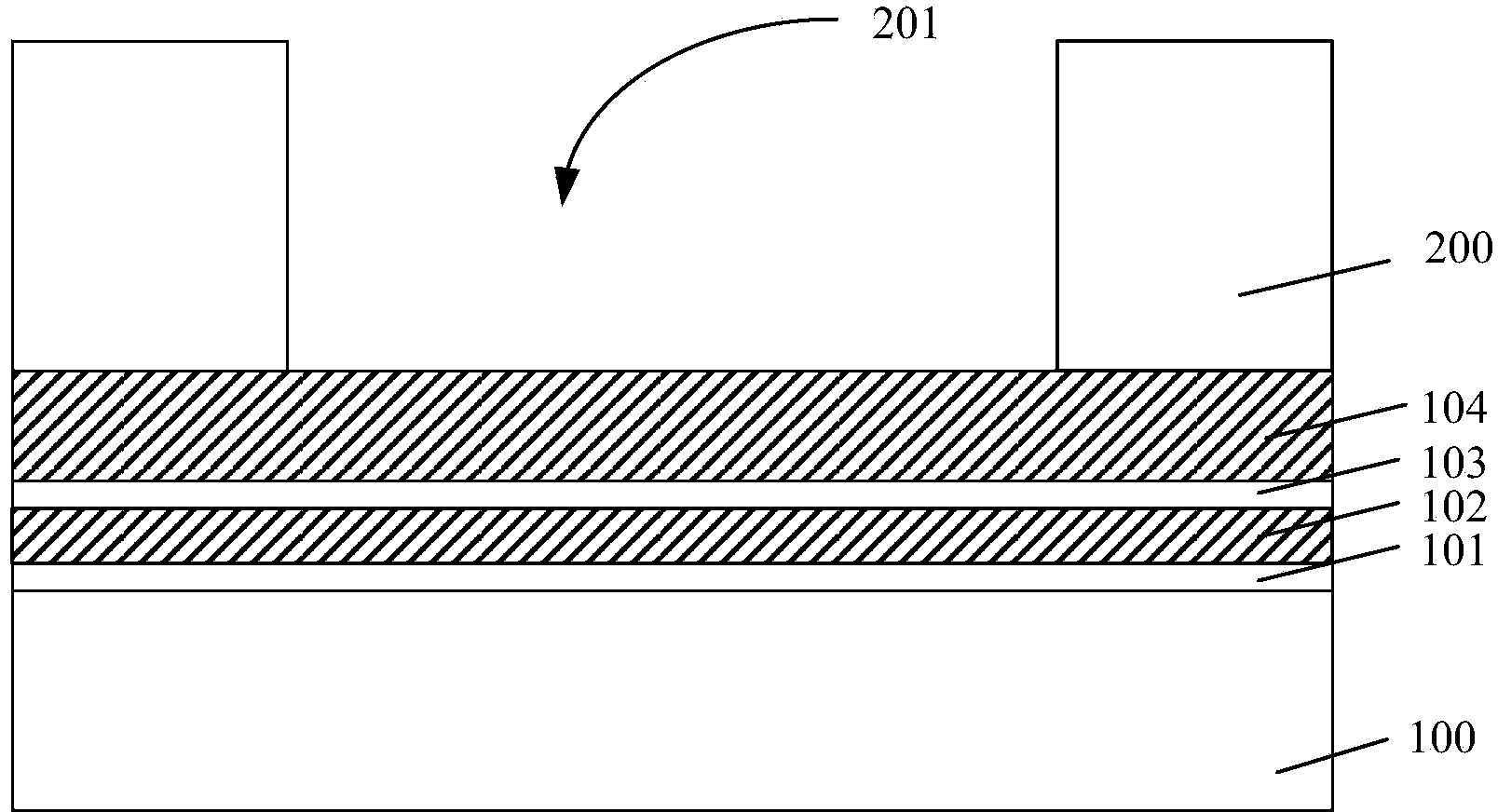

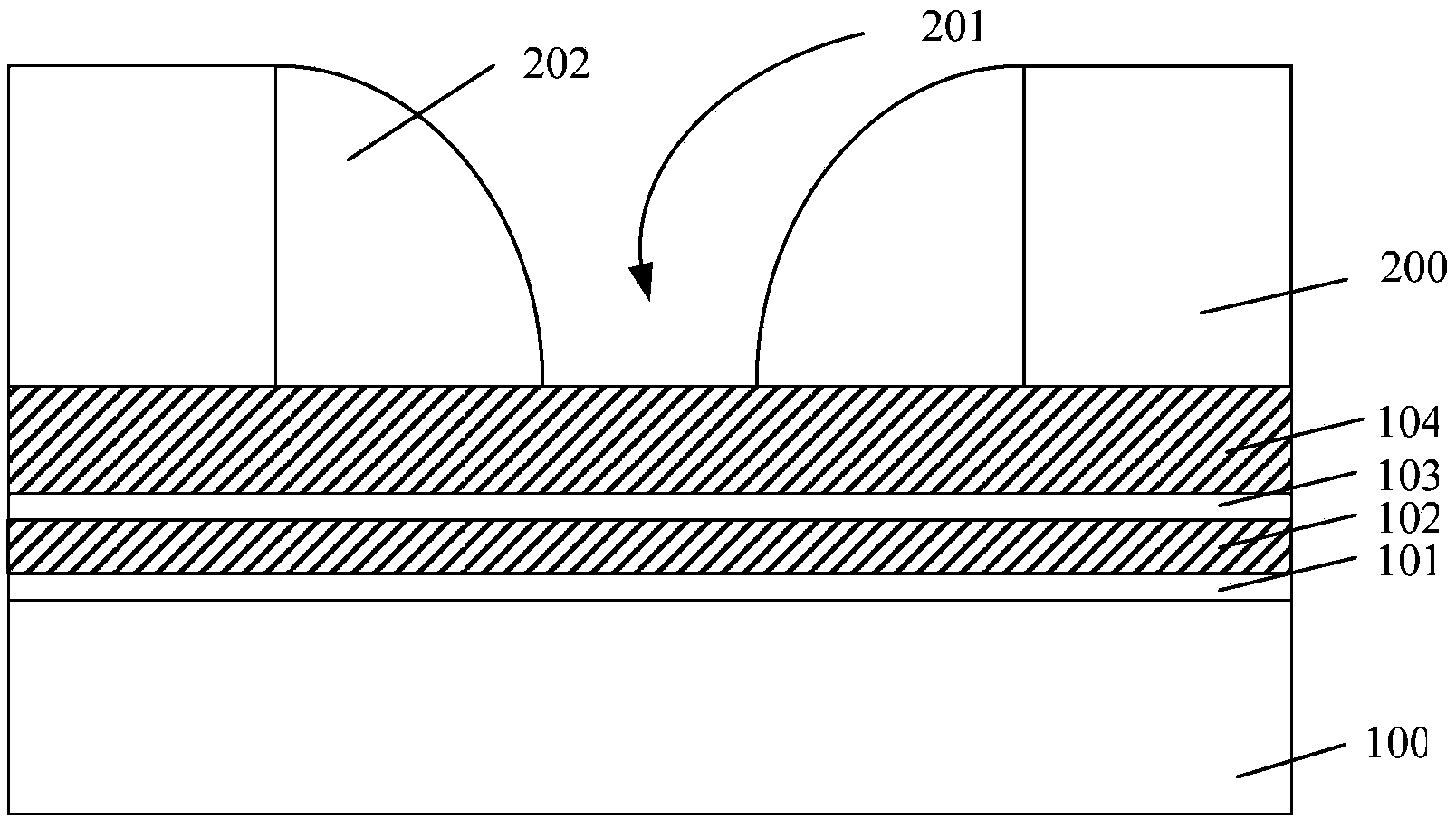

[0022] In order to solve the above problems, the source and drain of the memory cell formed in the embodiment of the present invention are located under the floating gate dielectric layer, which improves the coupling rate between the floating gate and the source or drain, so that the drain or The source voltage controls the opening or closing of the channel under the floating gate, so that the control gates on both sides of the word line are connected to the same selection control transistor to still realize the reading, writing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More