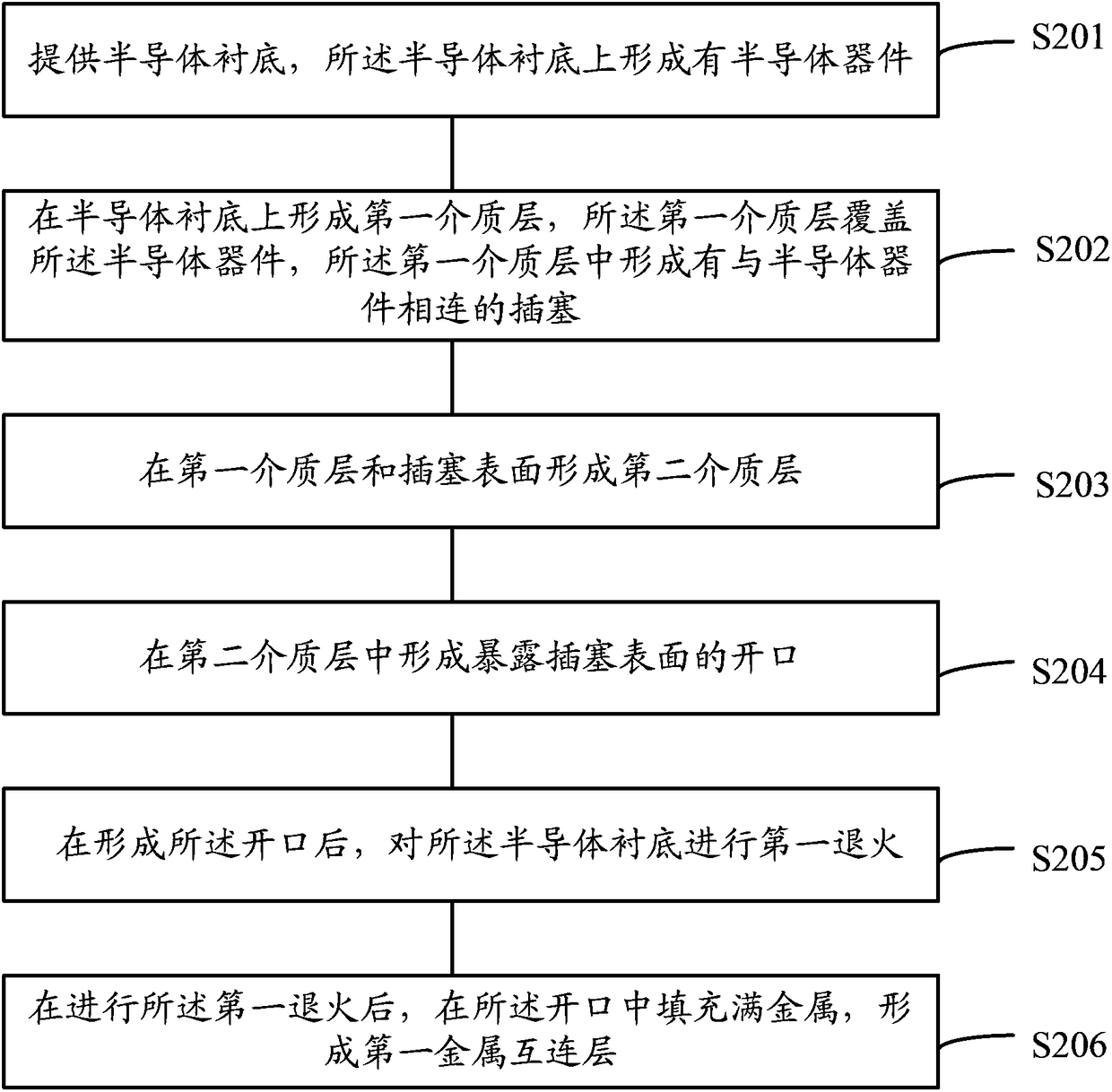

Formation method of semiconductor structure

A semiconductor and dielectric layer technology, applied in the field of semiconductor structure formation, can solve problems such as wafer deformation and semiconductor device failure, and achieve the effects of small superposition effect, reduced internal stress, and good release effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

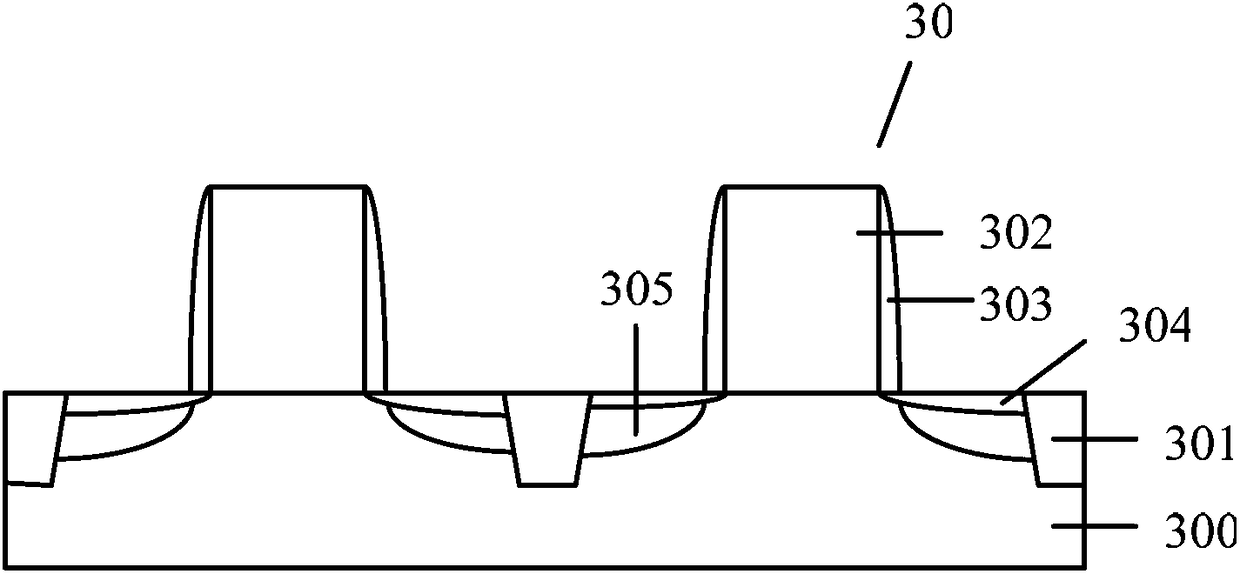

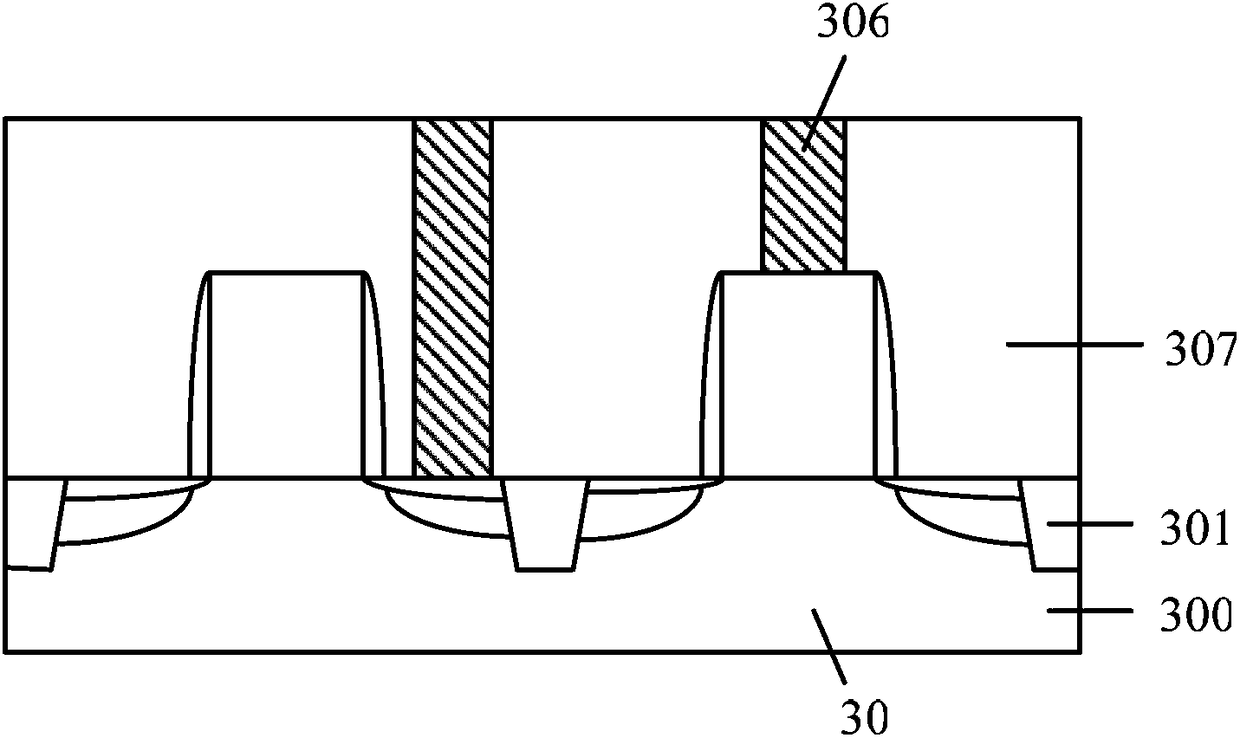

Embodiment Construction

[0028] The inventor found in the process of back-end metal interconnection process that the back pressure (Backside Pressure BSK) of the physical vapor deposition equipment often shifted when processing the wafer, especially in the top-level metal interconnection process, it would occur The phenomenon that the back pressure suddenly decreases. The size of the back pressure reflects the control of the position of the backside of the wafer by the electric suction chuck in the physical vapor deposition equipment (normally 7~9Torr). The smaller the value of the back pressure, it means that the electric suction The worse the position control of the suction chuck for the wafer is, the wafer will tilt in the cavity after it is less than a certain set value (usually 5Torr). When the back pressure value deviates from the allowable value, it needs to be corrected Wafers are reworked, which is likely to lead to chipping. The inventors further researched and found that the deviation of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More