Clock test circuit

A technology for testing circuits and clock circuits, which is applied in the direction of measuring electricity, measuring electrical variables, electronic circuit testing, etc. It can solve the problems of inaccurate test results and difficulty for testers to distinguish the decimal point of 0.3 seconds.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

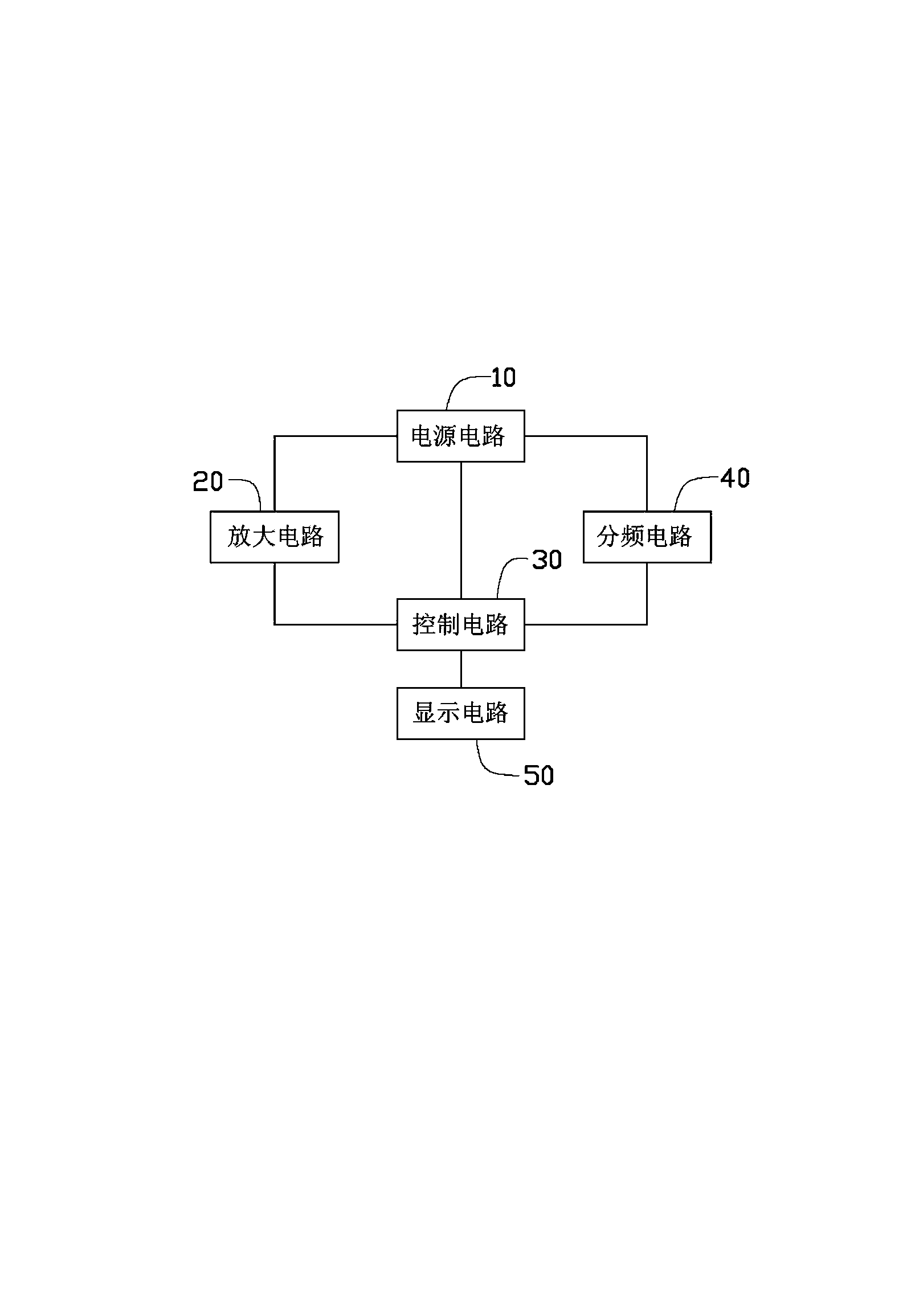

[0014] Please refer to figure 1 , the clock test circuit of the present invention is used for testing whether a clock circuit is qualified, and the preferred embodiment of this clock test circuit comprises an amplifying circuit 20, a frequency dividing circuit 40, a control circuit 30, a display circuit 50 and a The circuit 20 , the frequency dividing circuit 40 and the control circuit 30 provide the power supply circuit 10 with an operating voltage.

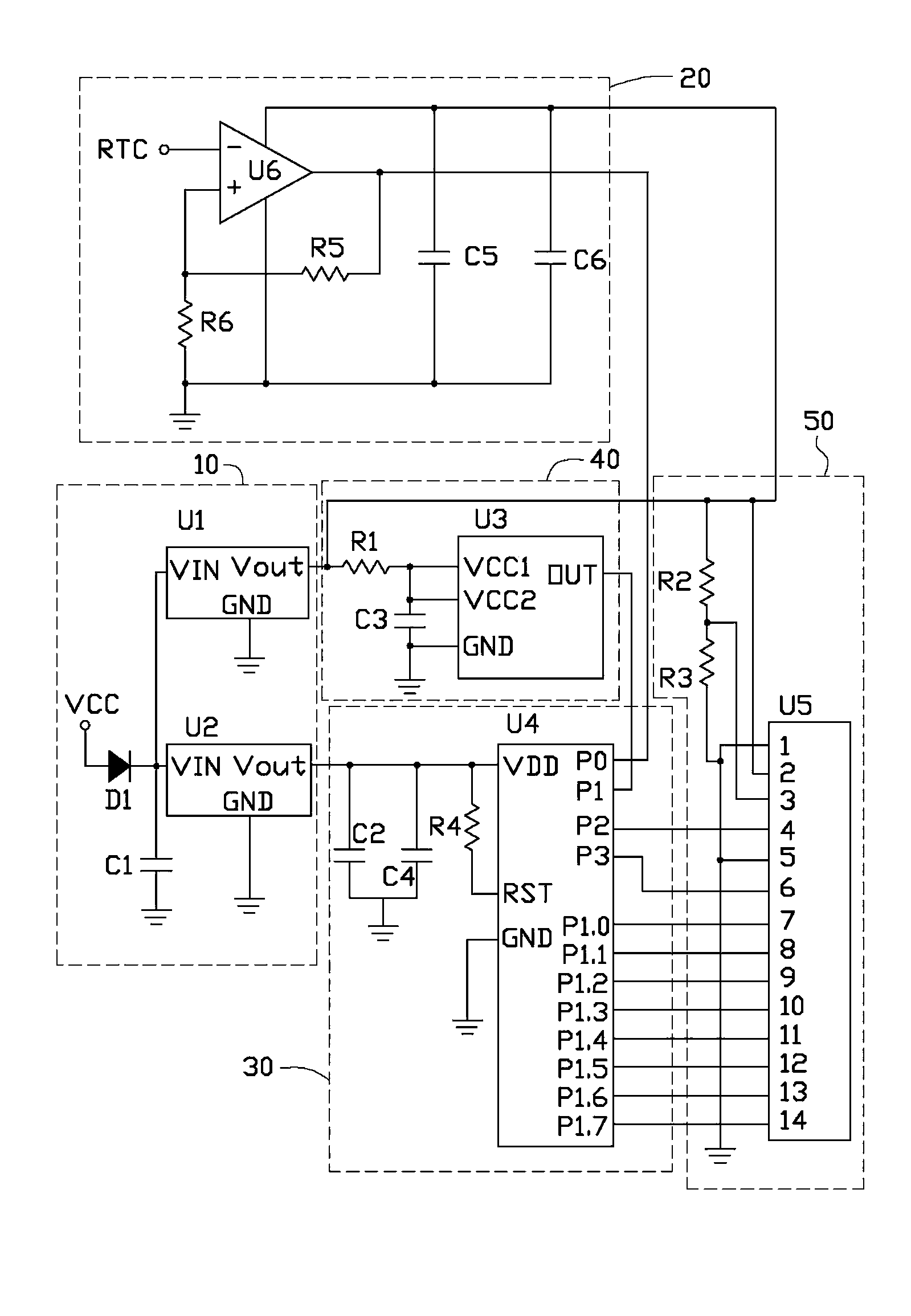

[0015] Please refer to figure 2 , the power circuit 10 includes a diode D1, a capacitor C1 and two power chips U1 and U2. The ground pins GND of the power chips U1 and U2 are both grounded. The input pin VIN of the power chip U1 is connected to the cathode of the diode D1 and grounded through the capacitor C1. The anode of the diode D1 is connected to the power supply VCC. The power chip U1 is used to convert the voltage output by the power supply VCC, and output the converted voltage through the output pin Vout of the powe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More