Patents

Literature

43 results about "Clock Test" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

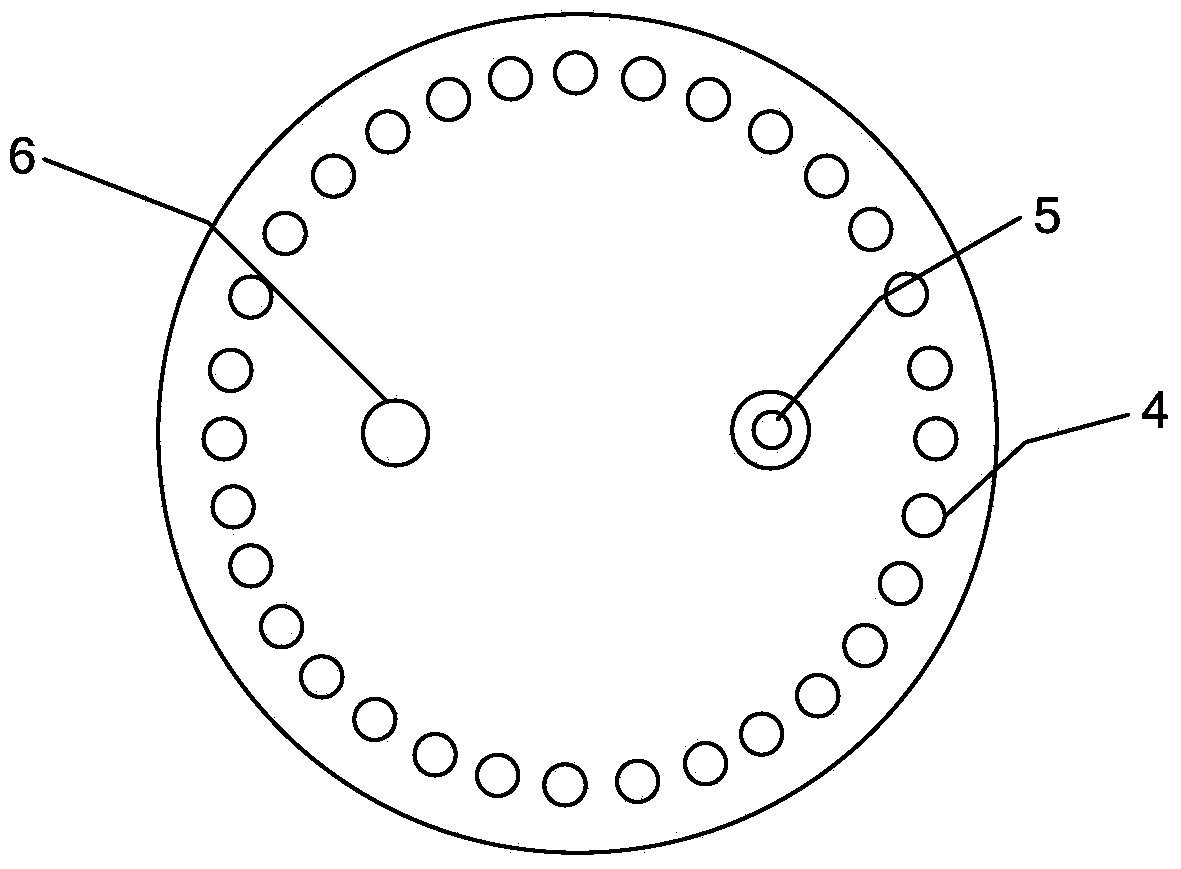

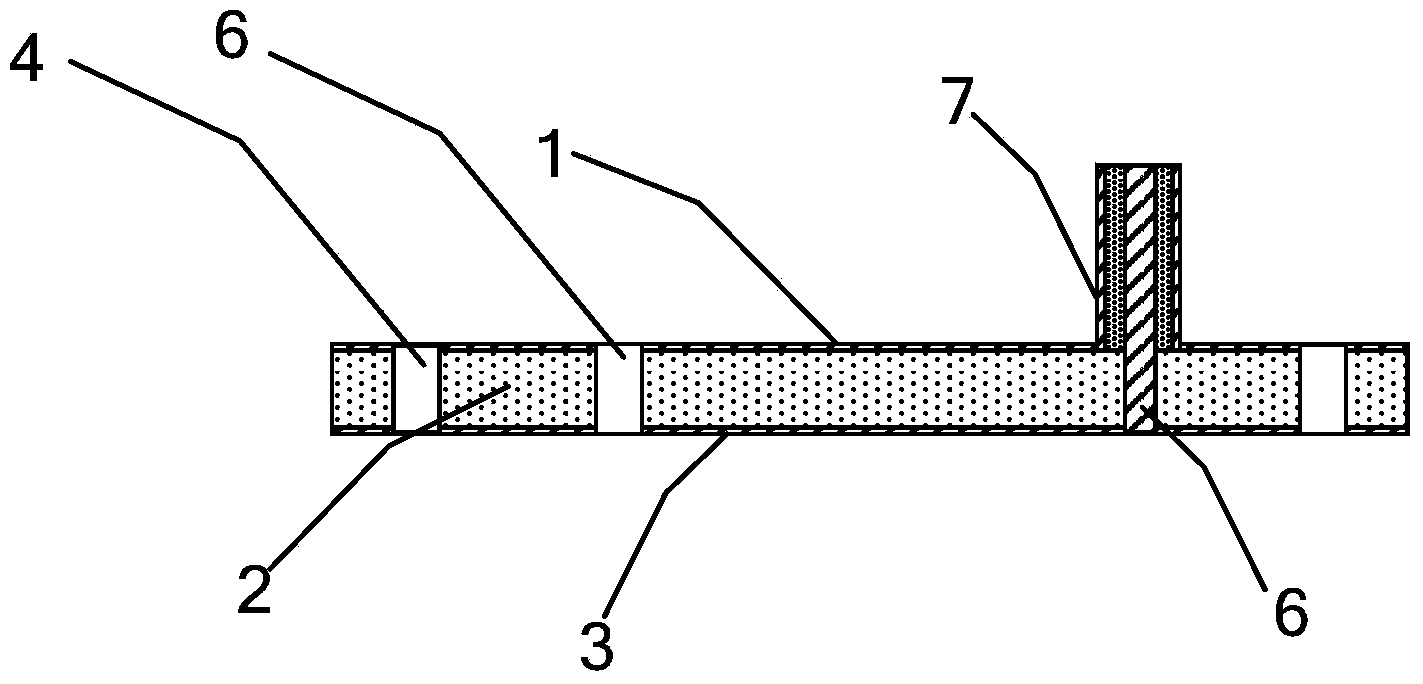

Method for measuring material complex permittivity based on substrate integrated waveguide round resonant cavities

ActiveCN103901278AEasy to processLow costResistance/reactance/impedenceResonant cavitySimultaneous equations

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

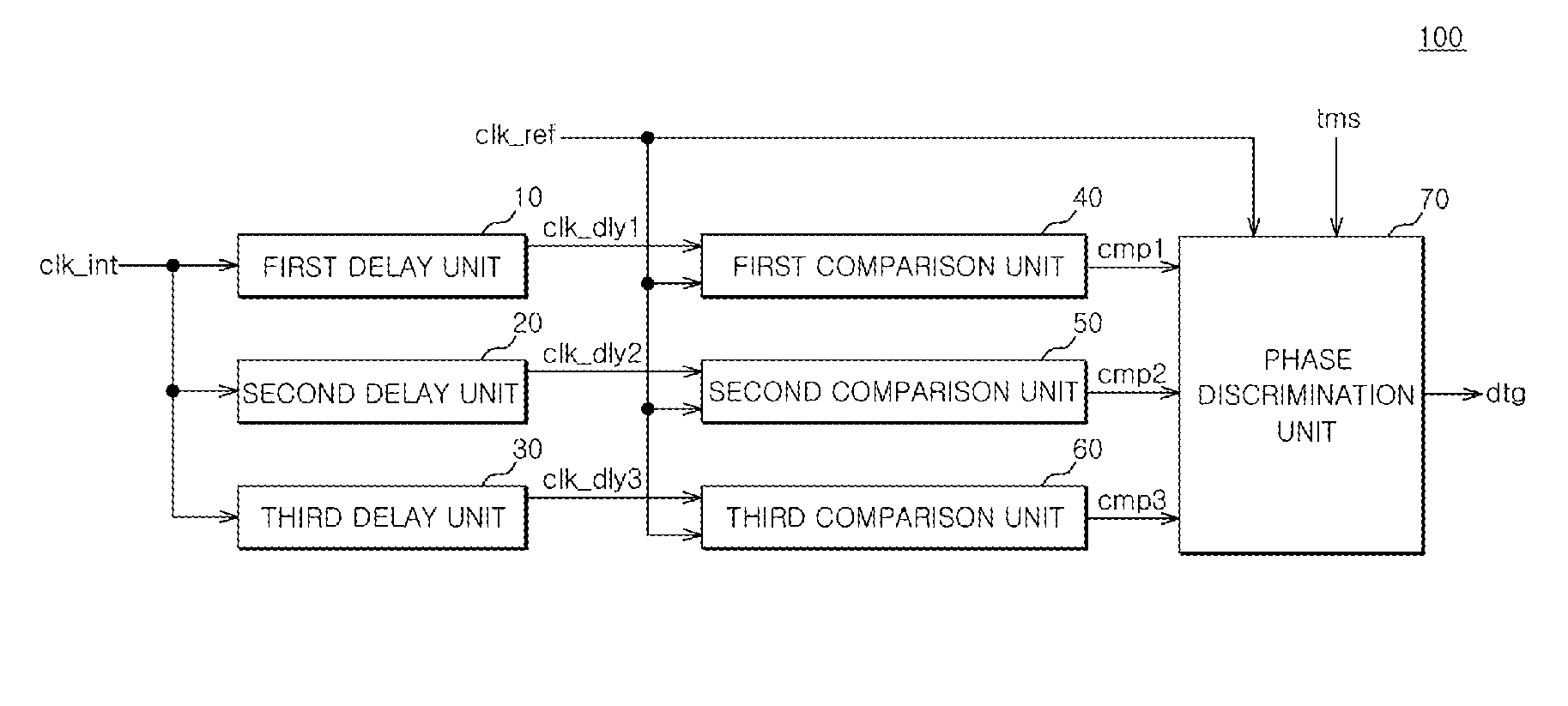

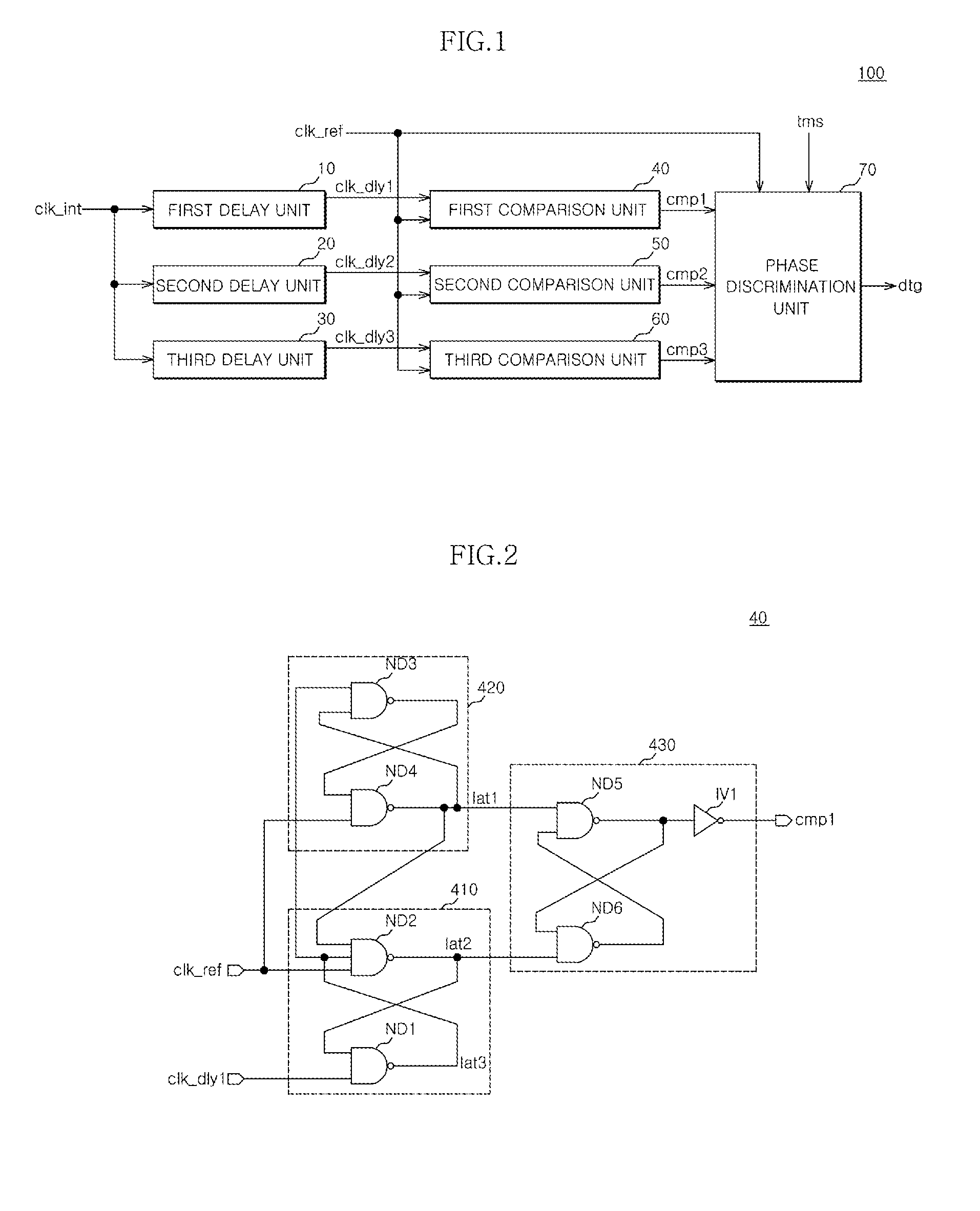

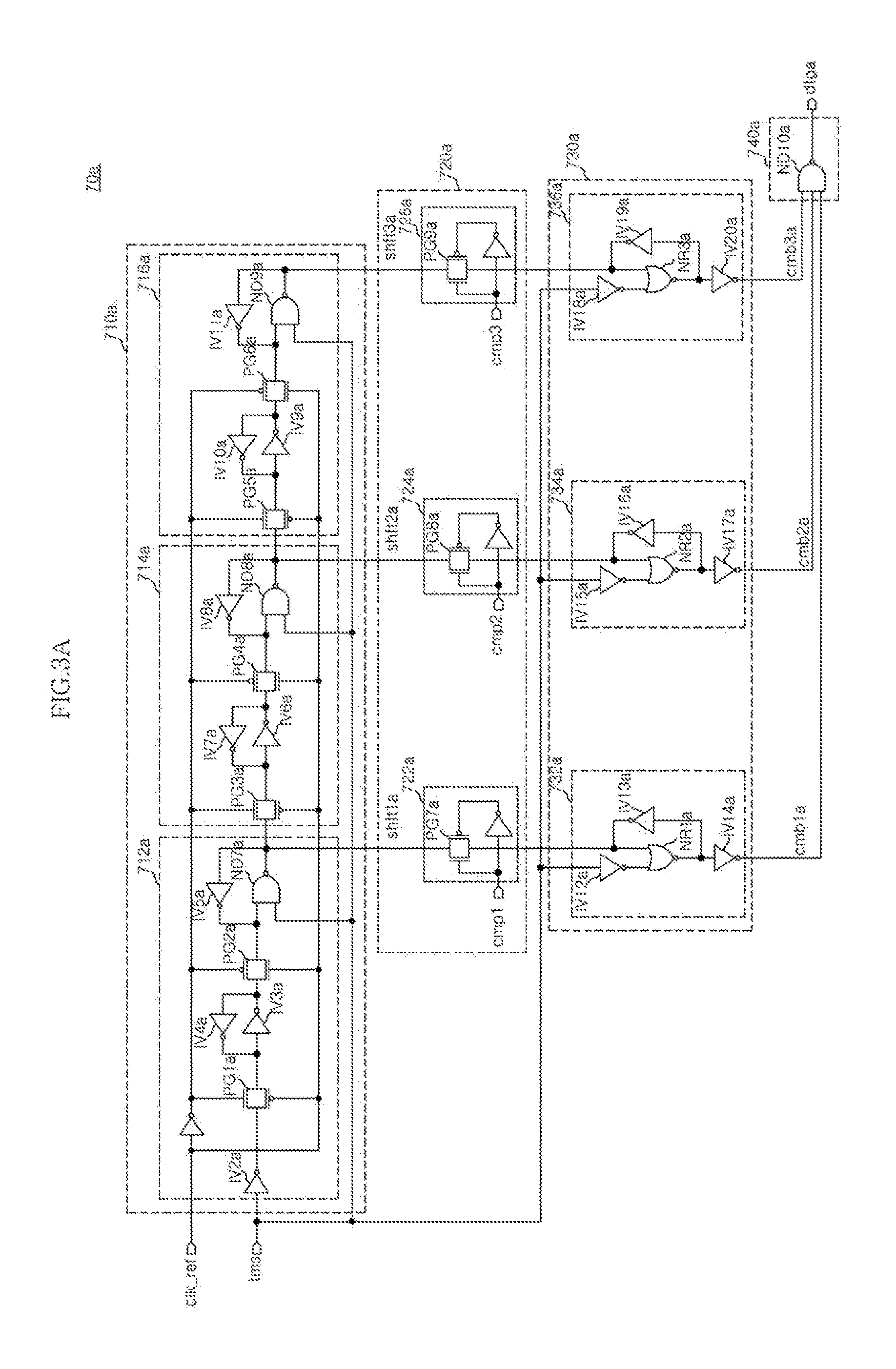

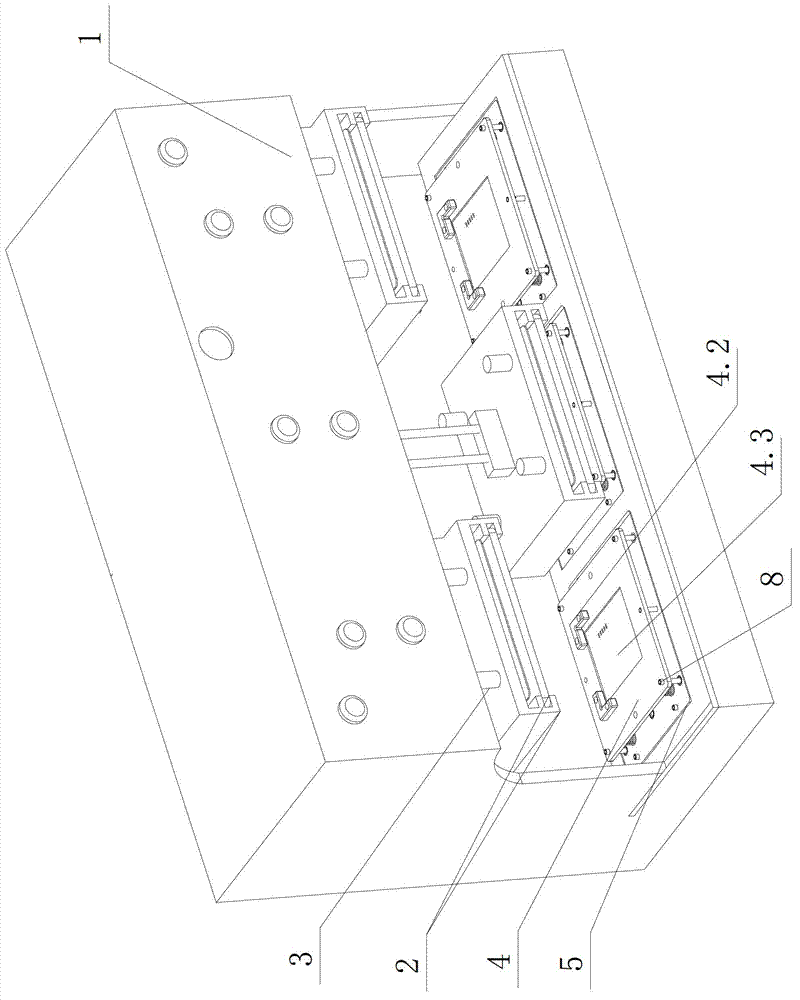

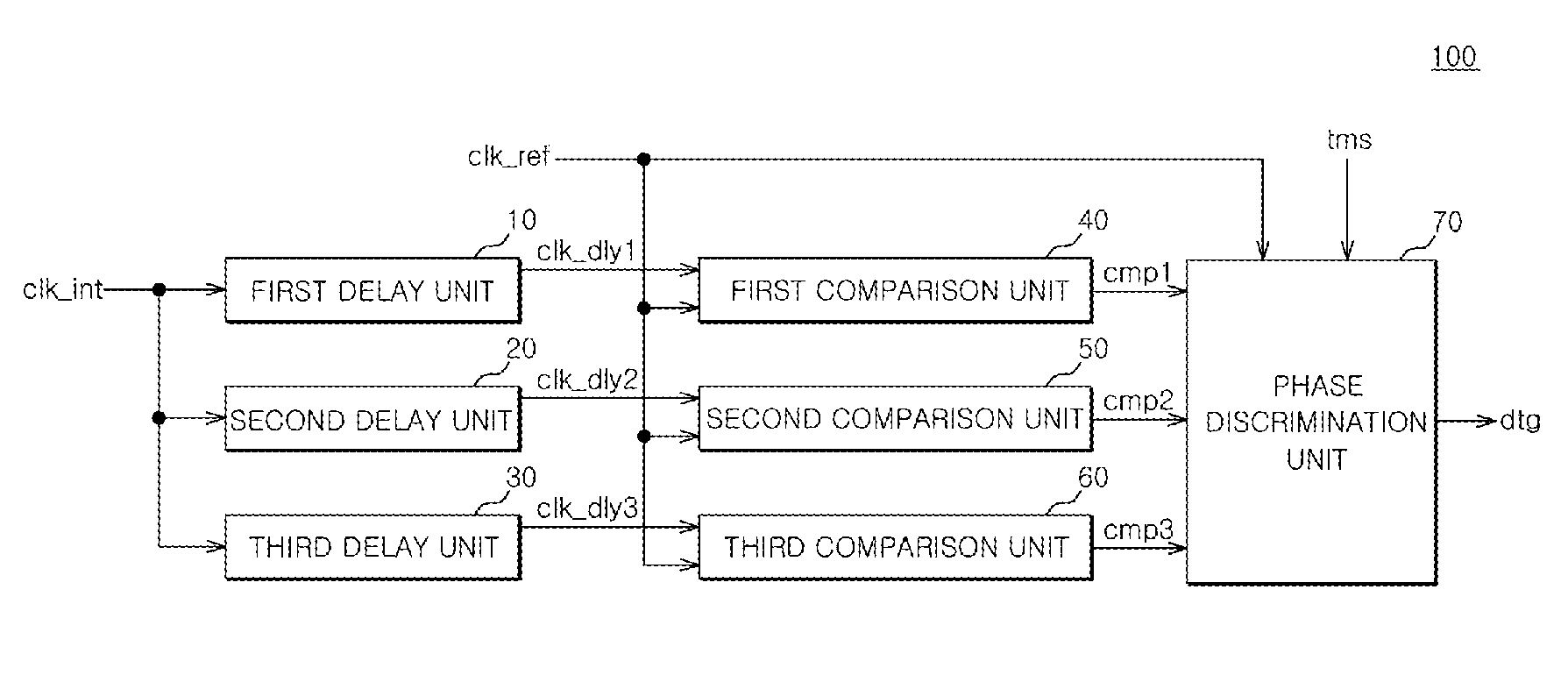

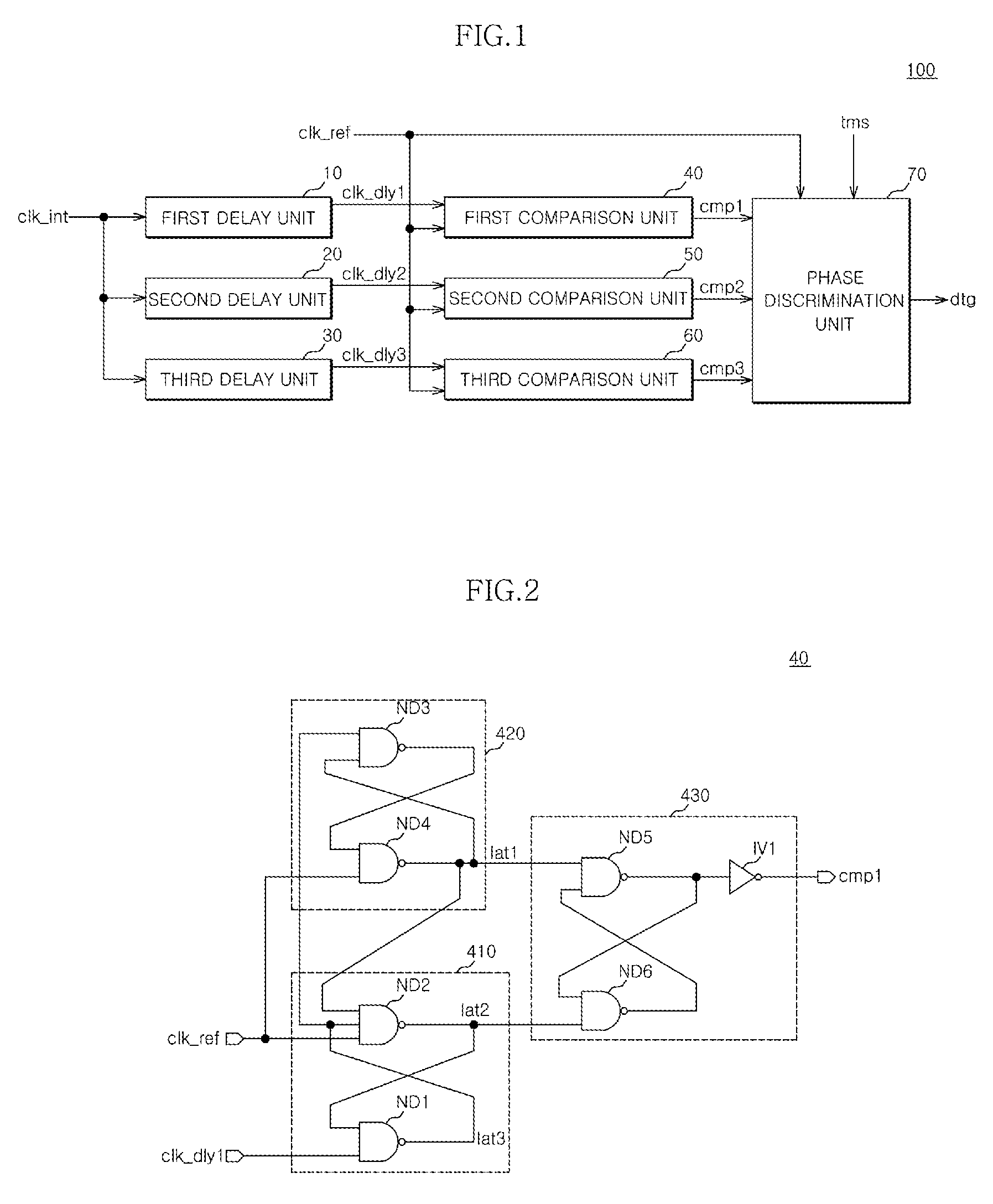

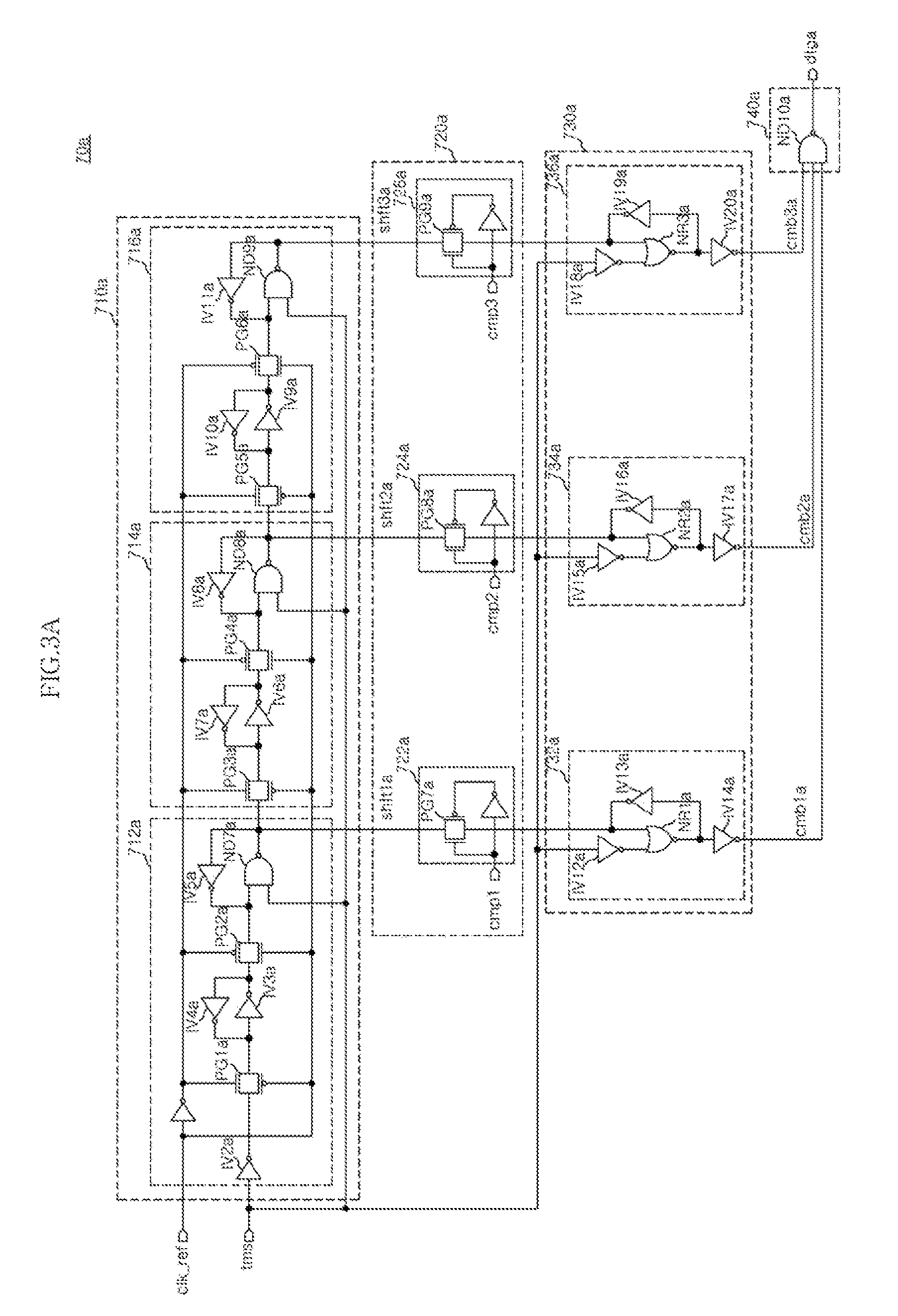

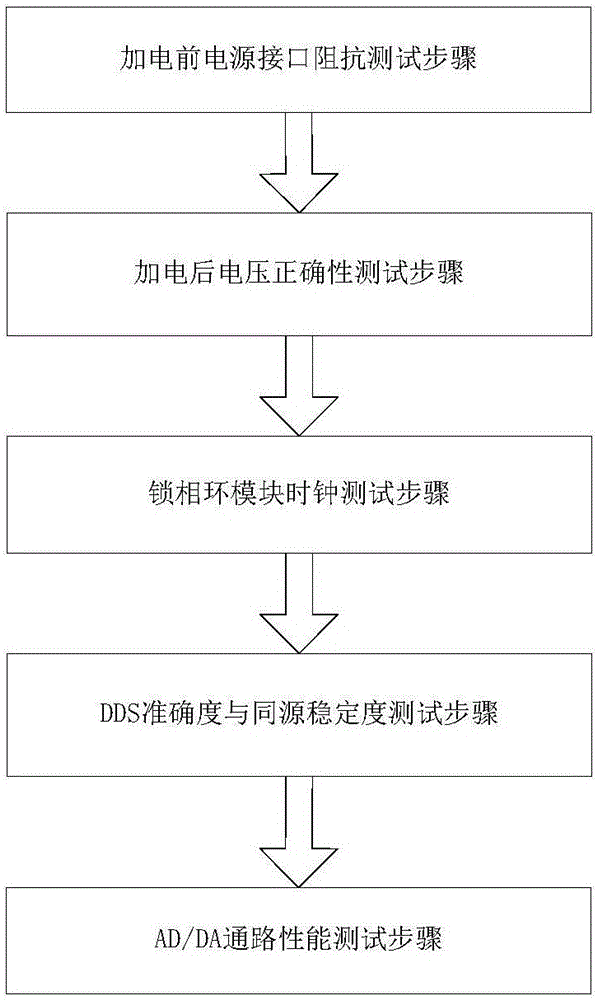

Clock test apparatus and method for semiconductor integrated circuit

A clock test apparatus for a semiconductor integrated circuit includes a delay unit configured to delay an internal clock signal. A comparison unit compares the phase of an output signal of the delay unit with the phase of a reference clock signal. A phase discrimination unit receives a test mode signal, the reference clock signal, and an output signal of the comparison unit, thereby outputting a discrimination signal.

Owner:SK HYNIX INC

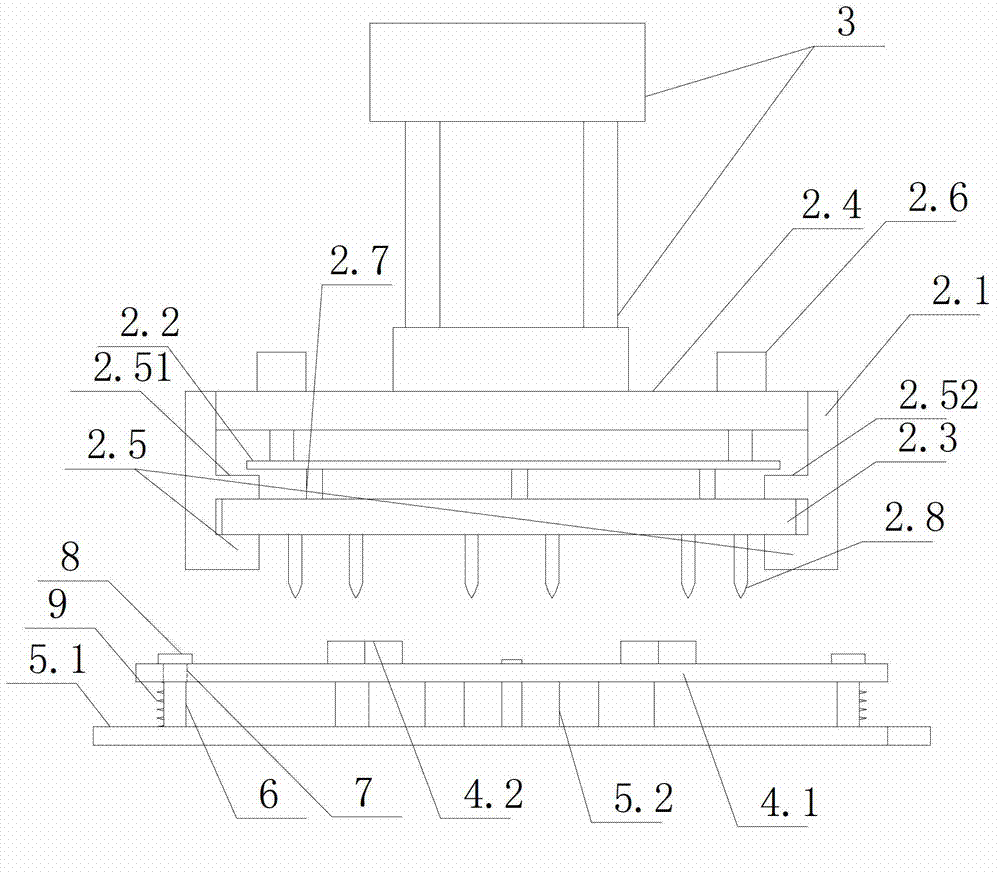

Test method based on final circular test (FCT) multi-station test device

ActiveCN103091624ATest saves time and effortImprove test efficiencyElectronic circuit testingTest efficiencyLab test method

The invention discloses a test method based on a final circular test (FCT) multi-station test device. The test method based on the FCT multi-station test device comprises the following steps: establishing a supply voltage database, writing in an address for a printed circuit board assembly (PCBA) of an electric energy meter, writing in a relay return circuit test program for the PCBA of the electric energy meter, establishing a test database, establishing an impulse test database, establishing a clock test database, fixing the PCBA on a single-station test device, supplying power for the PCBA of the electric energy meter, detecting supply voltage, detecting 485 port, detecting a relay return circuit of the PCBA, detecting the impulse of the electric energy meter, detecting a clock of the electric energy meter, lowering the voltage, detecting battery a current of the PCBA of the electric energy meter, and fetching out the PCBA of the electric energy meter from the single-station test device. The test method based on the final circular test (FCT) multi-station test device has the advantages of being time-saving, labor-saving, high in test efficiency and high in precision of test results.

Owner:NINGBO SANXING INTELLIGENT ELECTRIC

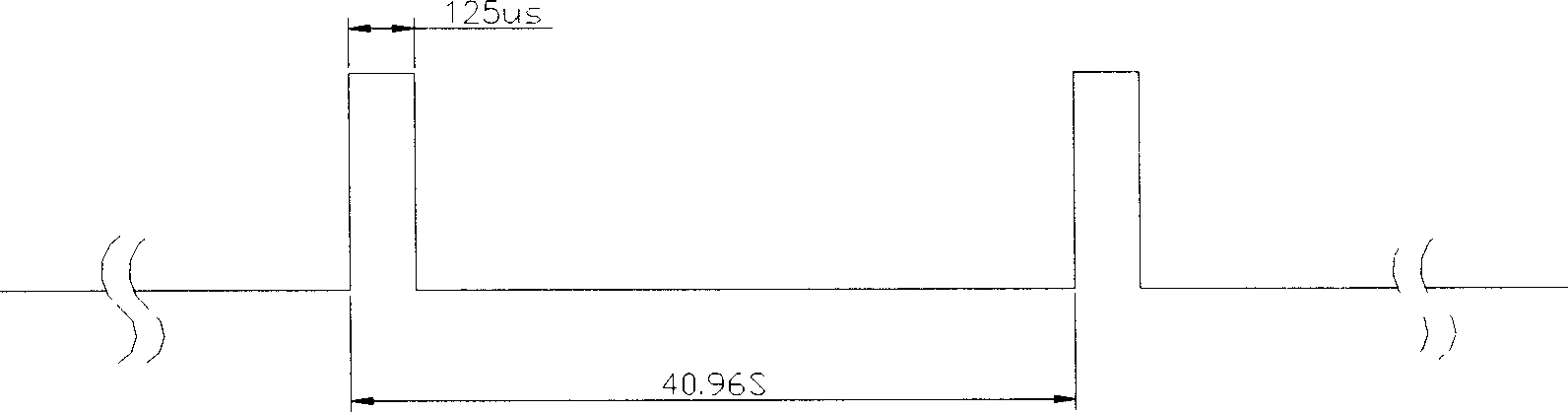

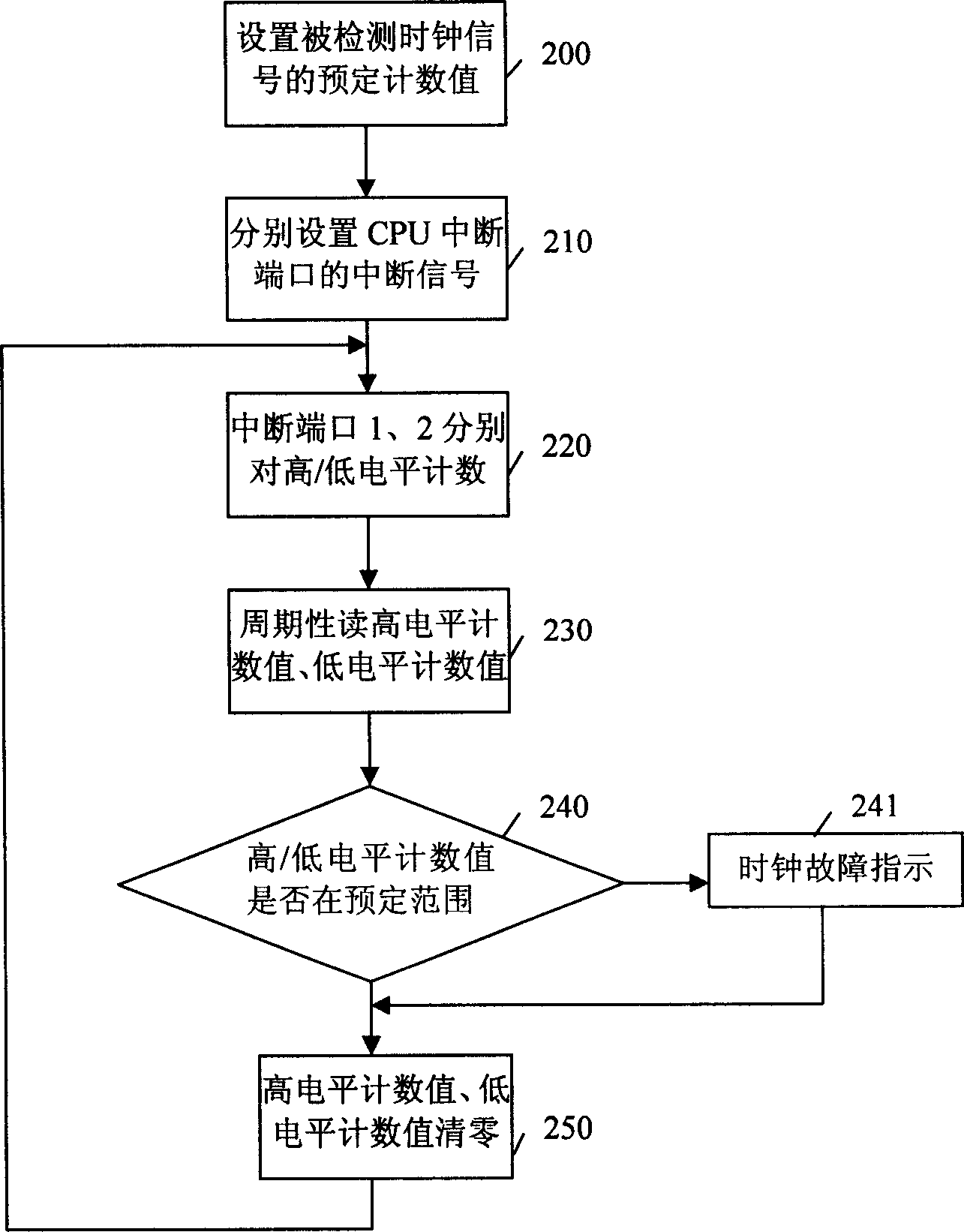

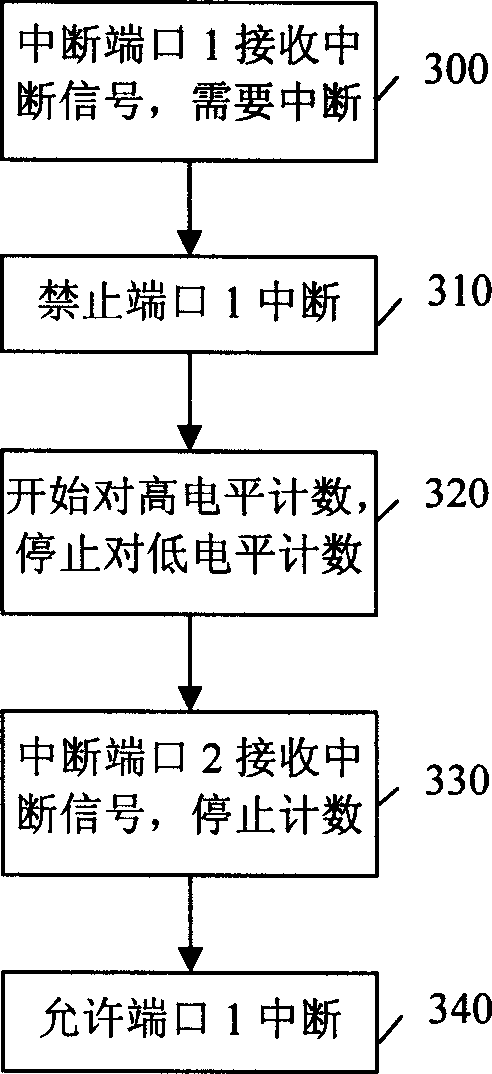

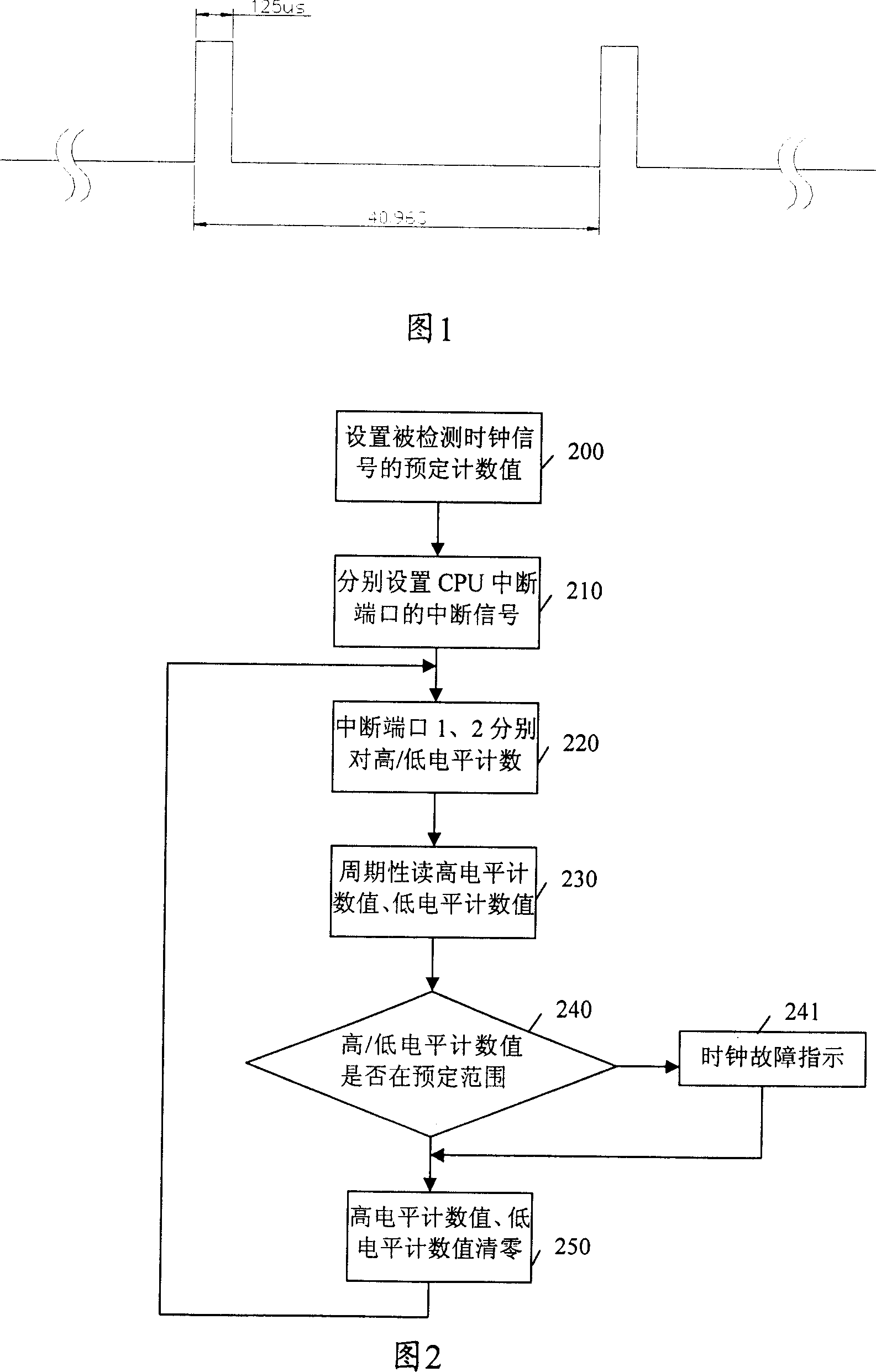

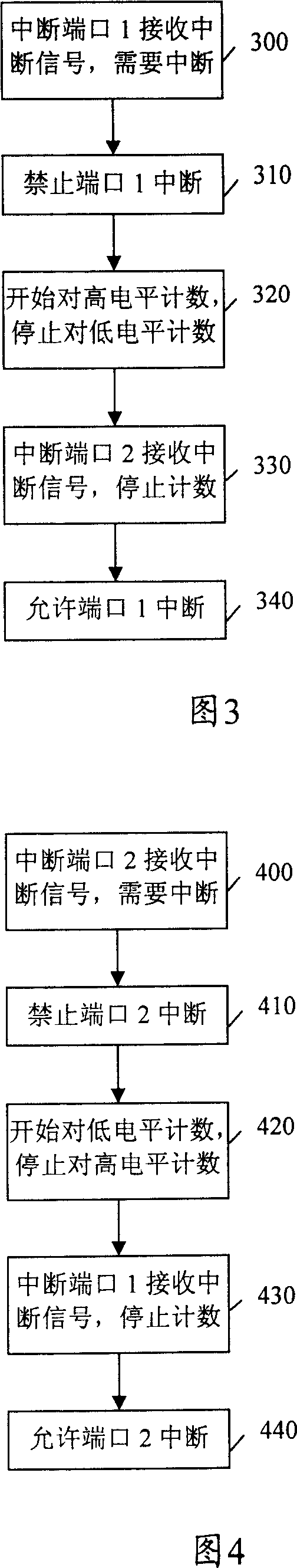

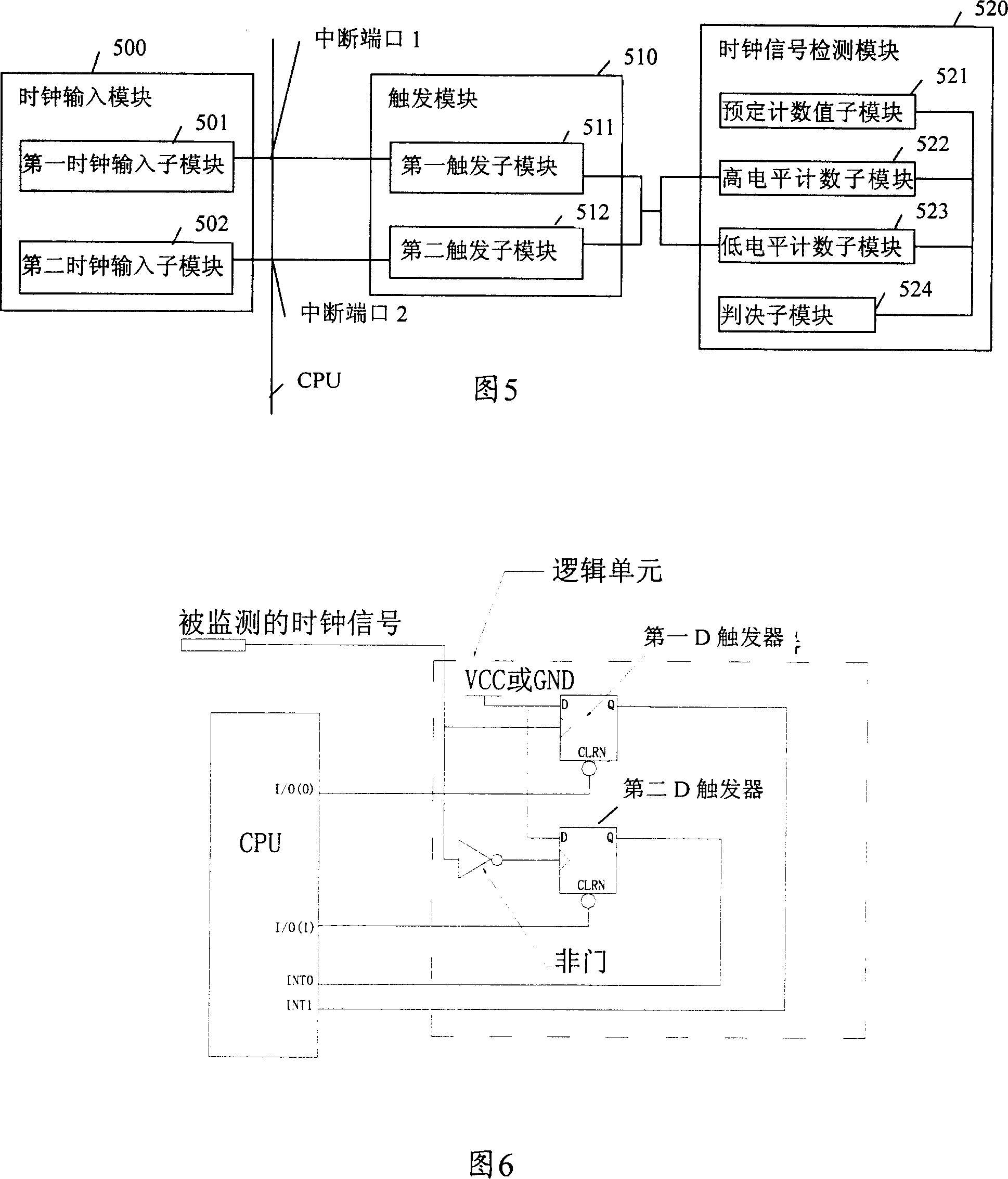

Clock signal detection method and apparatus in electronic devices

ActiveCN1655454ASimple designImprove reliabilityPulse techniqueSynchronising arrangementComputer scienceClock Test

This invention provides an electron device clock testing method, which comprises the following steps: determining the said CPU interval terminal signals and inputting the tested clock signal into the interval end of the said CPU; triggering the said tested clock signals for testing according to the interval signal. The invention provides an electron clock test device, which comprises clock input module, triggering module and clock signal test module.

Owner:DATANG MOBILE COMM EQUIP CO LTD

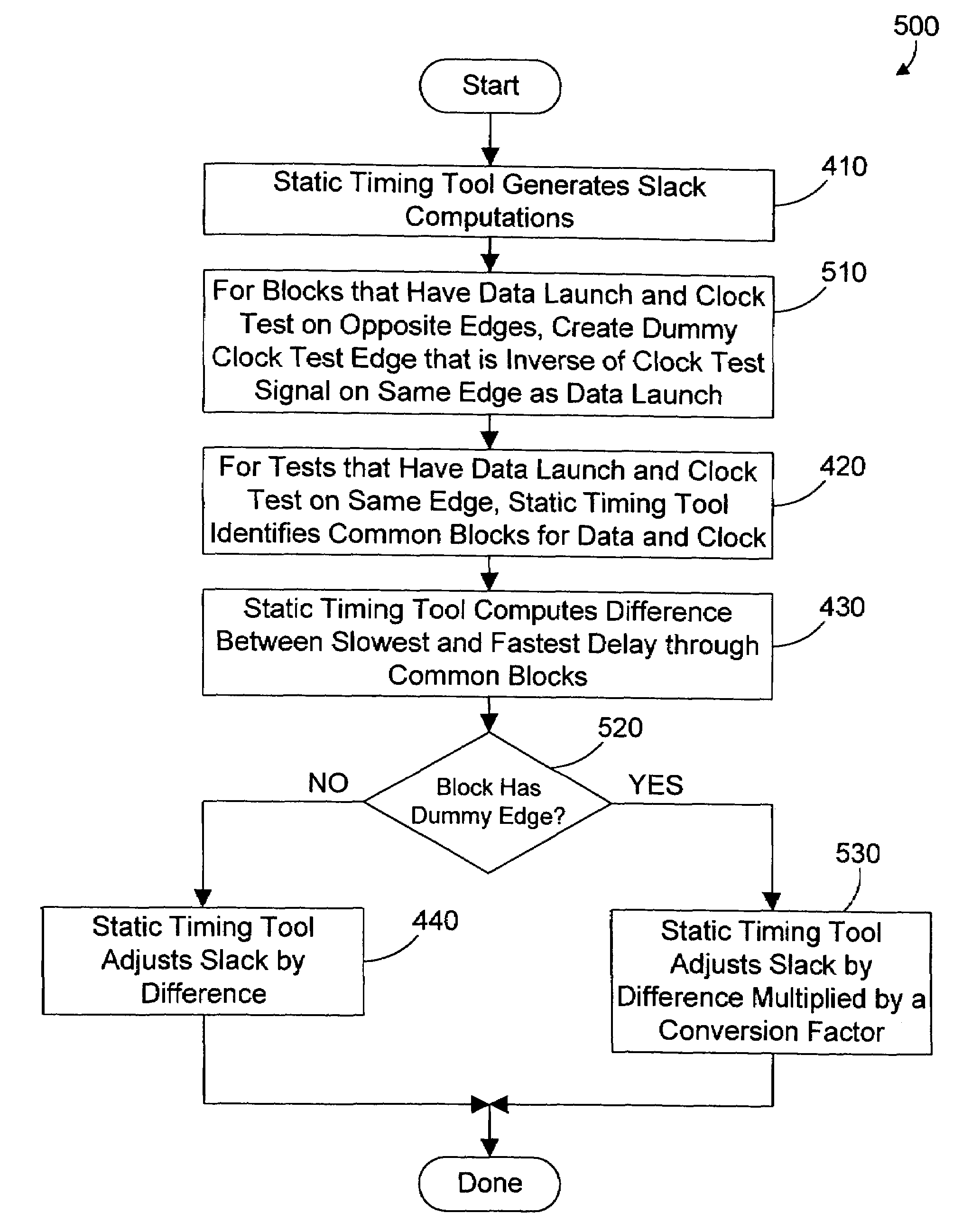

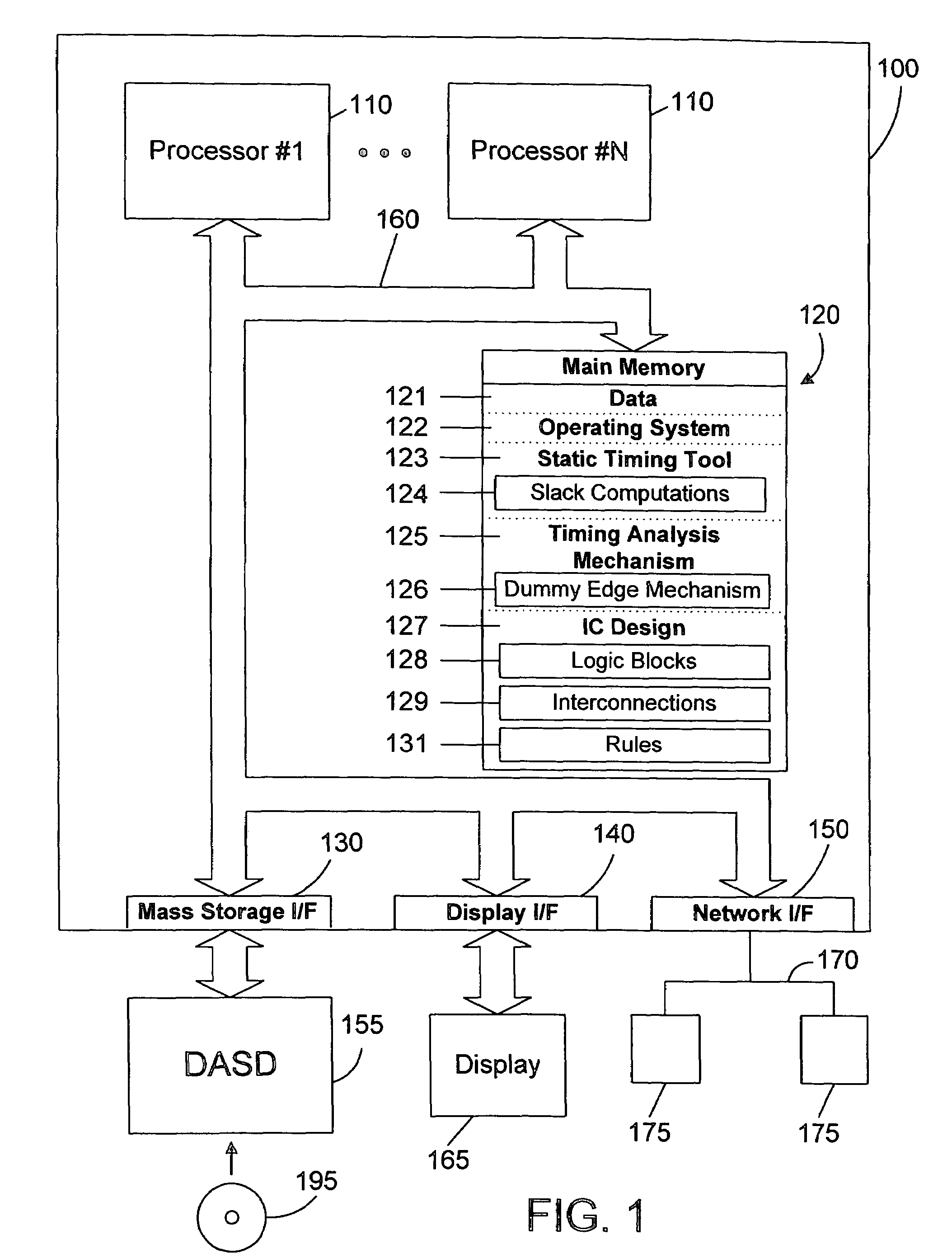

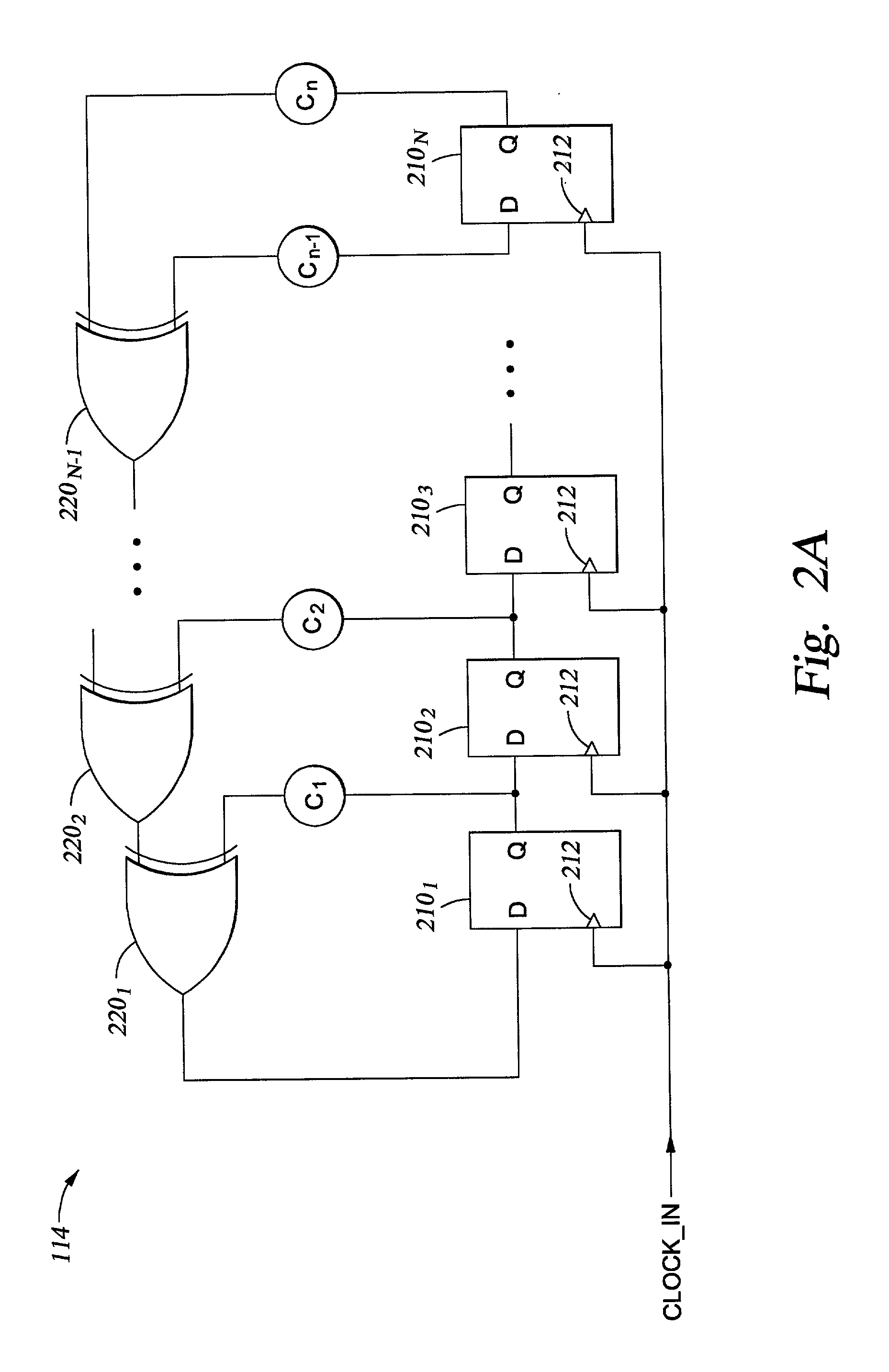

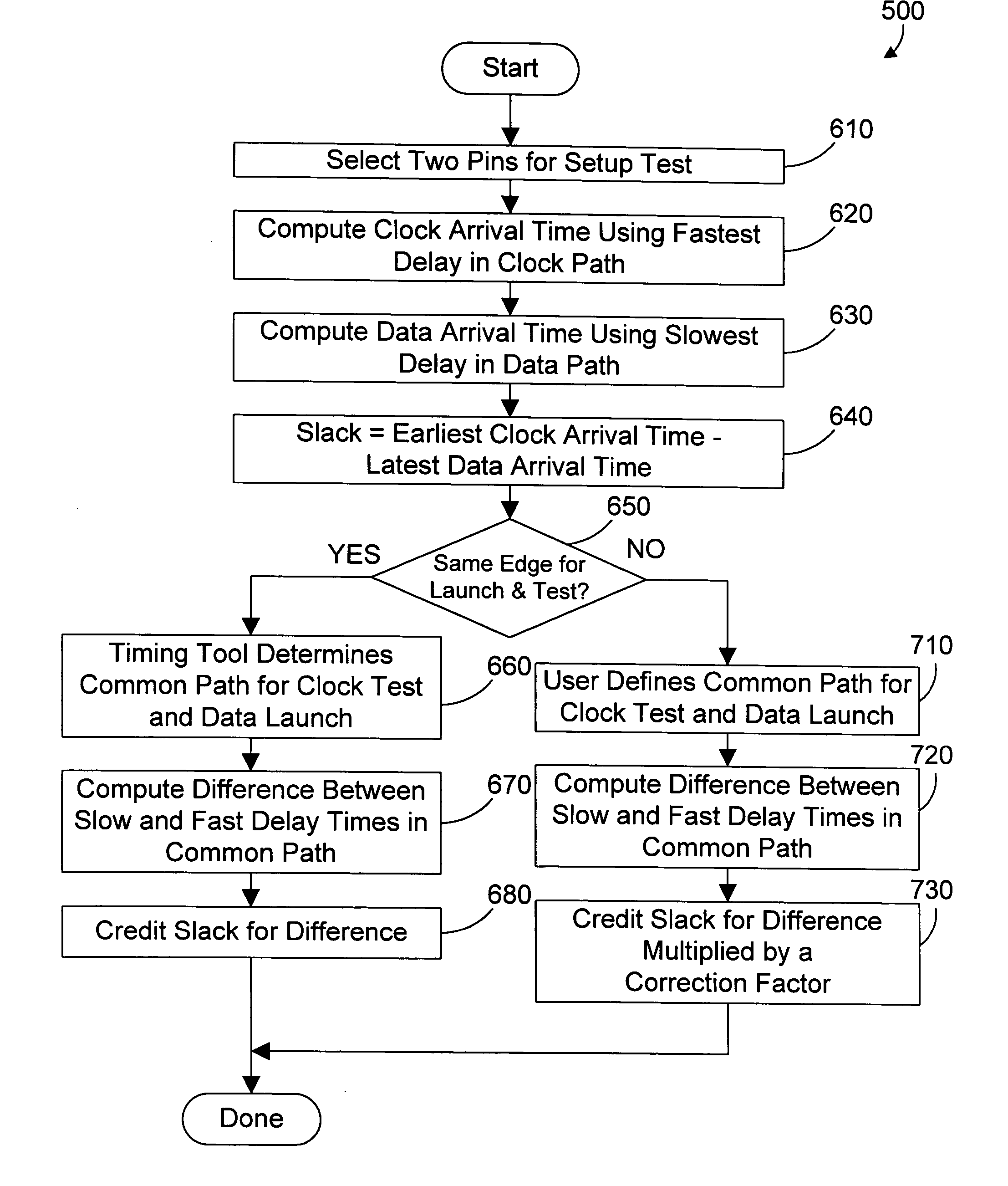

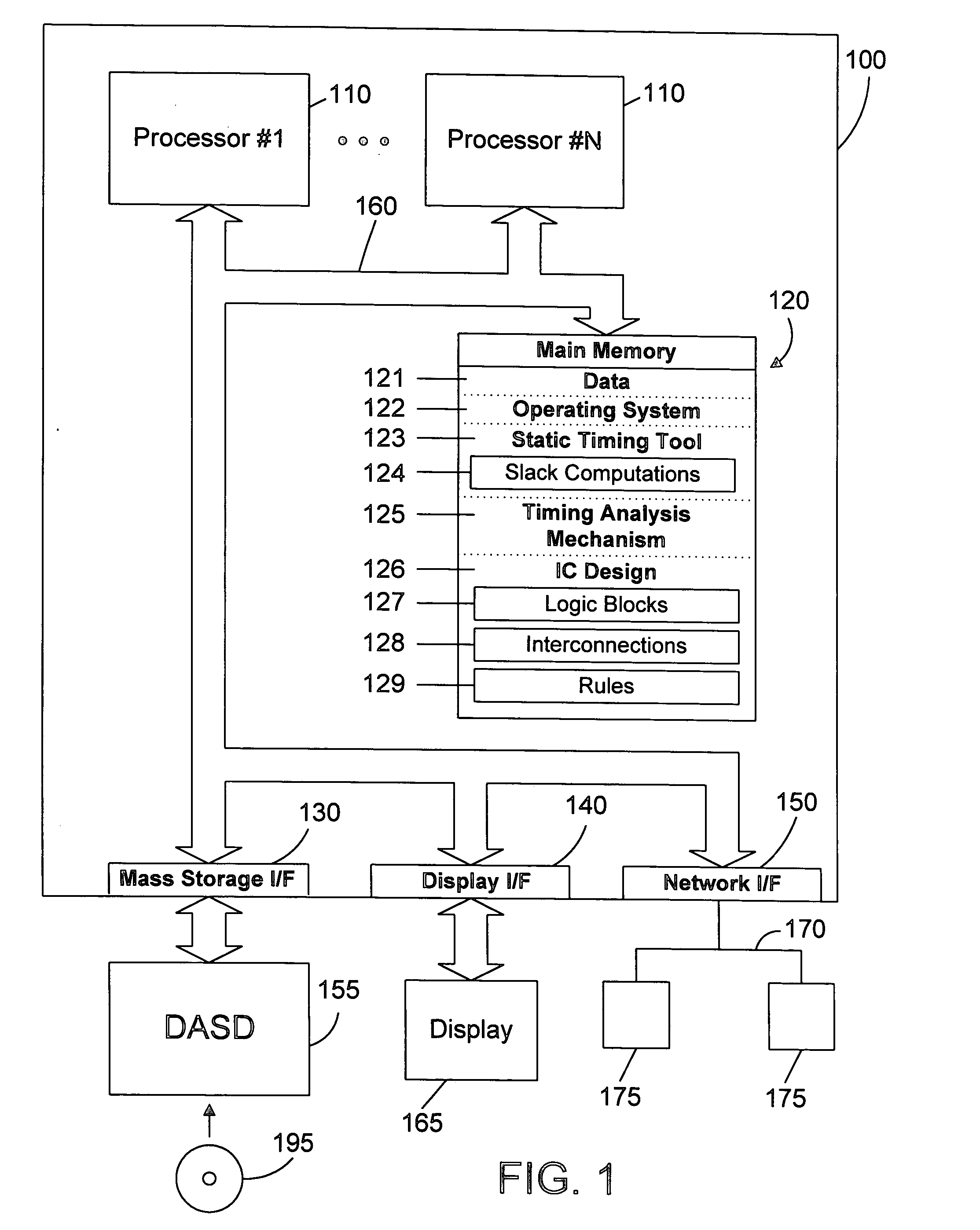

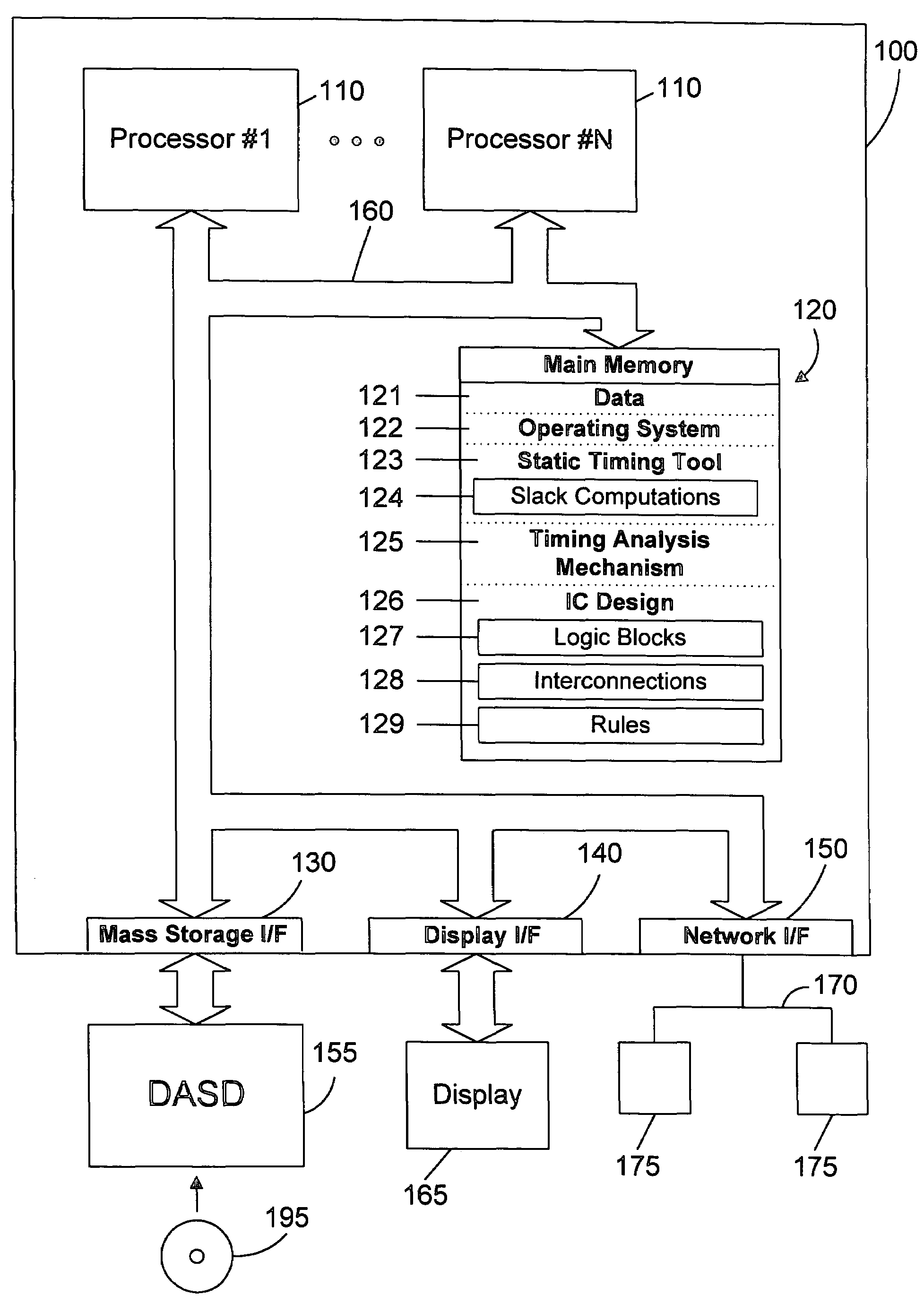

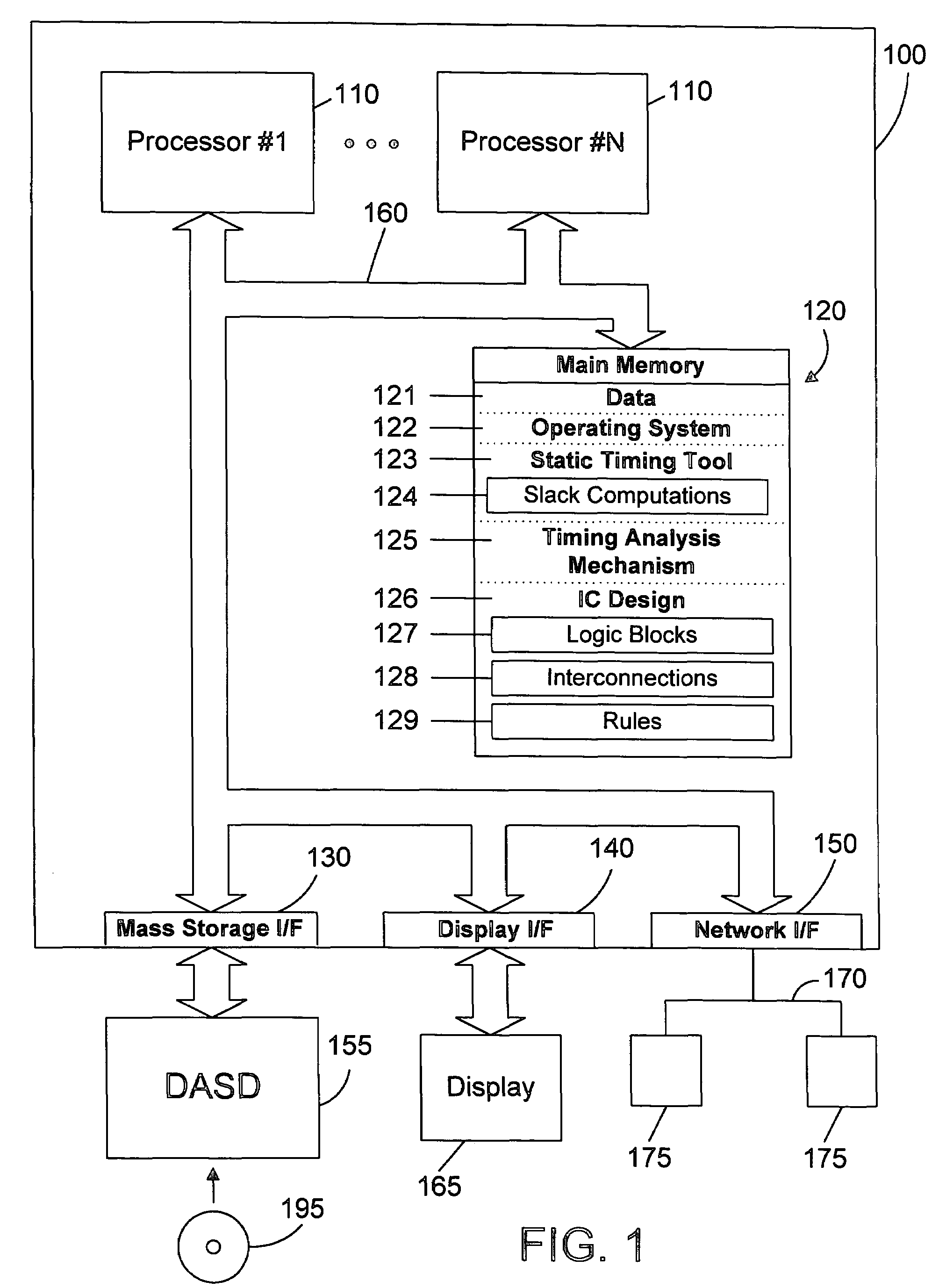

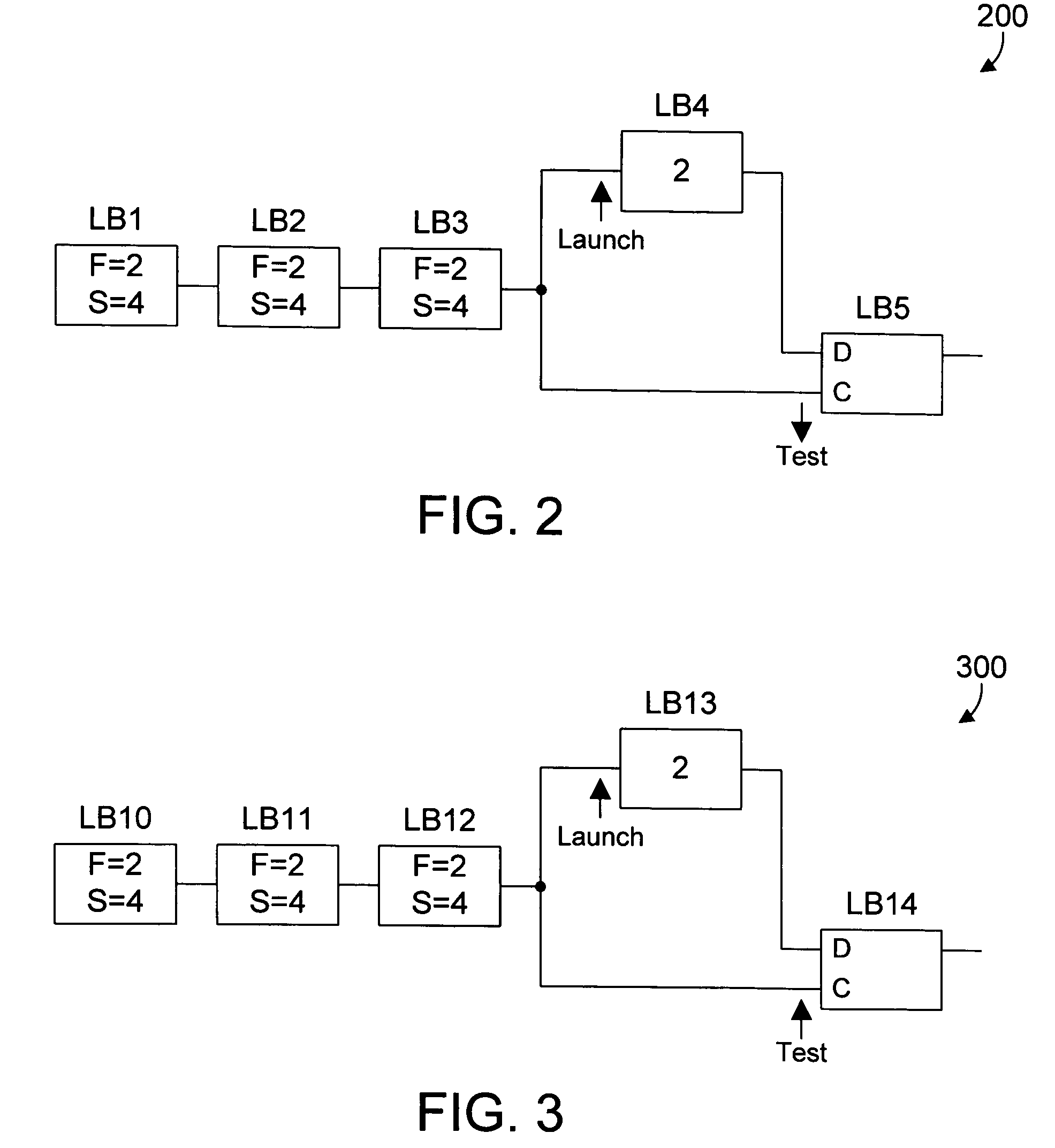

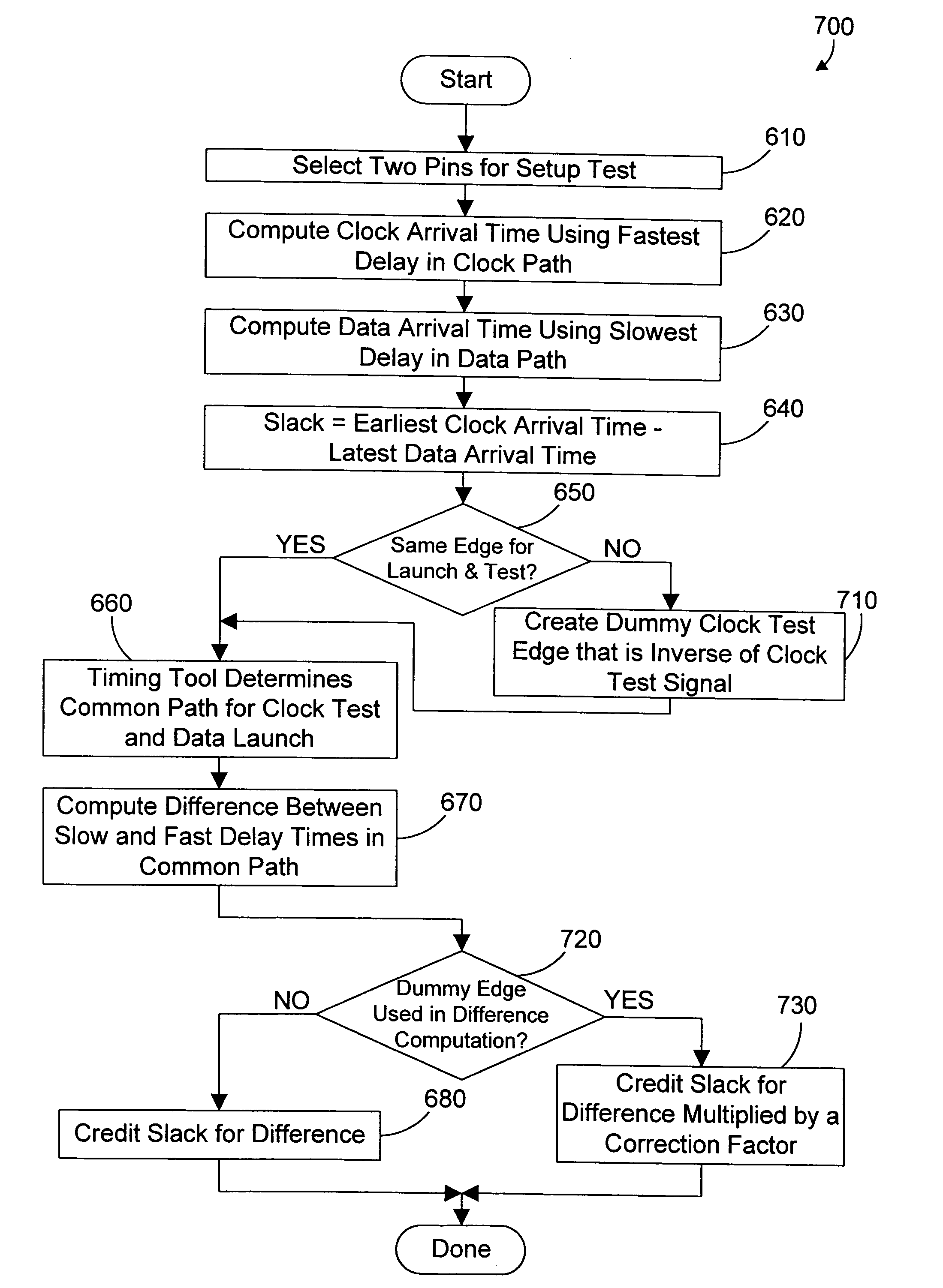

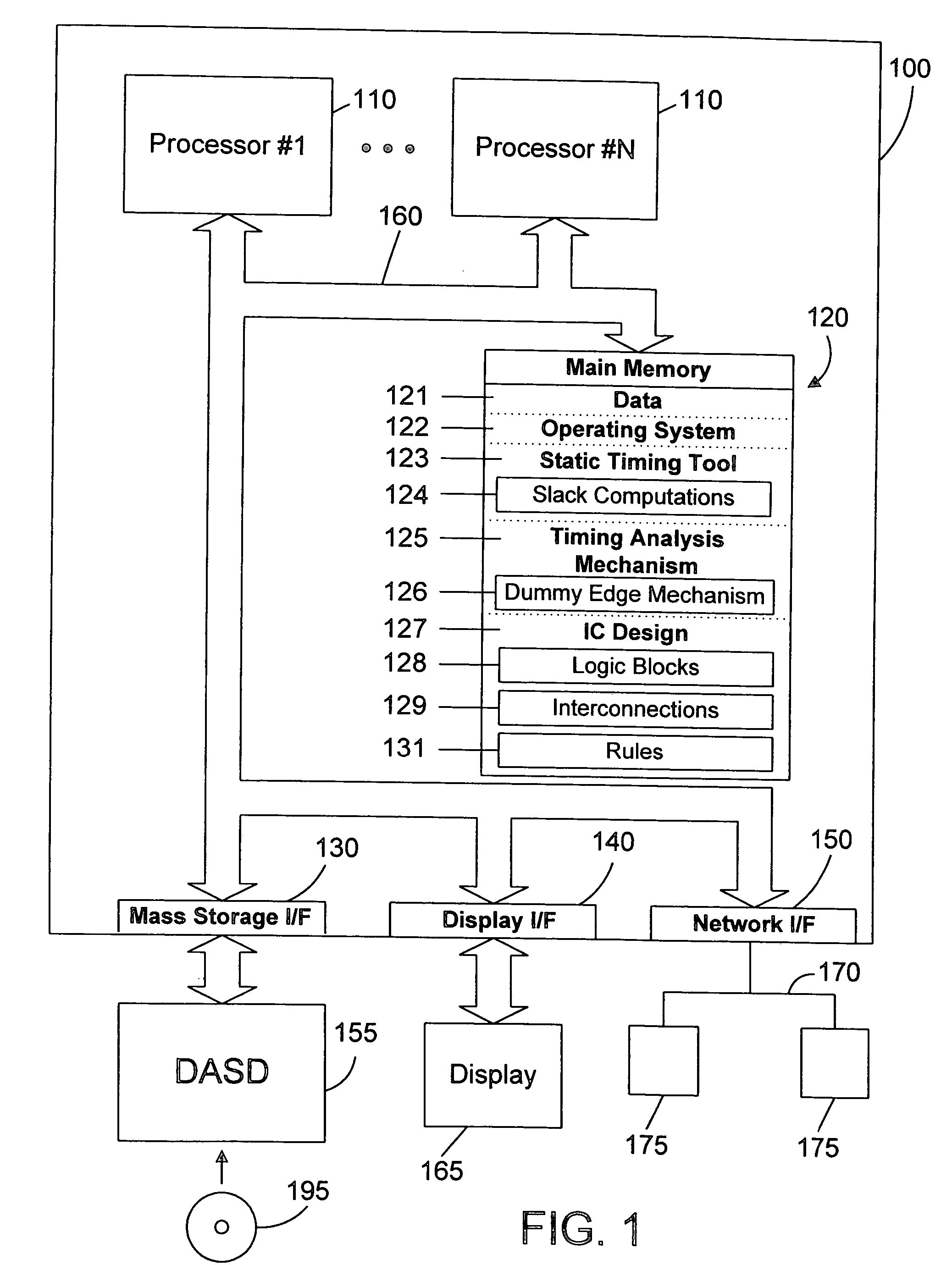

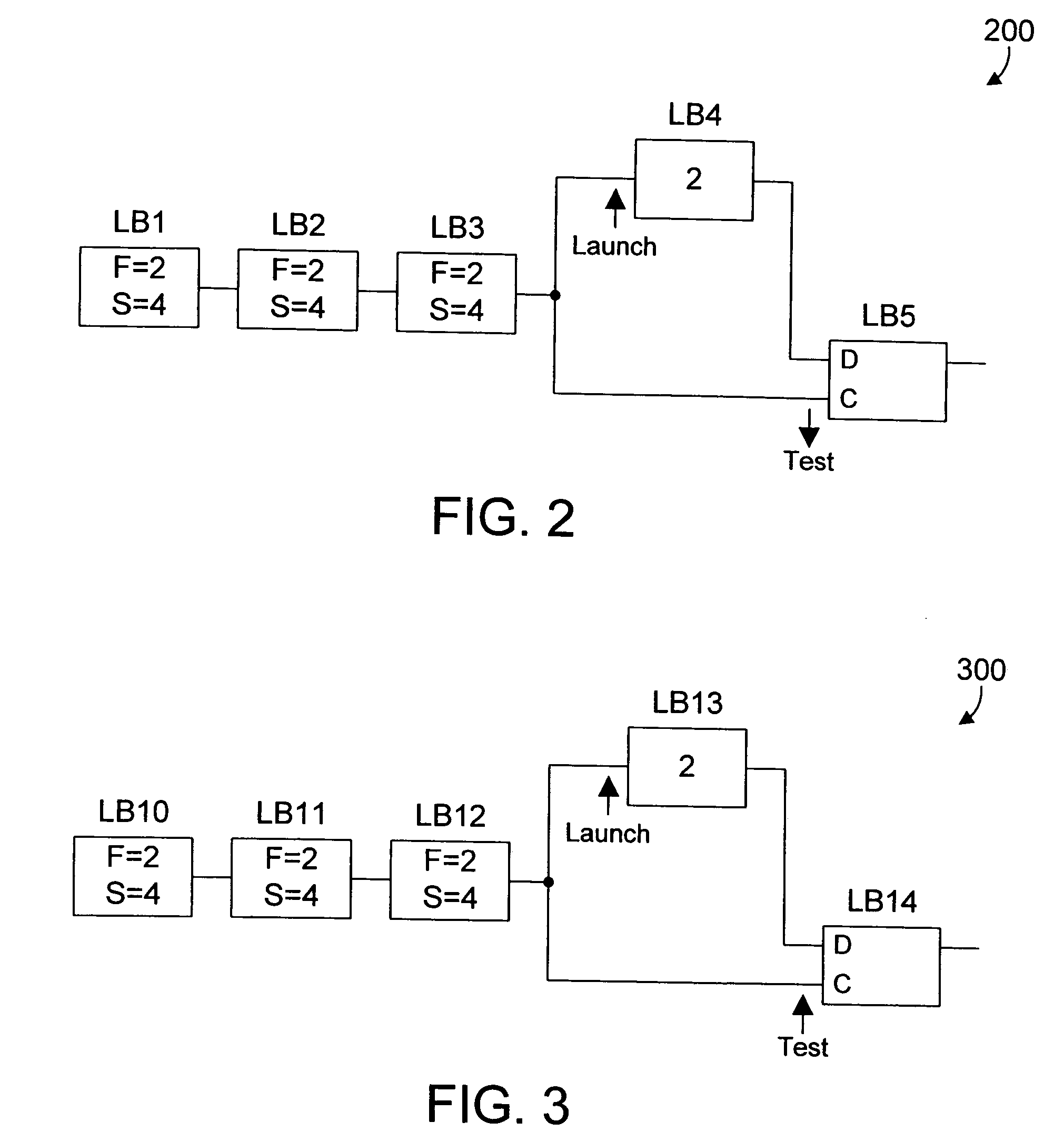

Apparatus and method for performing static timing analysis of an integrated circuit design using dummy edge modeling

InactiveUS7143379B2Reduce workloadComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisConversion factor

An apparatus and method perform static timing analysis on an integrated circuit design. Certain pessimistic assumptions regarding slack when data launch and clock test signals are on opposite edges and derived from common logic blocks are improved by creating a dummy clock edge that is on the same edge as the data launch signal, and allowing the timing tool to compute the slack improvement using its native functions. The slack improvement is then multiplied by a conversion factor, and the result is used to adjust the slack. The apparatus and method give credit for slack in common blocks automatically, thereby allowing a large number of pessimistic slack values to be automatically corrected and reducing the workload of an integrated circuit designer in addressing the timing problems in an integrated circuit design.

Owner:INT BUSINESS MASCH CORP

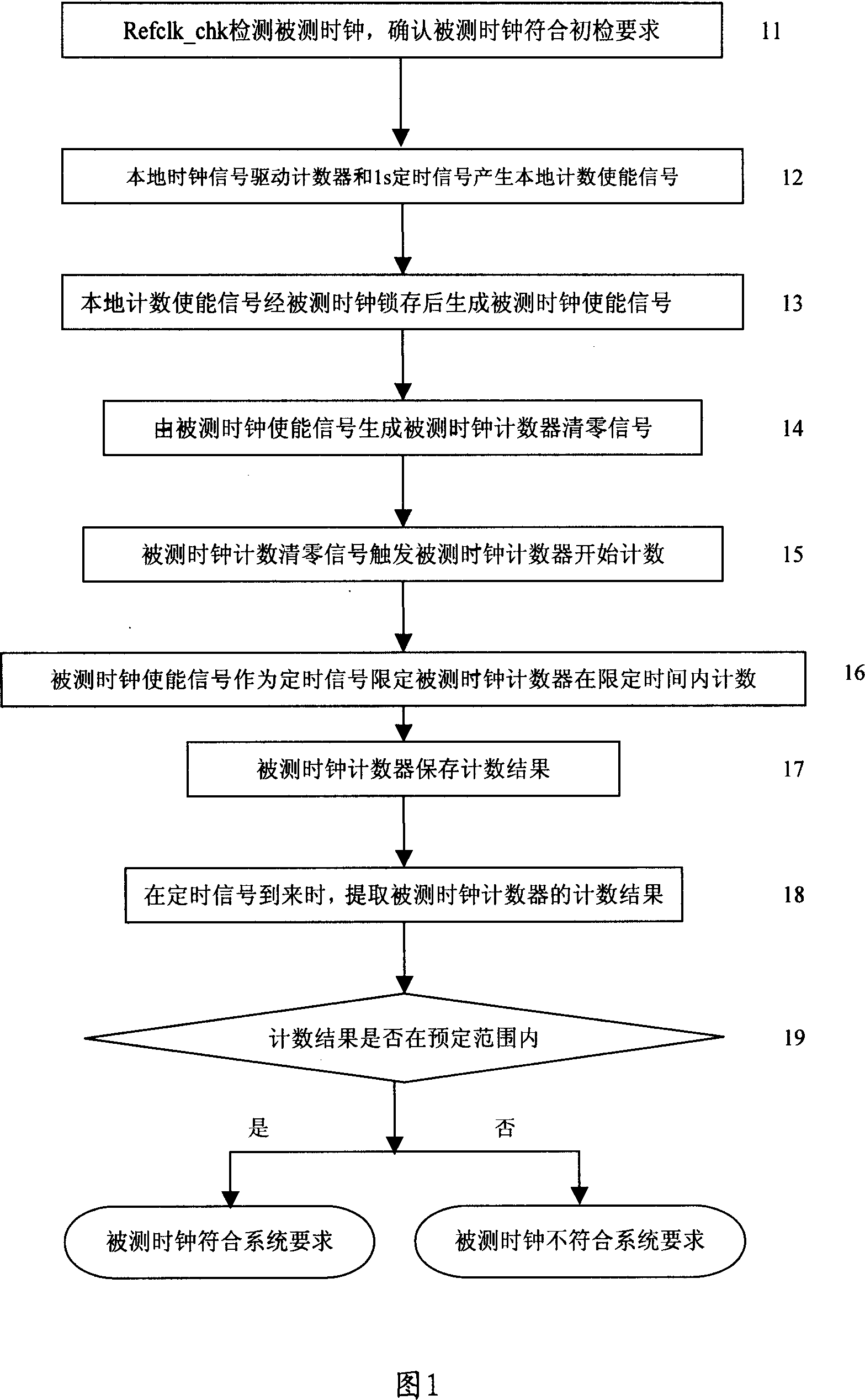

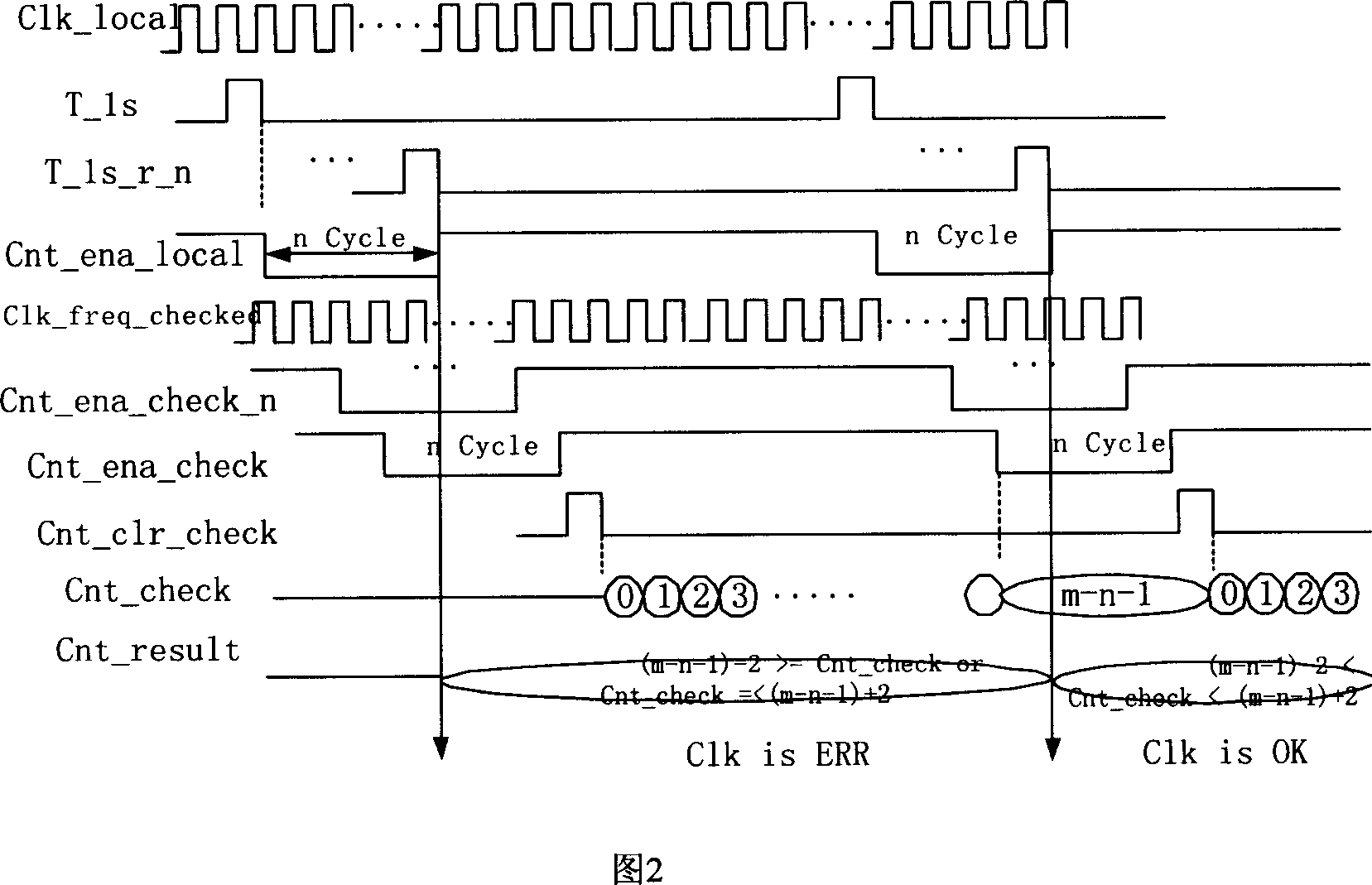

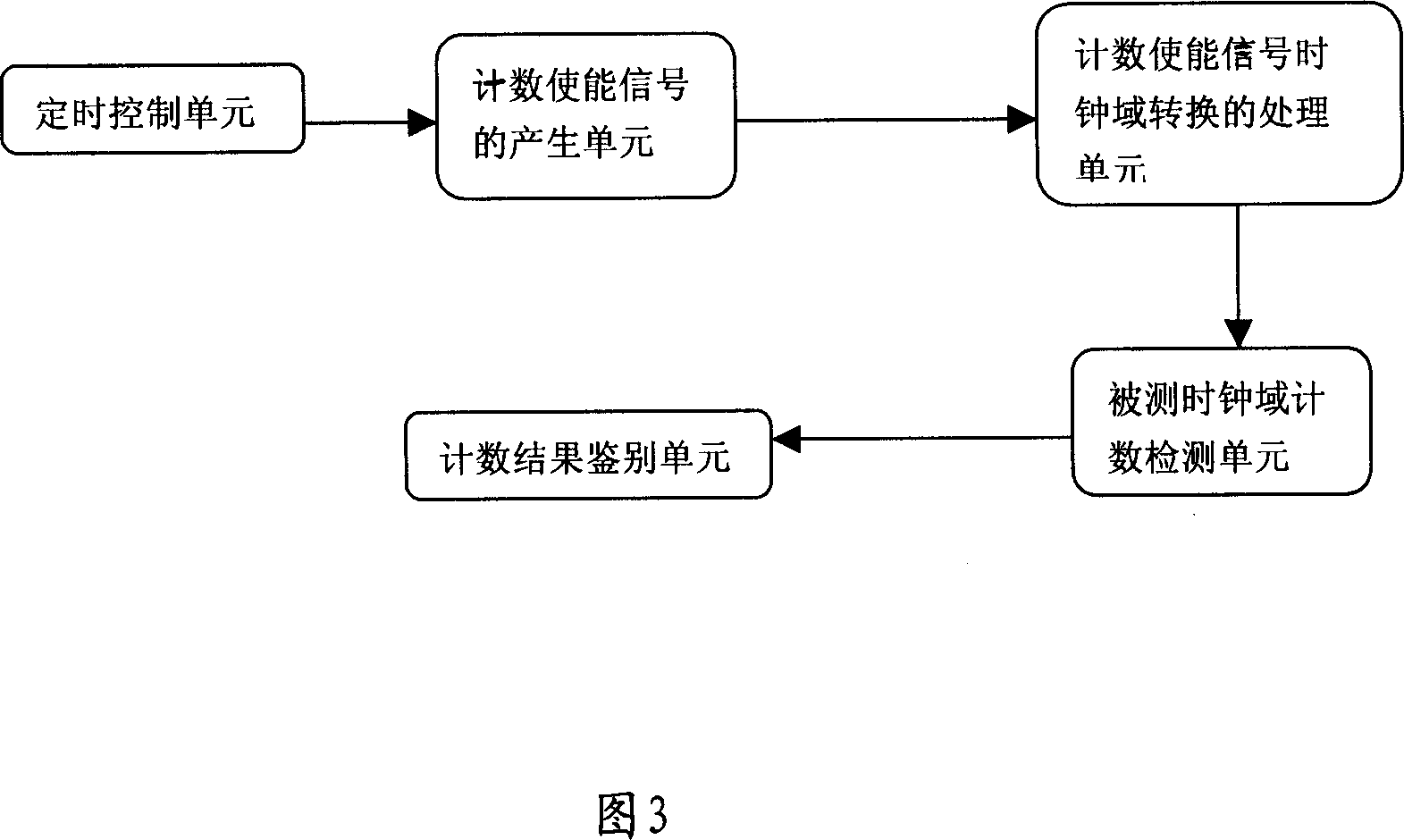

Method and device for clock detection

InactiveCN1925329ADetection accuracy meetsReliable servicePulse train pattern monitoringError detection/correctionClock rateTimer

This invention relates to one clock test method and device, which comprises the following steps: firstly generating meter energy signals according to local timing mechanism and the meter can transfer the tested signals into the clock zone to be tested to generate clock timer energy signals of zero and triggering the tested clock zone meter by signal and to start metering at fixed time circle; observing meter results to judge the accuracy of the clock to be tested.

Owner:HUAWEI TECH CO LTD

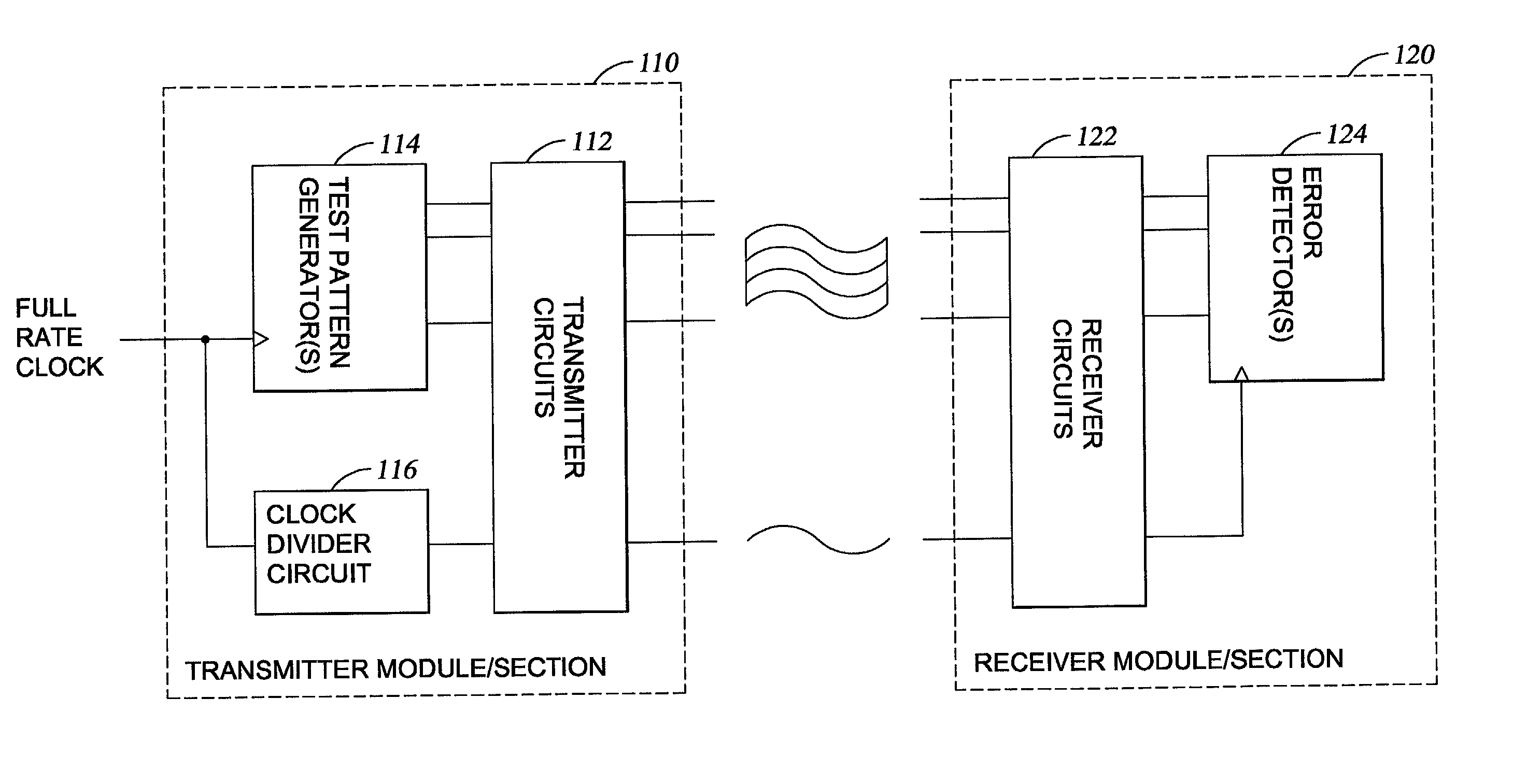

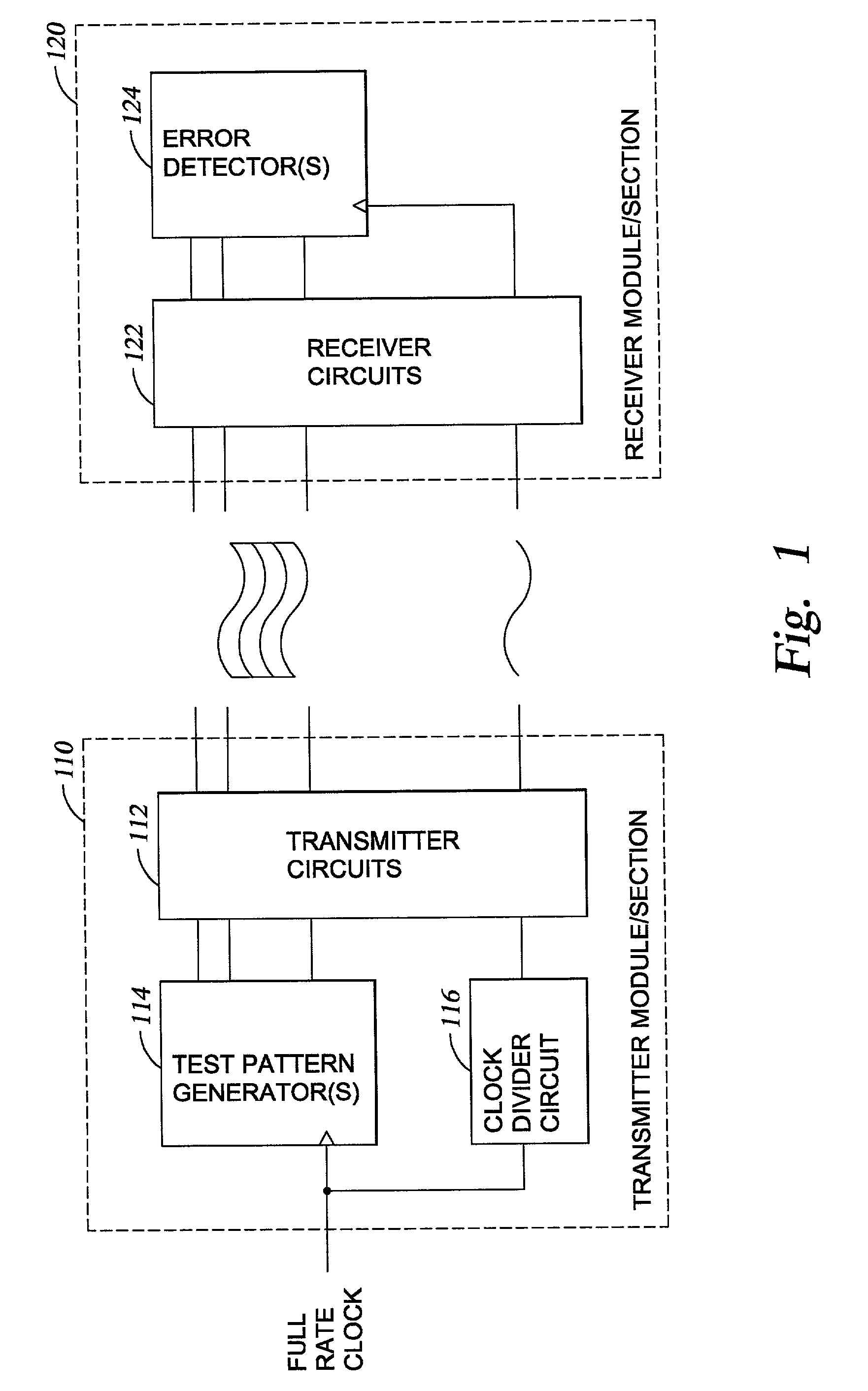

Architecture for built-in self-test of parallel optical transceivers

Method and apparatus for testing a parallel optical transceiver are provided. One embodiment provides a built-in self-testing (BIST) parallel optical transceiver comprising a full-rate clock test pattern generator and a clock divider circuit connected to provide a half-rate clock signal to one of the one or more transmitter channels, and an error detector comprising one or more error detection circuits connected to one or more receiver channels and configured to receive the half-rate clock signal. Another embodiment provides a method for testing a parallel optical transceiver, comprising: generating a full-rate clock test pattern to one or more transmitter channels; providing a half-rate clock signal to one of the one or more transmitter channels utilizing a clock divider circuit; transmitting test pattern and half-rate clock signals to one or more corresponding receiver channels; and detecting error utilizing one or more error detection circuits connected to receive the half-rate clock signal.

Owner:IBM CORP

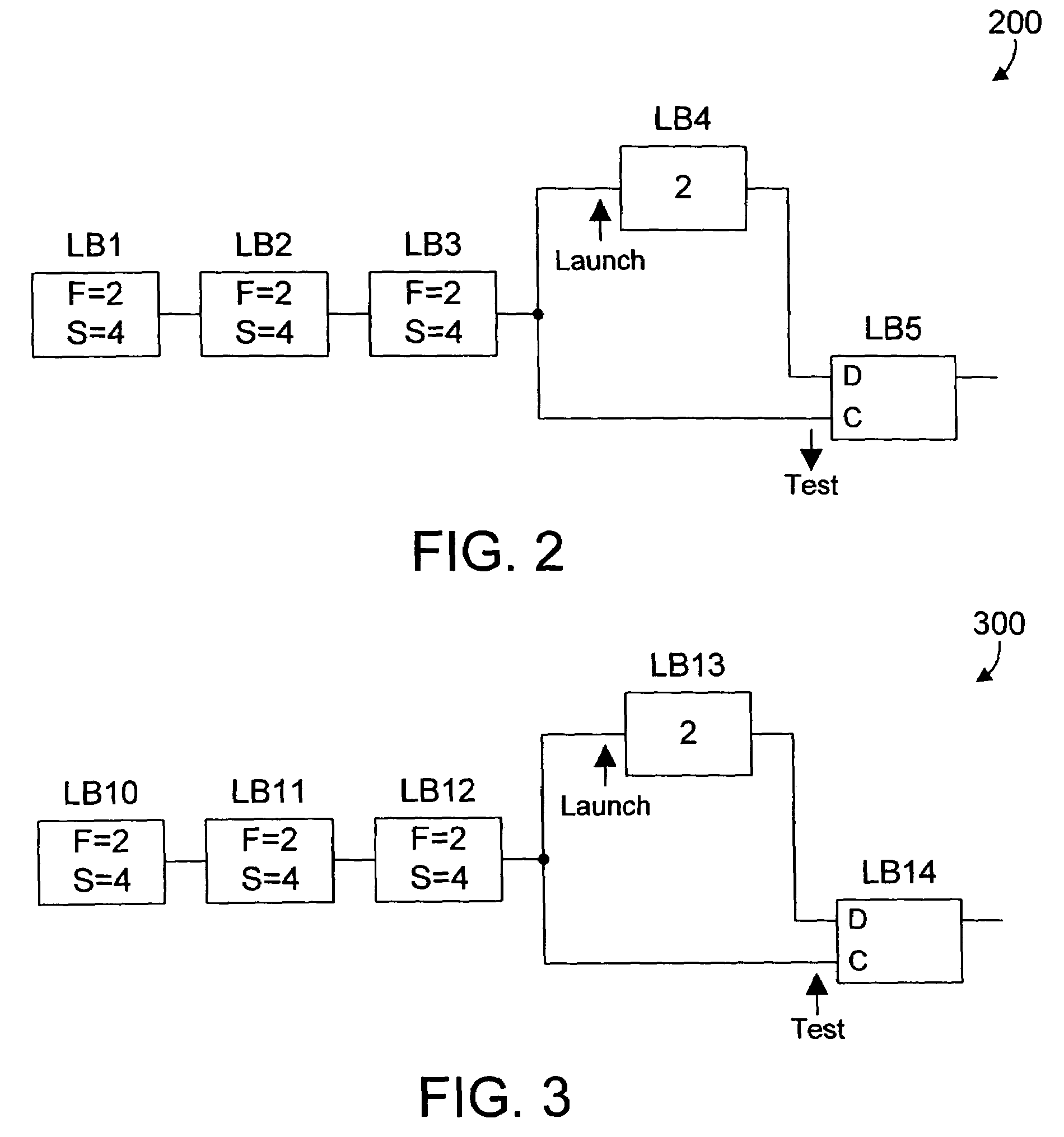

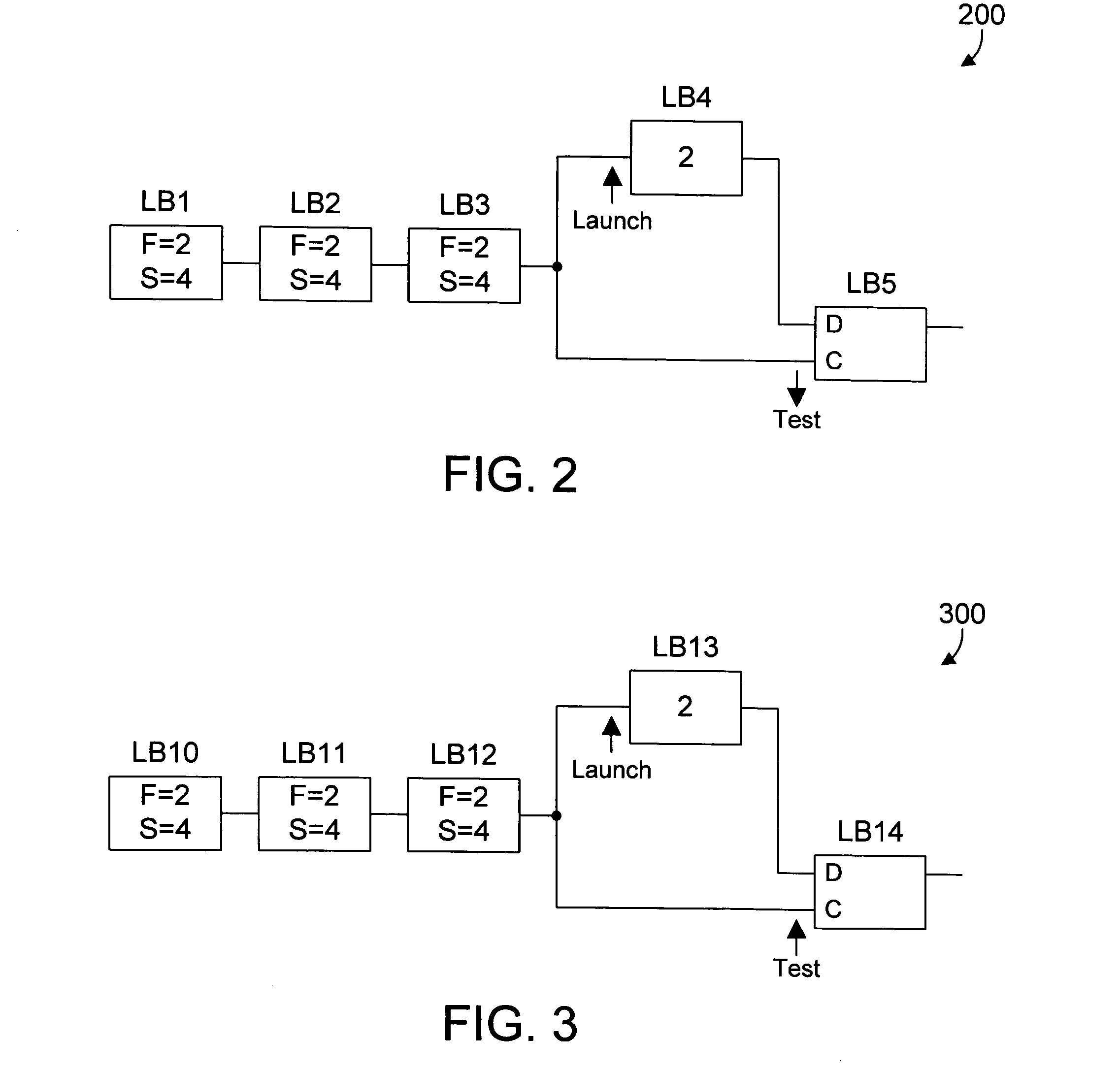

Apparatus and method for performing static timing analysis of an integrated circuit design

InactiveUS20050183051A1Reduce workloadExcessive pessimismComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisComputer architecture

An apparatus and method perform static timing analysis on an integrated circuit design. Certain pessimistic assumptions regarding slack when data launch and clock test signals are on opposite edges and derived from common logic blocks are improved by allowing the designer to identify common logic blocks, to compute the difference between maximum and minimum delays in the common logic blocks, and to improve the slack using this computed difference and a correction factor, thereby accounting for excessive pessimism in the static timing analysis that results from the common logic blocks. The apparatus and method give credit for slack in common blocks automatically, thereby allowing a large number of pessimistic slack values to be automatically corrected and reducing the workload of an integrated circuit designer in addressing the timing problems in an integrated circuit design.

Owner:GOOGLE LLC

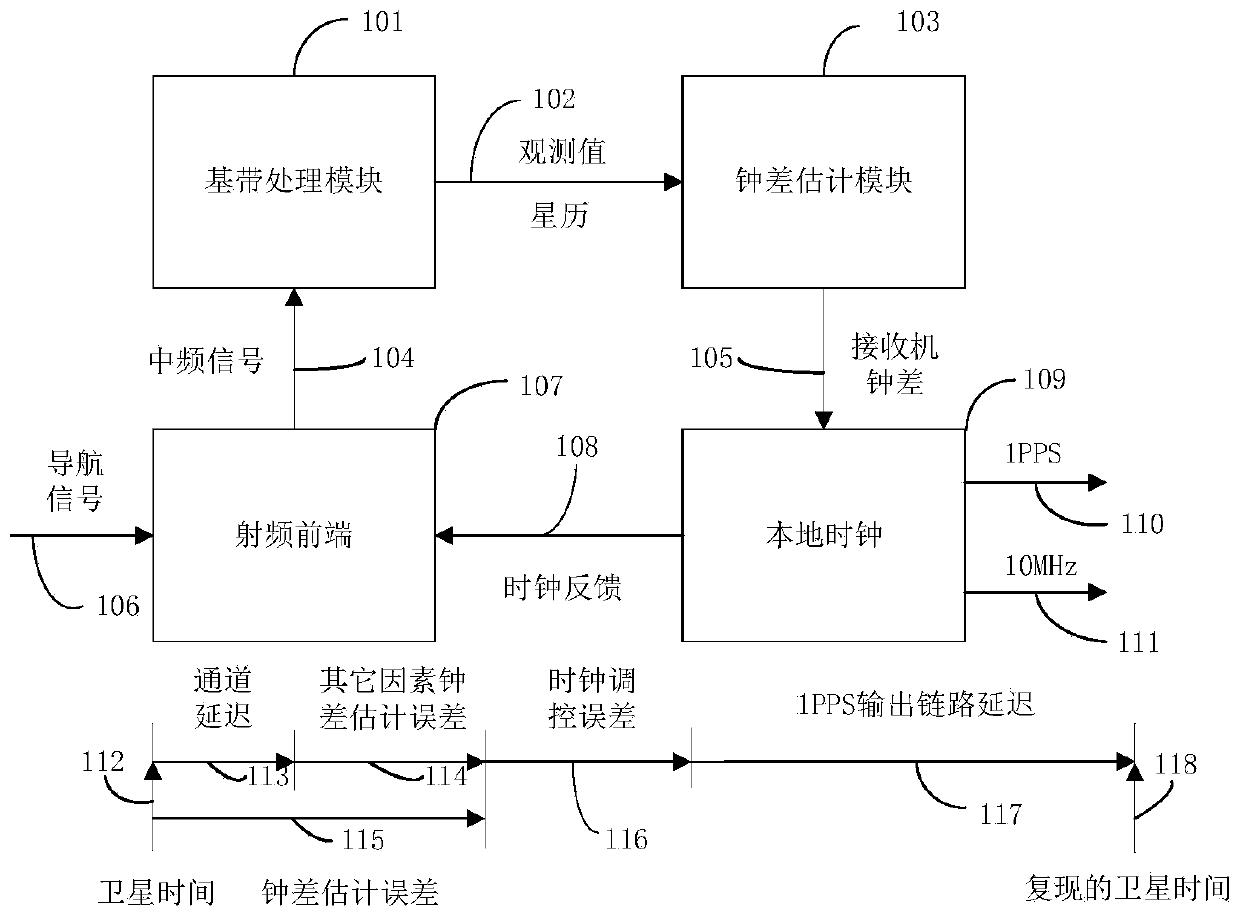

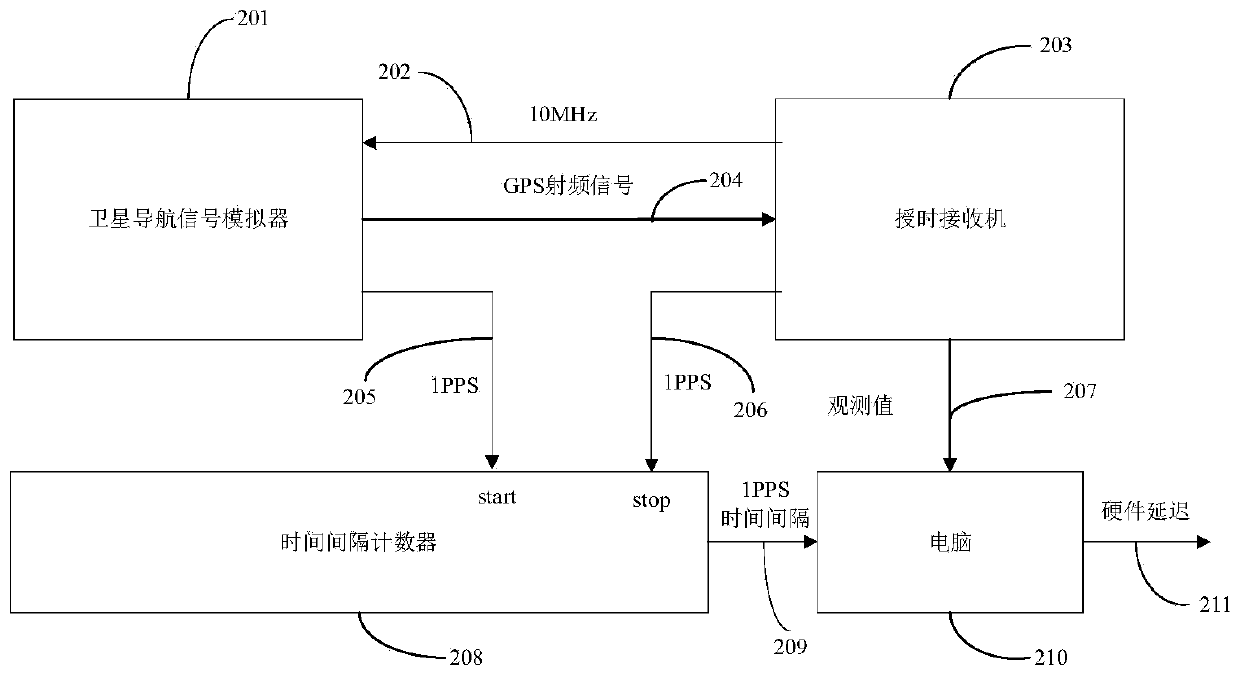

Time service receiver hardware delay calibration method and system based on clock correction compensation

ActiveCN111239775AImprove Delay Calibration AccuracyAvoid Atmospheric Error EffectsSatellite radio beaconingComputer hardwareClock correction

The invention discloses a time service receiver hardware delay calibration method and system based on clock correction compensation. The method is suitable for a time service receiver of which the observed value extraction time and the 1PPS are kept synchronous. Based on a signal processing process of the time service receiver, the invention provides a time service delay division method for emphasizing that satellite signals with different frequencies generate different hardware delays; on the basis, the invention further discloses a hardware delay measurement improvement scheme based on clockcorrection compensation; a common clock test system for a time service receiver and a satellite navigation signal simulator is built, a high-sampling-rate high-precision oscilloscope is used for measuring simulator delay of the satellite navigation simulator, a carrier phase smoothing pseudo-distance is used for distinguishing and receiving satellite signal frequency, clock difference is calculated, and therefore hardware delay calibration precision of the time service receiver is improved.

Owner:WUHAN UNIV

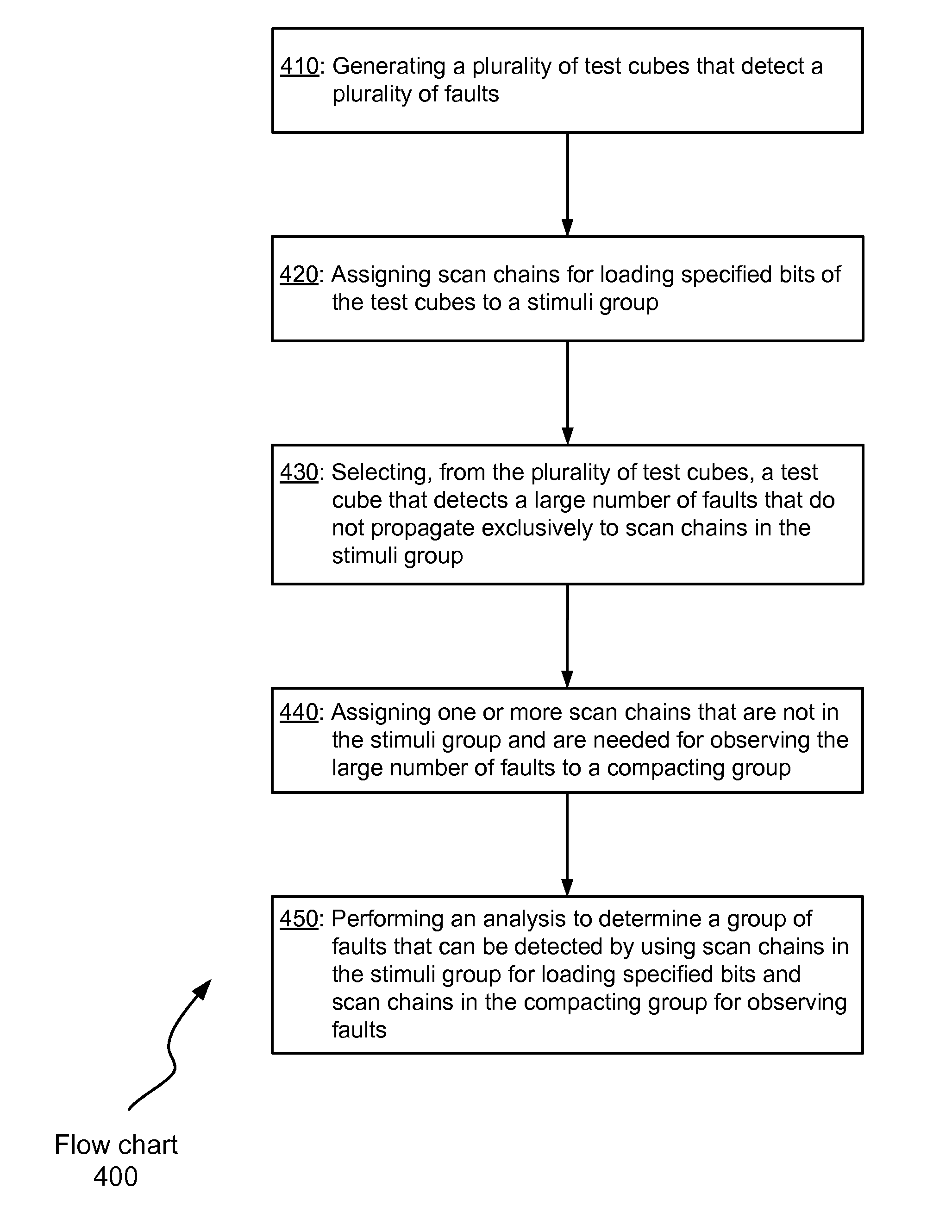

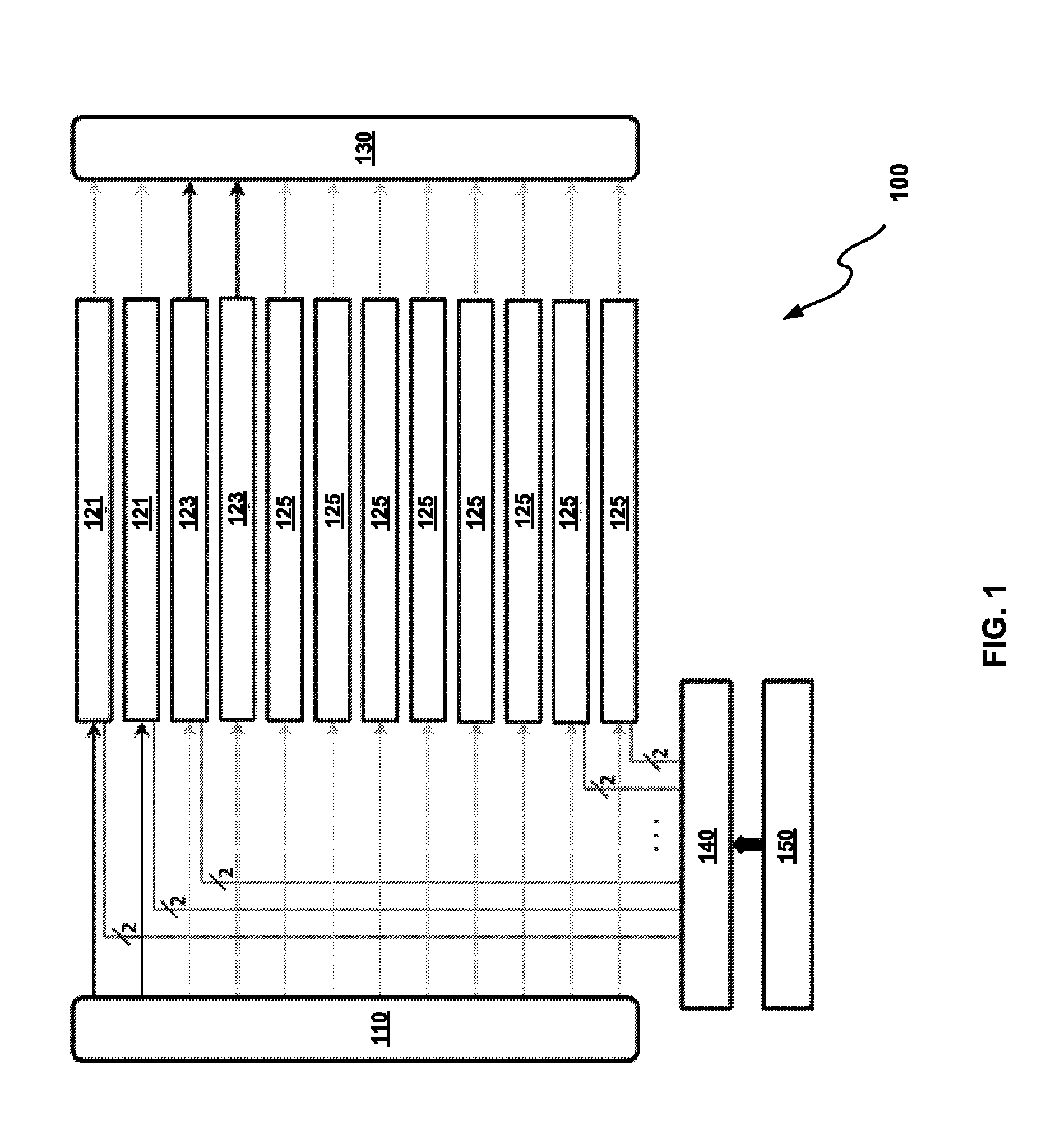

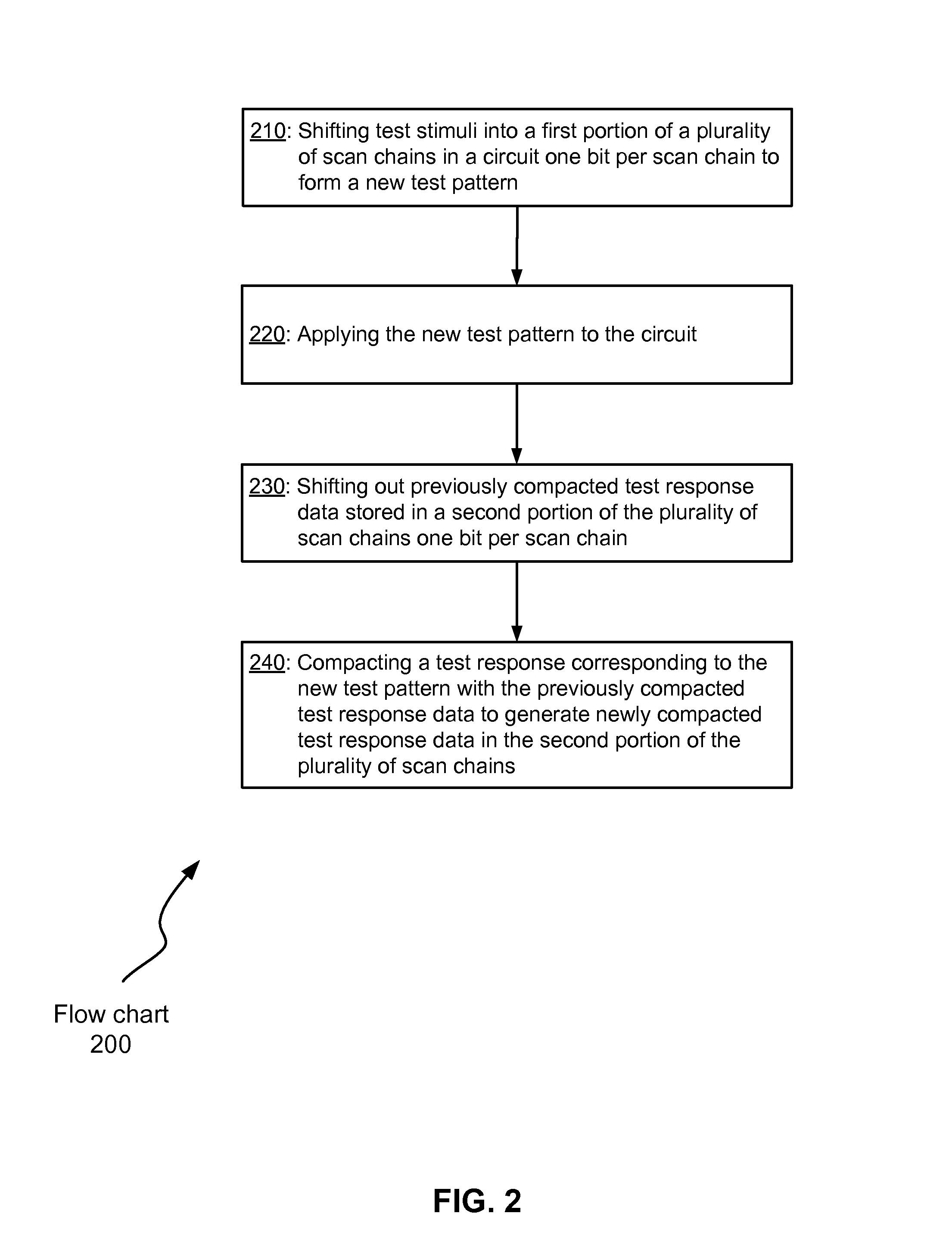

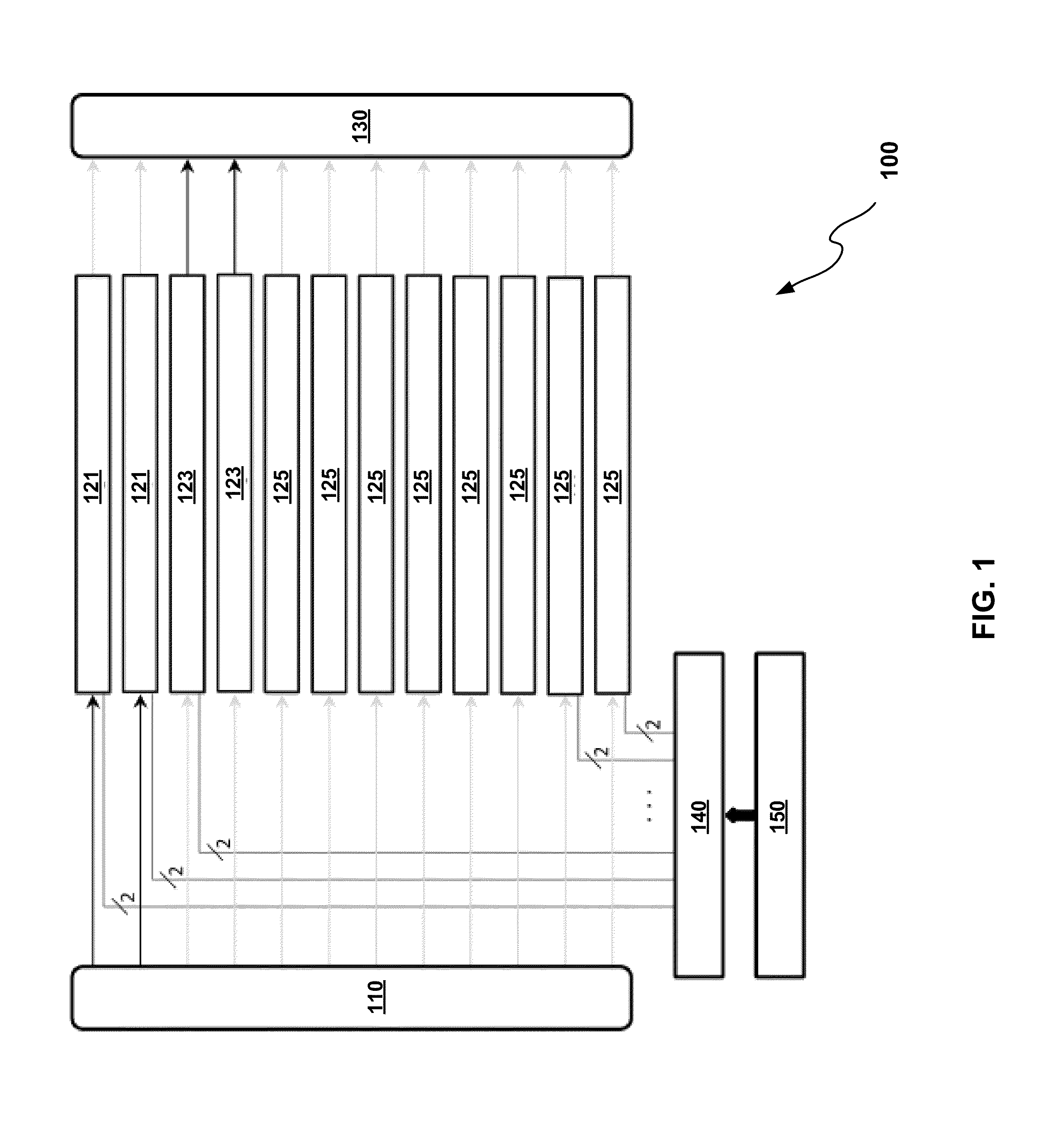

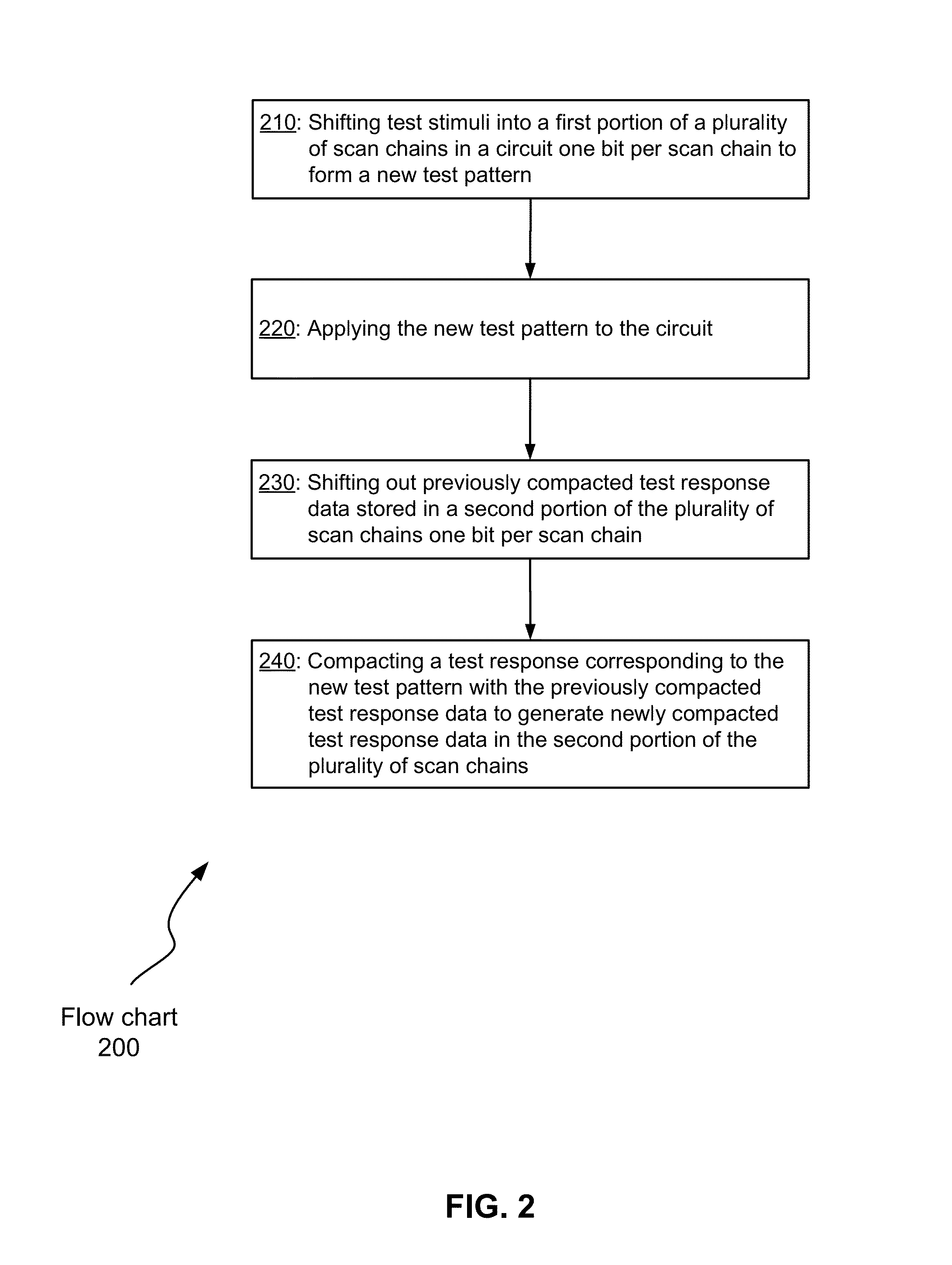

Fault-driven scan chain configuration for test-per-clock

Aspects of the invention relate to using fault-driven techniques to generate scan chain configurations for test-per-clock. A plurality of test cubes that detect a plurality of faults are first generated. Scan chains for loading specified bits of the test cubes are then assigned to a stimuli group. From the plurality of test cubes, a test cube that detects a large number of faults that do not propagate exclusively to scan chains in the stimuli group is selected. One or more scan chains that are not in the stimuli group and are needed for observing the large number of faults are assigned to a compacting group. The number of scan chains either in the compacting group or in both of the compacting group and the stimuli group may be limited to a predetermined number.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Apparatus and method for performing static timing analysis of an integrated circuit design

InactiveUS7269812B2Reduce workloadExcessive pessimismComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisComputer architecture

An apparatus and method perform static timing analysis on an integrated circuit design. Certain pessimistic assumptions regarding slack when data launch and clock test signals are on opposite edges and derived from common logic blocks are improved by allowing the designer to identify common logic blocks, to compute the difference between maximum and minimum delays in the common logic blocks, and to improve the slack using this computed difference and a correction factor, thereby accounting for excessive pessimism in the static timing analysis that results from the common logic blocks. The apparatus and method give credit for slack in common blocks automatically, thereby allowing a large number of pessimistic slack values to be automatically corrected and reducing the workload of an integrated circuit designer in addressing the timing problems in an integrated circuit design.

Owner:GOOGLE LLC

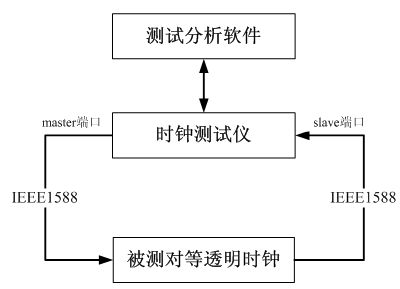

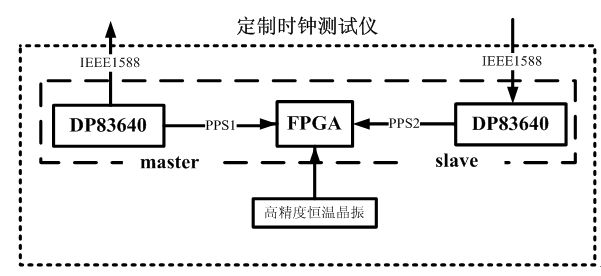

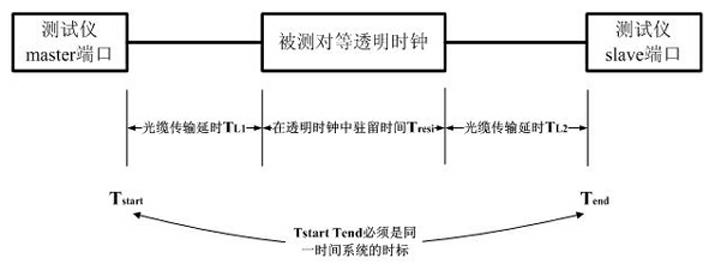

Method and system for testing error of correction field of peer-to-peer transparent clock, and clock tester

The invention relates to a method and system for testing an error of a correction field of a peer-to-peer transparent clock, and a clock tester. The system comprises the clock tester connected with the peer-to-peer transparent clock to be tested, wherein the clock tester is provided with a master clock port and a slave clock port; the master clock port and the slave clock port are connected with two ports of the peer-to-peer transparent clock to be tested respectively through two optical fibers; the master clock port is used for sending a synchronous message; the slave clock port is used for receiving the synchronous message; and the clock tester is also connected with a background computer for analyzing information acquired by the clock tester. Based on the clock tester which supports an IEEE1588-2008 protocol, the frequency modulation effectiveness of the peer-to-peer transparent clock and the correctness of the correction field calculated by the peer-to-peer transparent clock are analyzed through performing linear regression analysis and distributed analysis on a plurality of groups of test data by the background computer with statistical analysis software.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID +2

Apparatus and method for performing static timing analysis of an integrated circuit design using dummy edge modeling

InactiveUS20050183050A1Reduce workloadComputer aided designSoftware simulation/interpretation/emulationStatic timing analysisConversion factor

An apparatus and method perform static timing analysis on an integrated circuit design. Certain pessimistic assumptions regarding slack when data launch and clock test signals are on opposite edges and derived from common logic blocks are improved by creating a dummy clock edge that is on the same edge as the data launch signal, and allowing the timing tool to compute the slack improvement using its native functions. The slack improvement is then multiplied by a conversion factor, and the result is used to adjust the slack. The apparatus and method give credit for slack in common blocks automatically, thereby allowing a large number of pessimistic slack values to be automatically corrected and reducing the workload of an integrated circuit designer in addressing the timing problems in an integrated circuit design.

Owner:IBM CORP

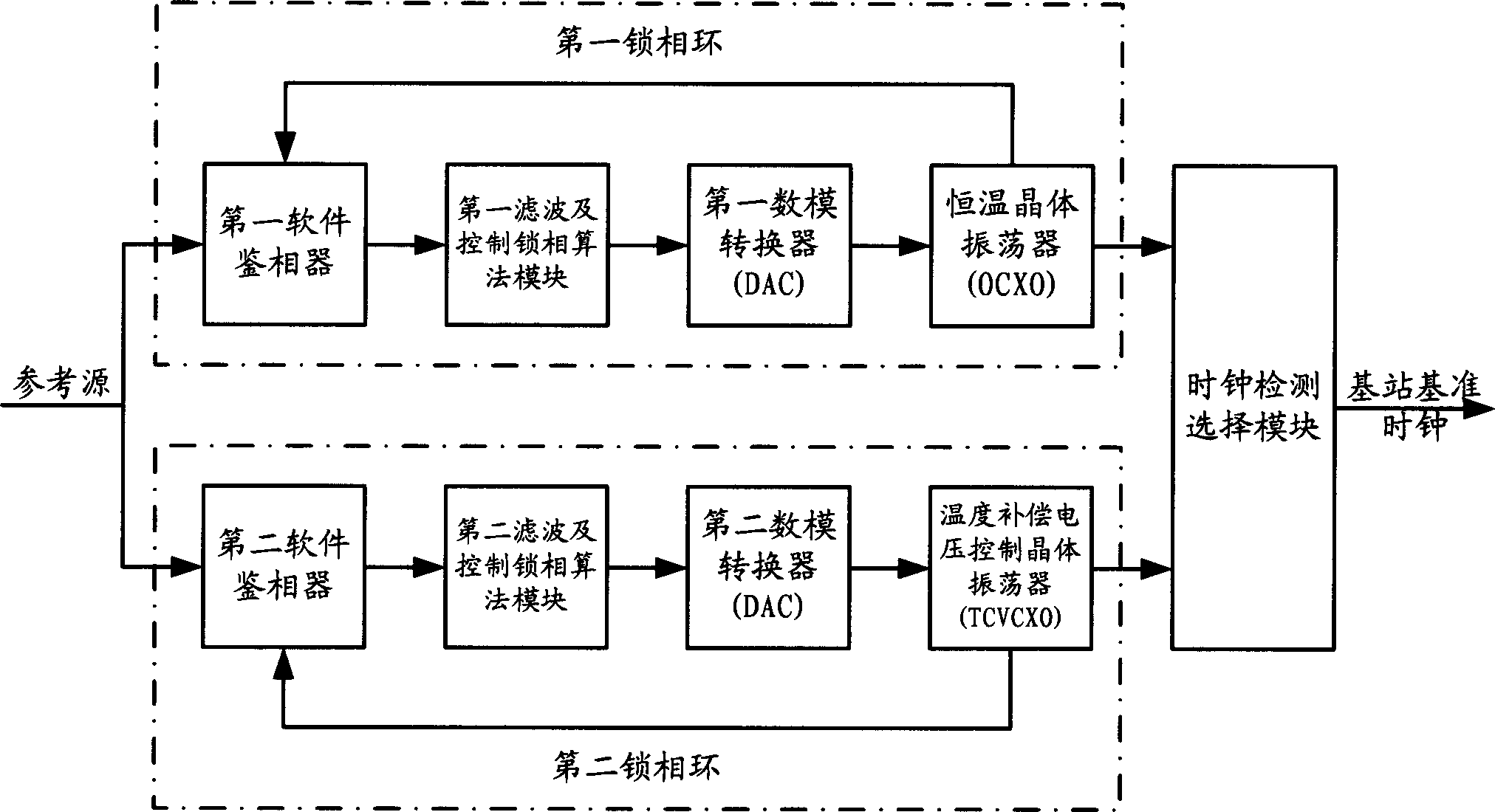

Clock back-up system in communication device

InactiveCN1859005ALow costReduce backup costsPulse automatic controlRadio/inductive link selection arrangementsSingle plateCommunication device

This invention discloses a clock bachup system in a communication device to reduce the cost for clock backup of the base stations on the basis of meeting the reliability of clocks, which takes TCVCXO as the standby clock of a communication device (base station), the primary and standby clocks are designed in two phase locking loops of a same signle board to carry out the switch by locking the loops and the reference source and clock test.

Owner:SHANGHAI HUAWEI TECH CO LTD

High-precision time synchronization method and system applied to electric energy meter

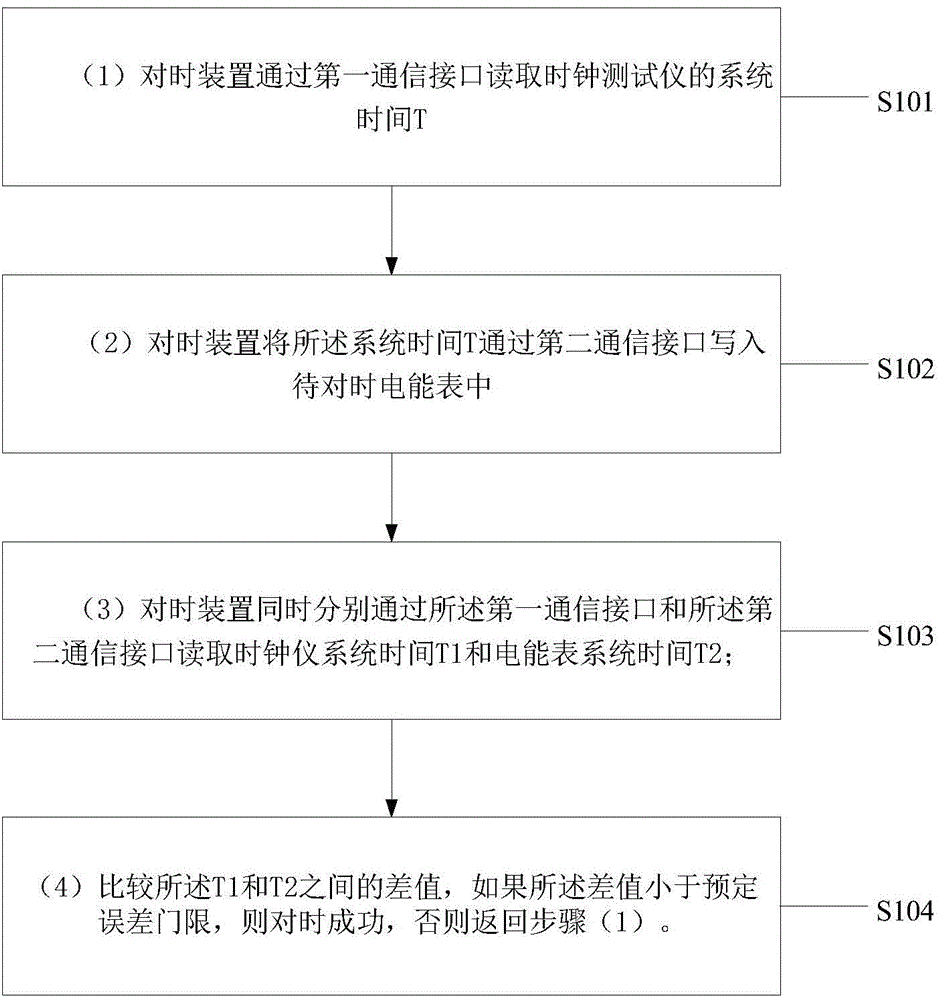

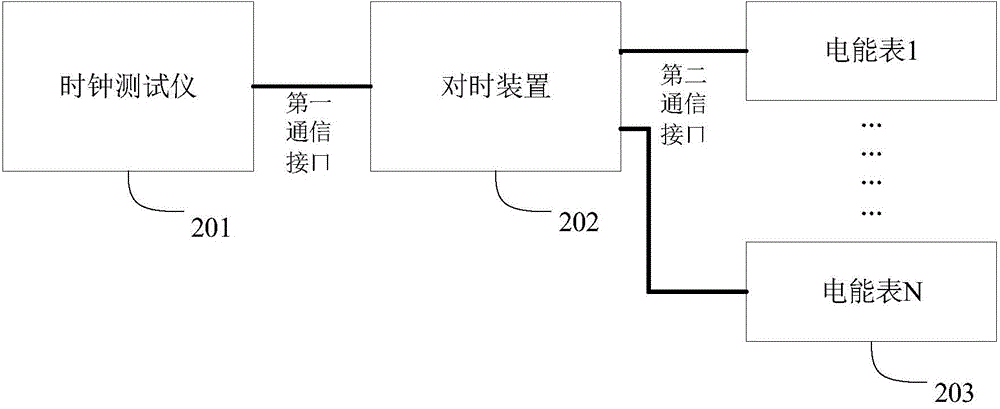

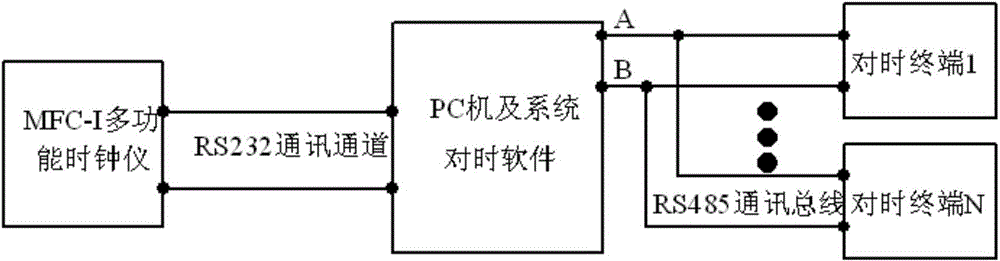

InactiveCN104483649AGuaranteed accuracyTime is stable and reliableElectrical measurementsCommunication interfaceTester device

The invention relates to a high-precision time synchronization method and system applied to an electric energy meter. The high-precision time synchronization system includes a clock tester, a timing synchronization device and an electric energy meter. The time synchronization method comprises the following steps that: (1) the timing synchronization device reads system time T of the clock tester through a first communication interface; (2) the timing synchronization device writes the system time T to an electric energy meter to be subjected to time synchronization through a second communication interface; (3) the timing synchronization device reads system time T1 of the clock tester and system time T2 of the electric energy meter respectively through the first communication interface and the second communication interface; and (4) the difference value of T1 and T2 is obtained through comparison, if the difference value is smaller than a predetermined error threshold, time synchronization is successful, otherwise, the method returns to step (1). With the high-precision time synchronization method and system can ensure the reliability of the time of a terminal system to be subjected to time synchronization and ensure the accuracy of time synchronization.

Owner:ZHUHAI ZHONGHUI MICROELECTRONICS

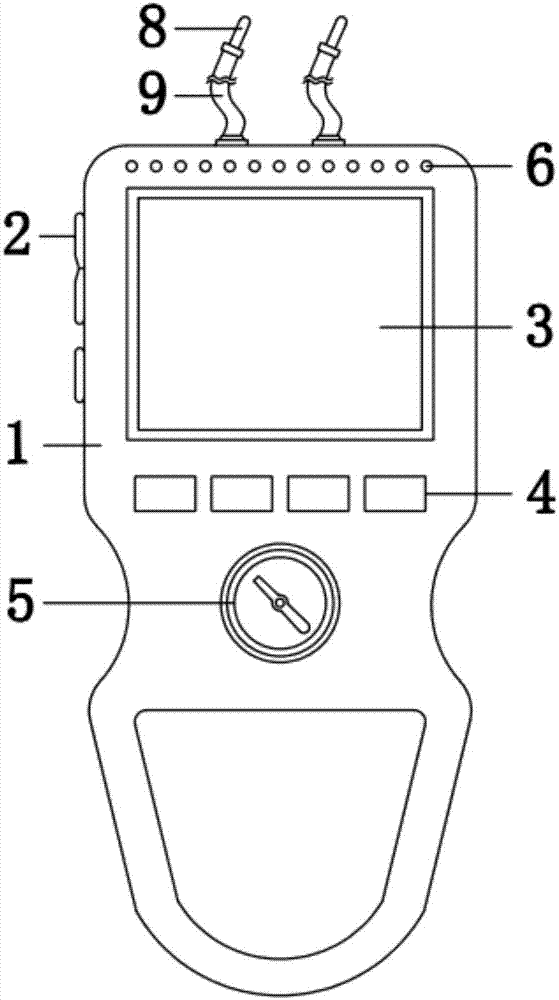

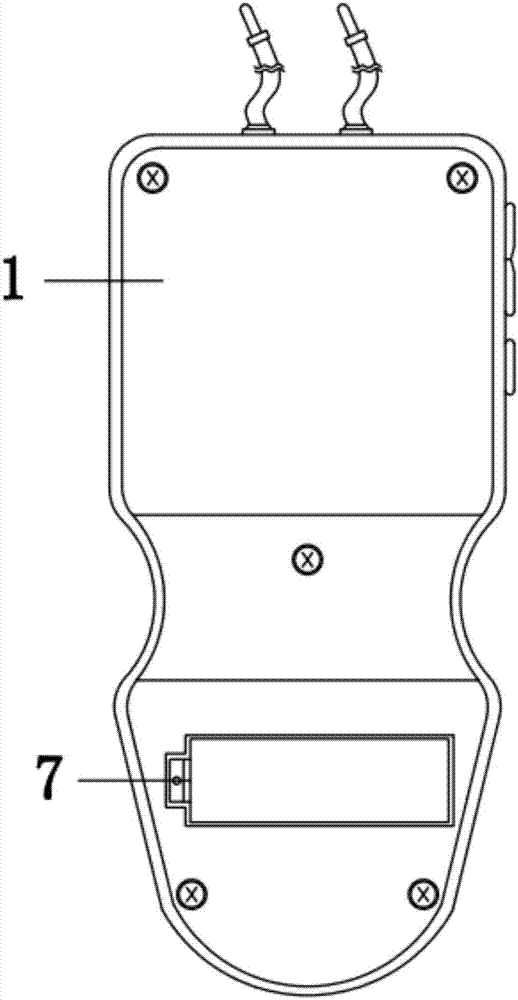

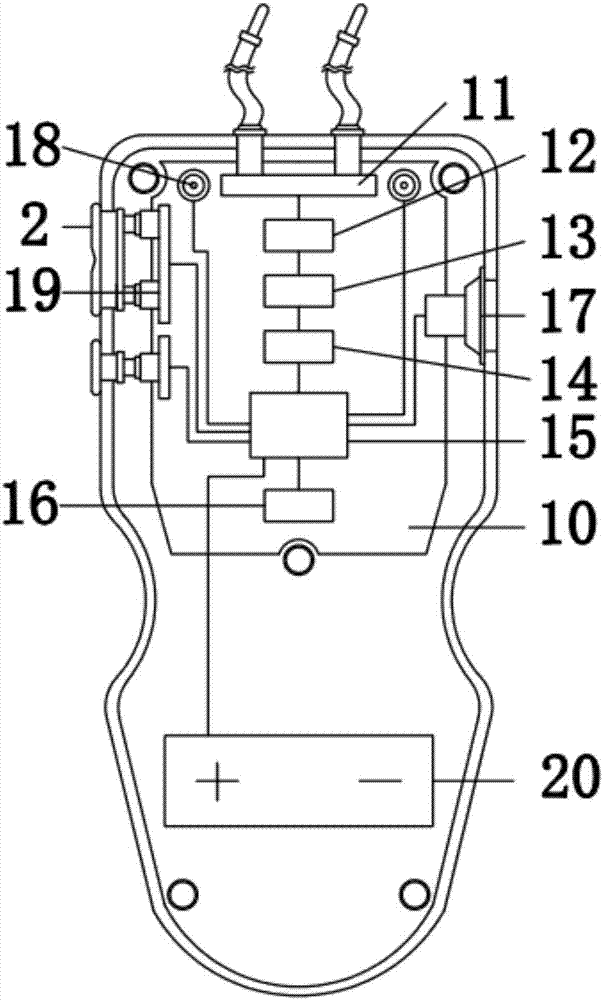

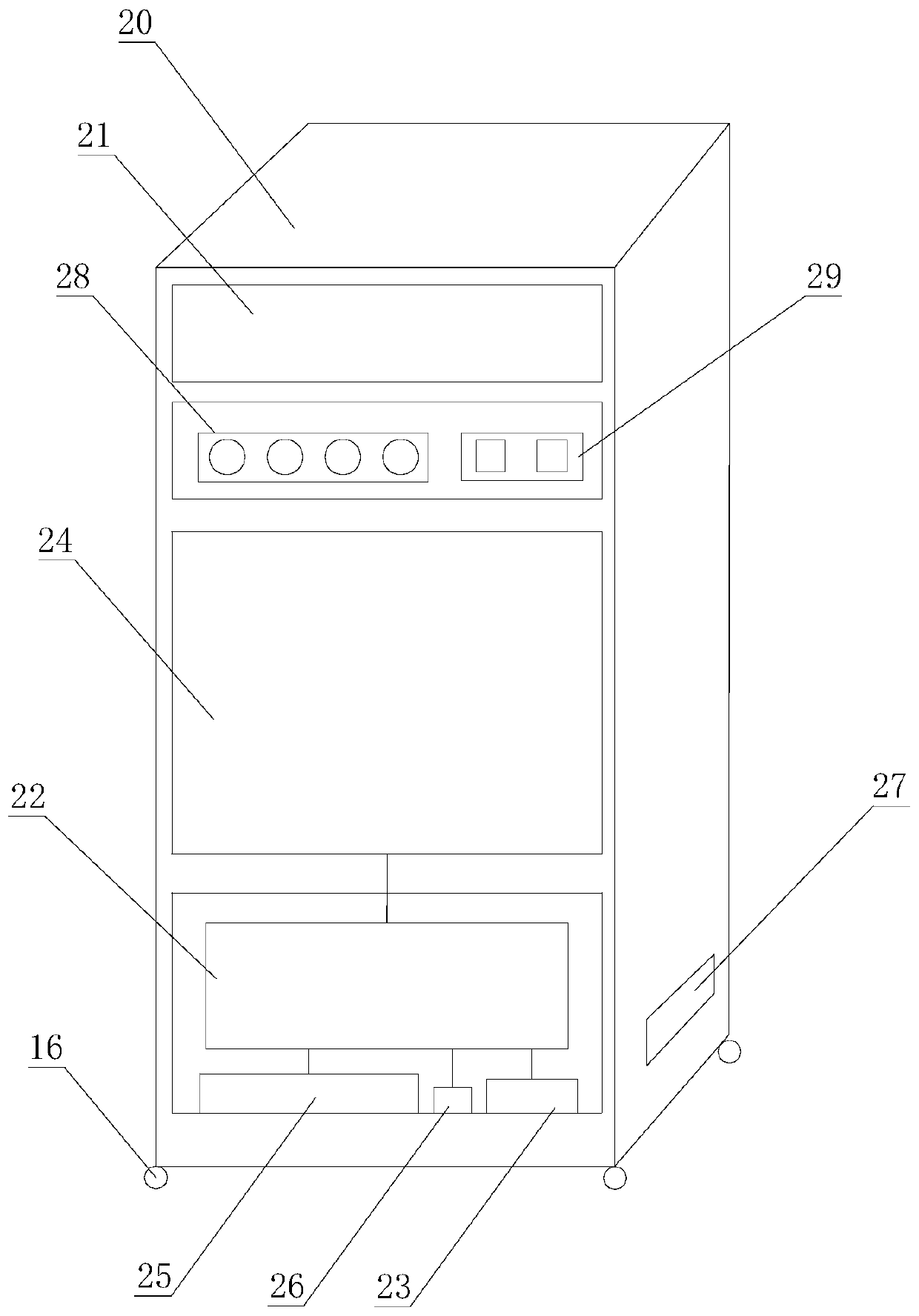

Clock intelligent tester

PendingCN107479357AAdd test functionAccurate acquisitionRegulating apparatusMode controlTester device

The invention discloses a clock intelligent tester, and belongs to the technical field of clock test. The clock intelligent tester comprises a tester shell. Volume and power buttons are inserted in the left side wall of the tester shell. A display screen is embedded in the front wall of the tester shell. Mode control buttons and a parameter adjusting knob are transversely arranged in the middle part of the front wall of the tester shell. The mode control buttons and the parameter adjusting knob are arranged at the lower part of the display screen. The mode control buttons are arranged at the upper side of the parameter adjusting knob. Sound playing holes are transversely and uniformly arranged at the top part of the front wall of the tester shell. According to the clock intelligent tester, accurate time obtained by satellite positioning acts as reference time, the measurement accuracy can be fundamentally enhanced, the current value and the voltage value in the clock can be measured through mode adjustment, the test function of the tester can be enhanced, and the test personnel are enabled to accurately acquire measurement information through simultaneous display of image display and voice play.

Owner:江苏大利邦精密制造有限公司

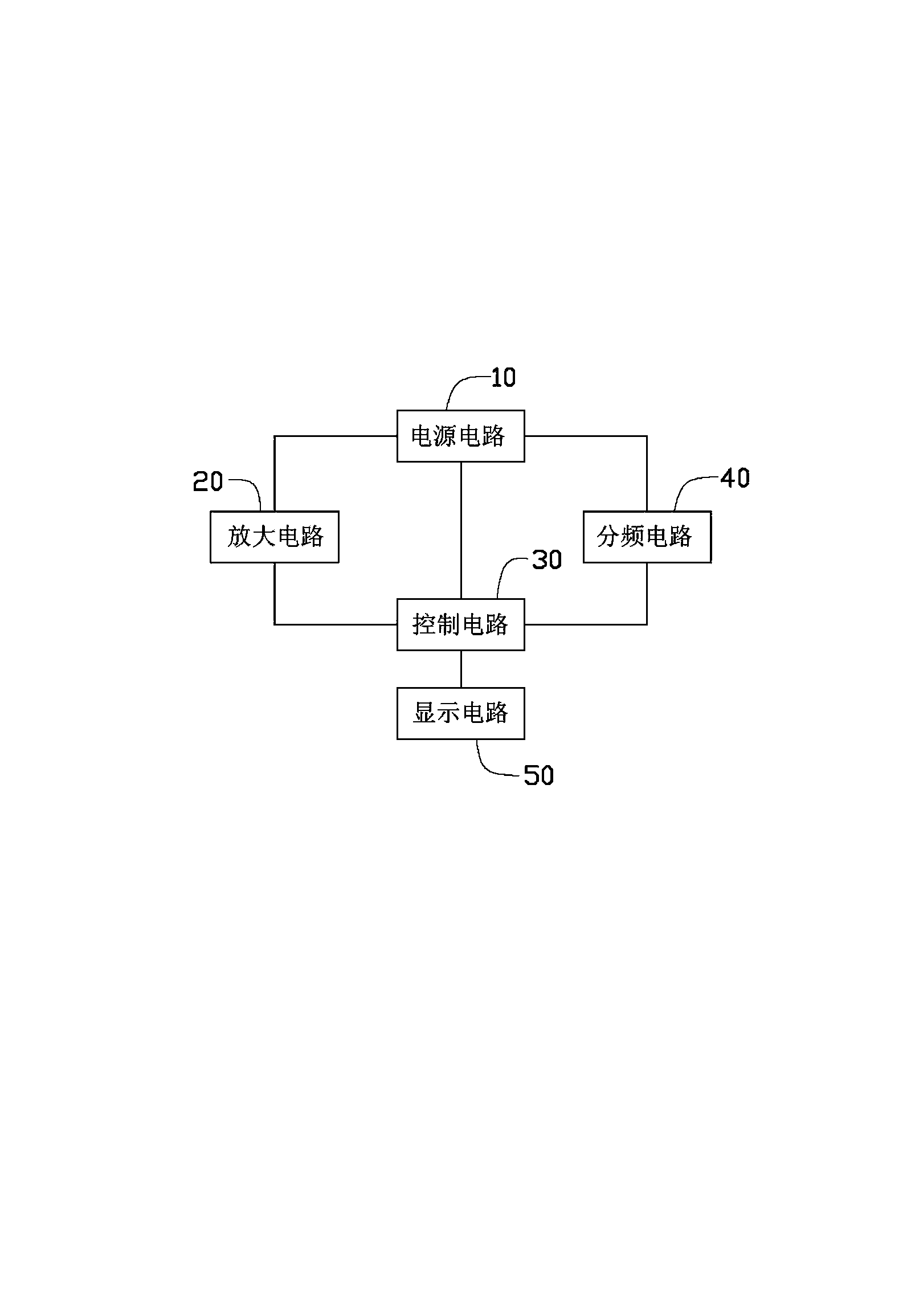

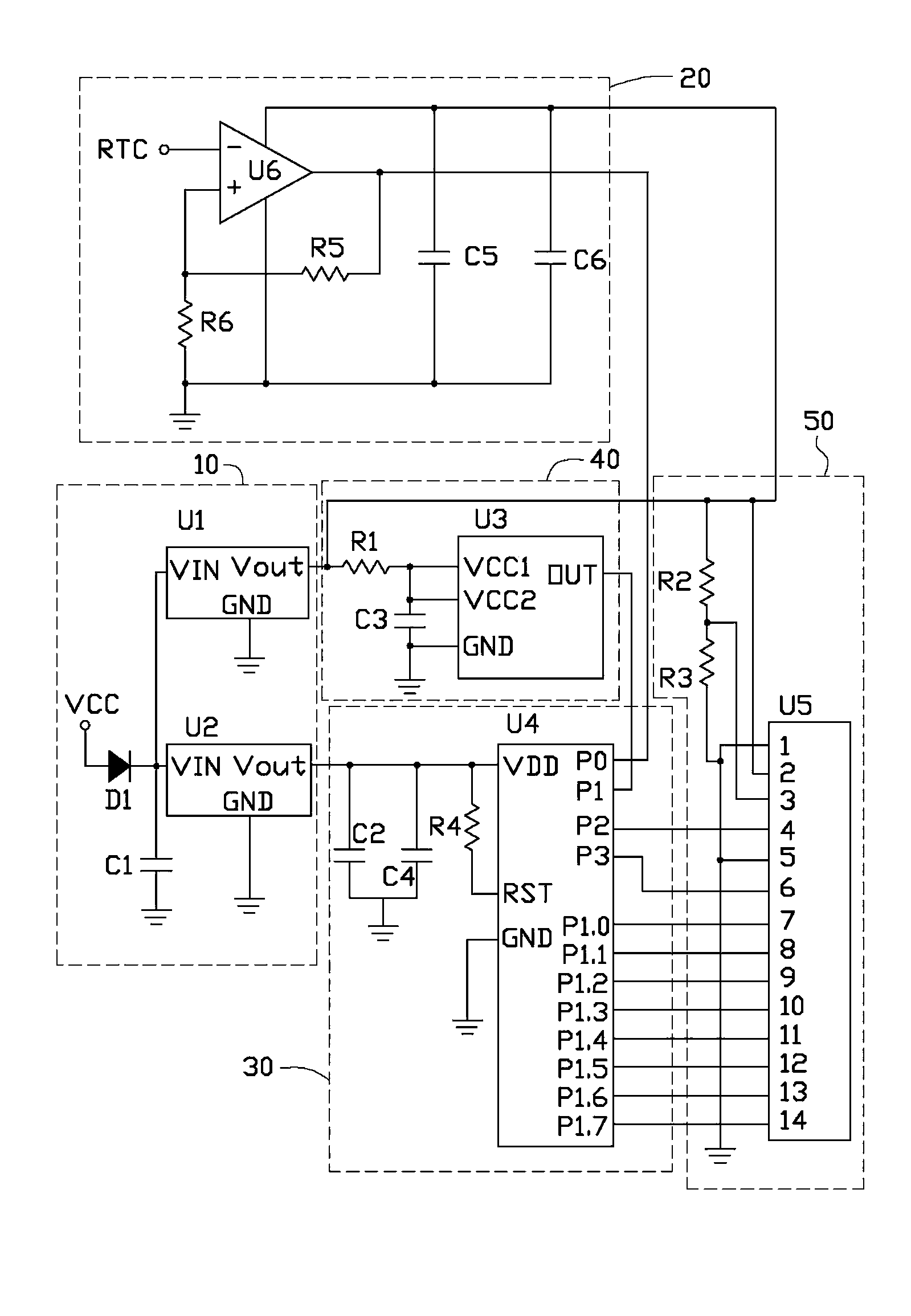

Clock test circuit

InactiveCN103529376AAvoid judgmentImprove accuracyElectronic circuit testingReal-time clockDividing circuits

A system for testing a real time clock (RTC) includes a frequency-dividing circuit configured to generate a frequency-dividing clock pulse signal equal to a rated frequency of a clock pulse signal generated by the RTC, and a control circuit including a processing chip. The processing chip includes a timer and a counter. The timer is used to record a test time of the RTC, the counter is used to record a pulse difference between the clock pulse signal and the frequency-dividing clock pulse signal during the test time. If a pulse rate difference between the counter and the timer is greater than a standard clock pulse difference, the RTC is unqualified, and if the pulse rate difference between the counter and the timer is less than the standard clock pulse difference, the RTC is qualified.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Test system and method for adjusting clock error of intelligent electric meter

PendingCN110837073AImprove detection efficiencyFast transmissionSetting time indicationElectrical measurementsComputer hardwareEmbedded system

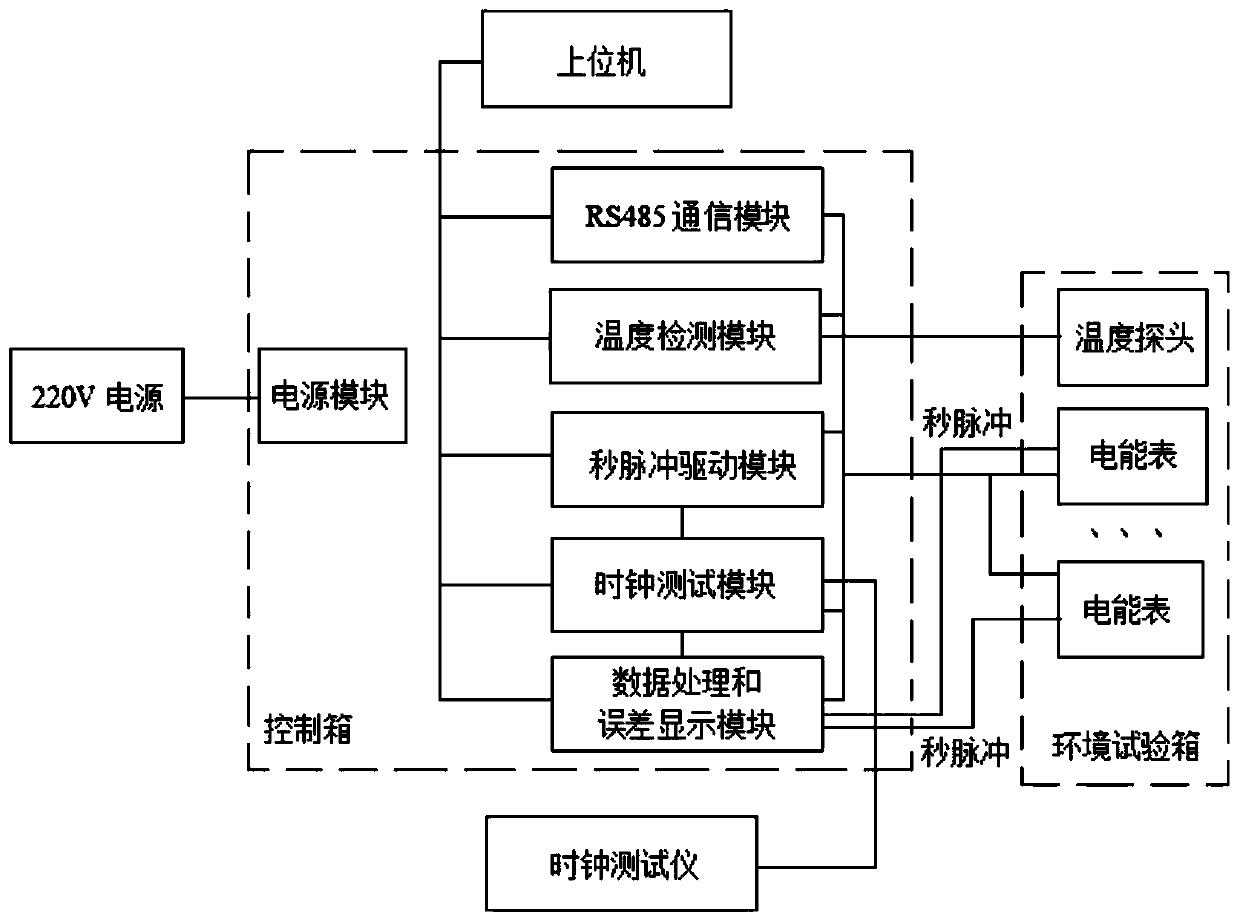

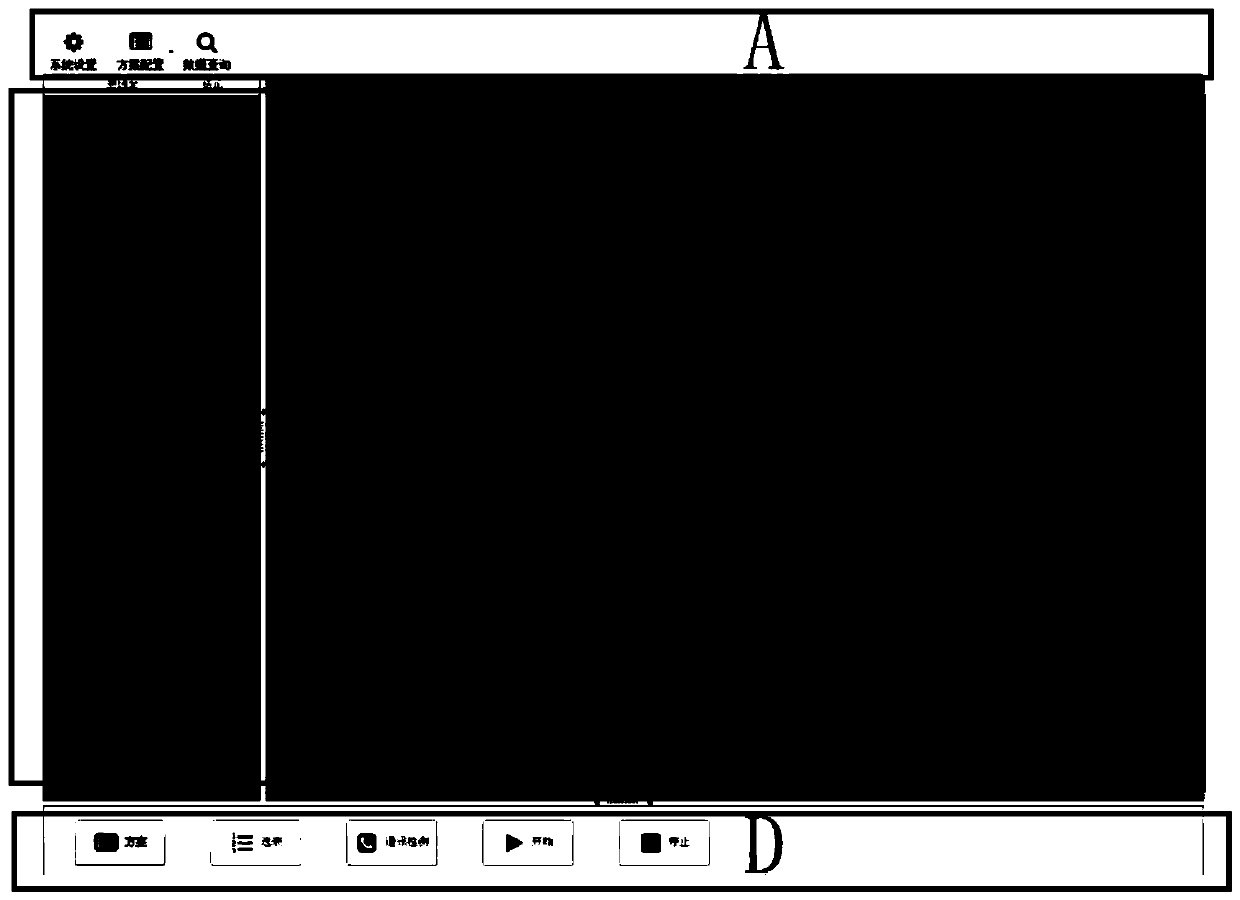

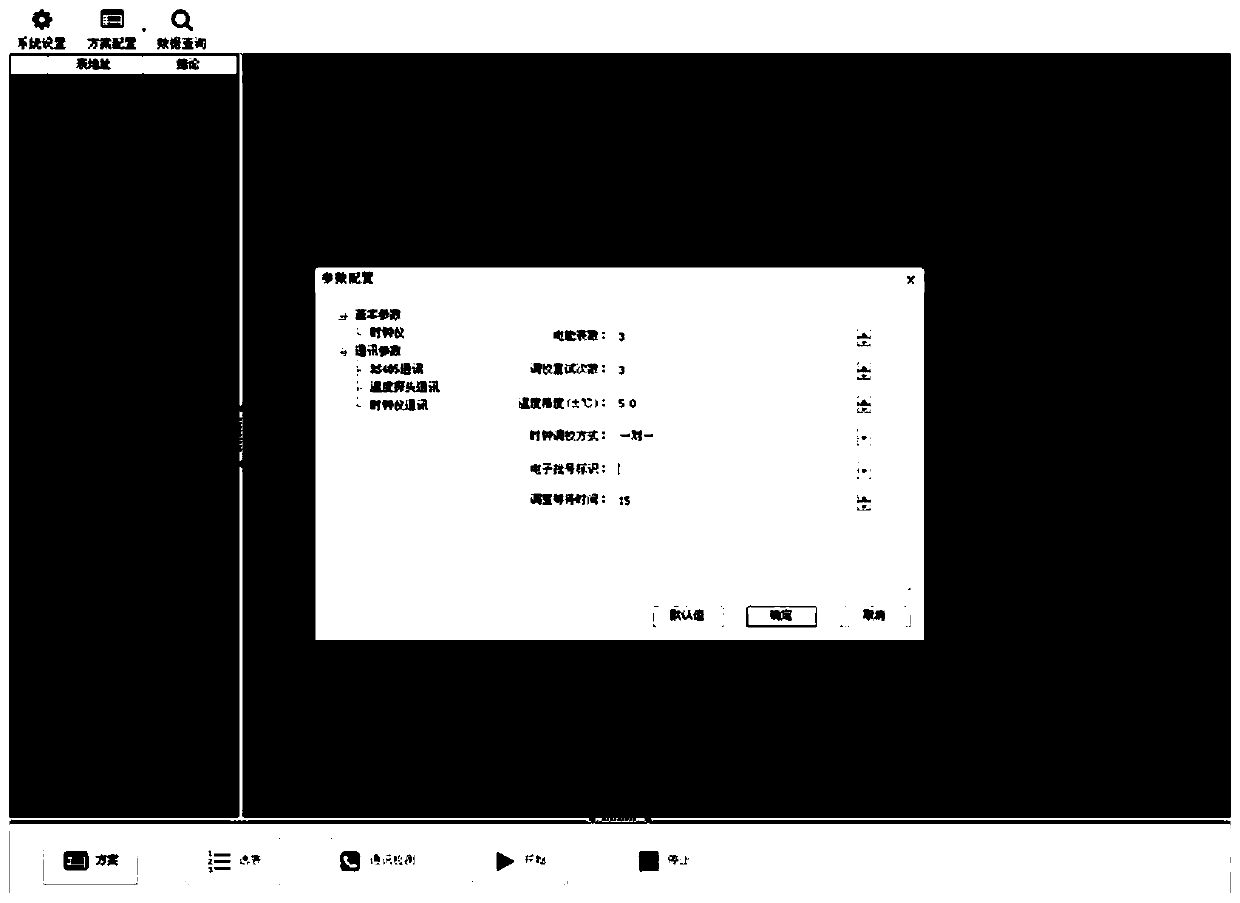

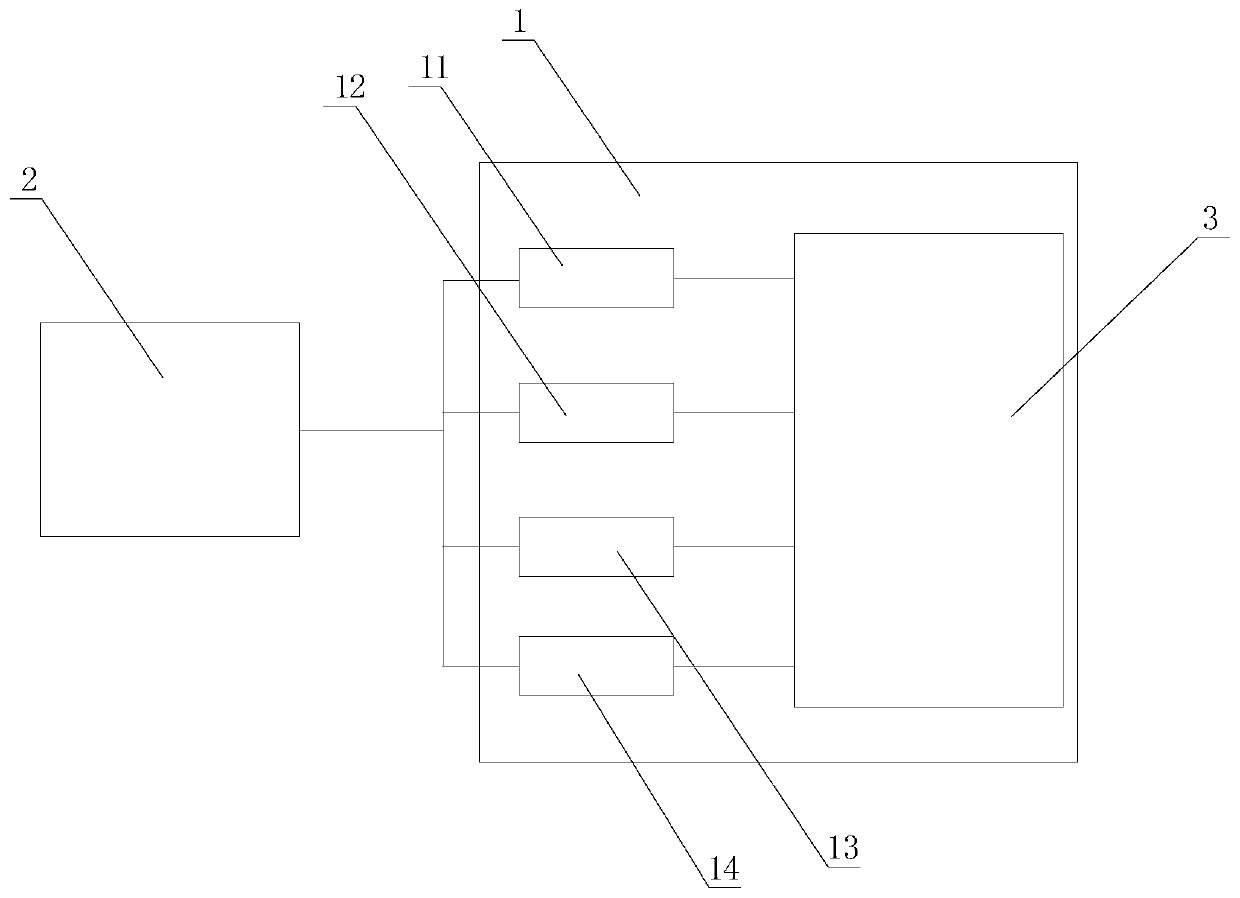

The invention discloses a test system and method for adjusting a clock error of an intelligent electric meter. According to the test system for adjusting a clock error of an intelligent electric meter, a host computer is connected with a temperature detection module, a clock test module, a second pulse drive module, and a data processing and error display module through a communication module; thetemperature detection module is configured to detect ambient temperature of the intelligent electric meter; the second pulse drive module and the clock test module are configured to connect a secondpulse output by the intelligent electric meter to the clock test module when the ambient temperature of the intelligent electric meter is detected; the clock test module is connected to the data processing and error display module, and is configured to receive the pulse output by the second pulse drive module, test the clock error, and send the test result to the data processing and error displaymodule; and the data processing and error display module is configured to receive the test result of the clock error sent by the clock test module, and display the test result through the host computer.

Owner:HENGYE ELECTRONICS JIAXING CITY

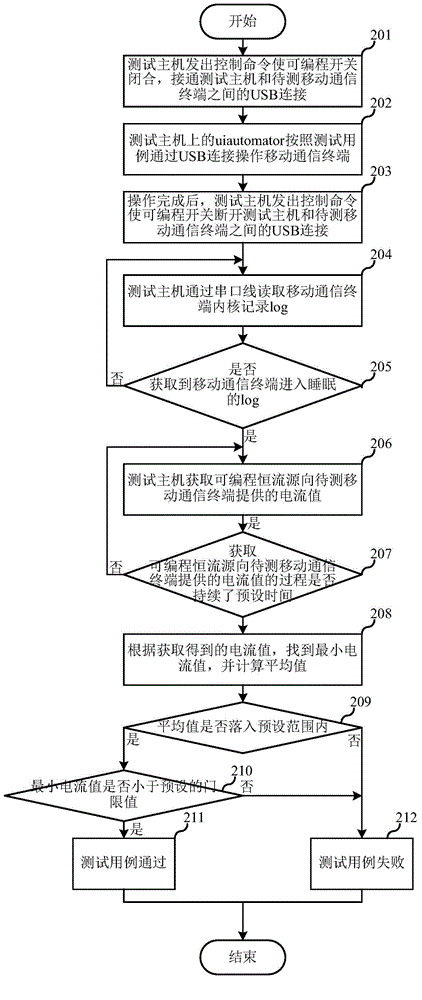

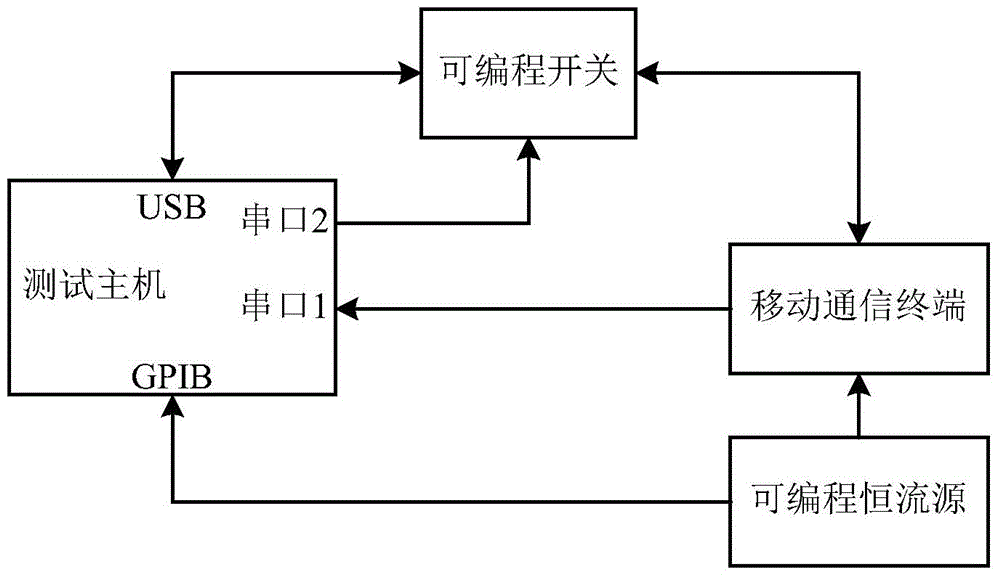

Slow clock test method for mobile communication terminal and test system thereof

ActiveCN104486779AHigh precisionImprove work efficiencySubstation equipmentWireless communicationComputer terminalUSB

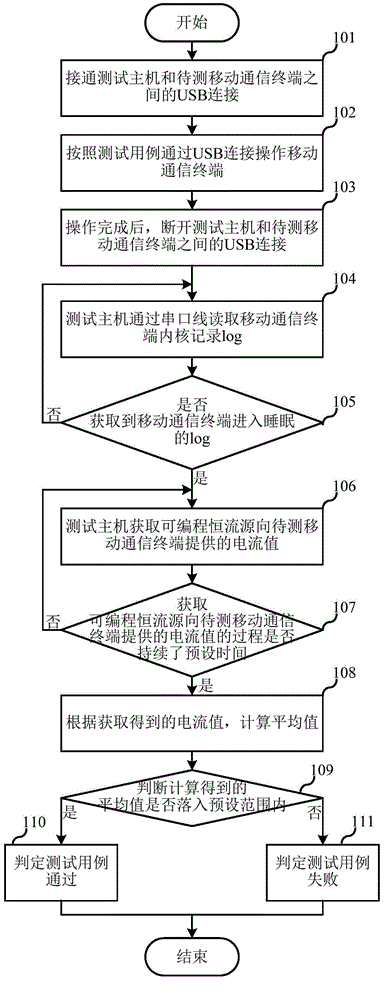

The invention relates to the field of the mobile communication terminal, and discloses a slow clock test method for a mobile communication terminal and a test system of the slow clock test method. The slow clock test method comprises the following steps that in a period that USB (universal serial bus) connection between a test host and the mobile communication terminal is switched on, the test host is used for operating the mobile communication terminal through the USB connection according to a test case; after the USB connection between the test host and a mobile communication terminal to be tested is cut off, the test host is used for judging whether the mobile communication terminal to be tested enters a sleep mode or not; after the mobile communication terminal to be tested enters the sleep mode, a current value provided for the mobile communication terminal to be tested from a programmable constant current supply is obtained, and a slow clock test result of the mobile communication terminal is judged according to the obtained current value. Due to the fact that the current value provided for the mobile communication terminal to be tested from the programmable constant current supply is read in the test, current test precision can be improved. Due to the fact that the mobile communication terminal is operated by the test host via the USB connection, working efficiency is improved.

Owner:SHENYANG CHENXUN SIMCOM TECH

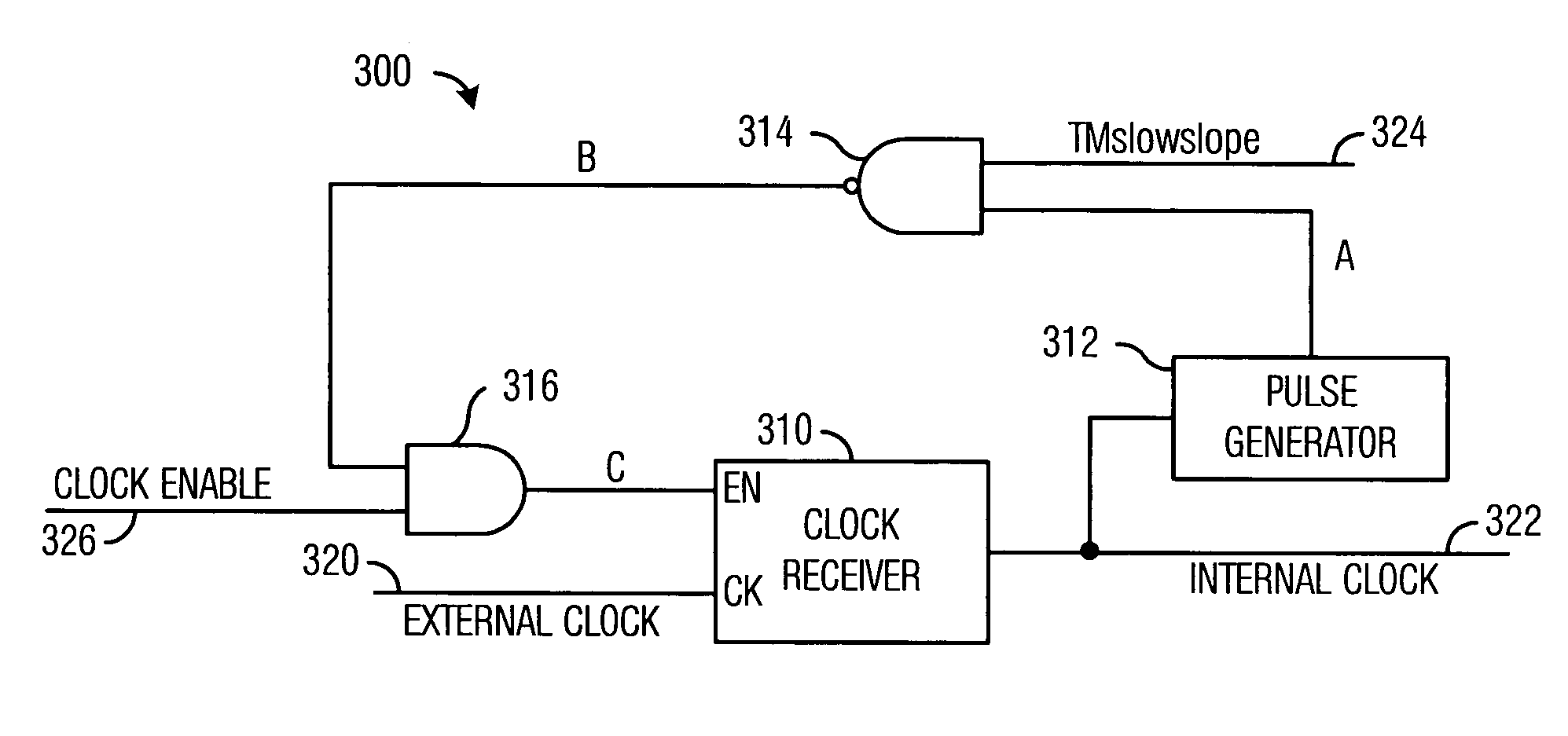

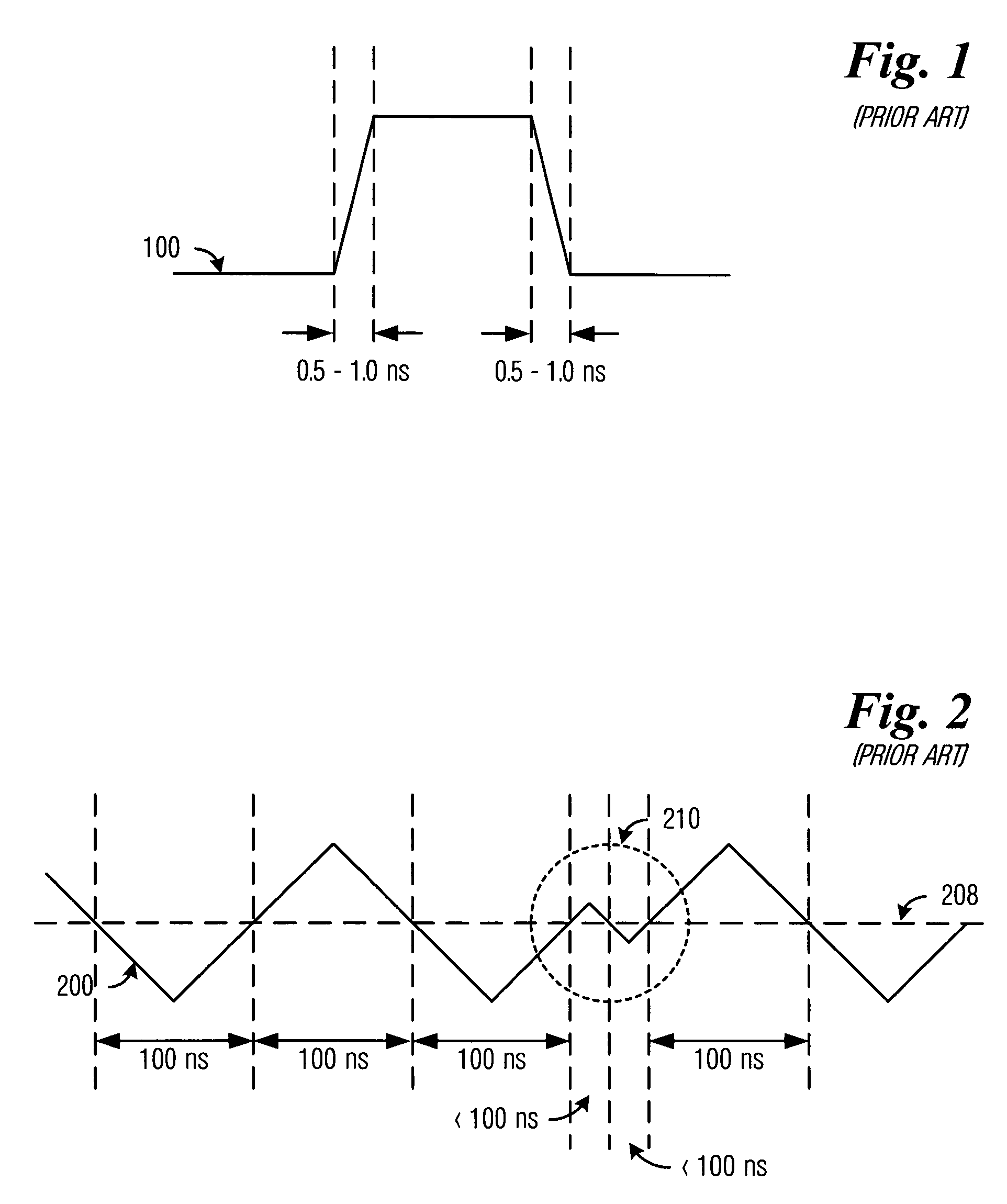

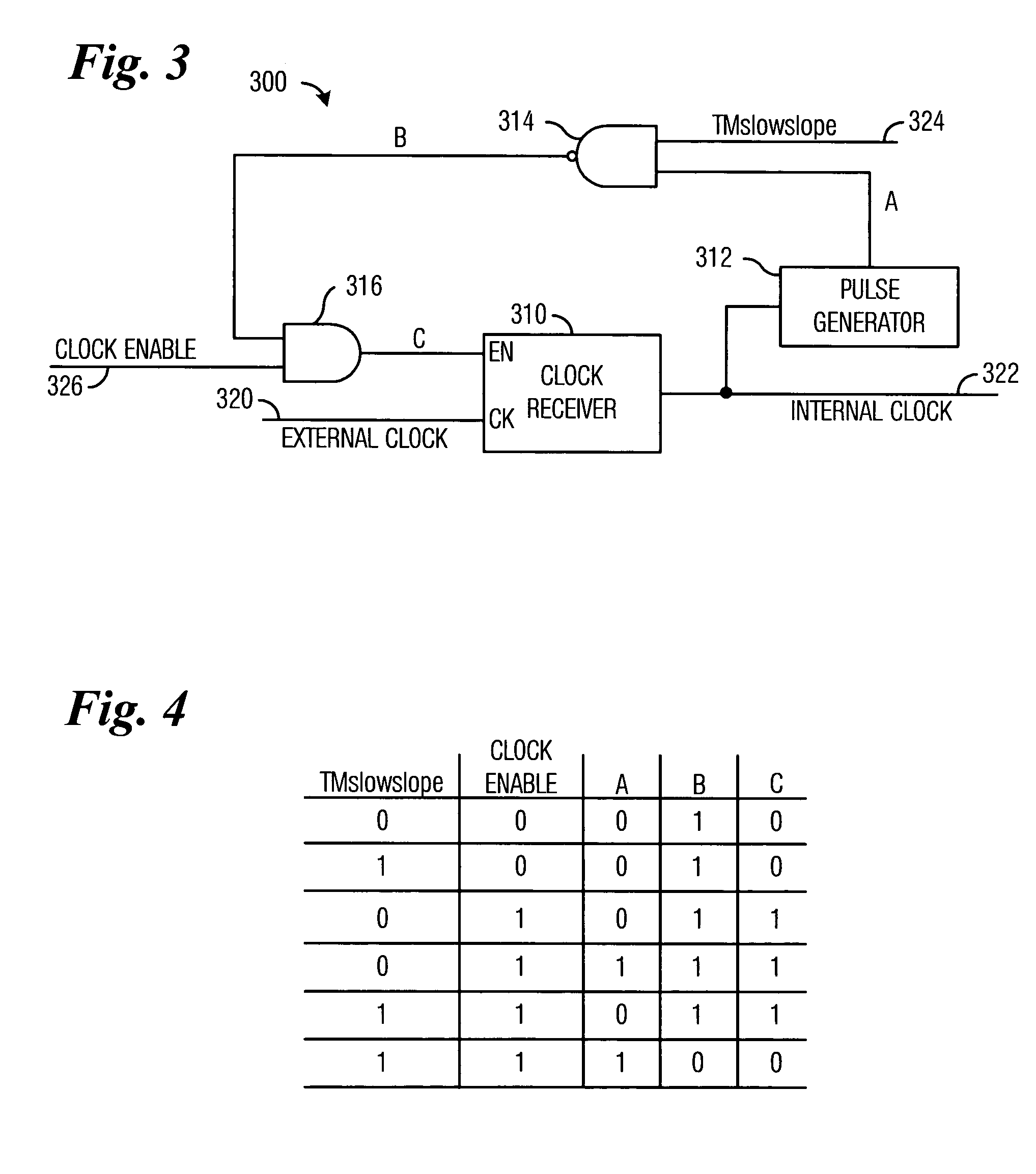

Noisy clock test method and apparatus

InactiveUS7293190B2Generating/distributing signalsPulse manipulationClock transitionComputer science

A clock filter for use in filtering an external clock signal to create an internal clock signal for use by an electronic device is provided. The clock filter receives the external clock signal and sets the internal clock signal high when the external clock signal is above a first threshold and sets the internal clock signal low when the external clock signal is below a second threshold. The clock filter holds the internal clock signal constant for a period of time after the clock transitions.

Owner:POLARIS INNOVATIONS LTD

Clock signal detection method and apparatus in electronic devices

ActiveCN1333529CSimple designImprove reliabilityPulse techniqueSynchronising arrangementClock TestElectron

Owner:DATANG MOBILE COMM EQUIP CO LTD

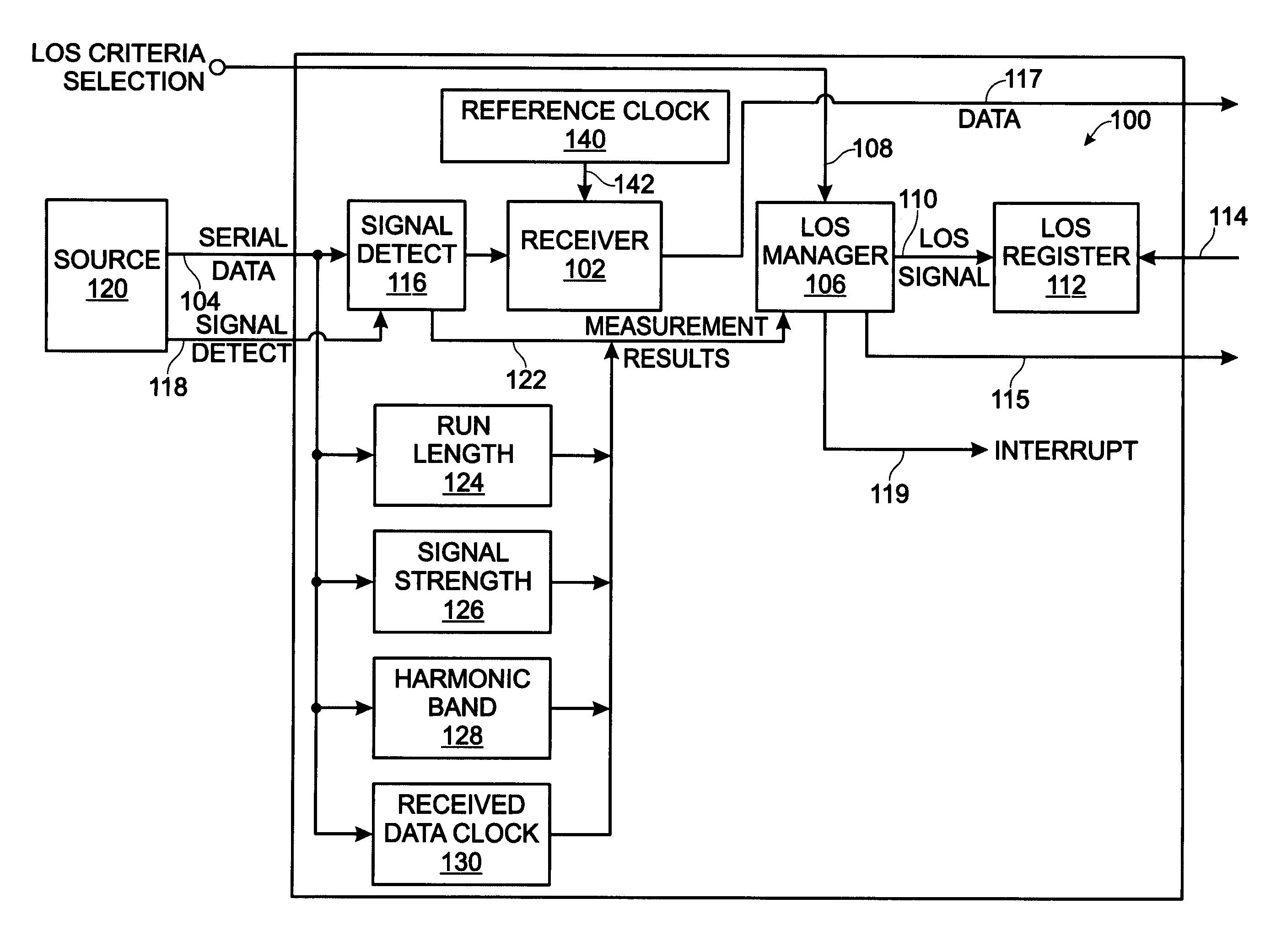

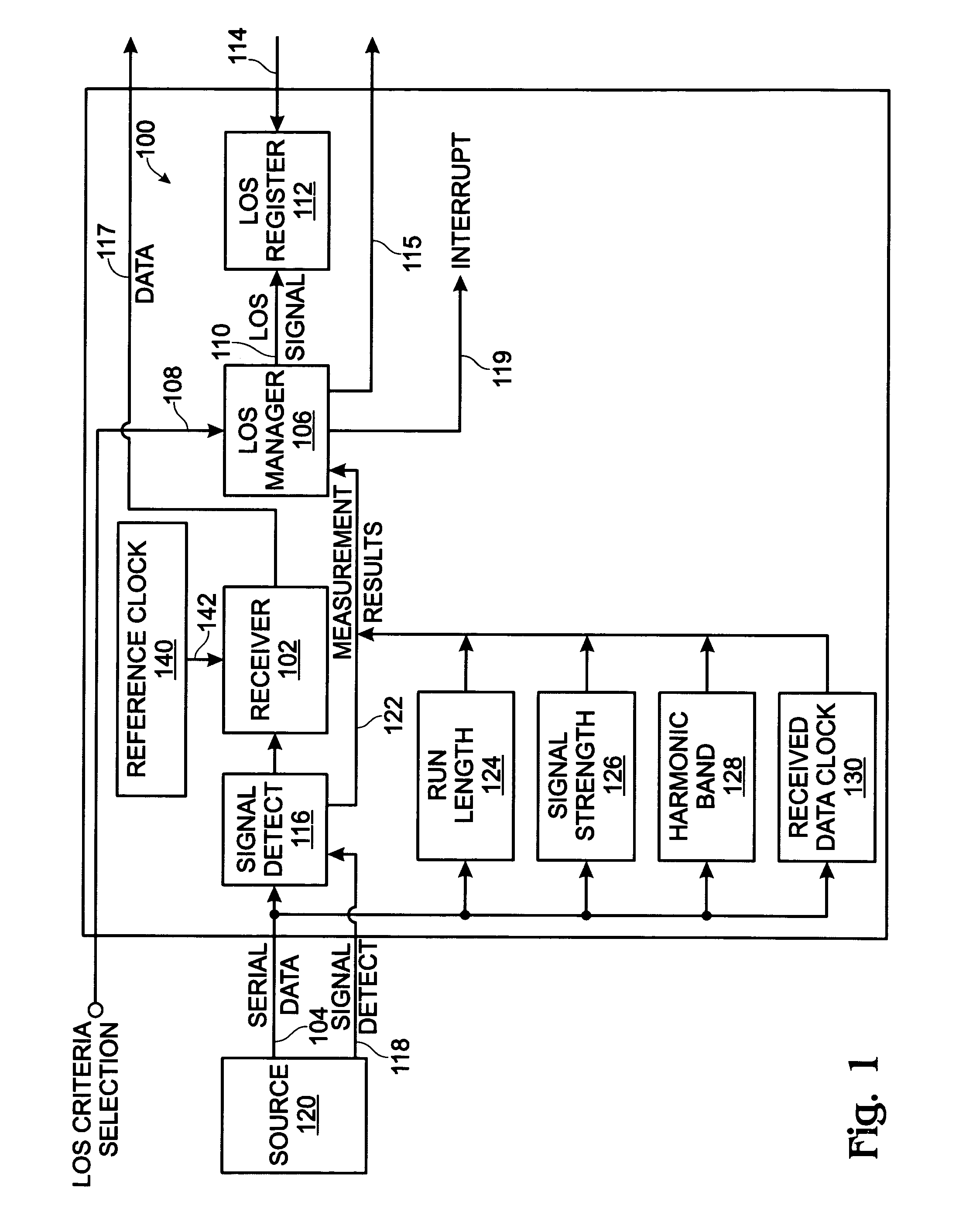

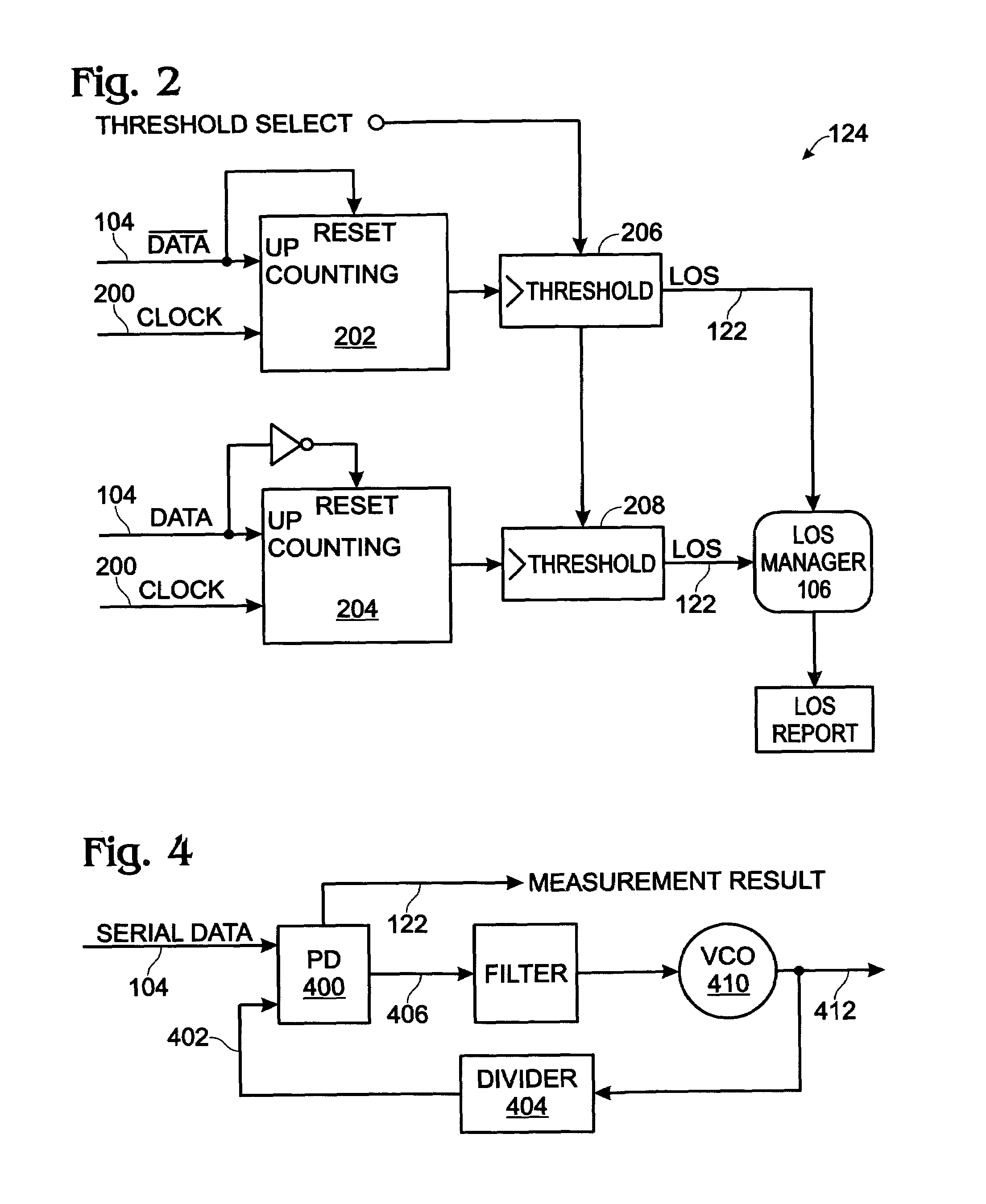

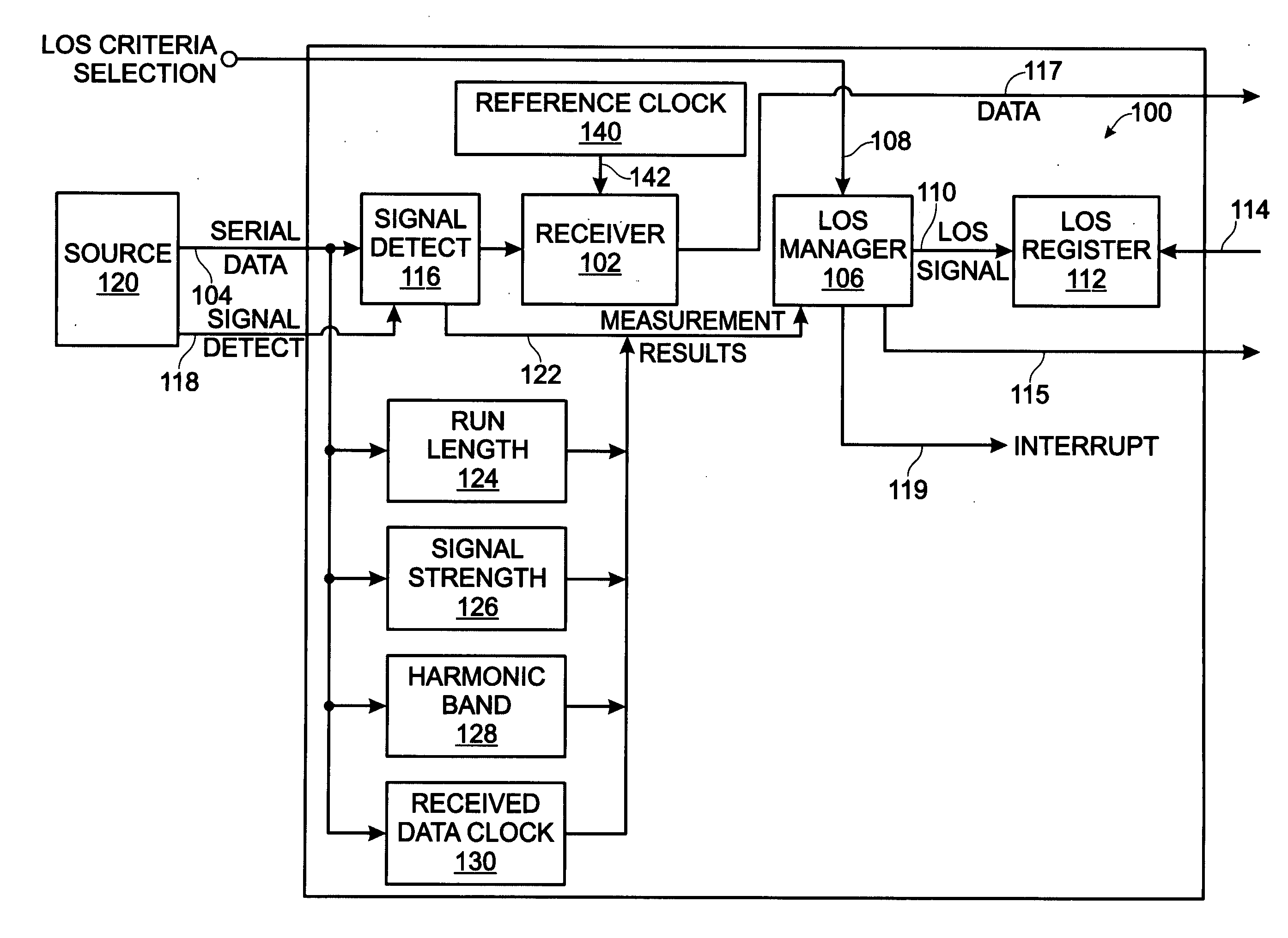

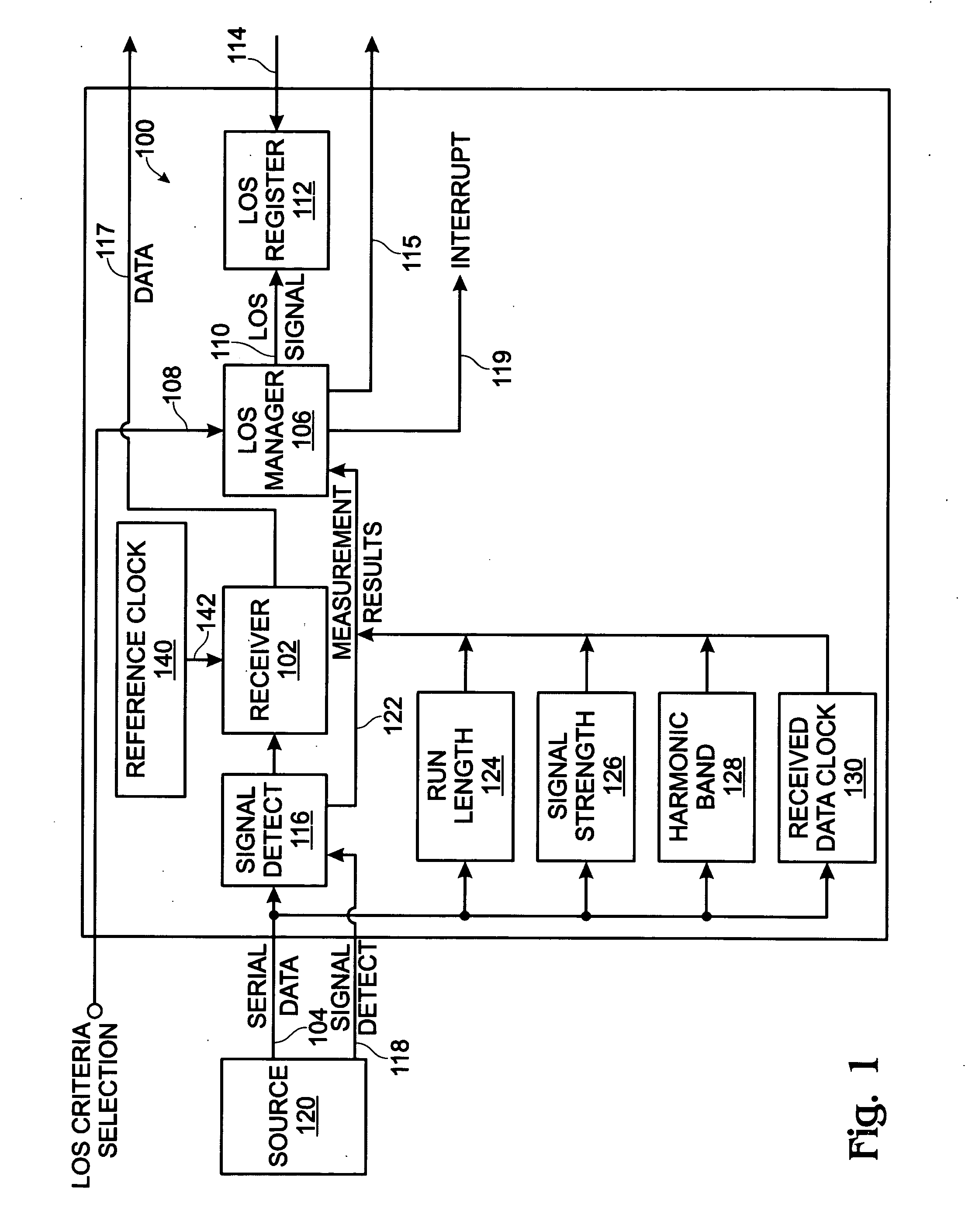

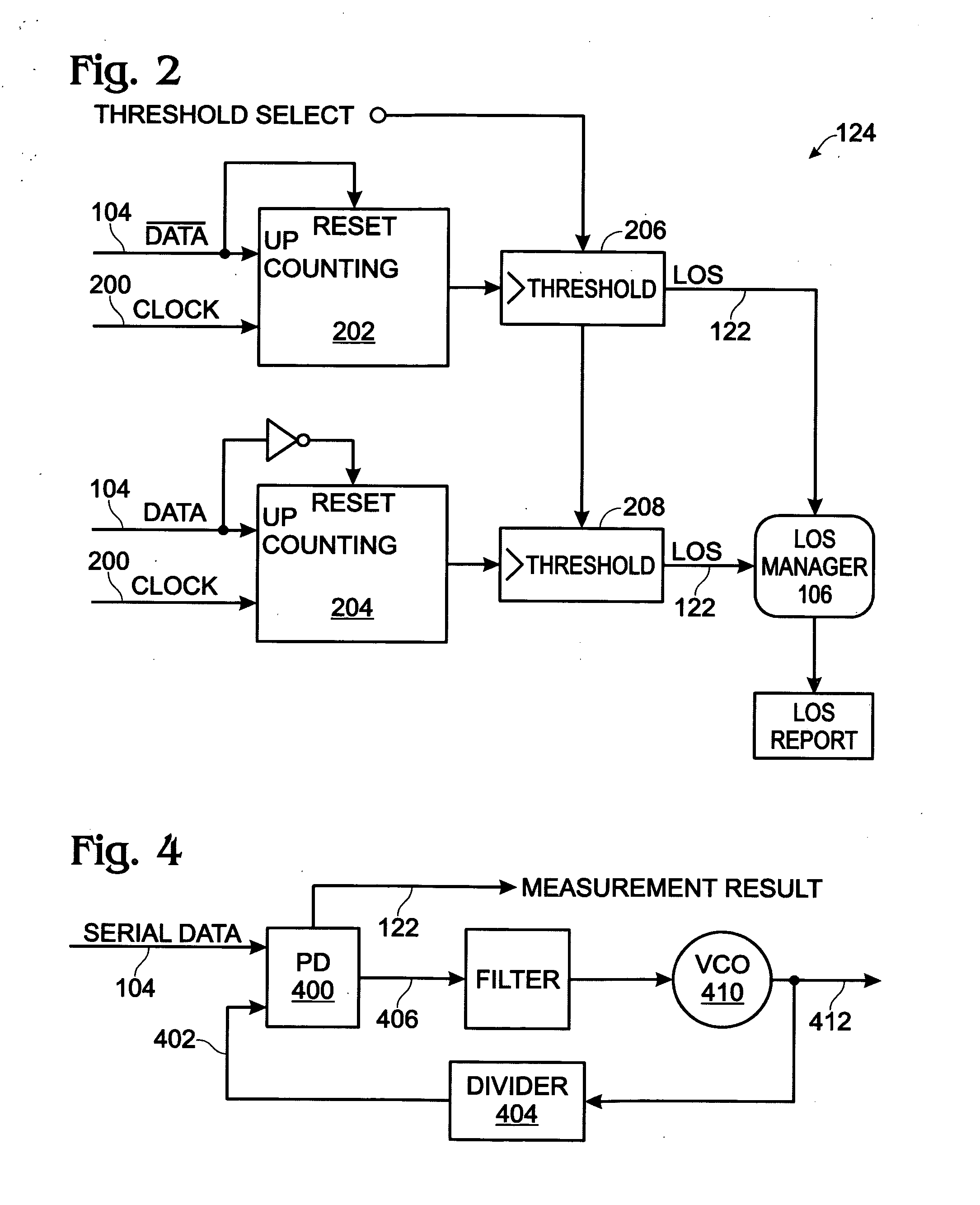

Selectable loss of signal (LOS) criteria

ActiveUS7633878B2Error detection/prevention using signal quality detectorTransmission systemsVoltage amplitudeDigital data

A system and method are provided for selecting loss of signal (LOS) criteria in a serial communications receiver. The method receives a serial stream of digital data and selects LOS criteria. The serial stream of digital data is compared to the selected LOS criteria. In response to the serial stream of digital data failing to meet the selected LOS criteria, a LOS signal is generated. Some examples of the LOS criteria that might be selected include: a “signal detect” signal received from the source transmitting the serial stream of digital data, a run length test, a signal strength (voltage amplitude) test, harmonic band detection test, and a received data clock test. In one aspect, selecting LOS criteria includes selecting combinations of the above-mentioned LOS criteria, so that the LOS signal is generated in response to failing to meet the combination of selected LOS criteria.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

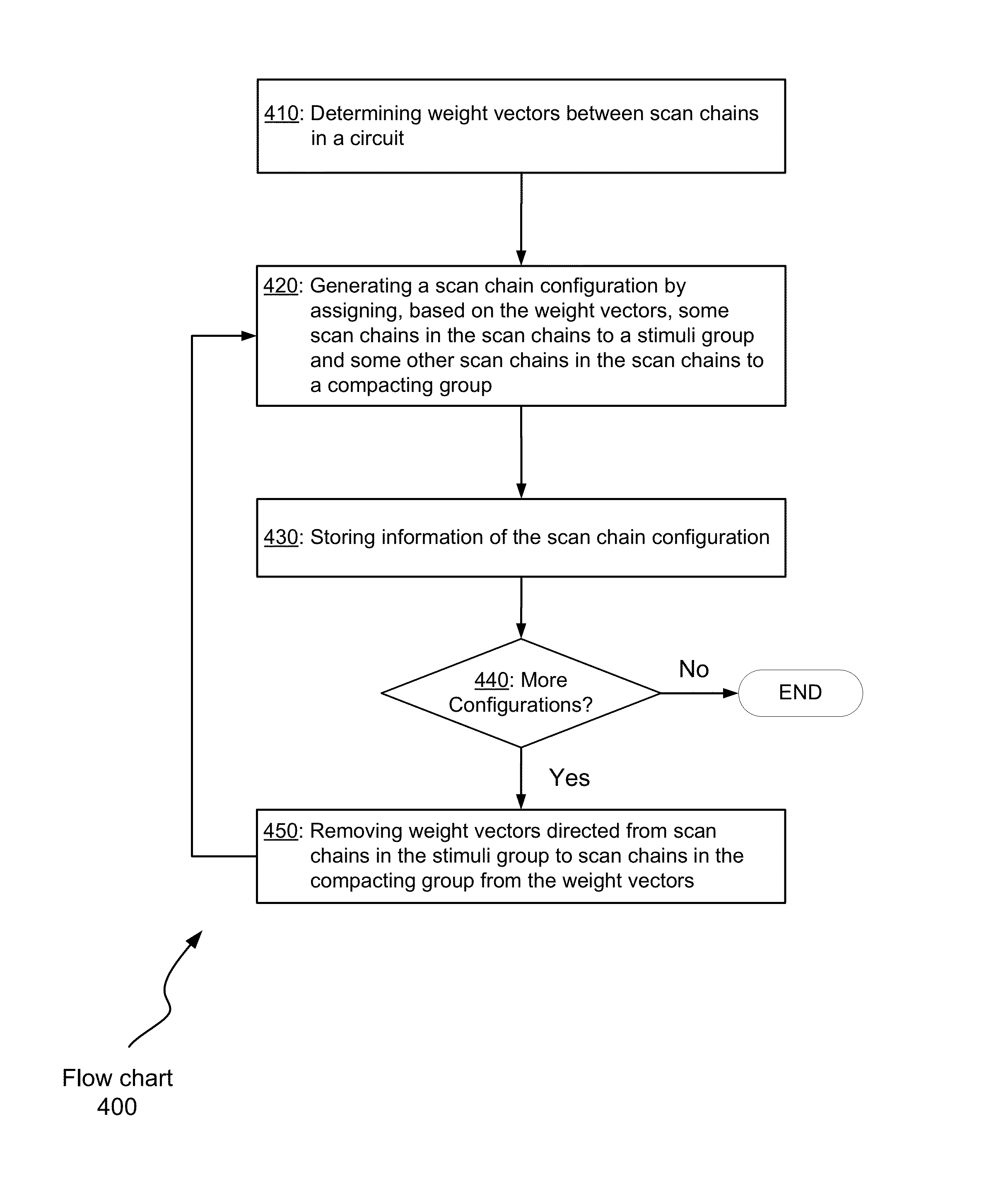

Scan chain configuration for test-per-clock based on circuit topology

Aspects of the invention relate to generating scan chain configurations for test-per-clock based on circuit topology. With various implementations of the invention, weight vectors between scan chains in a circuit are first determined. Based on the weight vectors, a scan chain configuration is generated by assigning some scan chains in the scan chains to a stimuli group and some other scan chains in the scan chains to a compacting group. Here, the stimuli group comprises scan chains to operate in a shifting-launching mode, and the compacting group comprises scan chains to operate in a capturing-compacting-shifting mode.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

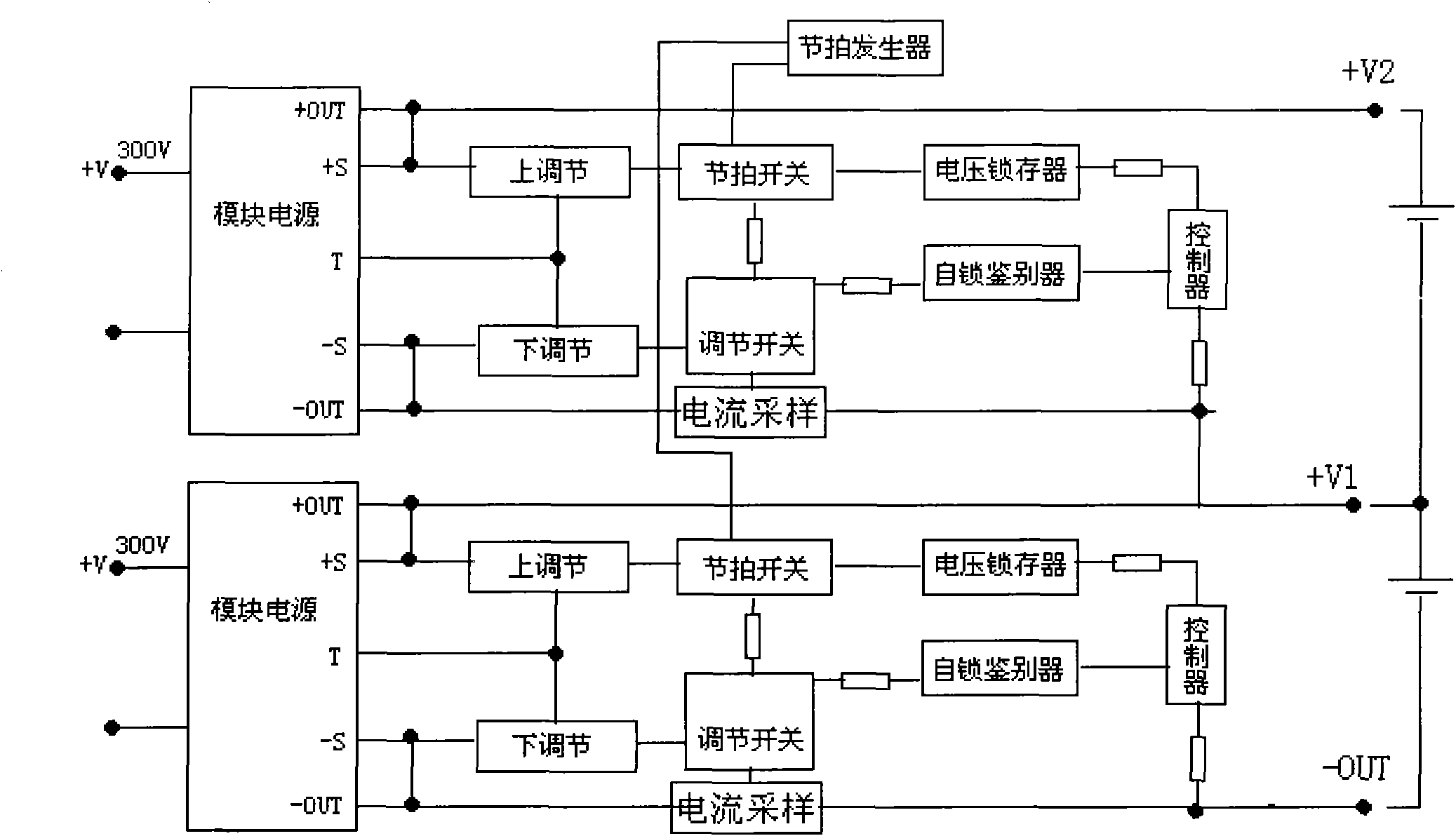

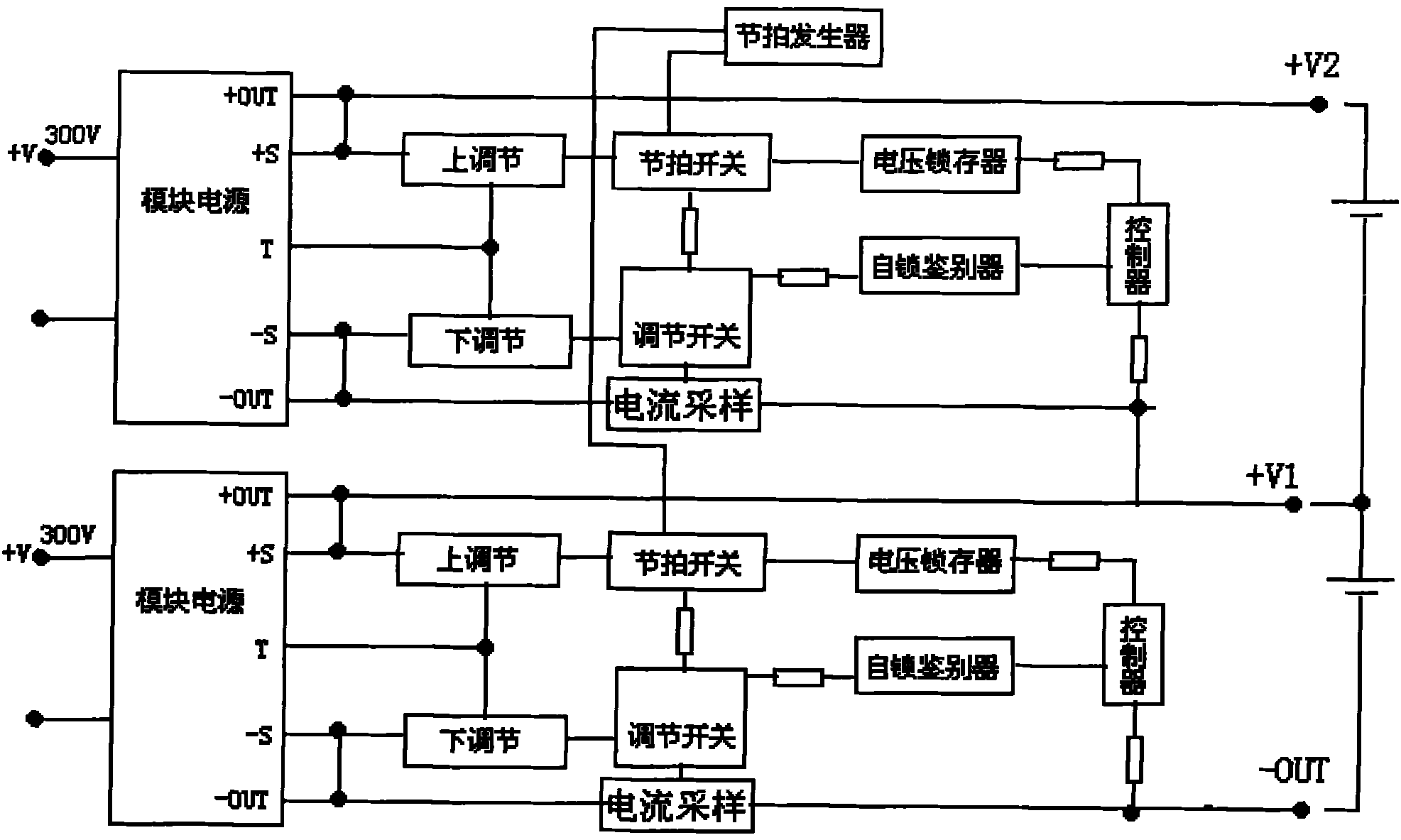

Clock test-and-control type balanced charging method for lithium battery pack

InactiveCN101887999AGuaranteed equalization accuracyEliminate the effects ofBatteries circuit arrangementsSecondary cells charging/dischargingCharge currentInternal resistance

The invention discloses a clock test-and-control type balanced charging method of a lithium battery pack, wherein, a balanced charging circuit comprises the lithium battery pack, a plurality of module power supplies and a clock pulse generator, wherein, the lithium battery pack is composed of a plurality of single lithium batteries which are connected in series, an output end of each module power supply is correspondingly connected with the single lithium battery, and each module power supply is respectively equipped with an independent control switch; a pulse signal generated by the clock pulse generator controls connection and disconnection of the control switches of the plurality of the module power supplies; and each single lithium battery independently charges under control, and at the moment when the control switches of the module power supplies are disconnected and charging current is zero, the testing and controlling voltage of the corresponding single battery is sampled. The balanced charging method of the invention can eliminate influence of the charging loop resistance and the internal resistance of the battery, ensure voltage balance for each lithium battery during the charging process of the lithium battery pack and guarantee safety control against overcharge of each lithium battery pack.

Owner:TIANJIN SHENLU ENERGY

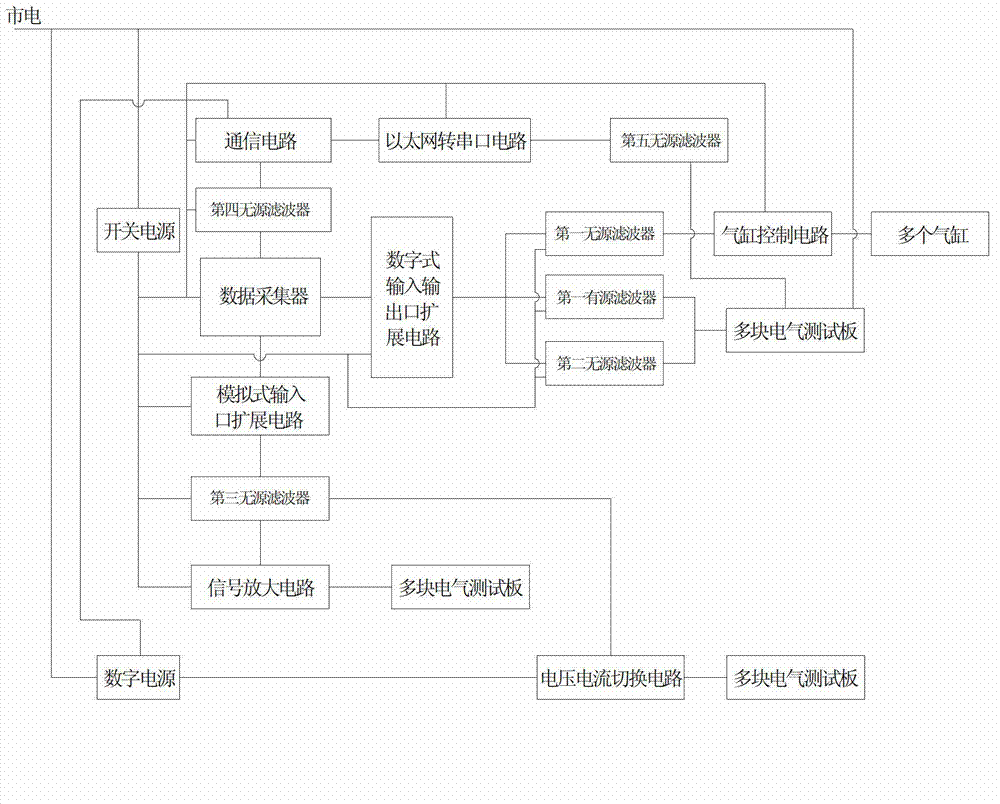

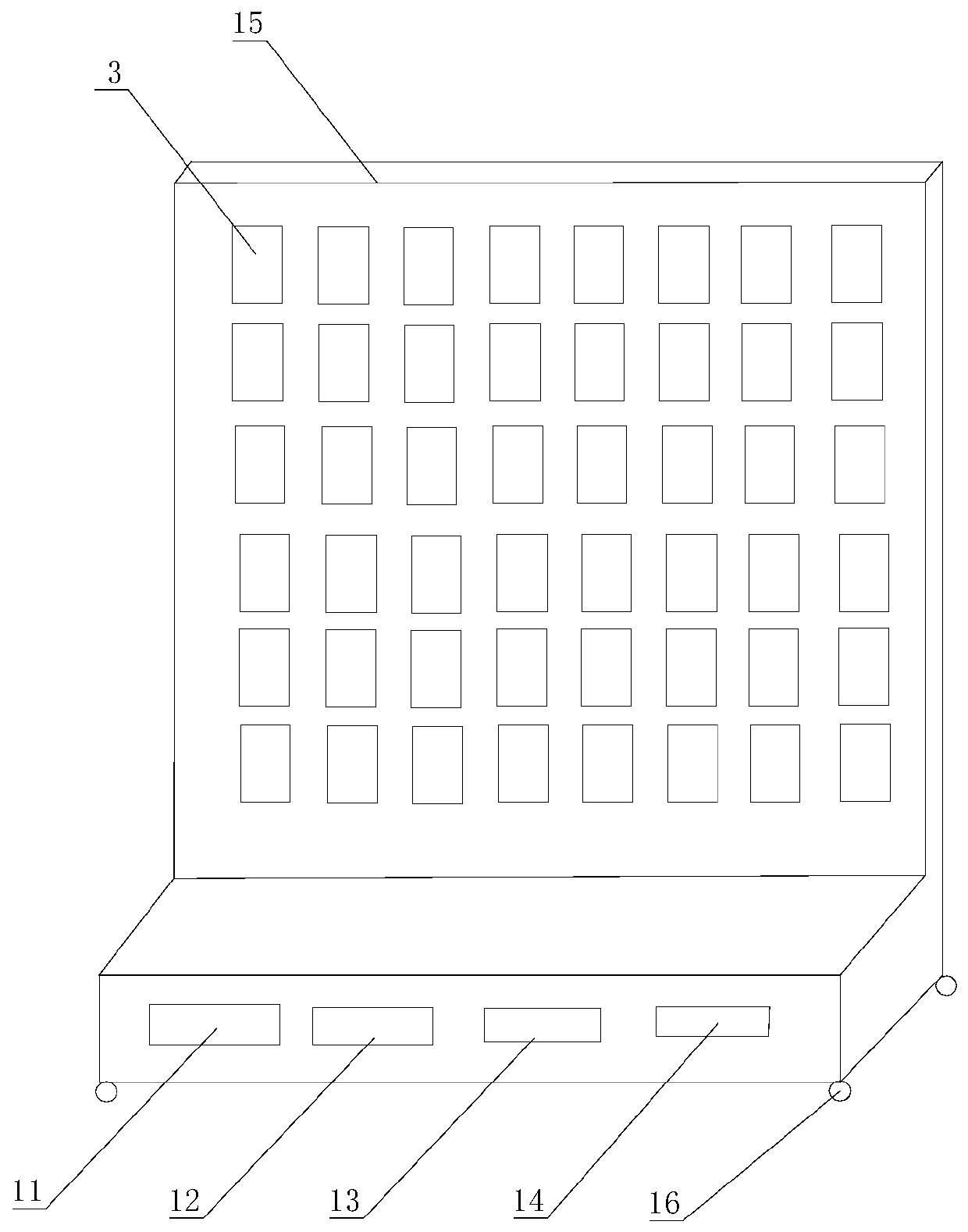

II-type collector fault disassembling, sorting and detecting device

InactiveCN110233681AReduce work intensityAvoid wastingTransmitters monitoringReceivers monitoringCarrier signalEngineering

The invention relates to an II-type collector fault disassembling, sorting and detecting device which comprises a test board and a control cabinet connected with the test board, and the test board comprises a clock test module, a 485 communication test module, an infrared communication test module, a carrier test module and a test meter position system. The device has the advantages that the II-type collectors are uniformly mounted on the test board through the test meter position system, the control cabinet sets test parameters, carrier communication and micropower communication tests of thetype-II collector are tested through configuration of the carrier test module. Then, accurate test clock output comparison sources are provided for the testboard through clock test modules arranged onthe testboard respectively. The 485 communication test module provides an analog 485 communication test, and the infrared communication test module completes an infrared communication test function,so that online batch detection of various fault types of the fault collector is realized, the overall detection efficiency is improved, the cost can be greatly saved, and the waste of resources is avoided.

Owner:浙江八达电子仪表有限公司 +1

Clock test apparatus and method for semiconductor integrated circuit

A clock test apparatus for a semiconductor integrated circuit includes a delay unit configured to delay an internal clock signal. A comparison unit compares the phase of an output signal of the delay unit with the phase of a reference clock signal. A phase discrimination unit receives a test mode signal, the reference clock signal, and an output signal of the comparison unit, thereby outputting a discrimination signal.

Owner:SK HYNIX INC

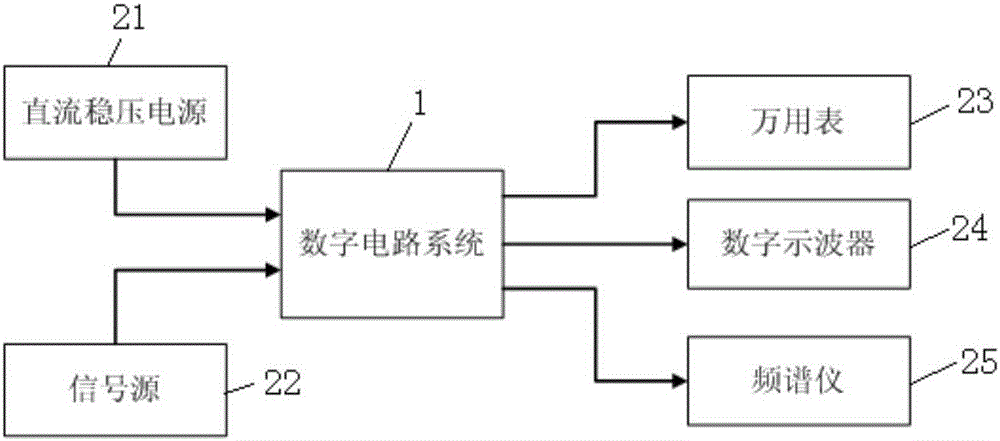

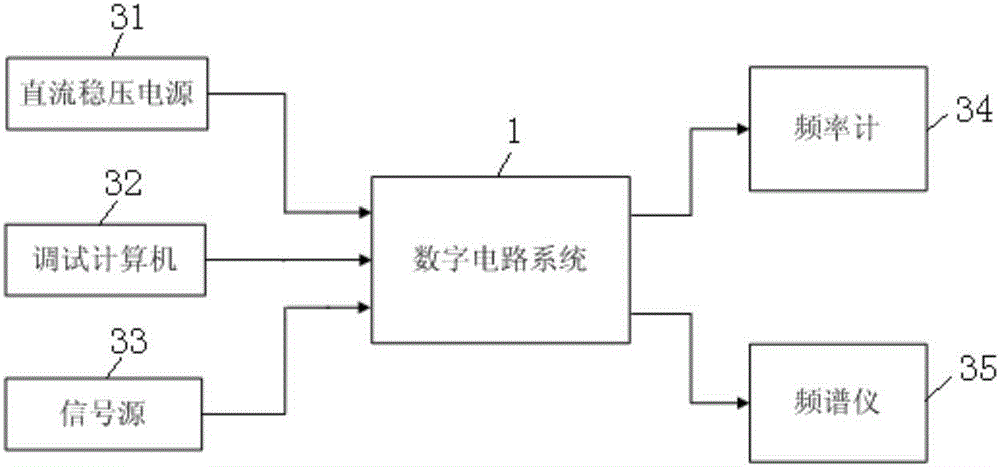

Digital circuit system test method

ActiveCN106526462AComprehensive testImprove reliabilityElectrical testingElectricityInterface impedance

The invention provides a digital circuit system test method. The method is characterized by carrying out test on collaborative modules in a digital circuit system in sequence through a power interface impedance test before powering up as well as a voltage correctness test, a phase-locked loop module clock test, a DDS accuracy and homologous stability test and an AD / DA access performance test after powering up, so that functions and performances of main modules in the digital circuit system can be subjected to comprehensive test, corresponding indexes of the digital circuit system can be evaluated effectively, test results can be obtained at a fastest speed, and reliability is high.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM +1

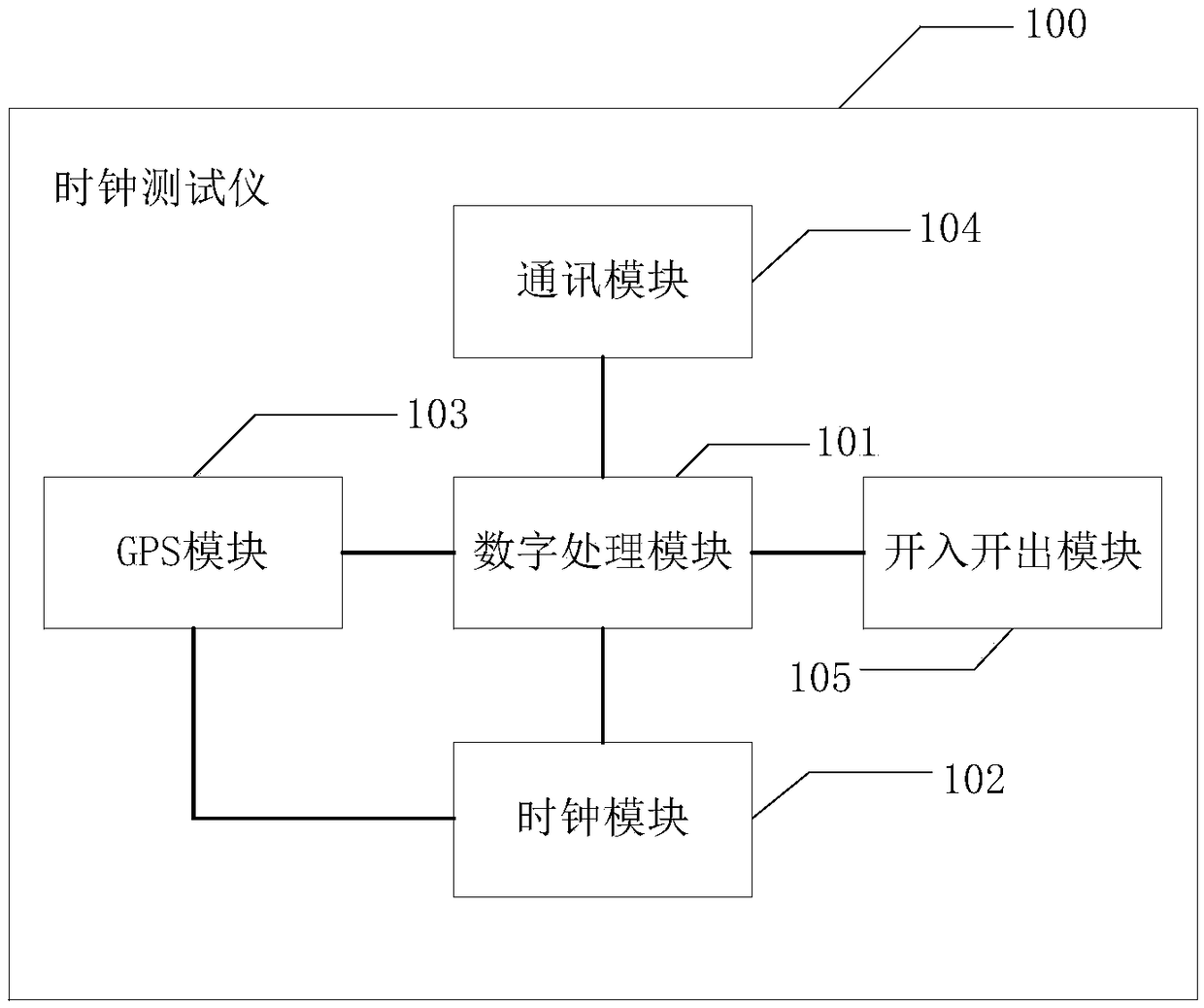

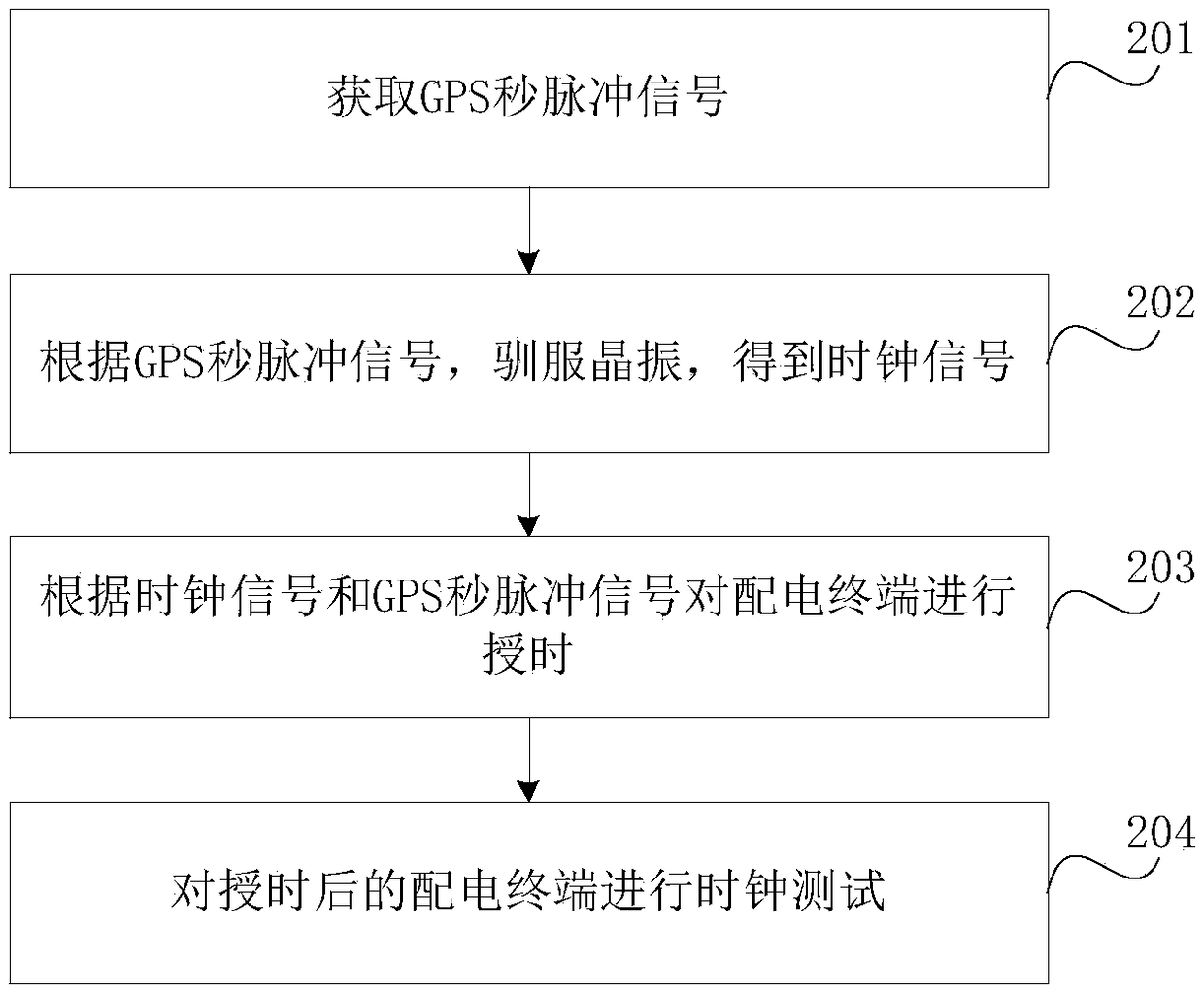

Clock tester and clock test method for distribution terminals

The invention discloses a clock tester and a clock test method of a distribution terminal. The clock tester comprises a digital processing module, a clock module, a GPS module, a communication moduleand an input / output module. The digital processing module is electrically connected with the clock module, the GPS module, the communication module and the input / output module, and the clock module iselectrically connected with the GPS module. The clock module is used for: acquiring the GPS second pulse signal generated by the GPS module; According to the GPS second pulse signal, the crystal oscillator is tamed to obtain the clock signal. Timing the distribution terminal according to the clock signal and the GPS second pulse signal; The digital processing module is used for performing clock test on the time-given distribution terminal through the communication module and / or the in / out module. The clock tester provided by the present application enables the distribution terminal and the clock tester to coincide in time by timing the distribution terminal, so that the clock test is carried out based on the time of the same clock tester, and the accuracy of the clock test is improved.

Owner:YUNNAN POWER GRID CO LTD ELECTRIC POWER RES INST

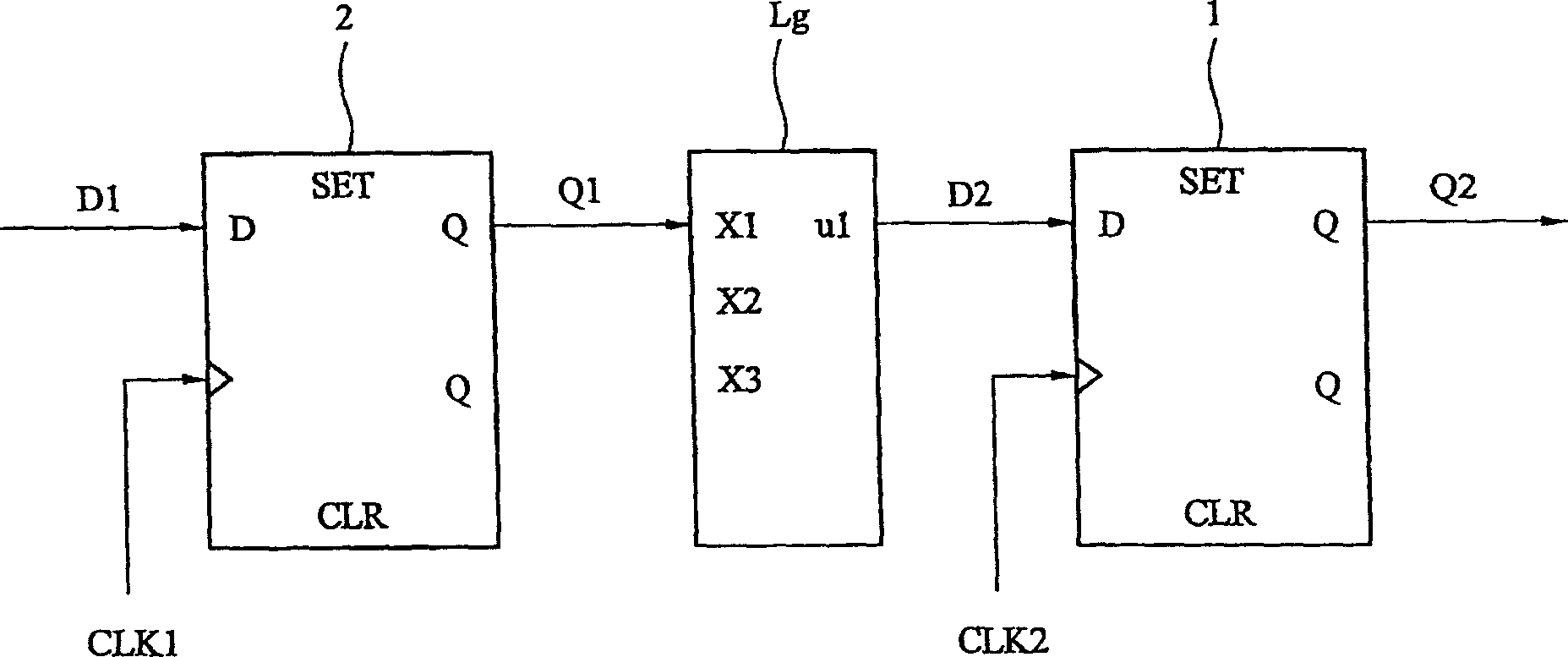

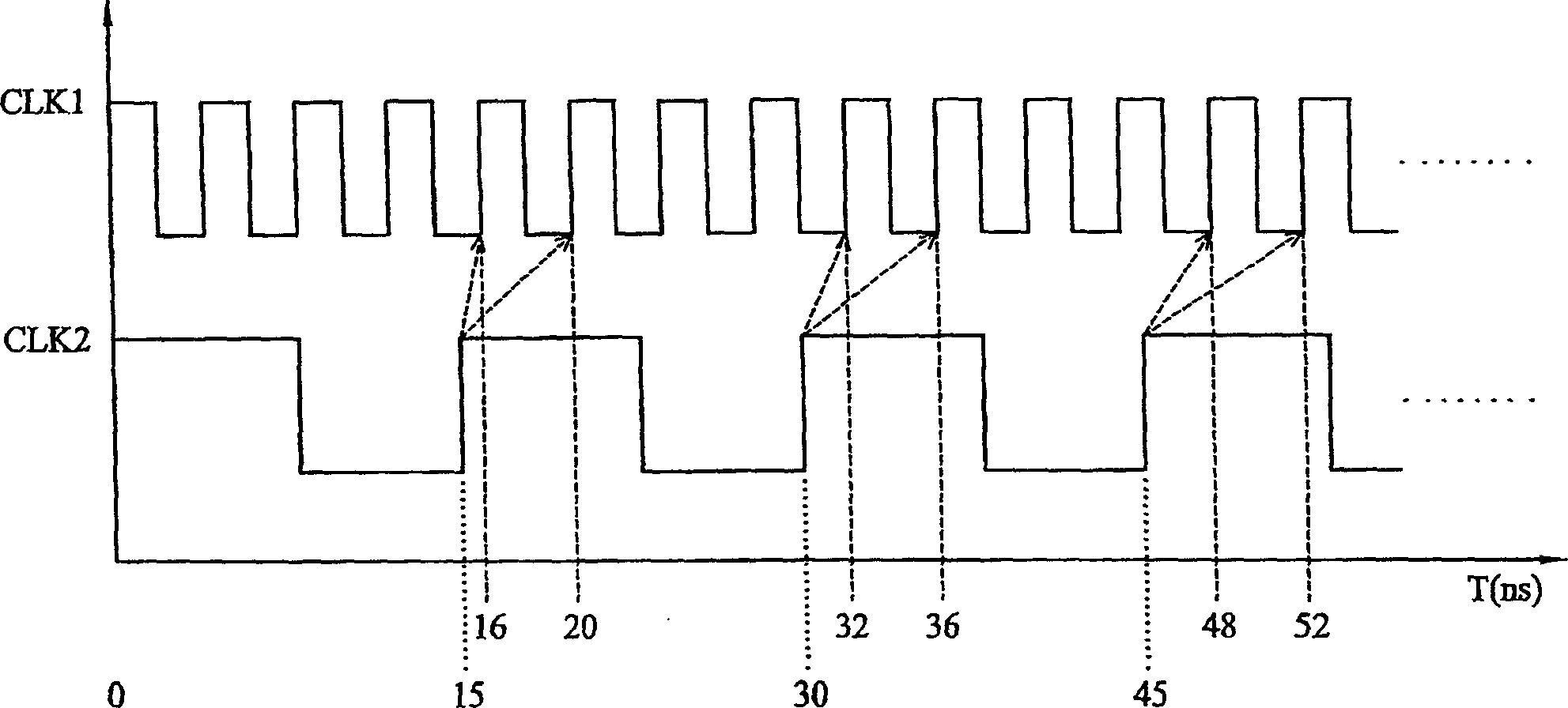

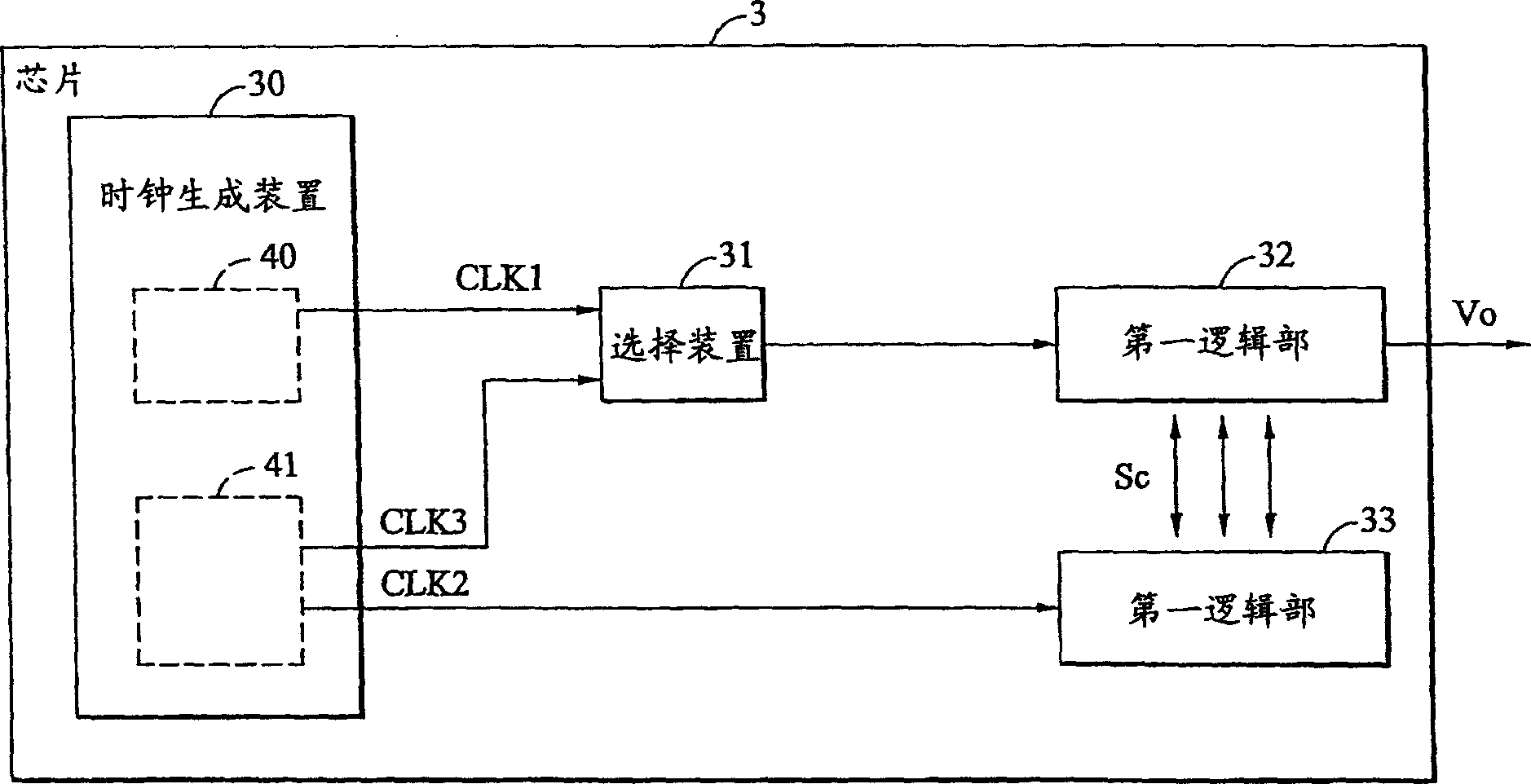

Testing method for chip synchronous clock and chip capable of synchronously testing clock function

ActiveCN1632935AImprove accuracyAvoiding problems with asynchronous effectsSemiconductor/solid-state device testing/measurementEmbedded systemClock Test

It is a chip with clock test function and its test method. The above chip at least comprises one first logic part, one-second logic part. The method comprises the following steps: to generate one third clock signal; to substitute the first clock signal with third clock signal; to test the above the part outside the first clock generation device of the chip; to make the first logic operation independent to the second logic part to test the first clock generation device.

Owner:VIA TECH INC

Selectable loss of signal (LOS) criteria

ActiveUS20080062884A1Error detection/prevention using signal quality detectorTransmission systemsVoltage amplitudeDigital data

A system and method are provided for selecting loss of signal (LOS) criteria in a serial communications receiver. The method receives a serial stream of digital data and selects LOS criteria. The serial stream of digital data is compared to the selected LOS criteria. In response to the serial stream of digital data failing to meet the selected LOS criteria, a LOS signal is generated. Some examples of the LOS criteria that might be selected include: a “signal detect” signal received from the source transmitting the serial stream of digital data, a run length test, a signal strength (voltage amplitude) test, harmonic band detection test, and a received data clock test. In one aspect, selecting LOS criteria includes selecting combinations of the above-mentioned LOS criteria, so that the LOS signal is generated in response to failing to meet the combination of selected LOS criteria.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC