Low-power-consumption small-area capacitor array and reset method and logic control method thereof

A capacitor array and small-area technology, applied in electrical components, electrical signal transmission systems, signal transmission systems, etc., can solve the problems of large input capacitance of SARADC, large dynamic power consumption of capacitor array, and influence on ADC sampling rate, etc., and achieve common mode Reduced level change range, increased flexibility, and flexible effects generation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to express the purpose, technical solution and advantages of the present invention more clearly, the present invention will be further described in detail below in conjunction with the accompanying drawings. Here, the embodiments and descriptions of the present invention are only for explaining the present invention, not as limiting the present invention.

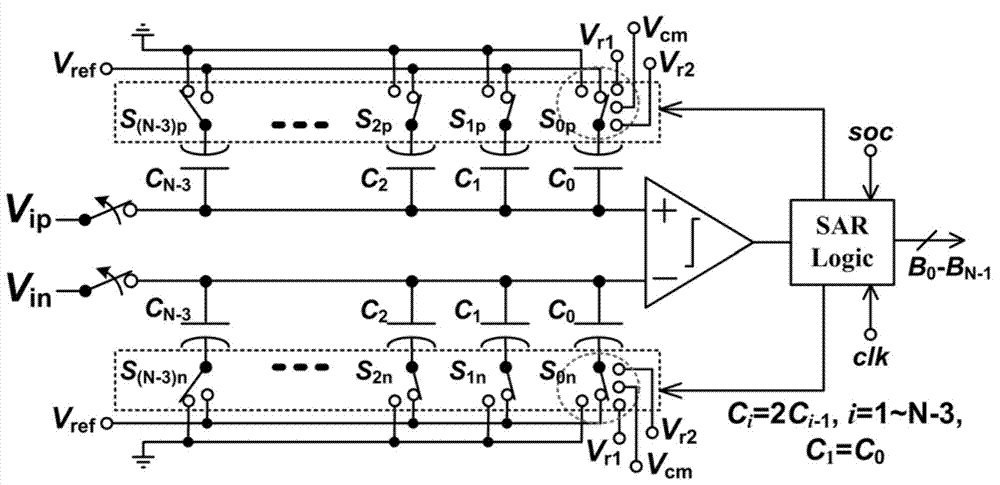

[0020] see figure 2 , the capacitor array with low power consumption and small area of the present invention includes two groups of capacitors C 0 , capacitance C 1 , capacitance C 2 , ... Capacitance C N-3 The capacitor array forms a binary capacitor array, and the switch S 0p ~Switch S ip and switch S 0n ~Switch S in Composed of capacitor array switches, four reference voltages V ref , V cm , V r1 and V r2 and the differential input signal V ip and V in ; Where N is an integer greater than or equal to 3, i=N-3; V ip and V in Connected to the two input terminals of the comparator respectiv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com