A kind of i/o interface circuit of asynchronous sram

An interface circuit and asynchronous technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of high power consumption, poor reliability, and unstable control of I/O interface circuits, so as to reduce power consumption and enhance accuracy performance, speed up the response

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

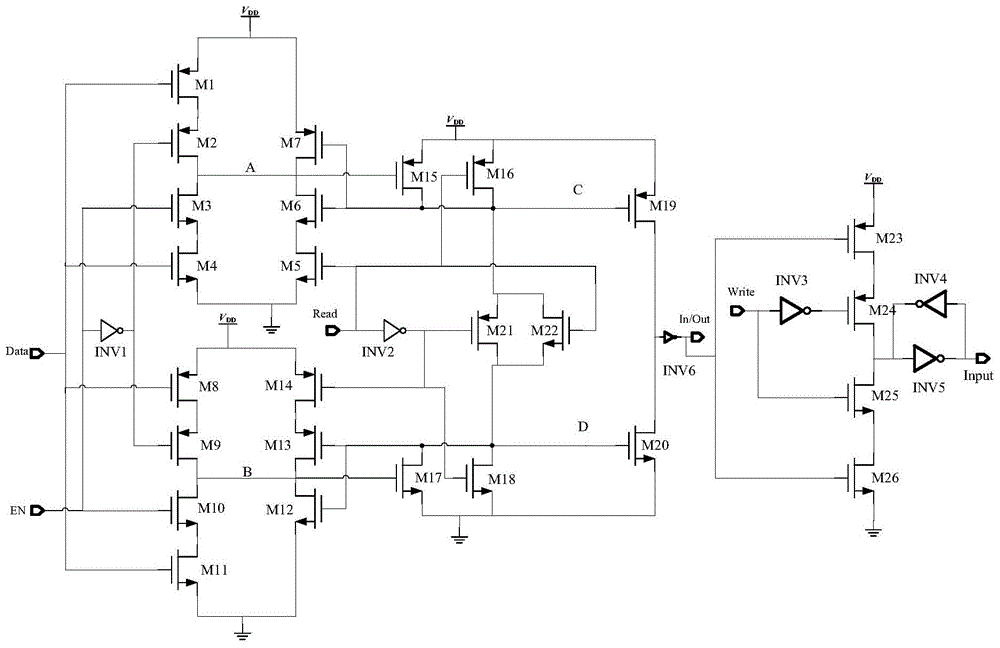

[0012] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and embodiments.

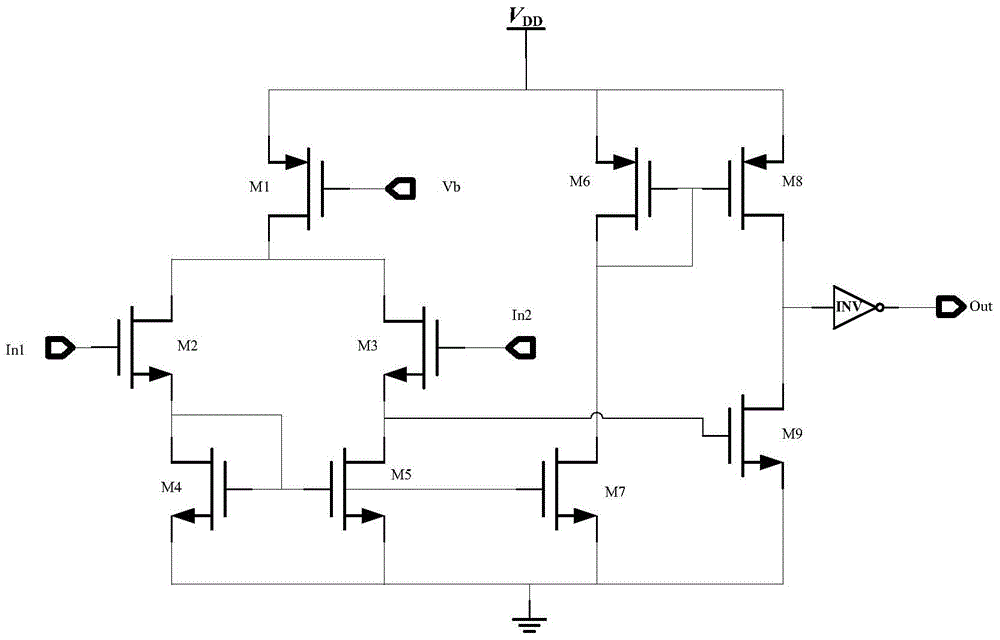

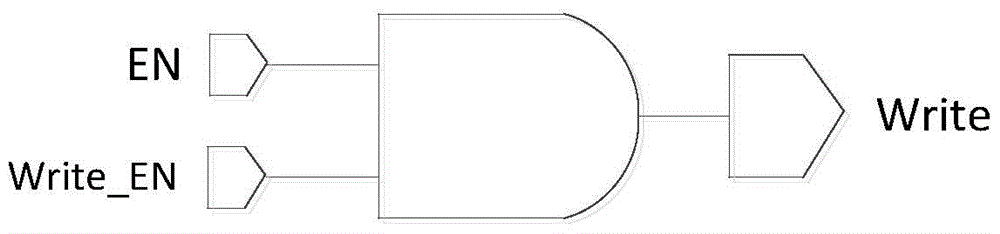

[0013] An embodiment of the present invention provides an I / O interface circuit of an asynchronous SRAM, including a read circuit and a write circuit. Wherein, the output terminal of the reading circuit is connected with the input terminal of the writing circuit; the reading circuit is connected with the enable signal EN, the data signal Data and the reading signal Read; the writing circuit is connected with the writing signal Write.

[0014] see figure 2, the read circuit includes a first PMOS transistor M1, a second PMOS transistor M2, a third NMOS transistor M3, a fourth NMOS transistor M4, a fifth NMOS transistor M5, a sixth NMOS transistor M6, a seventh PMOS transistor M7, an eighth PMOS transistor Transistor M8, ninth PMOS transistor M9, tenth NMOS transistor M10, eleventh NMOS transistor M11, twelfth NMOS transistor M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More