Thin film transistor (TFT) array substrate and liquid crystal panel thereof

A technology for array substrates and liquid crystal panels, applied in the field of TFT array substrates and liquid crystal panels, can solve problems such as unclean etching, short-circuiting of short-circuit bars, abnormal display of substrates, etc., and achieve the effect of avoiding abnormal display problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

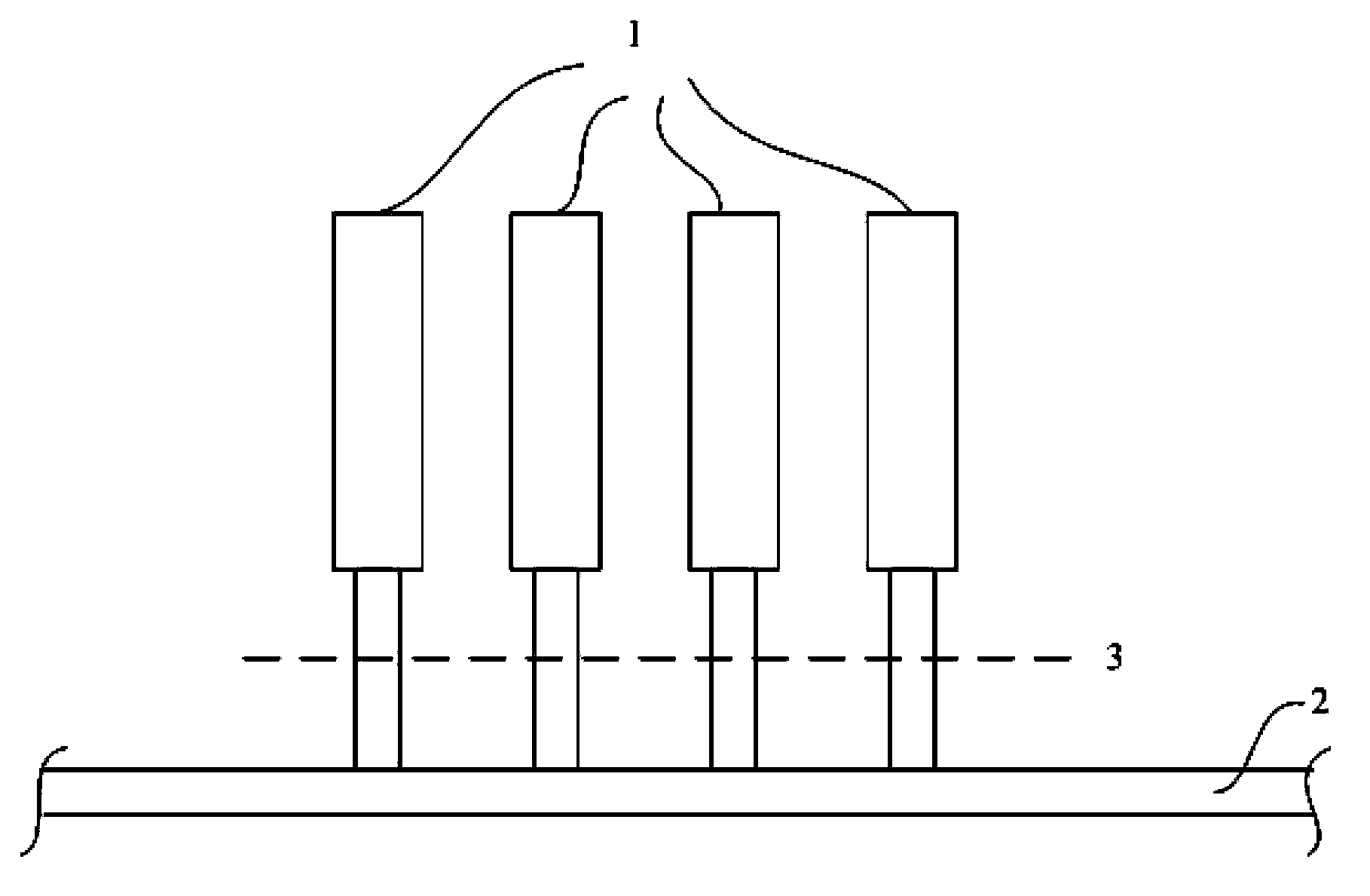

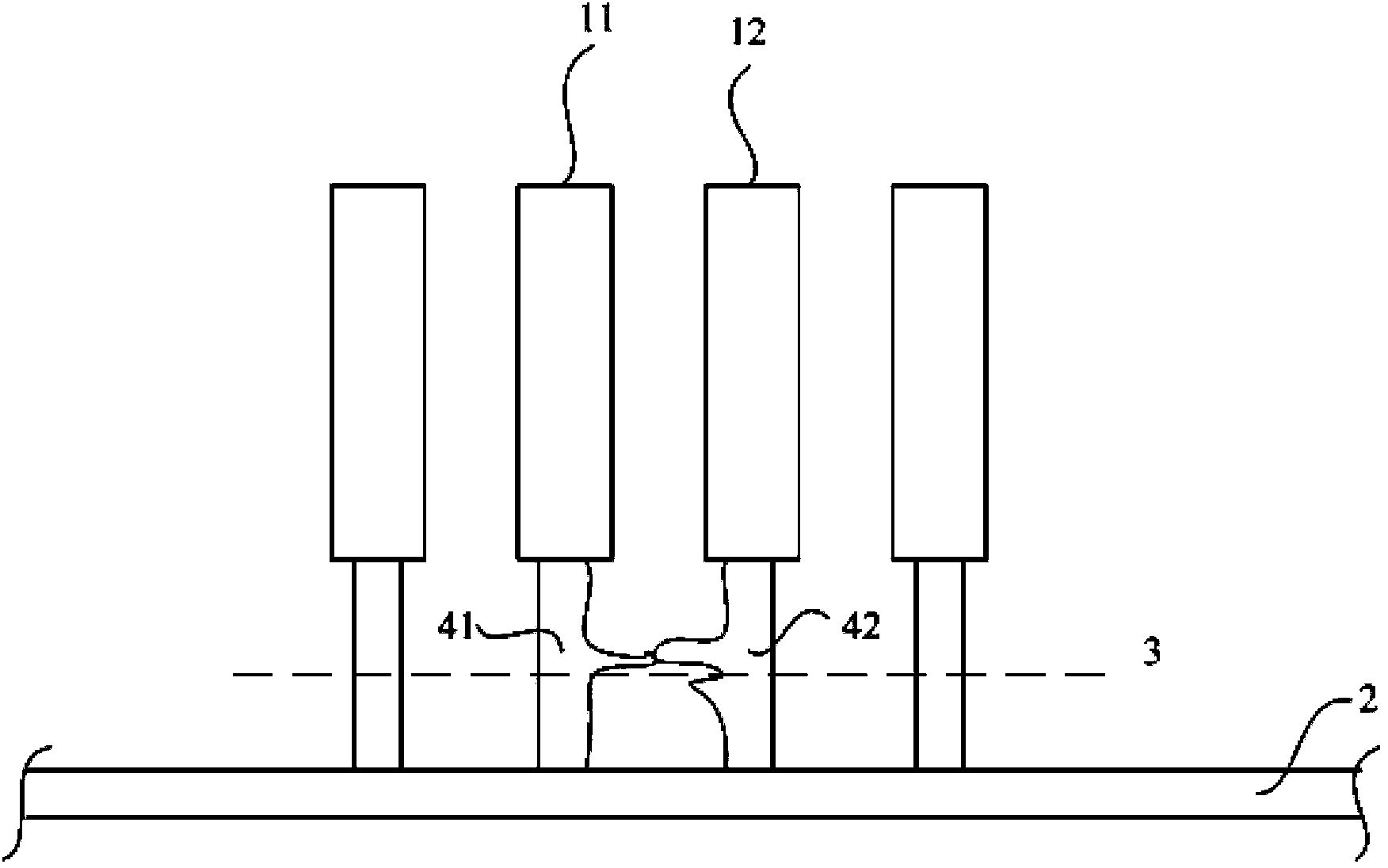

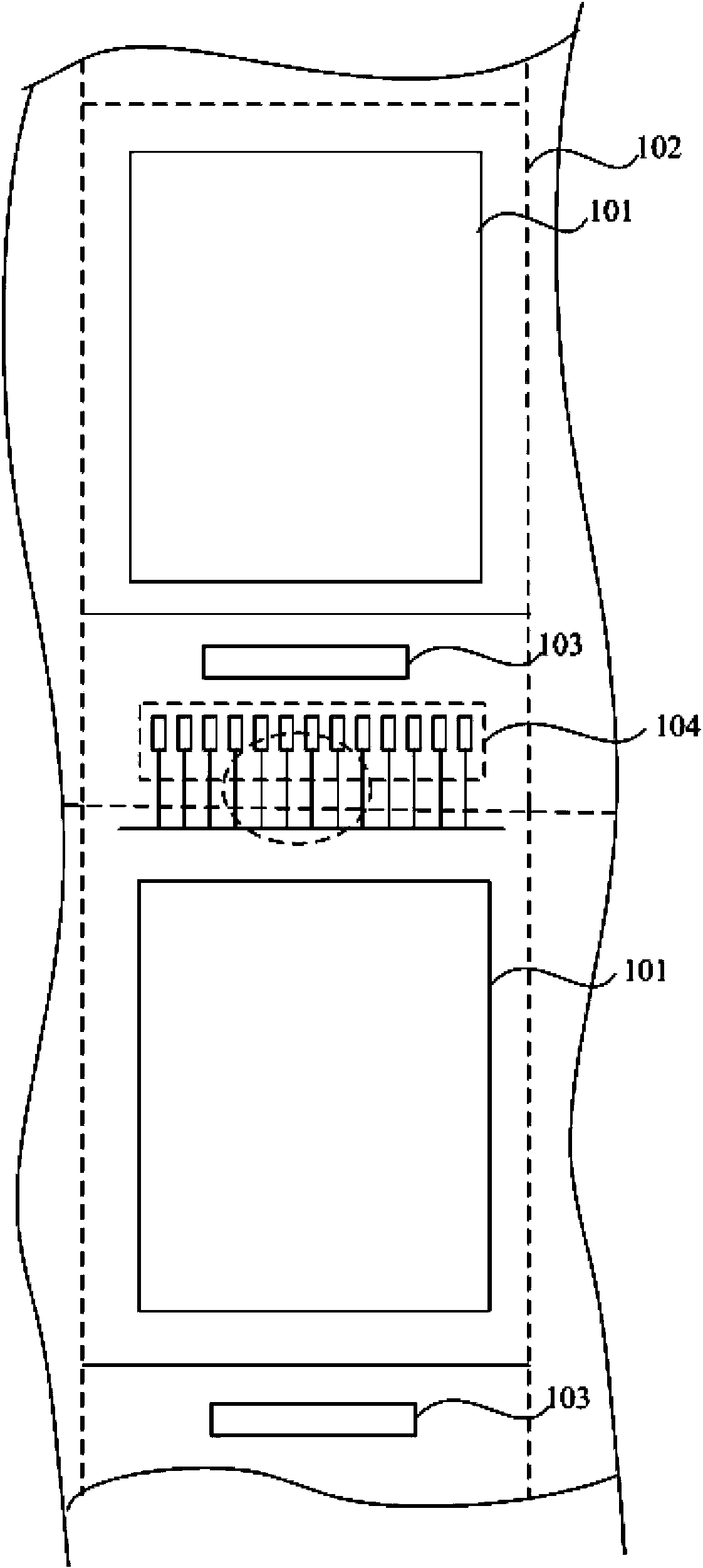

[0054] see image 3 and Figure 4 . in, image 3A TFT array substrate provided by the present invention is shown, and the array substrate 102 includes a display area 101 and a non-display area other than the display area 101 . The non-display area includes an IC (Integrated Circuit) driver chip 103, which is used to transmit various received signals to the array substrate to control the gray scale of the display; the pad area 104 is used to receive external signals, and transmit the The signal is correspondingly transmitted to the IC driver chip; and other wires (not shown in the figure). Figure 4 yes image 3 A partially enlarged view of the pad region 104 at the edge of the array substrate 102 in .

[0055] refer to Figure 4 , the TFT array substrate of the present invention, comprising:

[0056] Substrate 1;

[0057] A plurality of pads 2 on the surface of the substrate 1, the pads 2 are used to receive external signals; the pads 2 here can be FOG pads, test p...

Embodiment 2

[0071] This embodiment is a further embodiment obtained on the basis of the first embodiment. see Figure 8 The difference between this embodiment and the first embodiment is that the liner 2 includes a first liner 21 and a second liner 22 . For the convenience of description, the first short-circuit bar 3 also includes a first sub-short-circuit bar 31 and a second sub-short-circuit bar 32 correspondingly, the first sub-short-circuit bar 31 is set correspondingly to the first pad 21, and the second sub-short-circuit bar 32 is connected to the second sub-short-circuit bar 32 . The two pads 22 are arranged correspondingly. Preferably, the first pad 21 is a FOG pad. Further, the second pad 22 is a test pad.

[0072] The ESD device 5 includes a first ESD device 51 and a second ESD device 52, the first ESD device 51 is electrically connected to the first pad 21 and the first sub-short bar 31 corresponding thereto, and the second ESD device 52 is electrically connected to the sec...

Embodiment 3

[0075] This embodiment is further obtained on the basis of the second embodiment. The difference from Embodiment 2 is that in this embodiment, since the FOG pad 21 is more susceptible to electrostatic hazards than the test pad 22, the first short circuit bar 31 electrically connecting the FOG pad 21 and the first sub-short bar 31 The ESD device 51 adopts a first-level bidirectional ESD device, which has played the role of faster discharge; the second ESD device 52 electrically connected to the test pad 22 and the second sub-short bar 32 adopts a multi-level ESD device, preferably, the second ESD device 52 uses two-stage bidirectional ESD devices.

[0076] see Figure 9 , Figure 9 is a schematic diagram of a TFT-based two-stage bidirectional ESD device. The two-stage bidirectional ESD device is formed by connecting two one-stage bidirectional ESD devices in series. see also Figure 8 , Figure 9 , the A terminal of the second ESD device 52 is electrically connected to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More