Laser simulation single particle effect back irradiation test method for memory circuit

A memory circuit, single-event effect technology, applied in static memory, instruments, etc., can solve problems such as difficulty in analyzing the influence of single-event performance, difficulty in obtaining pulsed laser response characteristics, difficulty in single-event sensitivity, etc., to reduce experimental errors. , The effect of simplifying the test steps and reducing the cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

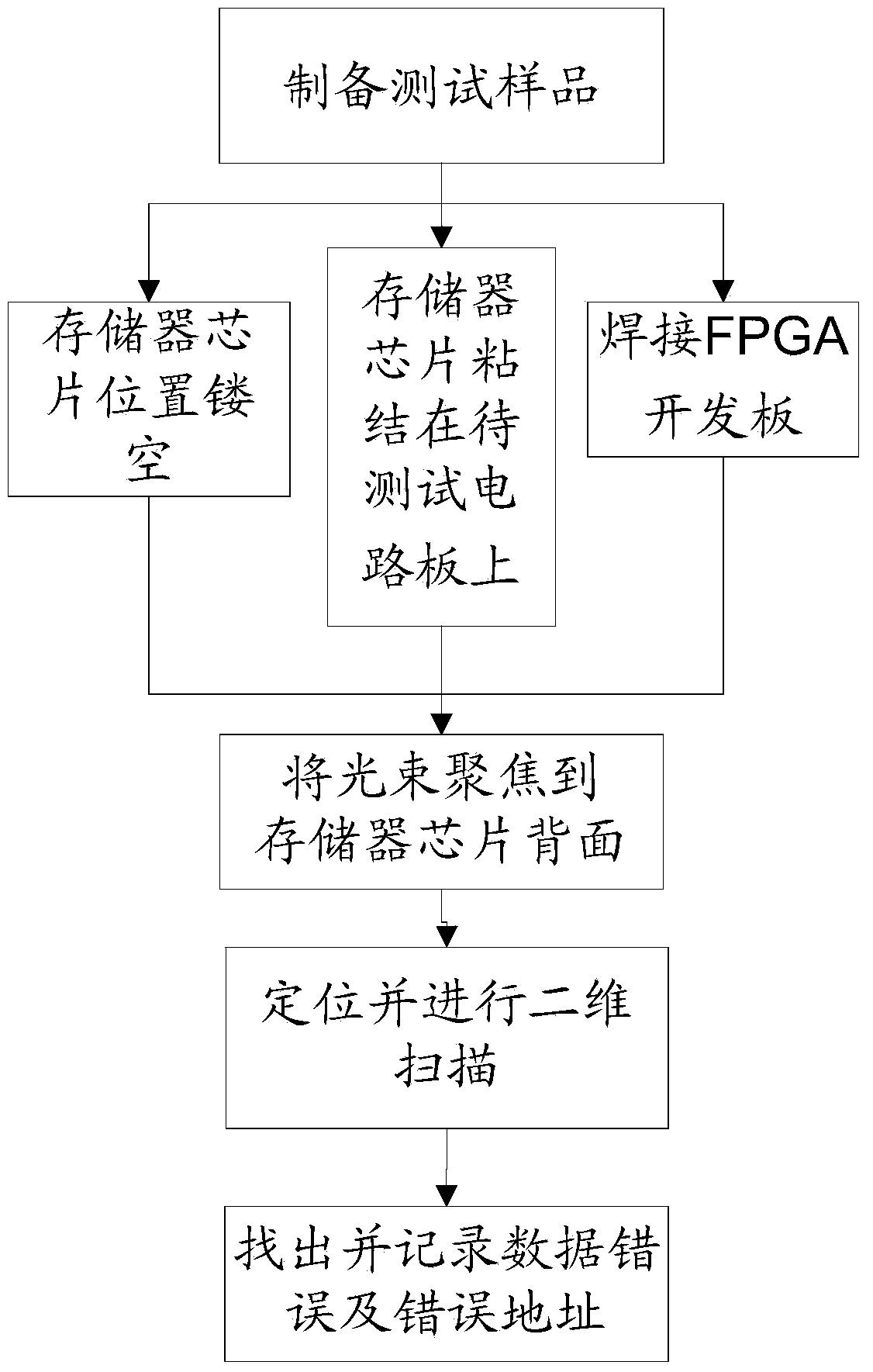

[0028] figure 1 The process flow of the pulsed laser simulation single event effect back irradiation test method for the memory circuit of the present invention is described:

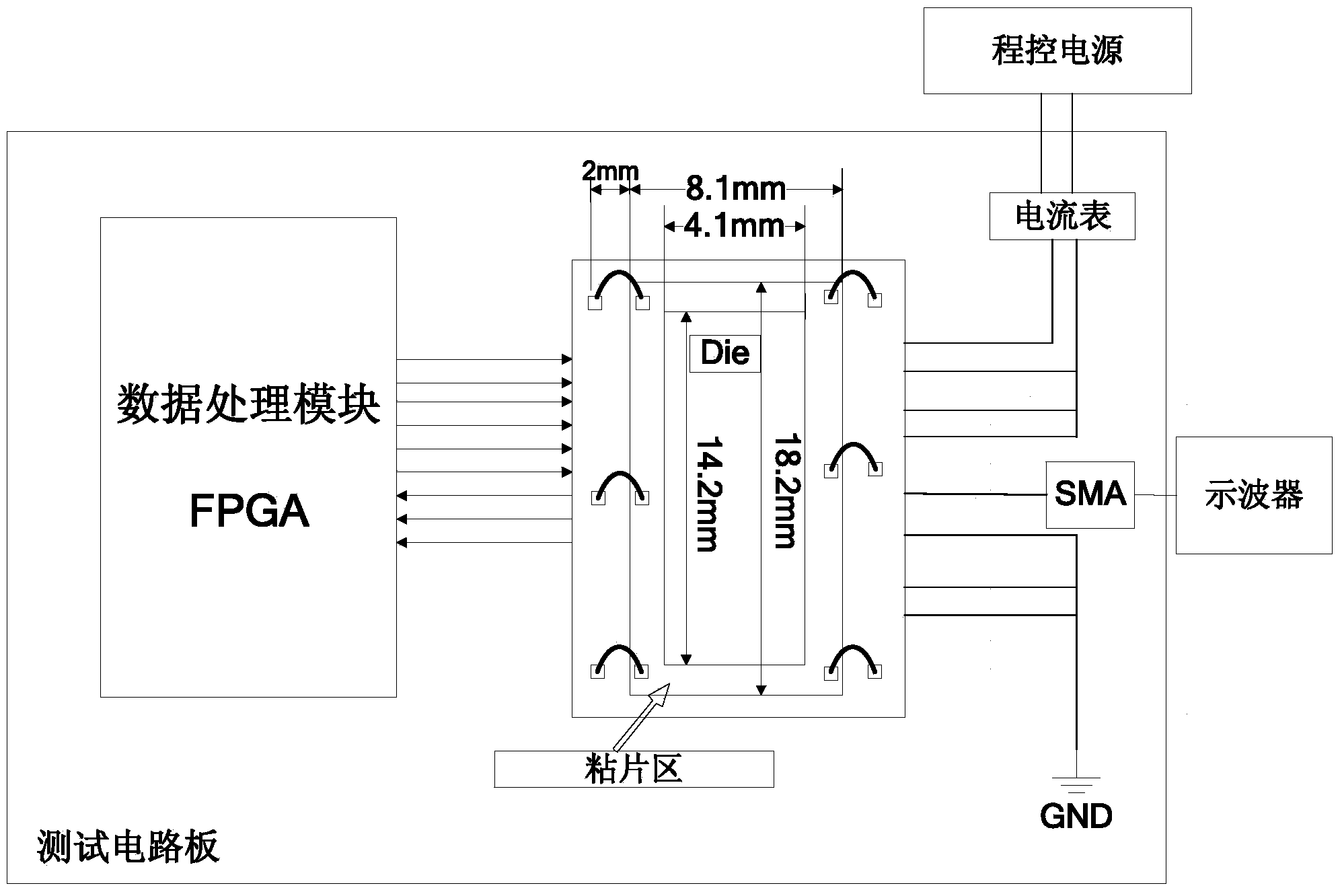

[0029] (1) Prepare memory circuit test samples; first, hollow out the position where the memory chip is bonded on the circuit board to be tested to form a hollow hole. The shape and size of the hollow hole are based on the shape and size of the memory chip, and a 2mm sticky chip is reserved around it area, and the rest of the central part is hollowed out; then the memory chip is bonded to the circuit board to be tested, and the memory chip is bonded to the pad of the circuit board to be tested with aluminum wire; at the same time, the FPGA development board is also soldered to the circuit board to be tested ;

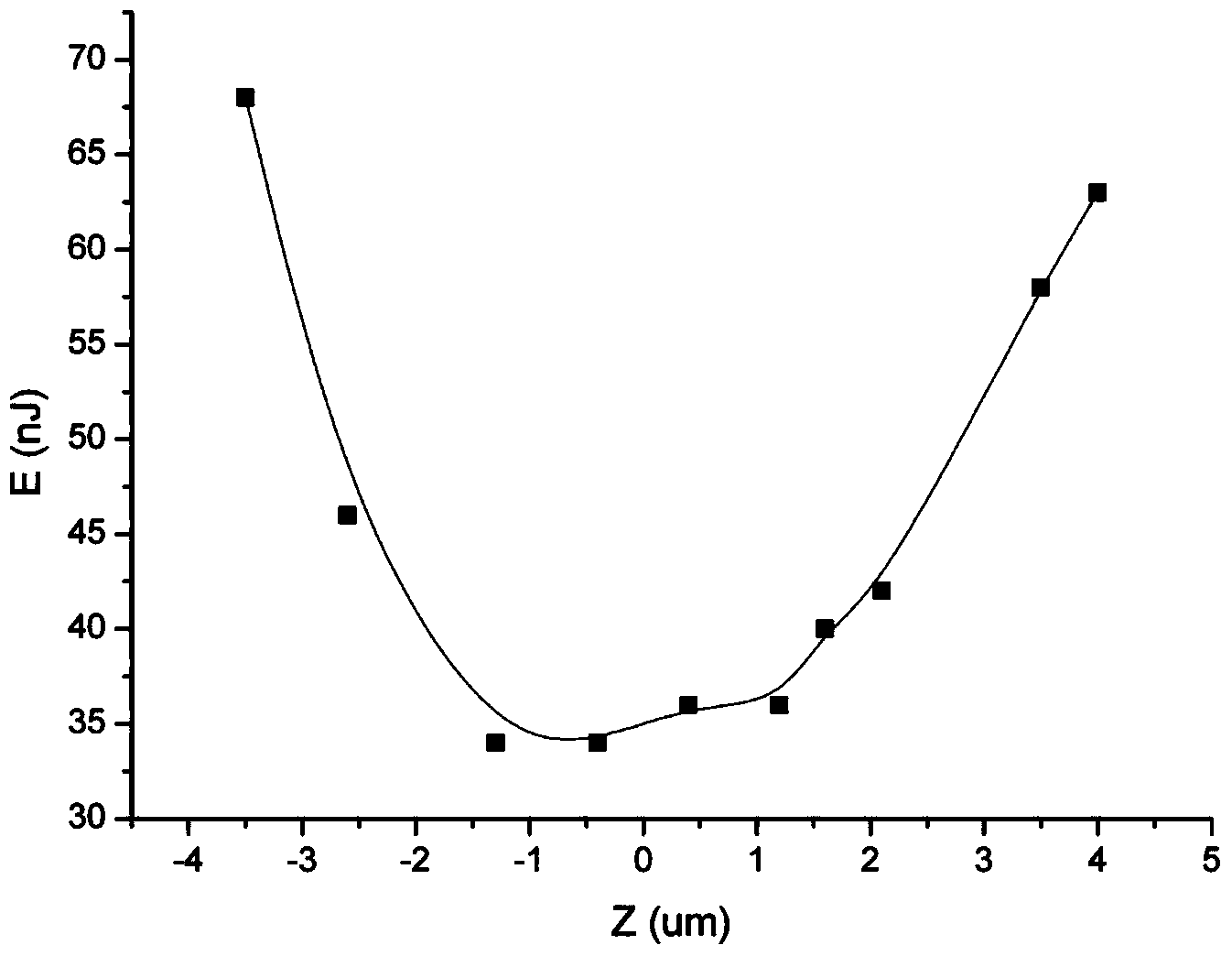

[0030] (2) Fix the memory circuit test sample on the three-dimensional translation stage, drive the three-dimensional translation stage, make the pulsed laser emitted by the external laser focus...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More