Manufacturing method of semiconductor device test sample

A manufacturing method and a technology for testing samples, which are applied in the semiconductor field, can solve problems such as floating gate short circuit, FLASH memory failure, etching, etc., and achieve the effect of small aspect ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

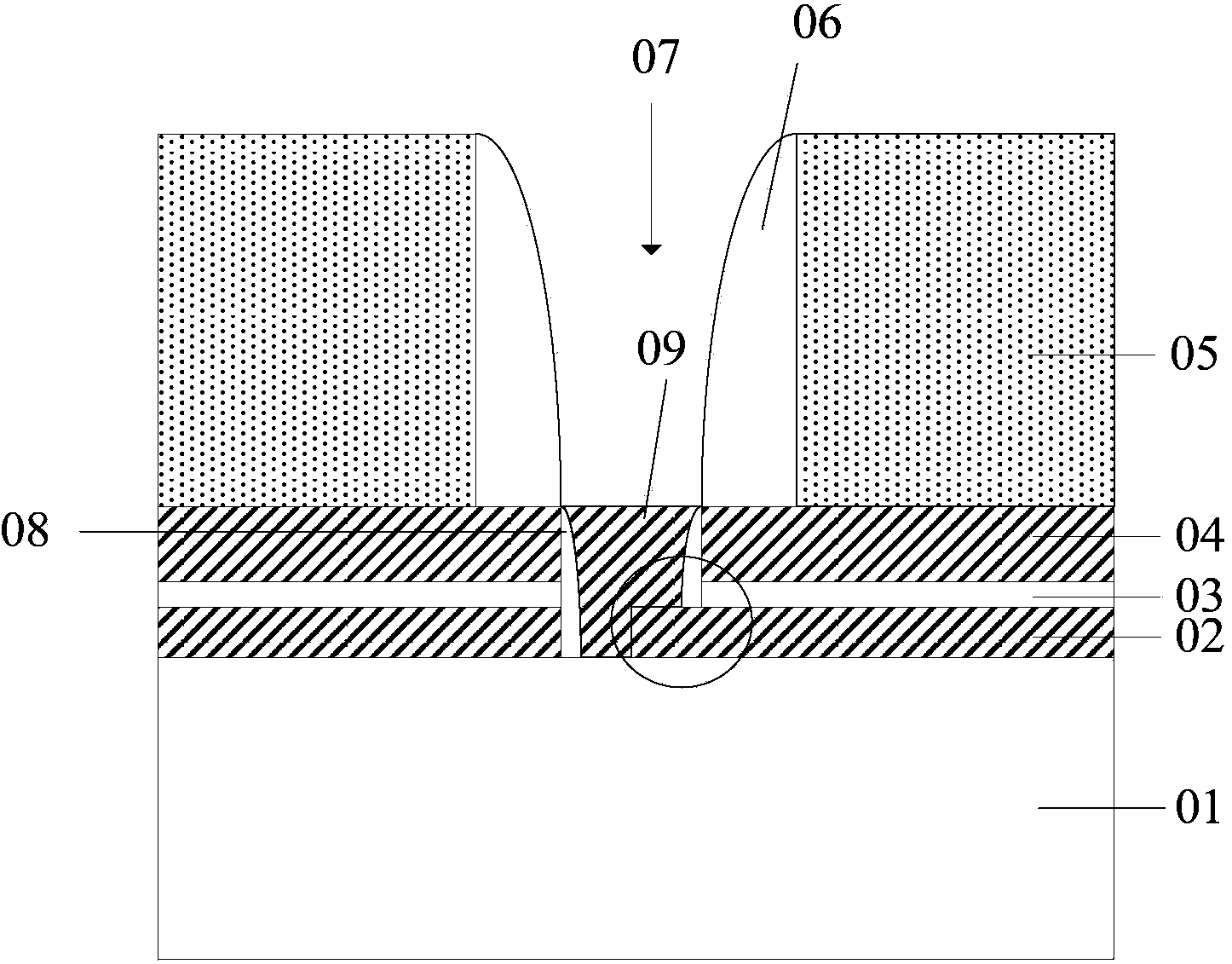

[0030] In existing semiconductor device test samples, if defects such as etching residues occur in trenches with a high aspect ratio, it is difficult for wafer inspection equipment to capture the above defects, which will easily cause batches of wafers to be scrapped due to defects , causing losses.

[0031] In order to solve the above technical problems, the present invention provides a method for manufacturing a test sample of a semiconductor device, so that the wafer inspection equipment can more sensitively capture the defects of etching residues in the gap online, and monitor such defects in time. Reduce the probability of semiconductor device failure.

[0032] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0033] In the following embodiments, the method for making a semiconductor devic...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com