Process Mapping Method Based on Local Minimization of Robdd and Area Delay Optimization

A technology of local minimum and process mapping, applied in the direction of program control devices, etc., can solve problems such as constraints, alternative division, inefficiency, delay and area, and achieve memory and time reduction, area and delay reduction, and operational efficiency improvement Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0047] The application principle of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

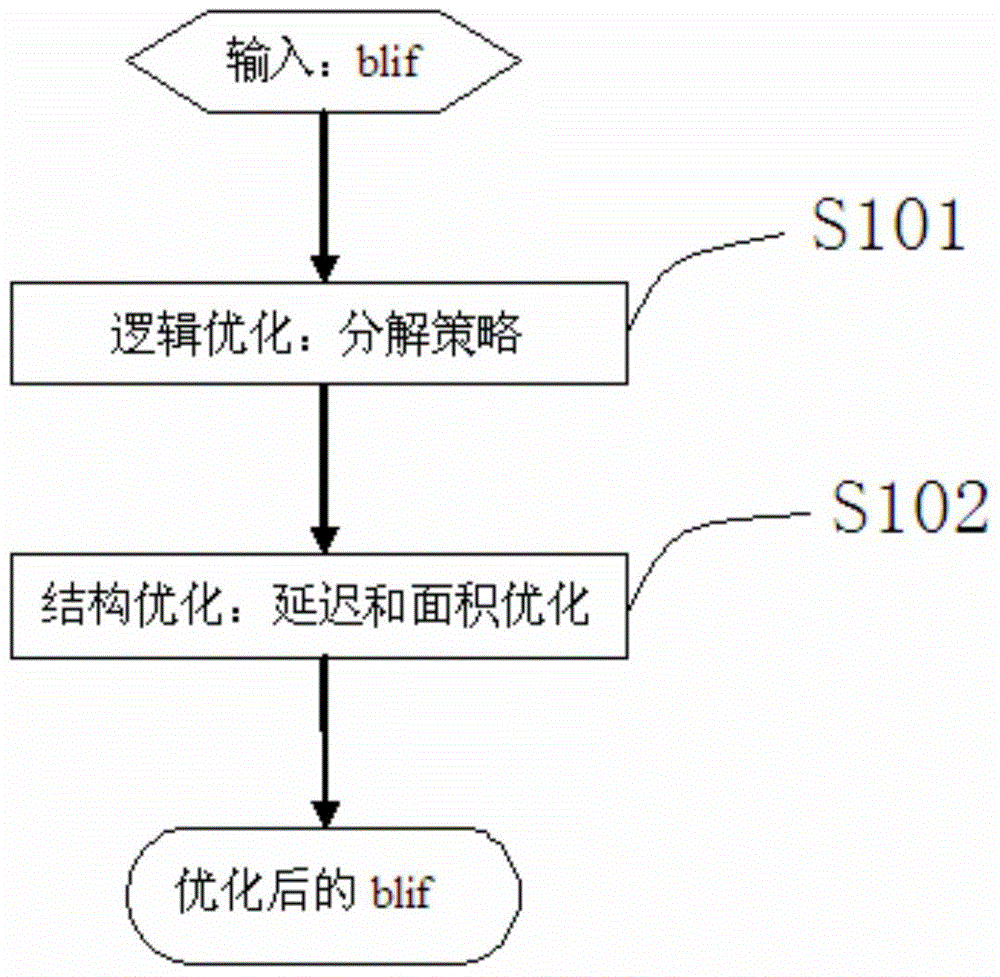

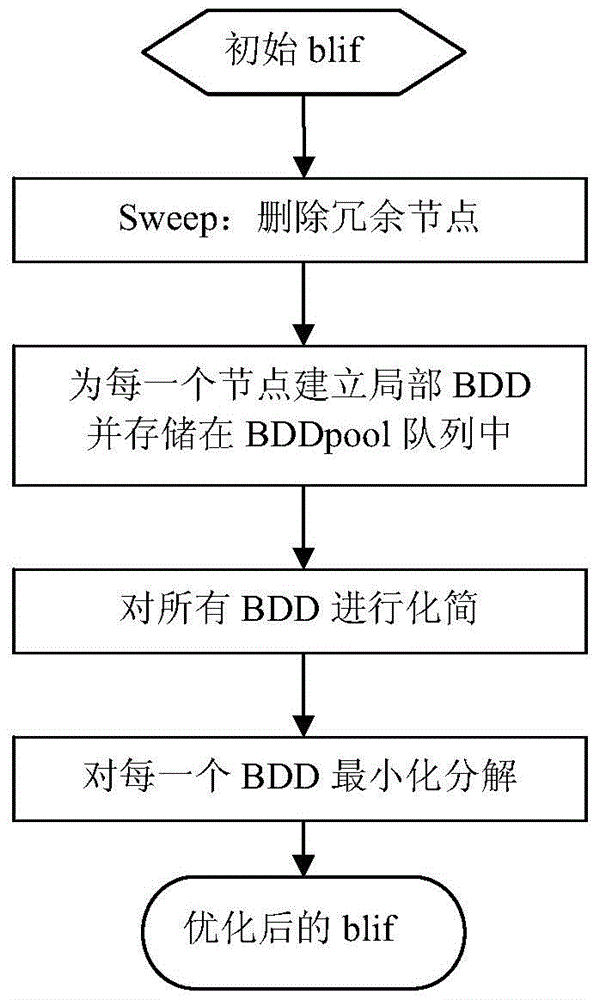

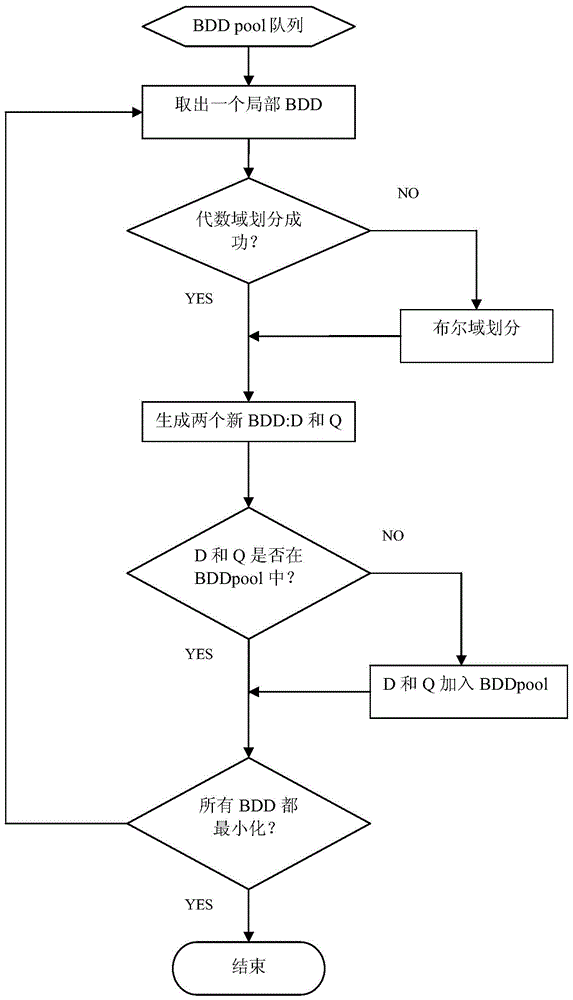

[0048] Such as figure 1 As shown, the method of process mapping based on local minimization of ROBDD and area delay optimization in the embodiment of the present invention is applied to the process mapping in the electronic design automation (EDA) software development process that supports FPGA development, and it integrates the logic of the previous step The generated Boolean network is converted into a LUT network and provided to the next step of packaging for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More