Drive circuit for GaN power devices

A technology for driving circuits and power devices, which is used in output power conversion devices, electrical components, and high-efficiency power electronic conversion. consumption, overcome the effect of overcharging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] Below in conjunction with accompanying drawing, describe technical scheme of the present invention in detail:

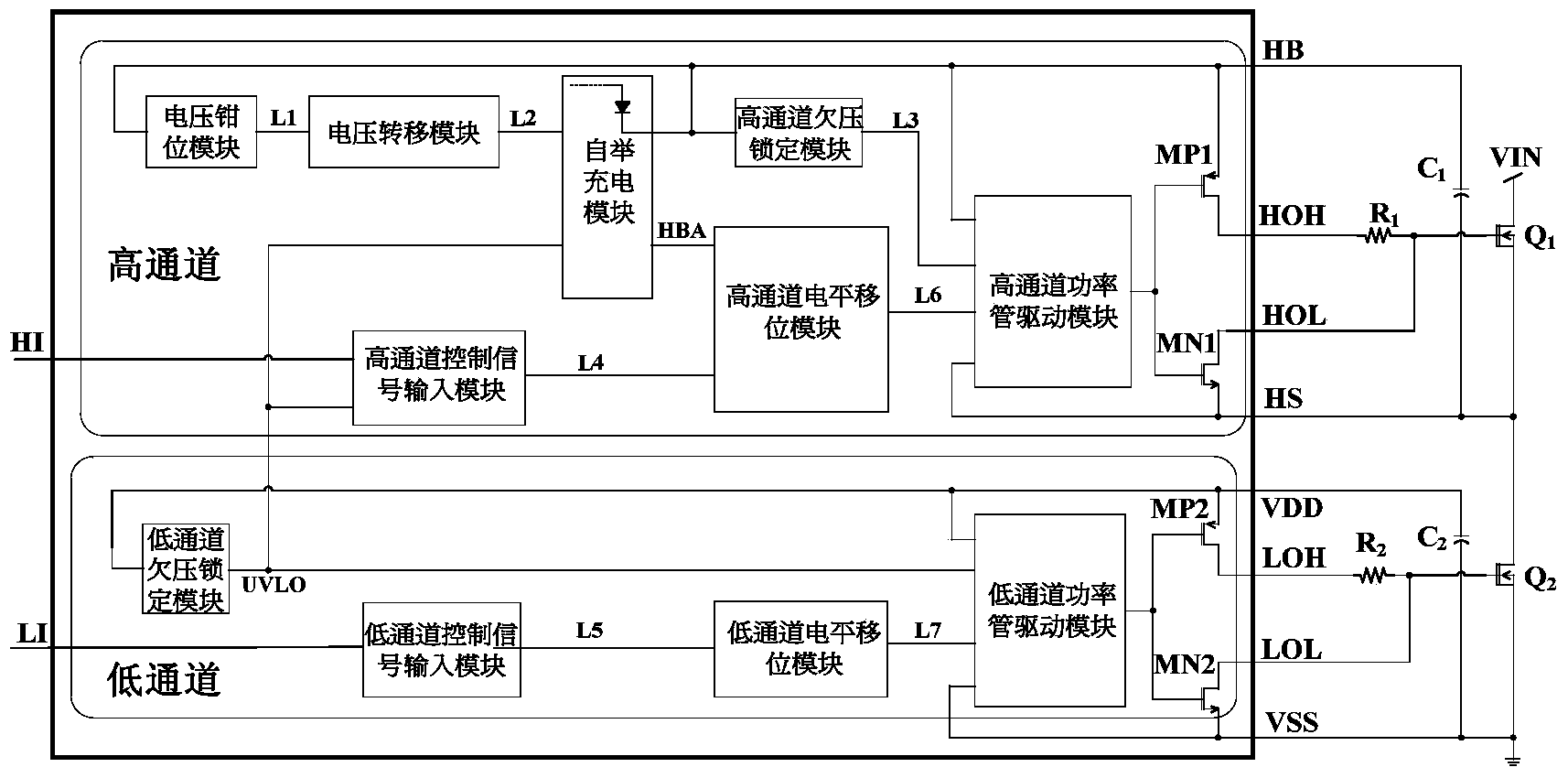

[0016] According to the characteristics of GaN FETs, based on the traditional half-bridge drive principle, the present invention proposes a fully integrated half-bridge drive circuit suitable for GaN FETs, the specific circuit structure is as follows image 3 As shown, including bootstrap capacitor voltage clamping module CLAMP, voltage transfer module LEVEL_DOWN, bootstrap charging module BOOT, high channel undervoltage lockout module UVLO_HS, high channel control signal input module HIN, high channel level shift module LEVEL_UPHS, high channel Power tube driver module DRIVER_HS, low-channel undervoltage lockout module UVLO, low-channel control signal input module LIN, low-channel level shift module LEVEL_UPLS, low-channel power tube driver module DRIVER_LS, PMOS tubes MP1, MP2, NMOS tubes MN1, MN2, GaN FET Q 1 , Q 2 , resistor R 1 , R 2 , capacitance C ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More