Device for scheduling and buffering data packets and method thereof

A data packet and data technology, applied in the field of data communication, can solve the problems of increasing chip cost, increasing chip storage burden, and large data packet length, etc., to achieve the effect of reducing chip cost, saving internal storage resources, and shortening delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

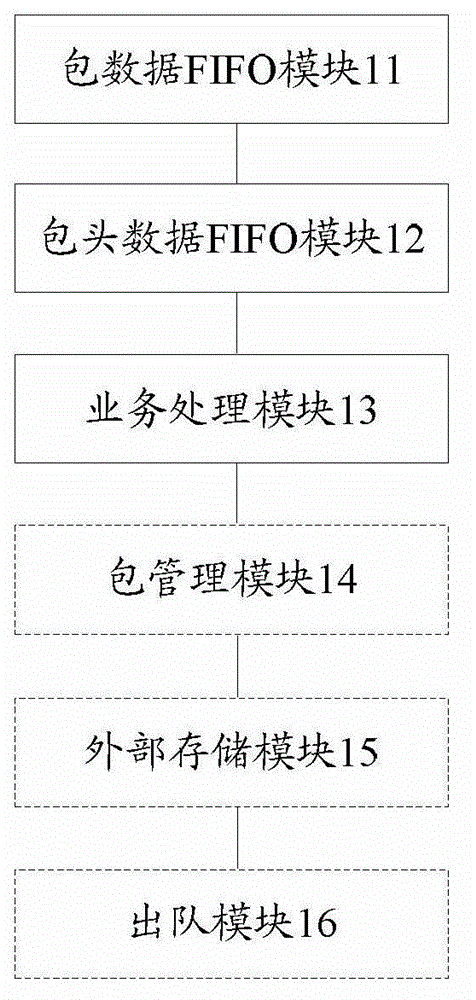

[0039] figure 1 It is a schematic diagram of the composition and structure of the data packet scheduling and buffering device of the present invention, such as figure 1 As shown, the device includes a packet data FIFO module 11, a packet header data FIFO module 12 and a service processing module 13; wherein,

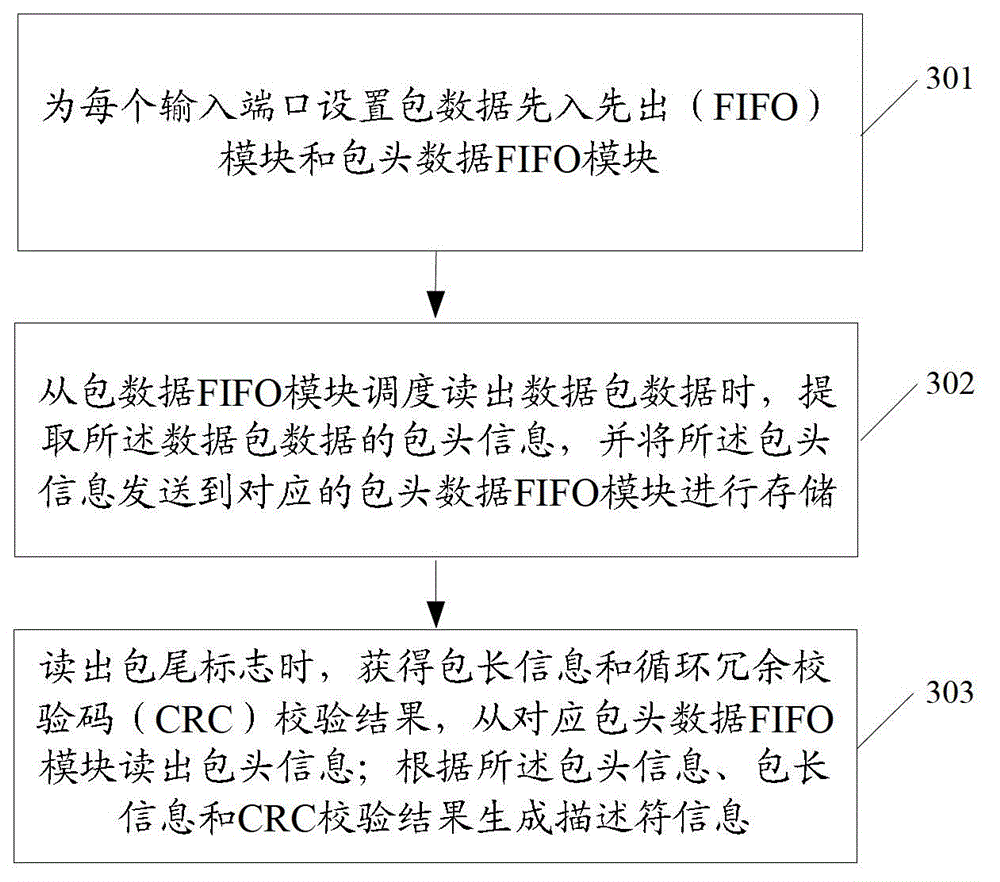

[0040] The packet data FIFO module 11 is used to schedule and read the packet data, extract the packet header information of the packet, and send the packet header information to the corresponding packet header data FIFO module 12 for storage; When going out the end of packet sign (EOP, End Of Packet), obtain packet length information and CRC check result, and described packet length information and CRC check result are sent to service processing module 13;

[0041] The packet header data FIFO module 12 is used to store the pa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More