Chemical Mechanical Polishing Method and Chip Layout Equivalent Feature Parameter Extraction Method

A technology of feature parameters and extraction methods, applied in special data processing applications, electrical digital data processing, instruments, etc., can solve the problems of low yield and low precision of integrated circuits, and achieve high yield and precision. low effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

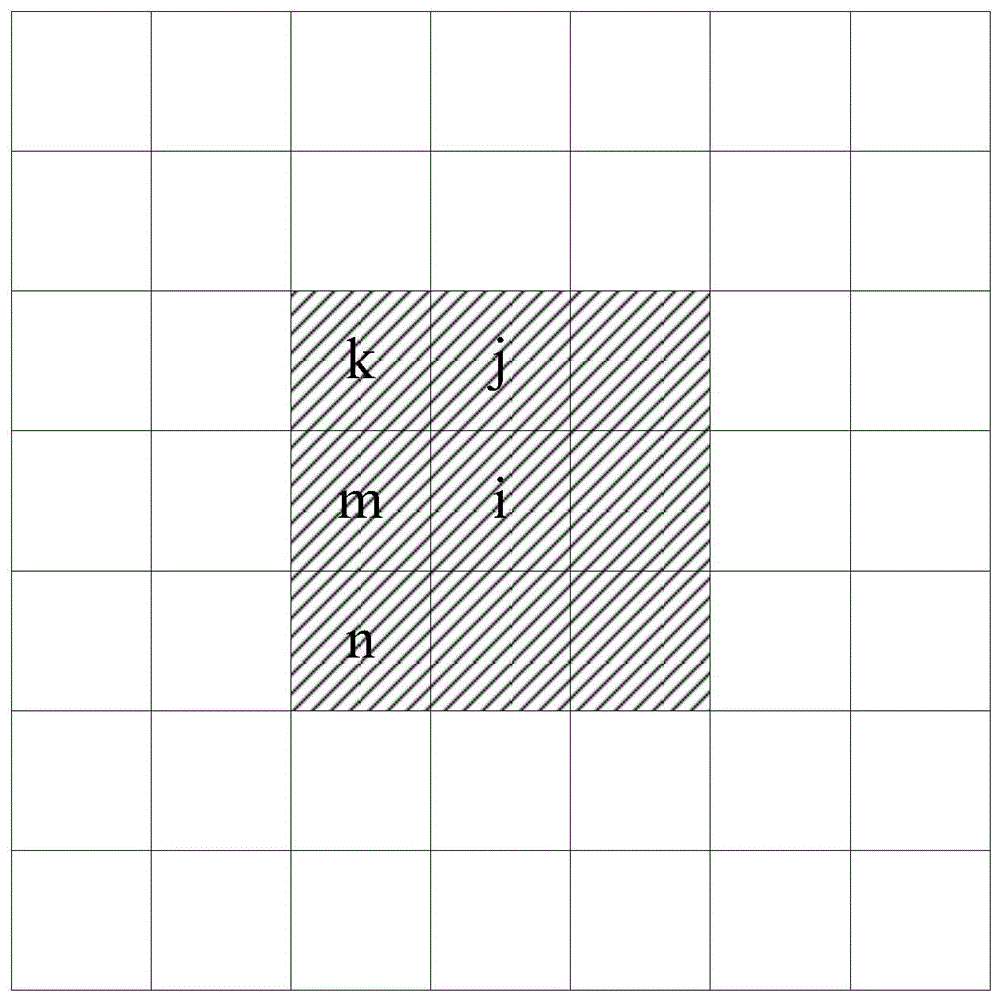

[0042] As mentioned in the background art section, in the prior art, the method for predicting chip surface topography using a CMP model has low accuracy, resulting in a low yield rate of integrated circuits.

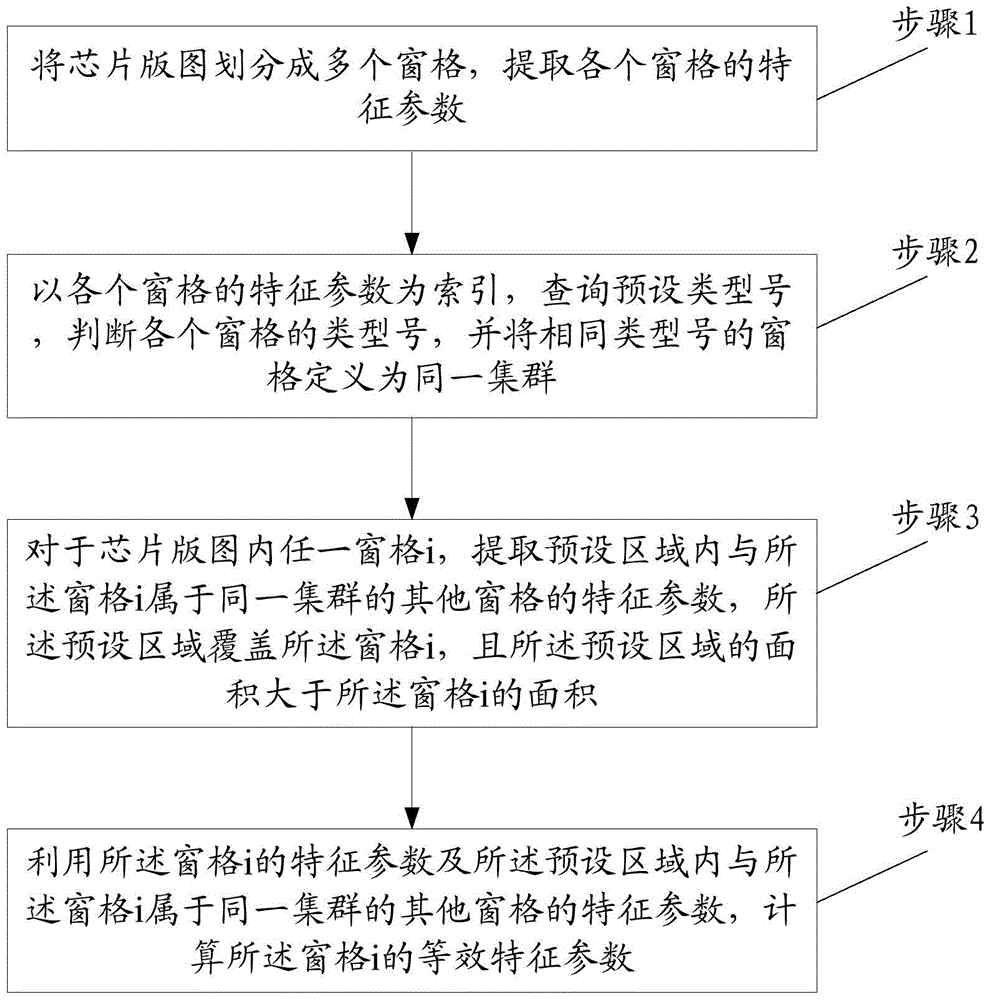

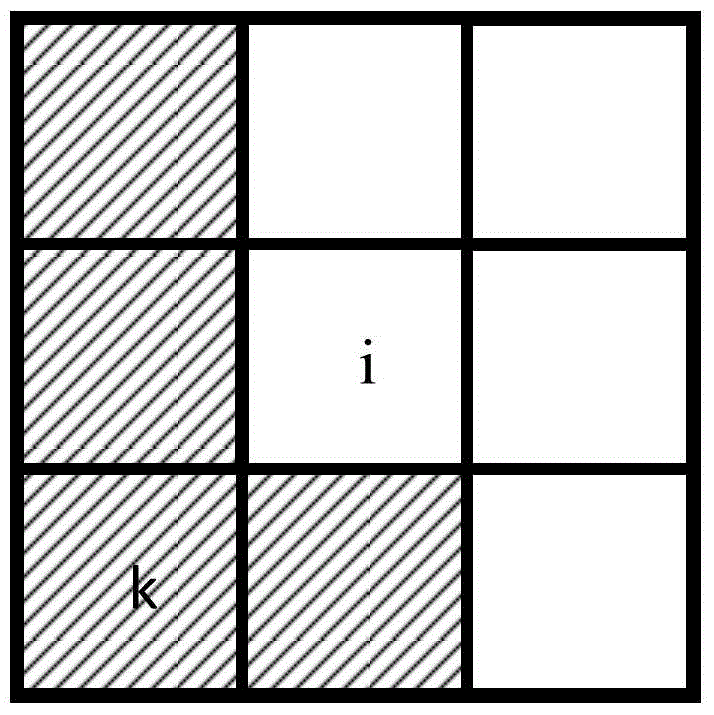

[0043] In the CMP simulation process, layout division and feature parameter extraction are very important steps. All subsequent simulation processes are based on the divided panes and the extracted feature parameters. Different layout division methods and different feature parameter extraction method, will lead to different CMP simulation results. If an unreasonable layout division method and characteristic parameter extraction method are adopted, the complexity of the subsequent CMP simulation process will be increased and the accuracy of the CMP simulation results will be reduced.

[0044]The method of layout division and feature parameter extraction in the prior art is as follows: first, starting from the starting point of the layout, using a fixed-size pane (or slig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More