Method for extracting chip layout features, cmp simulation method and system

A simulation method and layout technology, applied in design optimization/simulation, CAD circuit design, special data processing applications, etc., can solve problems such as reducing the accuracy of CMP simulation results, low integrated circuit yield, and graphic feature deviation, so as to reduce errors CMP hotspot information, shortening the production cycle, and improving the effect of precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] In order to make the purpose and features of the present invention more obvious and understandable, the specific implementation of the present invention will be further described below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

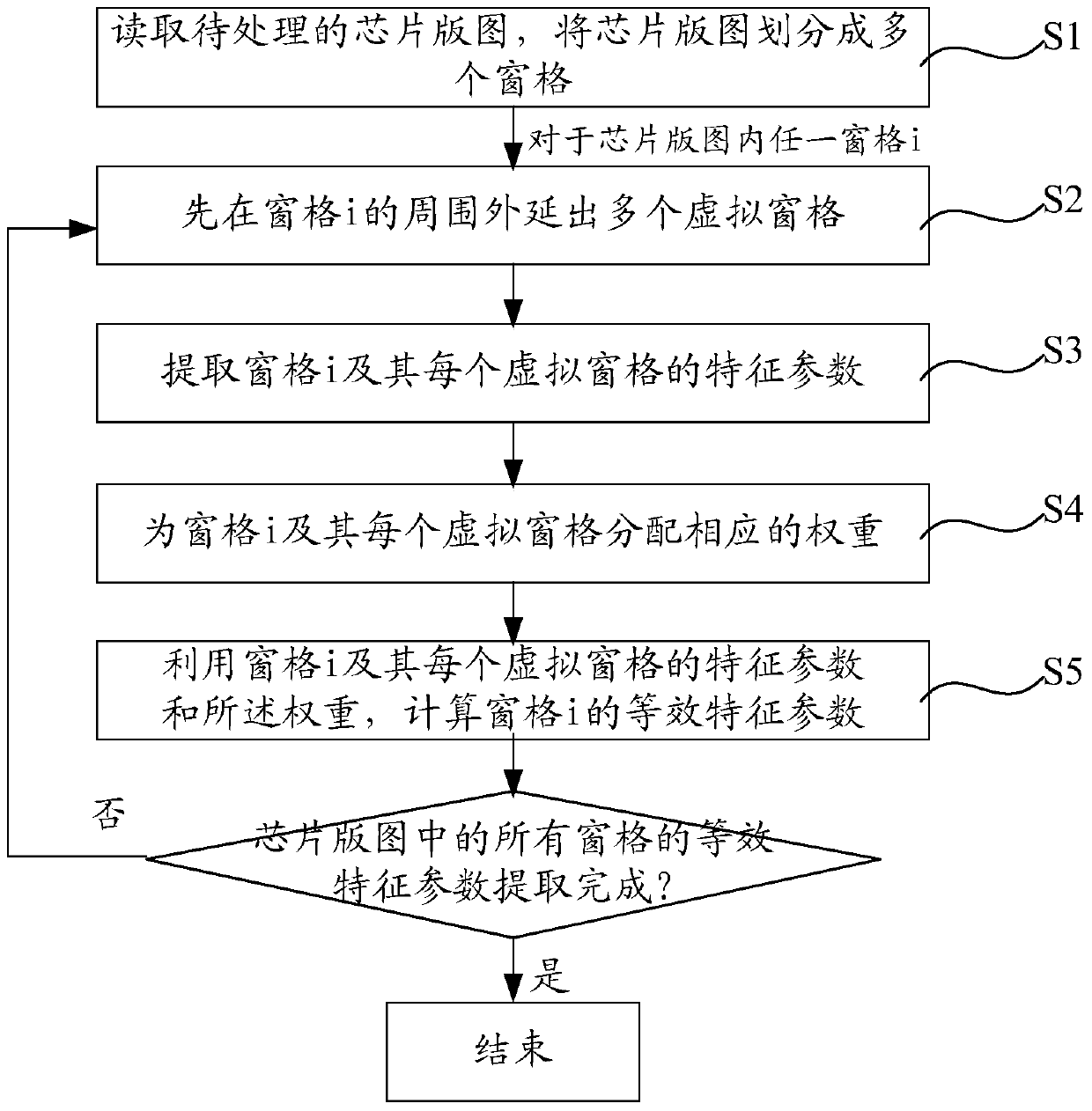

[0056] Please refer to figure 2 , the present invention proposes a method for extracting chip layout features, including:

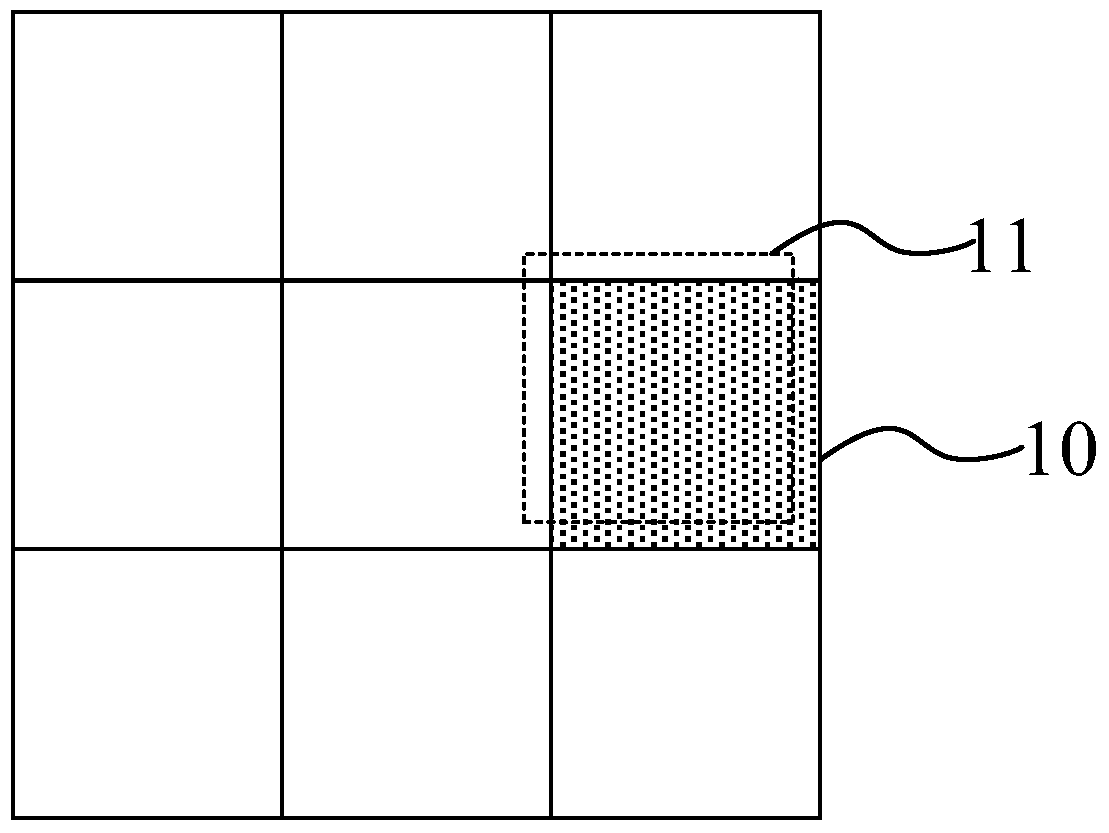

[0057] S1, read the chip layout to be processed, and divide the chip layout into multiple panes;

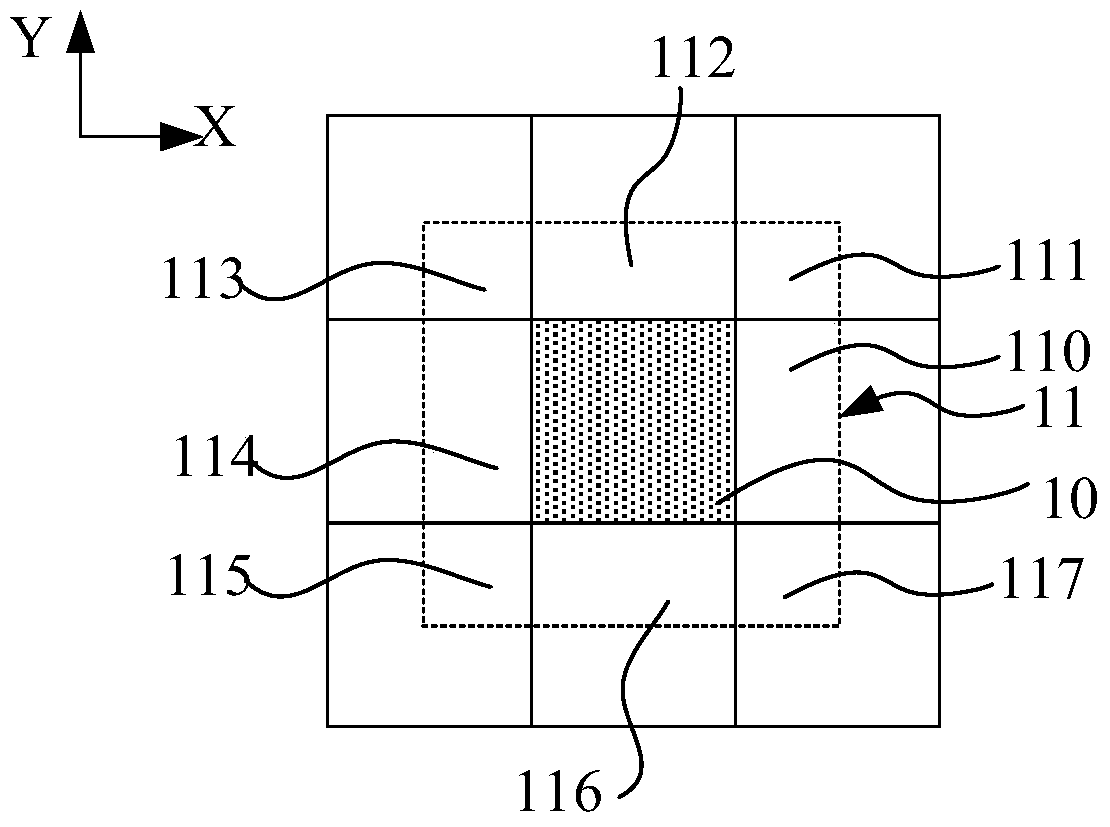

[0058] S2. For any pane in the chip layout, first extend a plurality of virtual panes around the pane;

[0059] S3, extracting the feature parameters of the pane and each virtual pane;

[0060] S4, assigning corresponding weights to the pane and each virtual pane;

[0061] S5. Calculate an equivalent feature parameter of the pane by using the feature parameter of the pane and each virtual pane a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More