Semiconductor device with multilayer epitaxial super junction structure and manufacturing method thereof

A manufacturing method and super junction technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as high manufacturing cost, long production cycle, and poor reverse recovery characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] In order to make the objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

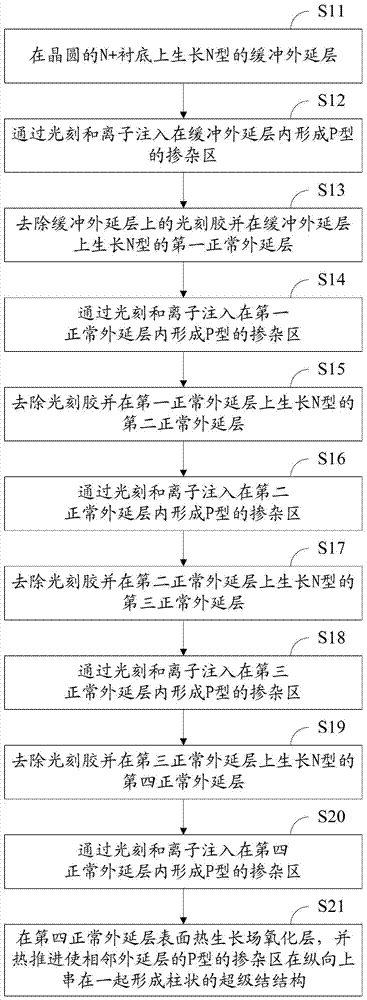

[0018] figure 1 It is a flowchart of a method for manufacturing a semiconductor device with a multilayer epitaxial super junction structure in an embodiment, including the following steps:

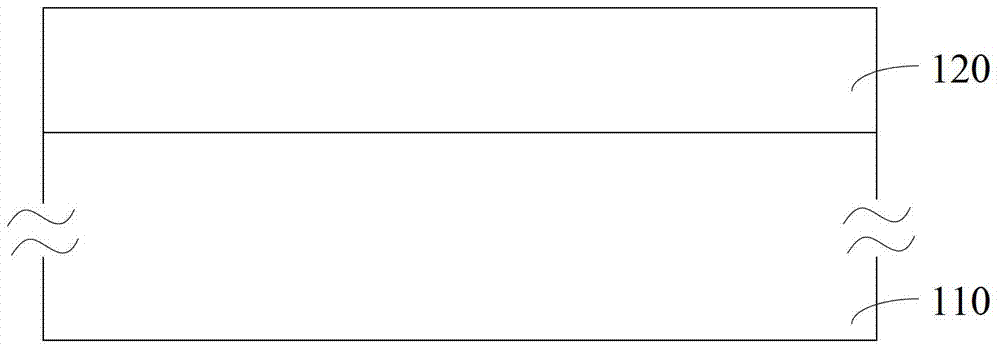

[0019] S11, growing an N-type buffer epitaxial layer on the N+ substrate of the wafer.

[0020] See Figure 2A , grow a thicker N-type buffer epitaxial layer 120 on the N+ substrate 110 .

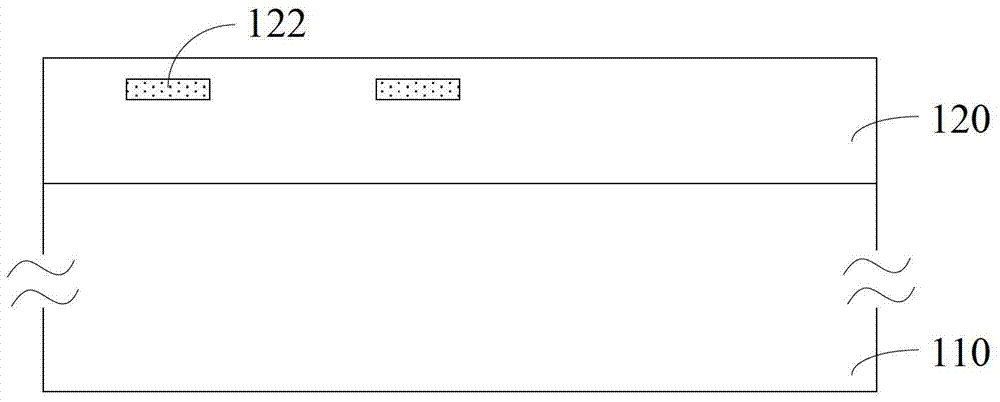

[0021] S12, forming a P-type doped region in the buffer epitaxial layer by photolithography and ion implantation.

[0022] See Figure 2B , form the doped region window by photolithography and form the P-type doped region 122 by ion implantation (the photoresist is in Figure 2B not shown). It can be understood that in an actual device, multiple doped regions 12...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More