Complementation common-source common-grid inverter and increment Sigma-Delta analog-to-digital conversion circuit

An analog-to-digital conversion circuit and cascode technology, applied in the direction of incremental modulation, can solve the problems of DC operating point and inverter strong process sensitivity, gain and bandwidth limitations, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The specific implementation manners of the present invention will be described below in conjunction with the accompanying drawings.

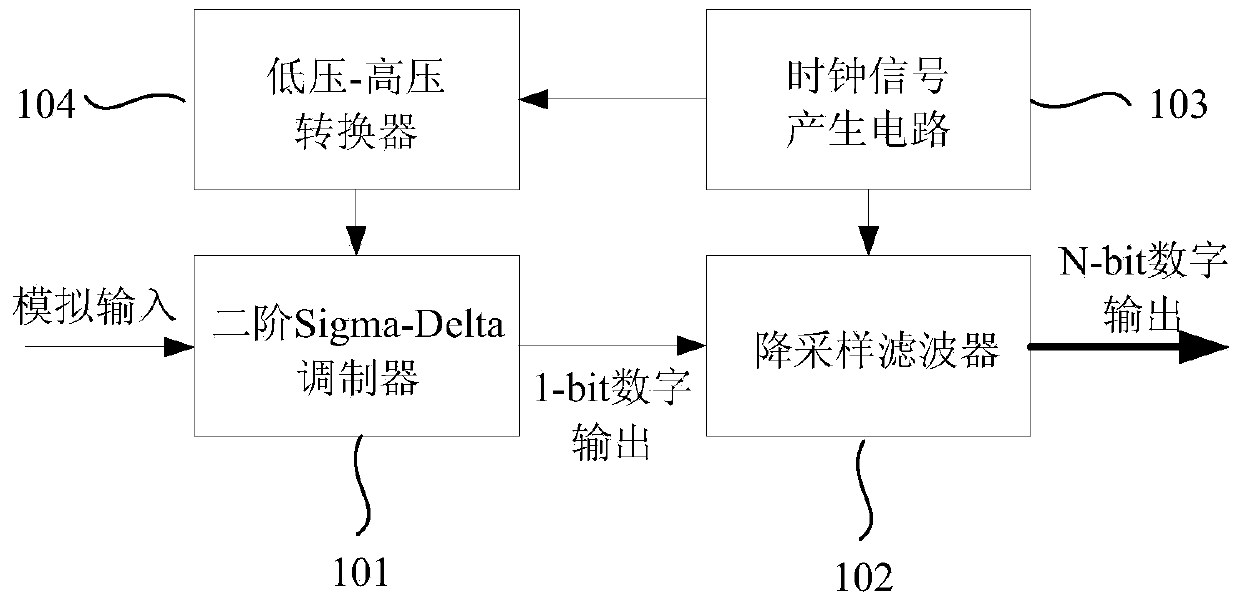

[0023] The present invention is composed of a second-order delta ΣΔ modulator section 101 , a downsampling filter section 102 , a clock signal generation circuit 103 , and a low voltage-high voltage converter 104 . The second-order incremental ΣΔ modulator 101 converts the input DC voltage into a 1-bit digital quantity containing high-frequency quantization noise, and the 1-bit digital quantity is input to the down-sampling filter 102, and converted into an N-bit digital output, and the clock signal is generated A part of the clock signal generated by the circuit 103 is sent to the second-order delta ΣΔ modulator 101 through the low-voltage-high-voltage converter 104 , and the other part is sent to the down-sampling filter unit 102 .

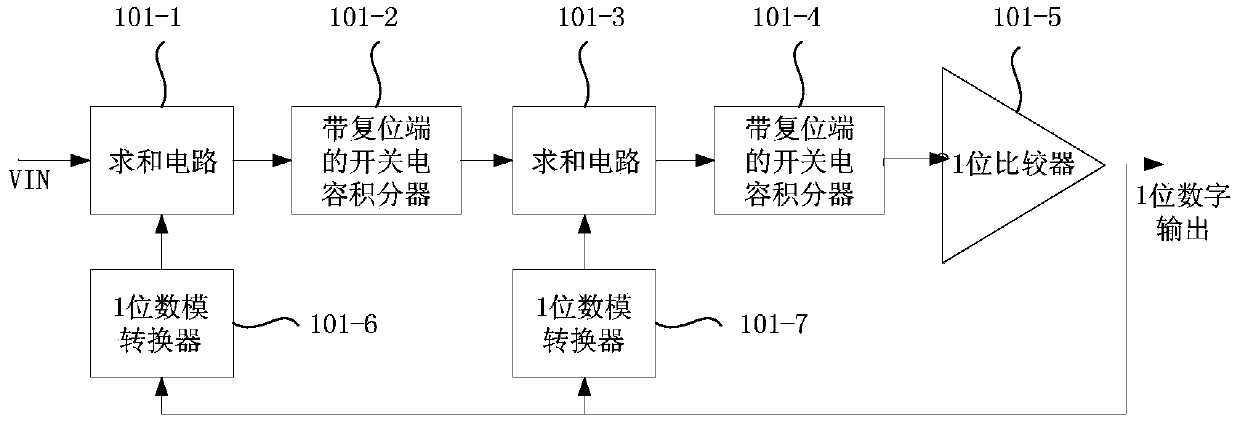

[0024]The second-order delta ΣΔ modulator part 101 is the core circuit of the whole system, which determ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More