Reference memory cell bias voltage generator and bias voltage supply method

A generator and bias voltage technology, applied in the field of serial interface flash memory, can solve problems such as memory cell degradation, reference memory cell damage, and reduce the reading boundary of serial interface flash memory, so as to reduce read interference Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

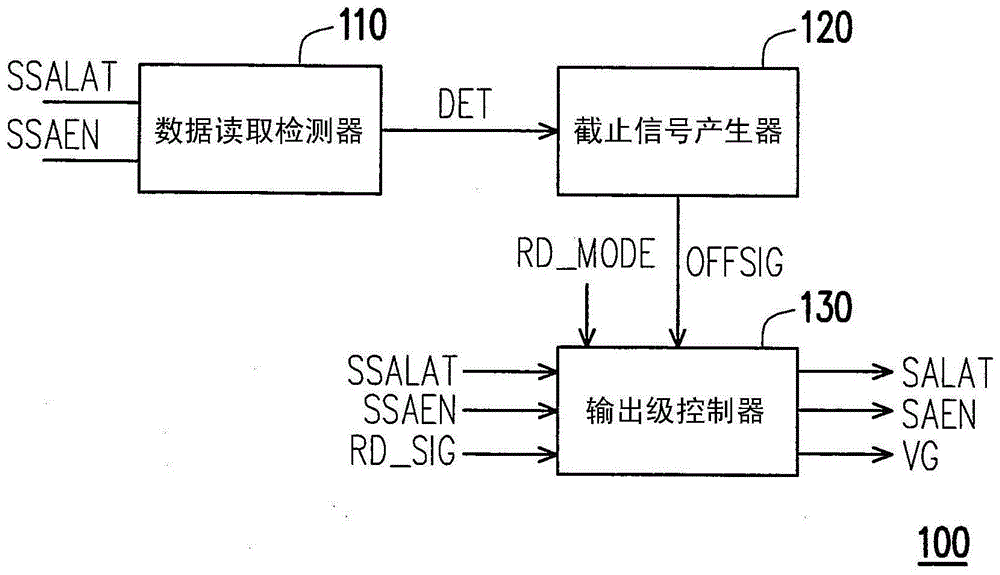

[0052] Please refer to the following figure 1 , figure 1 A schematic diagram of a bias voltage generator 100 for a reference memory cell according to an embodiment of the present invention is shown. The bias voltage generator 100 is suitable for a serial interface flash memory, such as a Serial Peripheral Interface (SPI) flash memory. The bias voltage generator 100 includes a data read detector 110 , an off signal generator 120 and an output stage controller 130 . The data read detector 110 receives the sense amplifier enable signal SSAEN and the sense amplifier latch signal SSALAT, both of which are timing signals in a synchronous timing system, according to the sense amplifier enable signal SSAEN and the sense amplifier latch transition point of signal SSALAT to generate detection signal DET. The cutoff signal generator 120 is coupled to the data reading detector 110 . The off signal generator 120 receives and generates the off signal OFFSIG through a time delay accordin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More