Sealing rings and chip with same

A sealing ring and inner sealing ring technology, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problem that the stress cannot be prevented from spreading to the integrated circuit area of the chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

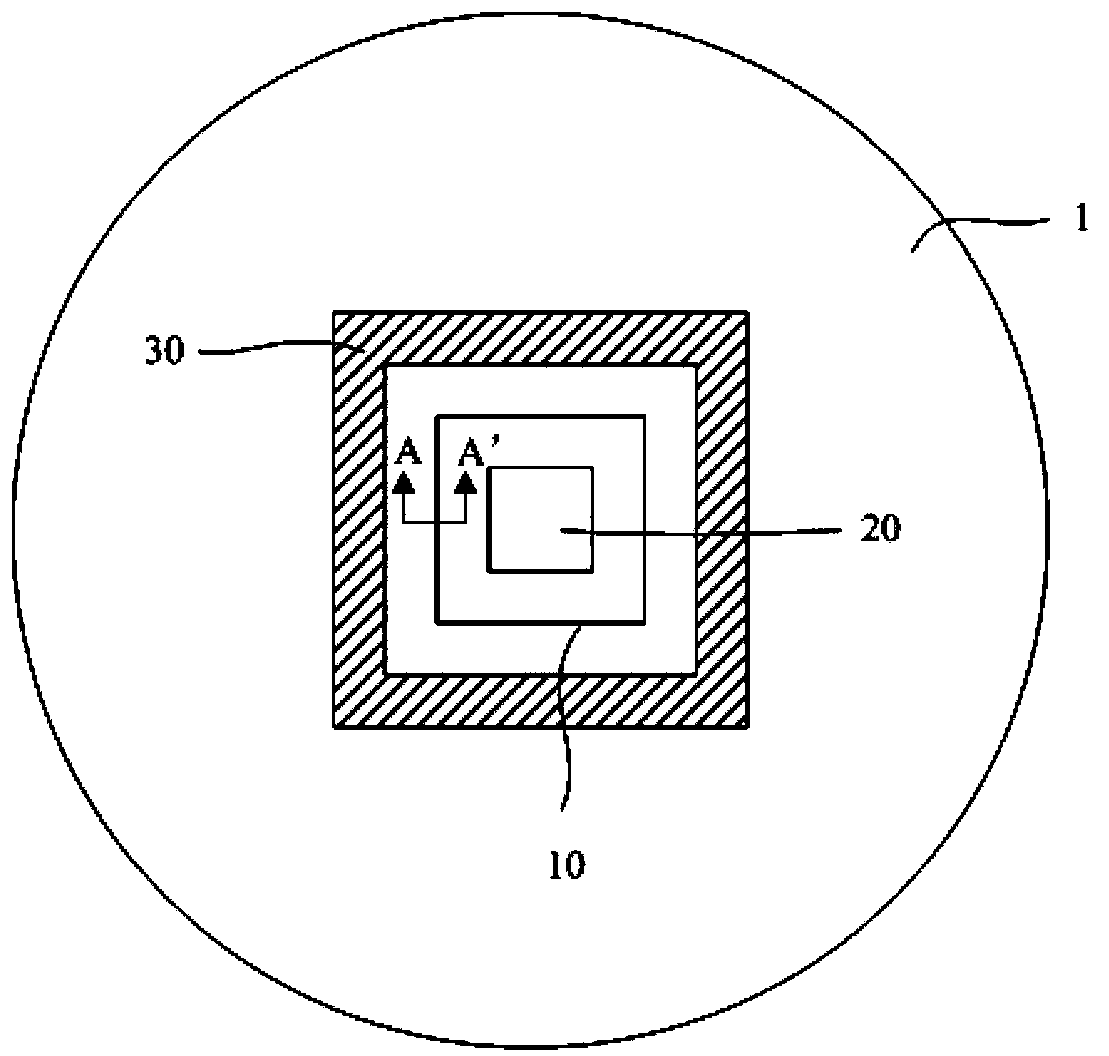

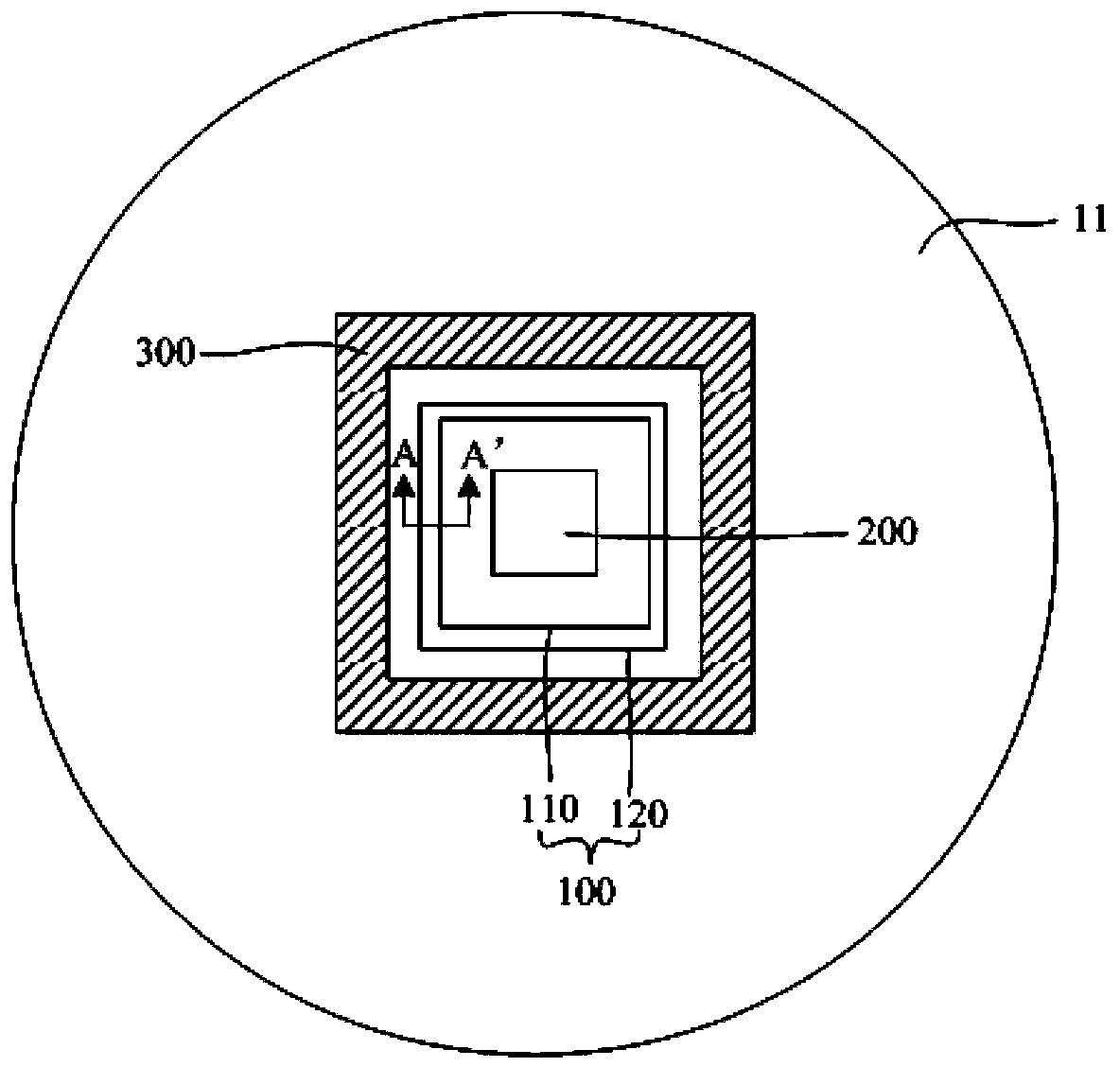

[0040] refer to image 3 , image 3It is a top view of the chip sealing ring 100 , the integrated circuit area 200 and the dicing line 300 formed on the wafer 11 . The chip sealing ring 100 is surrounded by a dicing line 300 , and the chip sealing ring 100 surrounds an integrated circuit region 200 in the chip. The chip sealing ring 100 includes an inner sealing ring 110 and an outer sealing ring 120 surrounding the inner sealing ring 110 . That is, the inner sealing ring 110 is closer to the integrated circuit area 200 .

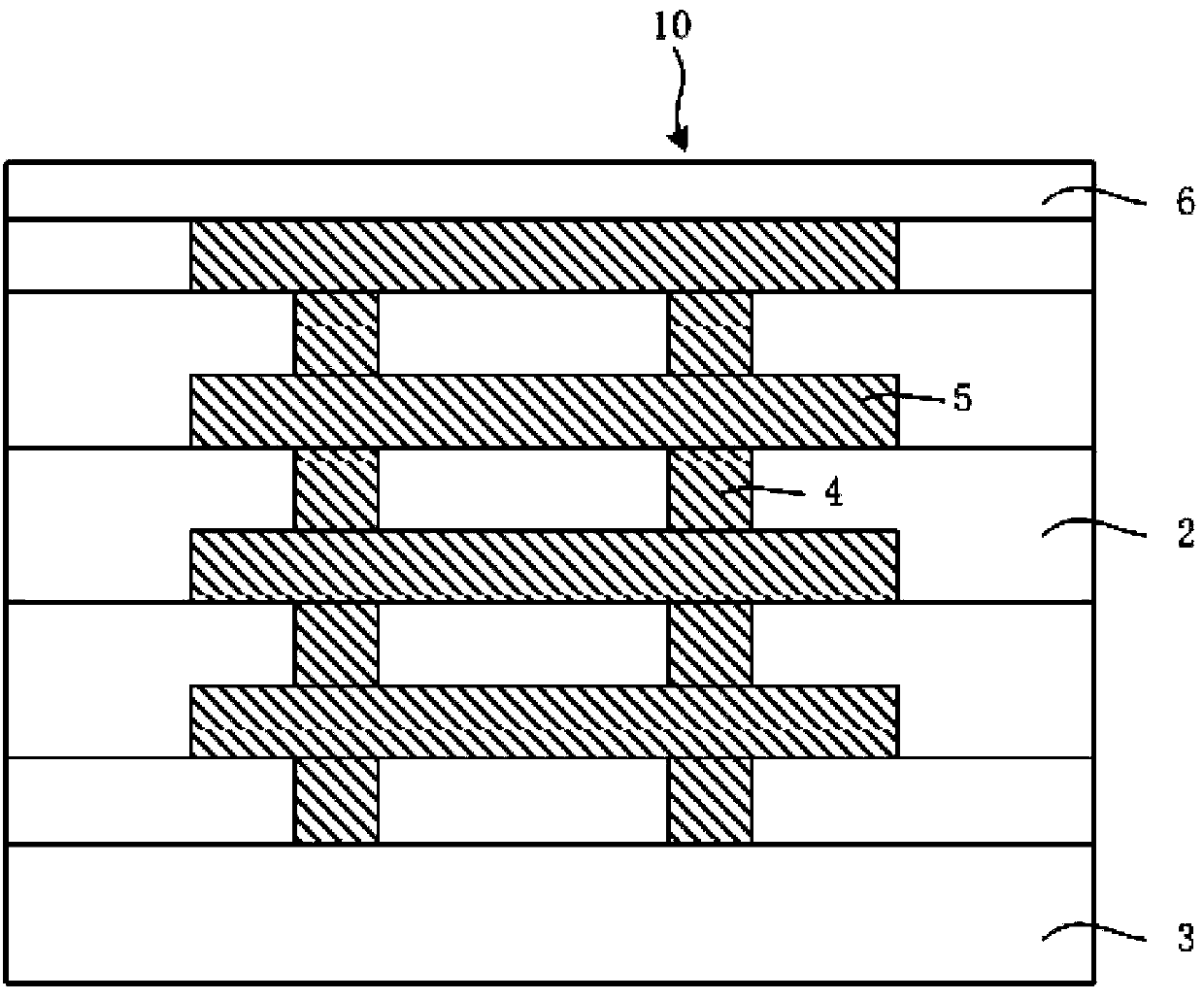

[0041] refer to Figure 4 , Figure 4 for image 3 Schematic diagram of the plane cut along the tangent AA'. The chip sealing ring 100 is located in the dielectric layer 130 of the chip, and the dielectric layer 130 and the integrated circuit region 200 are both located on the substrate 101 . The dicing line 300 is located on the left side of the chip sealing ring 100 , and the right side of the chip sealing ring 100 is the integrated circuit area 20...

no. 2 example

[0057] refer to Figure 5 , In a specific embodiment, the number of the inner sealing ring or the outer sealing ring is more than two, or the number of the inner sealing ring and the outer sealing ring is more than two. Figure 5 Shown are outer seal ring 120A and outer seal ring 120B, inner seal ring 110A and inner seal ring 110B.

[0058] In a specific embodiment, the number of the inner sealing ring and the outer sealing ring is more than two, the material of each first plug in the inner sealing ring is the same, and the inner sealing ring near the integrated circuit area The diameter of the first plug is larger than the diameter of the first plug in the inner seal ring away from the integrated circuit area; or, the diameters of each first plug are the same, and the first plug material in the inner seal ring near the integrated circuit area The fracture toughness is greater than the fracture toughness of the first plug material in the inner sealing ring far away from the i...

no. 3 example

[0064] refer to Image 6 , in a specific embodiment, the number of the outer sealing ring is two, which are the outer sealing ring 120A and the outer sealing ring 120B, and the outer sealing ring 120A and the outer sealing ring 120B share the top second conductive layer 121 and are connected to each other.

[0065]In a specific embodiment, there are two inner sealing rings, that is, the inner sealing ring 110A and the inner sealing ring 110B. The inner sealing ring 110A and the inner sealing ring 110B share the top first conductive layer 111 and are connected to each other.

[0066] Image 6 The case where there are two outer sealing rings and two inner sealing rings is only shown as an example. In other embodiments, the number of outer sealing rings may be more than three, and the number of inner sealing rings may also be more than three. Moreover, the number of sealing ring units of the outer sealing ring and the number of sealing ring units of the inner sealing ring do no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More