A scr device with high sustain voltage embedded gdpmos

A high sustaining voltage and sustaining voltage technology, applied in the direction of electric solid devices, electrical components, semiconductor devices, etc., can solve the problems of insufficient latch-up resistance, low triggering, high sustaining voltage, etc., to improve the secondary failure current, high The effect of maintaining voltage and high protection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below in conjunction with accompanying drawing and specific embodiment the present invention will be described in further detail:

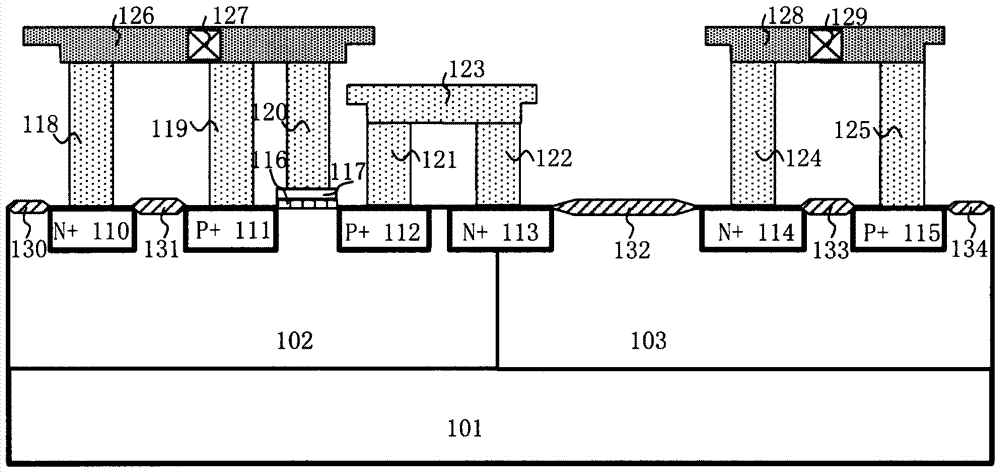

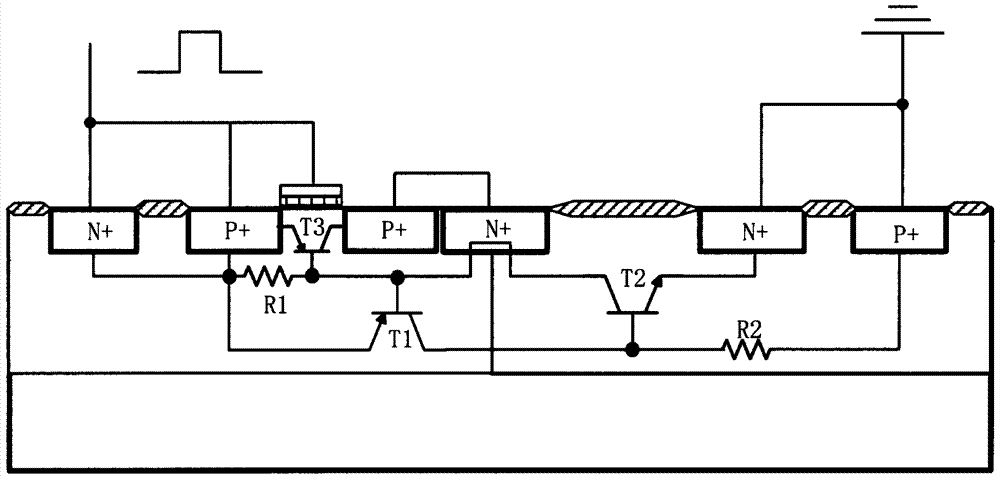

[0024] An example of the present invention designs an SCR device with a high sustaining voltage embedded GDPMOS, which not only makes full use of the characteristics of the SCR device's low on-resistance and large current discharge capability. By increasing the layout structure design and forming an embedded GDPMOS structure at the anode of the device, the sustaining voltage of the device can be increased, and the device can be used in integrated circuit products with different needs by adjusting the key layout size to avoid the latch-up effect .

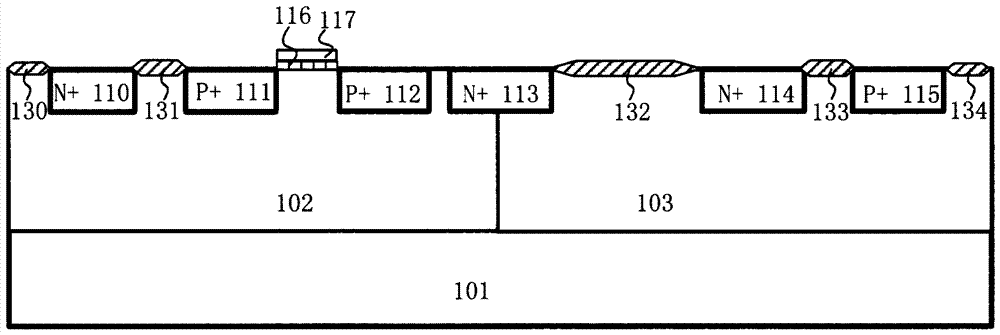

[0025] Such as figure 1 The cross-sectional view of the internal structure of the example device of the present invention is shown, specifically a SCR device with a high sustain voltage embedded GDPMOS, and an SCR current discharge path with an embedded GDPMOS structure to enhance the ESD robust...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More