Partially-depleted silicon-on-insulator triode structure

A technology of silicon on insulator and triode, which is applied in the direction of transistors, semiconductor devices, electrical components, etc., can solve the problems of poor performance of parasitic triodes in silicon MOSFET structures, and achieve good tube performance, easy layout and wiring, and large collector area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

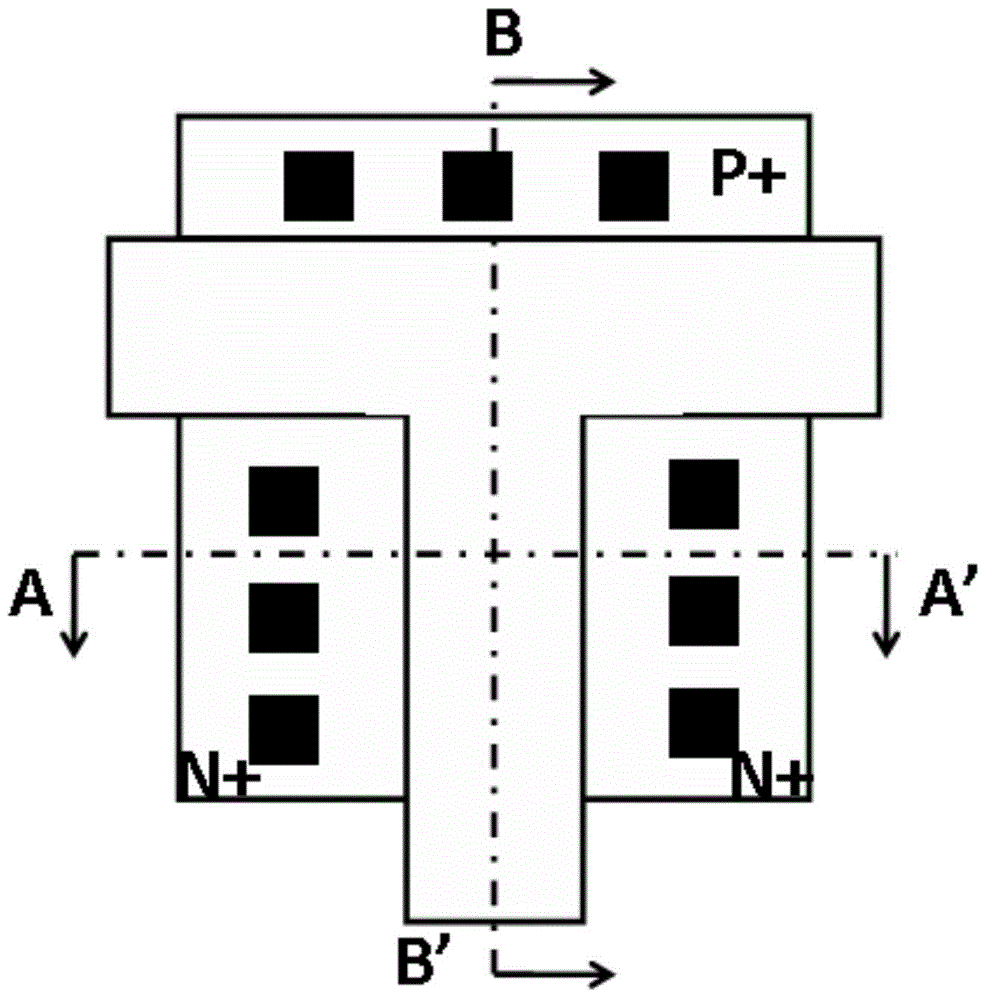

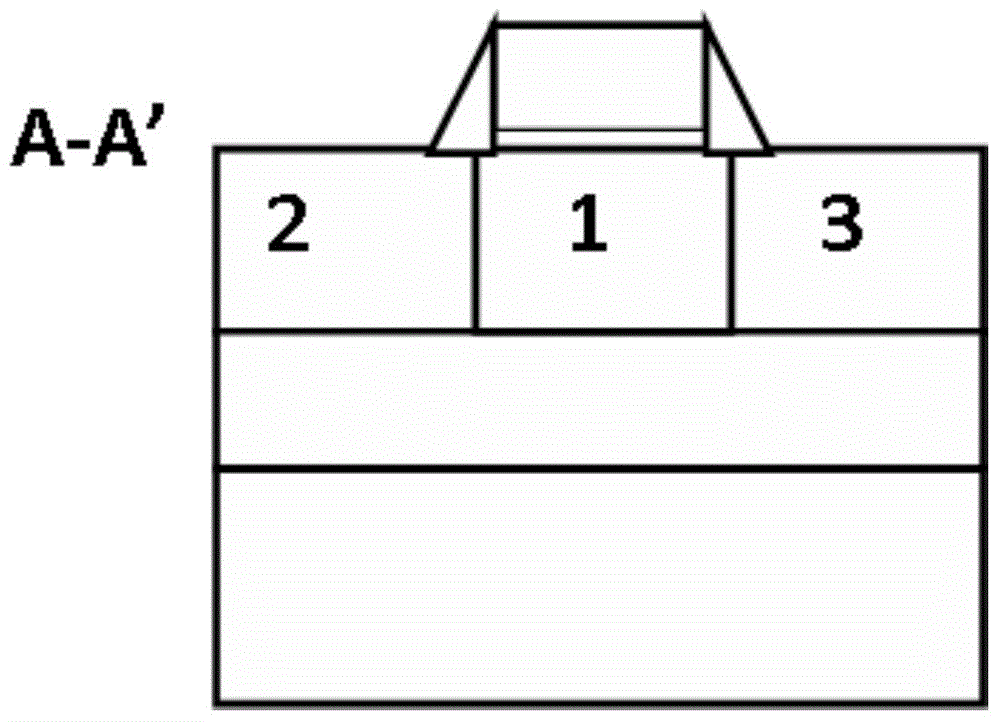

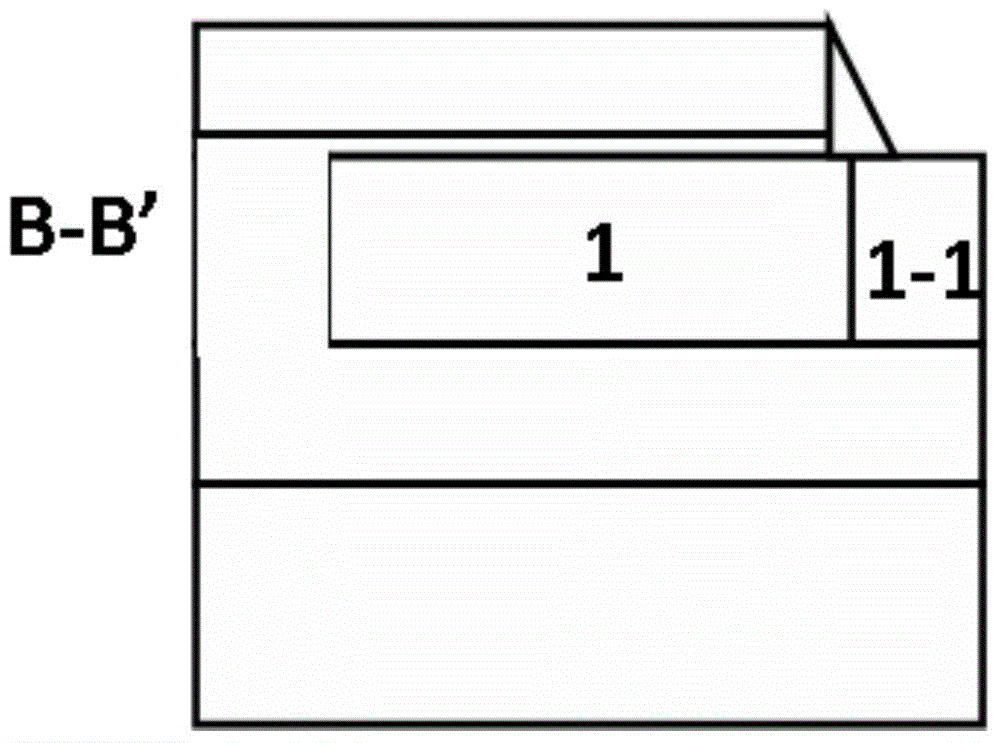

[0021] Figure 4 A schematic cross-sectional view of a partially depleted silicon-on-insulator transistor structure according to a preferred embodiment of the present invention is shown schematically.

[0022] Such as Figure 4 As shown, the partially depleted silicon-on-insulator transistor structure according to the preferred embodiment of the present invention includes: a buried oxide layer 200 (ie SOI silicon wafer) arranged on a substrate 100 (such as a silicon substrate), and a buried oxide layer 200 arranged on the buried oxide layer 200 The upper collector region 600 (preferably, the doping type of the collector region 600 is N-type doping, such as phosphorus doping, arsenic doping), the base region 500 arranged above the collector regi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More