RF impedance matching debugging method

A technology of impedance matching and debugging method, applied in impedance matching network, multi-terminal pair network, etc., can solve the problems of complicated use and impossible pre-installation of circuit simulation software, so as to improve the calculation speed and overcome the computer simulation method and manual calculation method. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

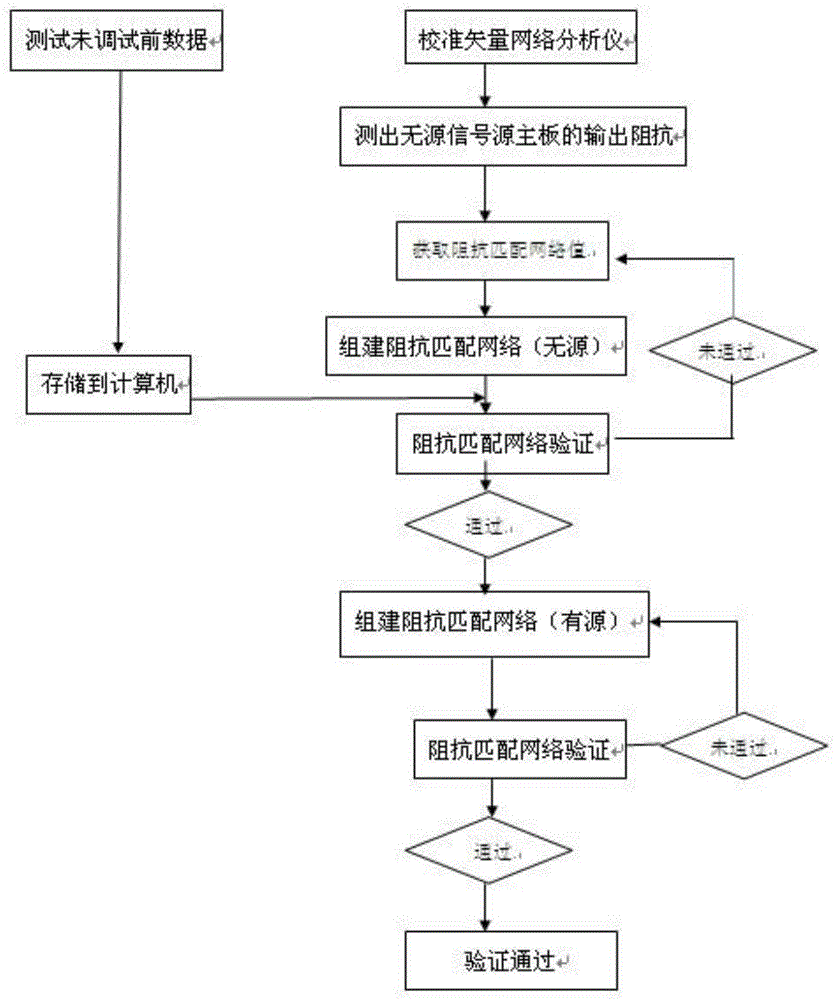

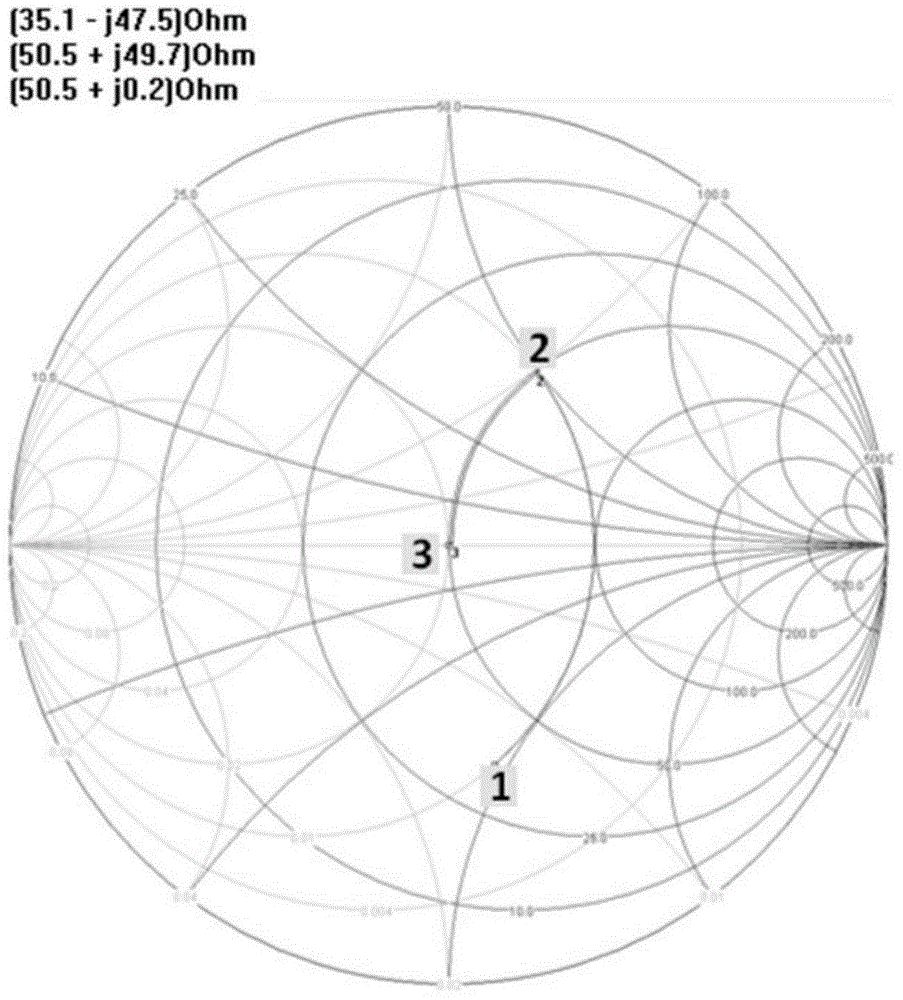

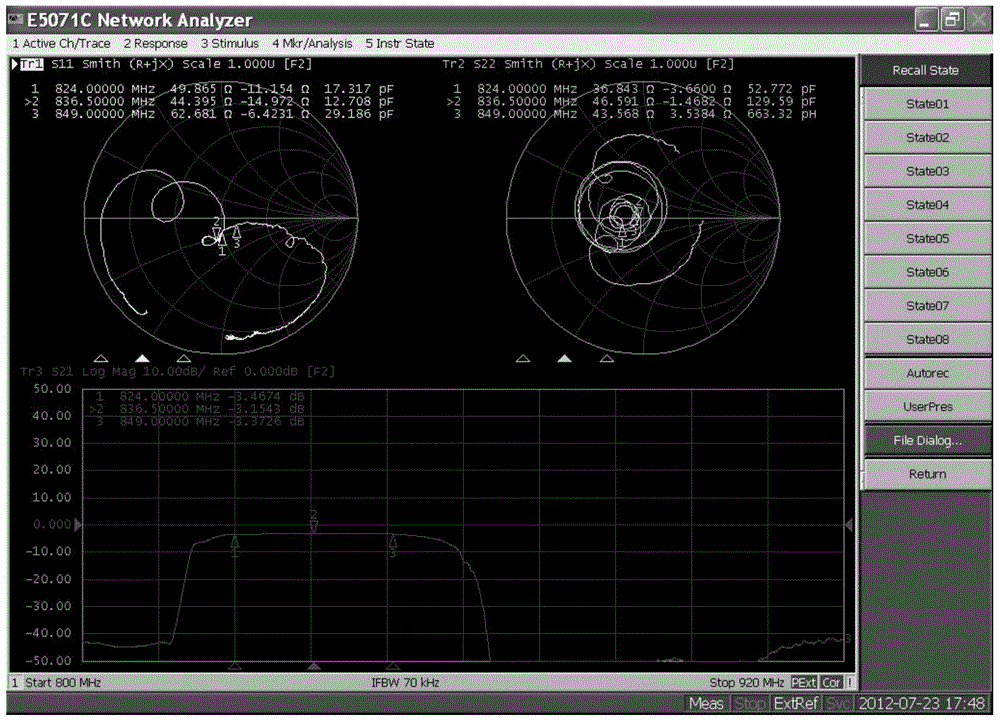

[0052] Take debugging the GSM850 circuit board of PA as an example, figure 2 It is the Smith circle diagram of the present embodiment; image 3 The vector network analyzer of the present embodiment measures the RF parameter diagram; Figure 4 It is the Load Pull diagram of the embodiment of the present invention. Designed at 824-849MHz PA operating frequency, signal source impedance: Z S =(35.1-J47.5)Ω, namely figure 2 1 o'clock position. Debugging according to the steps of the present invention, the result is that after the parallel inductance is 8.2nH, the signal source impedance is Z S =(50.5+J49.7)Ω, that is: figure 2in the 2 o'clock position. At the same time, after the series capacitor is 3.9pF, the signal impedance is Z L =(50.5+j0.2)Ω, that is: figure 2 in the 3 o'clock position. To make it meet the index requirement that the voltage standing wave ratio is less than 3.5 in the frequency range of 400-1200, by comparison Figure 4 , so as to optimize the PA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More