An automatic conversion system from hardware language vhdl to msvl

A hardware language, automatic conversion technology, used in memory systems, program control design, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

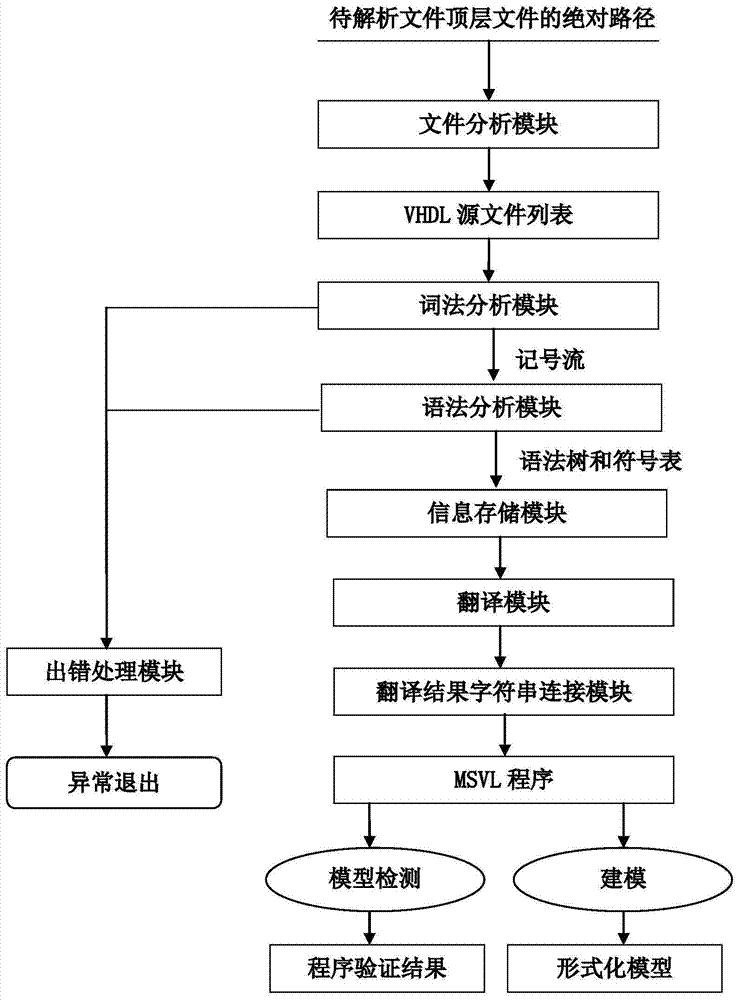

[0082] The present invention will be further described below with reference to the accompanying drawings.

[0083] like figure 1 , figure 2 As shown, the present invention is an automatic conversion system from VHDL to MSVL, and the automatic conversion system includes:

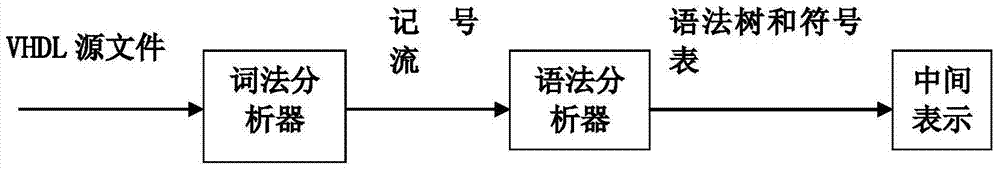

[0084] File analysis module: equipped with a file analyzer, the file analyzer analyzes the top-level file parameter string of the VHDL program file, analyzes the file parameter string, obtains all files that need to be translated, and analyzes the dependencies between the files , so that the order of translation is determined according to the dependencies, and a list of VHDL source files to be translated is generated, and the files in the list are passed to the lexical analysis module in order;

[0085] Lexical analysis module: equipped with a lexical analyzer, the lexical analyzer uses regular expressions to analyze the VHDL source program, and identifies the morphemes in the source program, such as keywo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More